През_память.ppt

- Количество слайдов: 66

ЗАПОМИНАЮЩИЕ УСТРОЙСТВА ЭВМ. ТИПЫ ЗУ И ИХ ОСНОВНЫЕ ХАРАКТЕРИСТИКИ. Назначение ЗУ в ЭВМ состоит в хранении исходной и промежуточной информации необходимой для проведения расчетов и их результатов. Основным требованием к ЗУ является надежное хранение информации без изменения ее начального содержания в течение длительного времени. Основными характеристиками любого ЗУ являются : быстродействие, ёмкость и стоимость. Быстродействие ЗУ оценивается временем обращения (интервалом времени между двумя последовательными обращениями) tобр(цикла) = tпоиск + tсч(зап) + tреген tвыб(дост) = tпоиск + tсч(зап) Ёмкость ЗУ измеряется либо в битах, либо в байтах, либо в n-разрядных словах, которые могут быть записаны в одну ячейку памяти. Стоимость ЗУ оценивается обычно в стоимости хранения одного бита информации и лежит в широких пределах.

ЗАПОМИНАЮЩИЕ УСТРОЙСТВА ЭВМ. ТИПЫ ЗУ И ИХ ОСНОВНЫЕ ХАРАКТЕРИСТИКИ. Назначение ЗУ в ЭВМ состоит в хранении исходной и промежуточной информации необходимой для проведения расчетов и их результатов. Основным требованием к ЗУ является надежное хранение информации без изменения ее начального содержания в течение длительного времени. Основными характеристиками любого ЗУ являются : быстродействие, ёмкость и стоимость. Быстродействие ЗУ оценивается временем обращения (интервалом времени между двумя последовательными обращениями) tобр(цикла) = tпоиск + tсч(зап) + tреген tвыб(дост) = tпоиск + tсч(зап) Ёмкость ЗУ измеряется либо в битах, либо в байтах, либо в n-разрядных словах, которые могут быть записаны в одну ячейку памяти. Стоимость ЗУ оценивается обычно в стоимости хранения одного бита информации и лежит в широких пределах.

ИЕРАРХИЧЕСКАЯ ОРГАНИЗАЦИЯ ПАМЯТИ Характеристики ЗУ антагонистичны и зависят от типа используемых запоминающих элементов. Стоимость Время доступа ЭСЛ ТТЛШ МОП МЛ МД ПЗС, ЦМД МД МЛ Время доступа МОП ТТЛШ ЭСЛ Ёмкость Иерархическая структура памяти предполагает объединение ЗУ различных типов, отличающихся по емкости и быстродействию, в общую память ЭВМ. Иерархическая структура ЗУ ЭВМ позволяет сочетать хранение большого объема информации с быстрым доступом к ней в процессе её обработки, что способствует повышению производительности вычислительных систем.

ИЕРАРХИЧЕСКАЯ ОРГАНИЗАЦИЯ ПАМЯТИ Характеристики ЗУ антагонистичны и зависят от типа используемых запоминающих элементов. Стоимость Время доступа ЭСЛ ТТЛШ МОП МЛ МД ПЗС, ЦМД МД МЛ Время доступа МОП ТТЛШ ЭСЛ Ёмкость Иерархическая структура памяти предполагает объединение ЗУ различных типов, отличающихся по емкости и быстродействию, в общую память ЭВМ. Иерархическая структура ЗУ ЭВМ позволяет сочетать хранение большого объема информации с быстрым доступом к ней в процессе её обработки, что способствует повышению производительности вычислительных систем.

ИЕРАРХИЧЕСКАЯ ОРГАНИЗАЦИЯ ПАМЯТИ Иерархия объединения различных типов памяти в ЭВМ: КЭШ Регистры Местная СОЗУ память Основная память Внешняя память Архив Регистры ОУ РОНы ОЗУ, ПЗУ, БЗУ НМД, НМЛ, ЗУЦМД, ЗУПЗС Такая структура памяти ЭВМ, представляющая собой последовательную цепочку различных по характеристикам ЗУ по которым в процессе решения задачи осуществляется перемещение информации позволяет совместить требования большой ёмкости с высоким быстродействием близким к быстродействию ЗУ верхнего уровня иерархии.

ИЕРАРХИЧЕСКАЯ ОРГАНИЗАЦИЯ ПАМЯТИ Иерархия объединения различных типов памяти в ЭВМ: КЭШ Регистры Местная СОЗУ память Основная память Внешняя память Архив Регистры ОУ РОНы ОЗУ, ПЗУ, БЗУ НМД, НМЛ, ЗУЦМД, ЗУПЗС Такая структура памяти ЭВМ, представляющая собой последовательную цепочку различных по характеристикам ЗУ по которым в процессе решения задачи осуществляется перемещение информации позволяет совместить требования большой ёмкости с высоким быстродействием близким к быстродействию ЗУ верхнего уровня иерархии.

КЛАССИФИКАЦИЯ ЗУ • • По специфике использования в ЭВМ - ЗУ со сменой информации в процессе работы СОЗУ, ВЗУ - ЗУ без смены информации - ЗУ с медленной сменой информации По способу размещения и поиску информации - адресные - безадресные а) ассоциативные б) стековые • По способу обращения к ячейке памяти - ЗУ с произвольным обращением - ЗУ с последовательным обращением а) периодические (циклические) б) апериодические

КЛАССИФИКАЦИЯ ЗУ • • По специфике использования в ЭВМ - ЗУ со сменой информации в процессе работы СОЗУ, ВЗУ - ЗУ без смены информации - ЗУ с медленной сменой информации По способу размещения и поиску информации - адресные - безадресные а) ассоциативные б) стековые • По способу обращения к ячейке памяти - ЗУ с произвольным обращением - ЗУ с последовательным обращением а) периодические (циклические) б) апериодические

ОПЕРАТИВНЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА Общие принципы организации ОЗУ: Элемент физической среды, использующийся для хранения единицы информации именуется элементом памяти (ЭП) или запоминающим элементом (ЗЭ). Элементы памяти объединяются в ячейки памяти (ЯП), служащие для хранения машинного слова определенной длины. Количество двоичных разрядов, которое можно разместить в ЯП, называется разрядностью памяти. Ячейки памяти объединяются в конструктивную единицу, называемую блоком памяти (БП). В каждый момент времени обращение может производиться только к одной ячейке памяти. По классификации приведенной выше ОЗУ относится к: - ЗУ со сменой информации в процессе работы - адресным ЗУ - ЗУ с произвольным доступом

ОПЕРАТИВНЫЕ ЗАПОМИНАЮЩИЕ УСТРОЙСТВА Общие принципы организации ОЗУ: Элемент физической среды, использующийся для хранения единицы информации именуется элементом памяти (ЭП) или запоминающим элементом (ЗЭ). Элементы памяти объединяются в ячейки памяти (ЯП), служащие для хранения машинного слова определенной длины. Количество двоичных разрядов, которое можно разместить в ЯП, называется разрядностью памяти. Ячейки памяти объединяются в конструктивную единицу, называемую блоком памяти (БП). В каждый момент времени обращение может производиться только к одной ячейке памяти. По классификации приведенной выше ОЗУ относится к: - ЗУ со сменой информации в процессе работы - адресным ЗУ - ЗУ с произвольным доступом

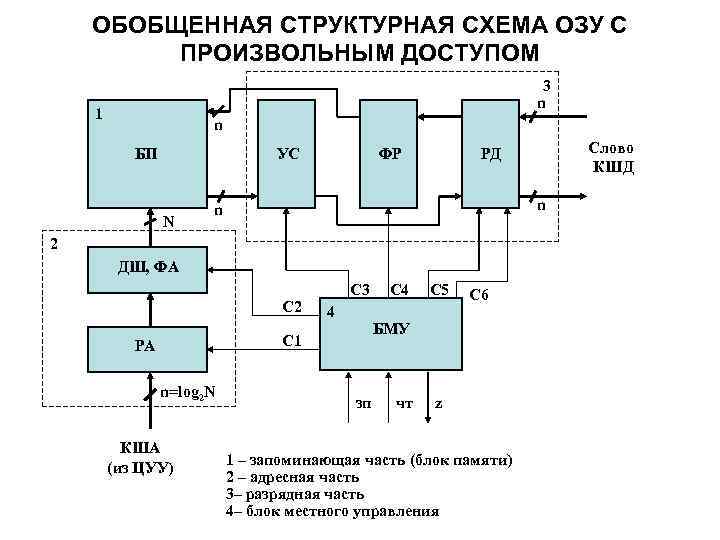

ОБОБЩЕННАЯ СТРУКТУРНАЯ СХЕМА ОЗУ С ПРОИЗВОЛЬНЫМ ДОСТУПОМ 3 n 1 n БП УС N ФР n n 2 ДШ, ФА C 2 C 3 4 n=log 2 N КША (из ЦУУ) C 4 C 5 C 6 БМУ C 1 РА Слово КШД РД зп чт z 1 – запоминающая часть (блок памяти) 2 – адресная часть 3– разрядная часть 4– блок местного управления

ОБОБЩЕННАЯ СТРУКТУРНАЯ СХЕМА ОЗУ С ПРОИЗВОЛЬНЫМ ДОСТУПОМ 3 n 1 n БП УС N ФР n n 2 ДШ, ФА C 2 C 3 4 n=log 2 N КША (из ЦУУ) C 4 C 5 C 6 БМУ C 1 РА Слово КШД РД зп чт z 1 – запоминающая часть (блок памяти) 2 – адресная часть 3– разрядная часть 4– блок местного управления

Процессы организации записи и чтения памяти с произвольным доступом Запись: КША РА ДШ, ФА БП КШД Чтение: РД ФР КША РА ДШ, ФА УС ФР КШД РС БП

Процессы организации записи и чтения памяти с произвольным доступом Запись: КША РА ДШ, ФА БП КШД Чтение: РД ФР КША РА ДШ, ФА УС ФР КШД РС БП

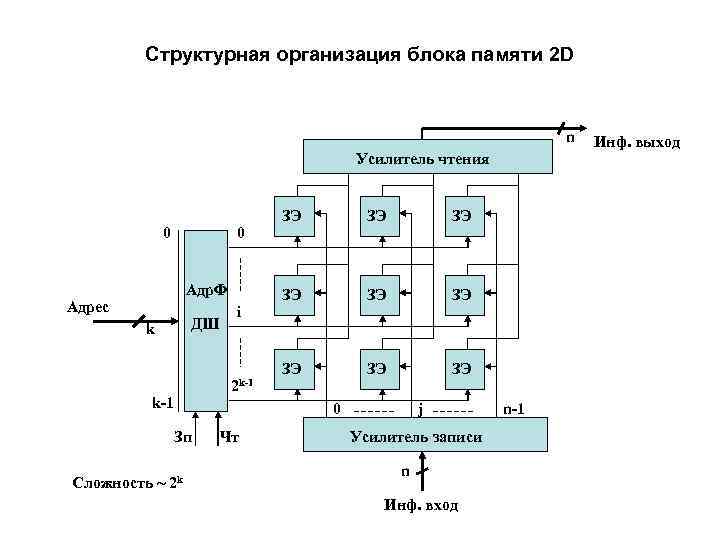

Структурная организация блока памяти 2 D n Усилитель чтения 0 0 Адр. Ф Адрес ДШ k i 2 k-1 ЗЭ ЗЭ ЗЭ 0 Зп Сложность ~ 2 k Чт j Усилитель записи n Инф. вход n-1 Инф. выход

Структурная организация блока памяти 2 D n Усилитель чтения 0 0 Адр. Ф Адрес ДШ k i 2 k-1 ЗЭ ЗЭ ЗЭ 0 Зп Сложность ~ 2 k Чт j Усилитель записи n Инф. вход n-1 Инф. выход

Структурная организация блока памяти 3 D n Усилитель чтения 0 j Инф. выход n-1 ЗЭ А д р Ф 1 Адрес i' ЗЭ ЗЭ ЗЭ 0 ЗЭ ЗЭ ЗЭ (k-1)/2 -1 Зп Сложность ~ 2√ 2 k j i'' Чт Адр. Ф 2 (k-1)/2 Усилитель записи k-1 0 Адрес n-1 Инф. вход n

Структурная организация блока памяти 3 D n Усилитель чтения 0 j Инф. выход n-1 ЗЭ А д р Ф 1 Адрес i' ЗЭ ЗЭ ЗЭ 0 ЗЭ ЗЭ ЗЭ (k-1)/2 -1 Зп Сложность ~ 2√ 2 k j i'' Чт Адр. Ф 2 (k-1)/2 Усилитель записи k-1 0 Адрес n-1 Инф. вход n

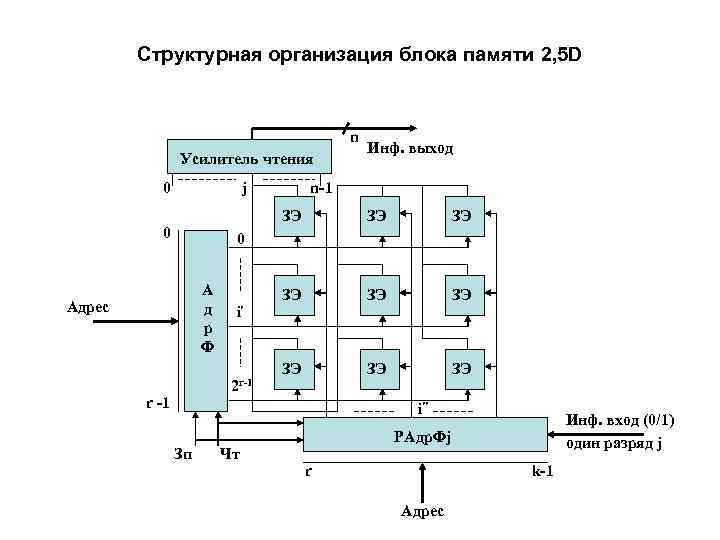

Структурная организация блока памяти 2, 5 D n Усилитель чтения 0 j Инф. выход n-1 ЗЭ 0 ЗЭ ЗЭ 0 А д р Ф Адрес i' 2 r-1 r -1 i'' Зп Чт Инф. вход (0/1) один разряд j РАдр. Фj r k-1 Адрес

Структурная организация блока памяти 2, 5 D n Усилитель чтения 0 j Инф. выход n-1 ЗЭ 0 ЗЭ ЗЭ 0 А д р Ф Адрес i' 2 r-1 r -1 i'' Зп Чт Инф. вход (0/1) один разряд j РАдр. Фj r k-1 Адрес

Структура n-разрядной памяти 2, 5 D n Адрес (0÷r-1) j ЗМ 0 ЗМJ РАдр. Фj РАдр. Фn-1 0 Адрес (r ÷ k-1) Инф. выход ЗМn-1 РАдр. Ф 0 Ус чт n-1 j n-1 n Инф. вход

Структура n-разрядной памяти 2, 5 D n Адрес (0÷r-1) j ЗМ 0 ЗМJ РАдр. Фj РАдр. Фn-1 0 Адрес (r ÷ k-1) Инф. выход ЗМn-1 РАдр. Ф 0 Ус чт n-1 j n-1 n Инф. вход

Структурная организация блока памяти 2 DМ 0 Адрес 0 Адр. Ф (0÷r) r-1 i' 2 r-1 ЗЭ ЗЭ ЗЭ i'' Обр Инф. вход РАдр. Коммутатор Чт/Зп r k-1 Адрес (r÷k-1) Инф. выход

Структурная организация блока памяти 2 DМ 0 Адрес 0 Адр. Ф (0÷r) r-1 i' 2 r-1 ЗЭ ЗЭ ЗЭ i'' Обр Инф. вход РАдр. Коммутатор Чт/Зп r k-1 Адрес (r÷k-1) Инф. выход

Классификация ОЗУ по области применения 1. ОЗУ средней емкости умеренного быстродействия 2. ОЗУ высокого быстродействия 3. ОЗУ большой емкости

Классификация ОЗУ по области применения 1. ОЗУ средней емкости умеренного быстродействия 2. ОЗУ высокого быстродействия 3. ОЗУ большой емкости

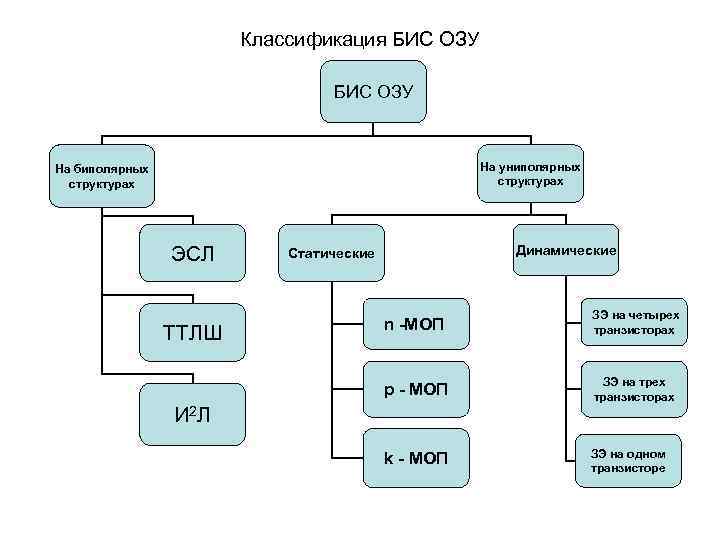

Классификация БИС ОЗУ На униполярных структурах На биполярных структурах ЭСЛ Динамические Статические ЗЭ на четырех транзисторах p - МОП ТТЛШ n -МОП ЗЭ на трех транзисторах k - МОП ЗЭ на одном транзисторе И 2 Л

Классификация БИС ОЗУ На униполярных структурах На биполярных структурах ЭСЛ Динамические Статические ЗЭ на четырех транзисторах p - МОП ТТЛШ n -МОП ЗЭ на трех транзисторах k - МОП ЗЭ на одном транзисторе И 2 Л

Быстродействие статической памяти ЭСЛ – 2, 7 – 15 нсек ТТЛ - 35 – 100 нсек И 2 Л – 100 – 200 нсек n – МОП - 25 – 300 нсек K - МОП - 25 - 200 нсек Арсенид Галлия - 1, 7 - 4, 5 нсек Атомарная технология (переходы Джозефсона) - 10 псек

Быстродействие статической памяти ЭСЛ – 2, 7 – 15 нсек ТТЛ - 35 – 100 нсек И 2 Л – 100 – 200 нсек n – МОП - 25 – 300 нсек K - МОП - 25 - 200 нсек Арсенид Галлия - 1, 7 - 4, 5 нсек Атомарная технология (переходы Джозефсона) - 10 псек

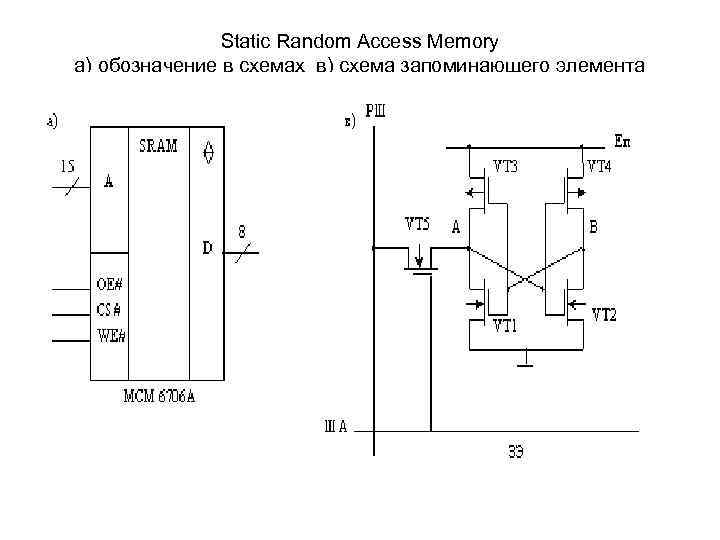

Static Random Access Memory а) обозначение в схемах в) схема запоминающего элемента

Static Random Access Memory а) обозначение в схемах в) схема запоминающего элемента

Static Random Access Memory б) структура СБИС г) временные диаграммы чтения и записи

Static Random Access Memory б) структура СБИС г) временные диаграммы чтения и записи

Обозначение в функциональных схемах DRAM

Обозначение в функциональных схемах DRAM

Структурная схема СБИС DRAM

Структурная схема СБИС DRAM

Dynamic Random Access Memory

Dynamic Random Access Memory

Временные диаграммы работы DRAM

Временные диаграммы работы DRAM

Организация регенерации 1. Авторегенерация в процессе чтения 2. Распределенная регенерация ( период разбивается на кванты tрф=Tрф/N 1 и за каждый квант проводится регенерация одной строки) 3. Пакетная регенерация ( в каждый период Tрф сначала производится регенерация всех строк ~100 мкс, а остальное время отводится для выполнения считывания и записей) Регенерация может отличаться способом формирования адресной строки и протоколом взаимодействия контроллера памяти и СБИС DRAM 1. ROR (RAS only Refresh) счетчик адреса расположен в контроллере памяти, а временная диаграмма отличается отсутствием адреса столбца, строба CAS и сигналов в шине данных 2. CBR (CAS Before RAS) счетчик адреса строки размещен внутри СБИС, а контроллер памяти формирует вначале сигнал CAS, а затем RAS 3. Скрытая регенерация (hidden refresh) при этом в конце полезного цикла записи или чтения сигнал CAS удерживается в активном состоянии, а RAS переводится в пассивное. Затем RAS становится активным при уже активном CAS, что и инициирует выполнение регенерации по схеме CBR

Организация регенерации 1. Авторегенерация в процессе чтения 2. Распределенная регенерация ( период разбивается на кванты tрф=Tрф/N 1 и за каждый квант проводится регенерация одной строки) 3. Пакетная регенерация ( в каждый период Tрф сначала производится регенерация всех строк ~100 мкс, а остальное время отводится для выполнения считывания и записей) Регенерация может отличаться способом формирования адресной строки и протоколом взаимодействия контроллера памяти и СБИС DRAM 1. ROR (RAS only Refresh) счетчик адреса расположен в контроллере памяти, а временная диаграмма отличается отсутствием адреса столбца, строба CAS и сигналов в шине данных 2. CBR (CAS Before RAS) счетчик адреса строки размещен внутри СБИС, а контроллер памяти формирует вначале сигнал CAS, а затем RAS 3. Скрытая регенерация (hidden refresh) при этом в конце полезного цикла записи или чтения сигнал CAS удерживается в активном состоянии, а RAS переводится в пассивное. Затем RAS становится активным при уже активном CAS, что и инициирует выполнение регенерации по схеме CBR

Рост быстродействия памяти и процессоров

Рост быстродействия памяти и процессоров

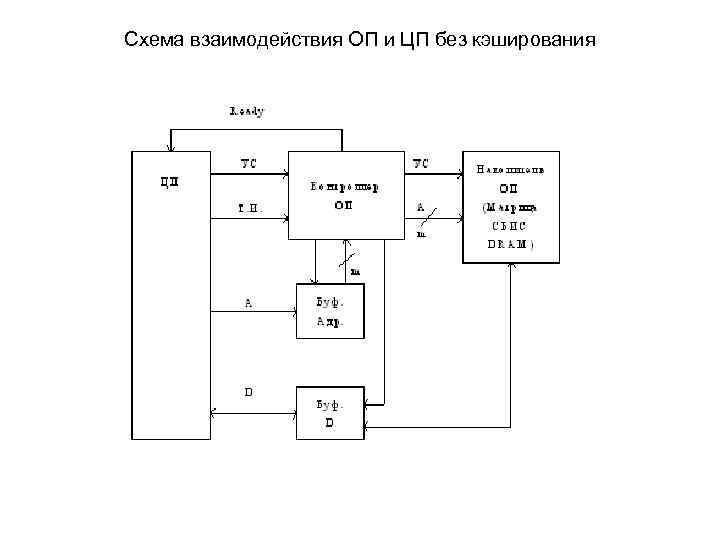

Схема взаимодействия ОП и ЦП без кэширования

Схема взаимодействия ОП и ЦП без кэширования

Схема взаимодействия ЦП и ОП с кэшированием

Схема взаимодействия ЦП и ОП с кэшированием

Структура ОП с пакетным доступом с использованием чередования банков

Структура ОП с пакетным доступом с использованием чередования банков

Структура ОП с конвейерным доступом с использованием чередования банков

Структура ОП с конвейерным доступом с использованием чередования банков

Архитектурные особенности СБИС DRAM высокого быстродействия FPM (Fast Page Mode) Ускорение доступа к последовательности слов данных, расположенных в одной строке матрицы. Здесь используются групповые операции обмена, а оценка осуществляется по количеству тактов, требуемых для чтения блока данных из четырех слов. Считывание строки производится только один раз. Использование режима FPM не требует каких-либо изменений в самой СБИС, изменяется протокол обмена и, следовательно, контроллер ОП.

Архитектурные особенности СБИС DRAM высокого быстродействия FPM (Fast Page Mode) Ускорение доступа к последовательности слов данных, расположенных в одной строке матрицы. Здесь используются групповые операции обмена, а оценка осуществляется по количеству тактов, требуемых для чтения блока данных из четырех слов. Считывание строки производится только один раз. Использование режима FPM не требует каких-либо изменений в самой СБИС, изменяется протокол обмена и, следовательно, контроллер ОП.

EDO DRAM (Extended Data Out) В тракт передачи данных в СБИС включен дополнительно регистр защелка. Данные на внешних выводах СБИС остаются неизменными до появления следующего строба CAS. Это позволяет передавать данные по системной шине и во время пауз между стробирующими импульсами CAS, что уплотняет передачу данных пакета по шине и уменьшает период следования импульсов CAS. Режим EDO требует изменения в структуре СБИС.

EDO DRAM (Extended Data Out) В тракт передачи данных в СБИС включен дополнительно регистр защелка. Данные на внешних выводах СБИС остаются неизменными до появления следующего строба CAS. Это позволяет передавать данные по системной шине и во время пауз между стробирующими импульсами CAS, что уплотняет передачу данных пакета по шине и уменьшает период следования импульсов CAS. Режим EDO требует изменения в структуре СБИС.

BEDO DRAM (Burst) Дополнительно вводится счетчик адреса столбца для пакетного цикла. Это уменьшает внешние обмены СБИС – адрес столбца передается в счетчик только в начале пакетного цикла (С 1 и С 5). Поток данных по шине уплотнен. Импульсы CAS поступают в ускоренном темпе. Ослабленная зависимость от системного окружения позволяет реализовать конвейерный режим работы СБИС. Внешне это проявляется в более быстром темпе следования данных и некотором отставании потока данных от потока импульсов CAS.

BEDO DRAM (Burst) Дополнительно вводится счетчик адреса столбца для пакетного цикла. Это уменьшает внешние обмены СБИС – адрес столбца передается в счетчик только в начале пакетного цикла (С 1 и С 5). Поток данных по шине уплотнен. Импульсы CAS поступают в ускоренном темпе. Ослабленная зависимость от системного окружения позволяет реализовать конвейерный режим работы СБИС. Внешне это проявляется в более быстром темпе следования данных и некотором отставании потока данных от потока импульсов CAS.

SDRAM – синхронная динамическая память • • • Синхронизирована с частотой шины без тактов ожидания внутри пакетного цикла Выполнена по Би. КМОП технологии Быстродействие характеризуется вектором 5 -1 -1 -1 при тактовой частоте шины 100 МГц и выше Имеет внутренний пакетный счетчик, используемый для инкрементного увеличения адреса столбца в режиме пакетного обращения. Это позволяет инициировать новое обращение к SDRAM памяти до завершения предыдущего Использует конвейеризацию тракта продвижения информации в цикле обращения к СБИС Применяет организацию накопителя из m банков с чередованием банков

SDRAM – синхронная динамическая память • • • Синхронизирована с частотой шины без тактов ожидания внутри пакетного цикла Выполнена по Би. КМОП технологии Быстродействие характеризуется вектором 5 -1 -1 -1 при тактовой частоте шины 100 МГц и выше Имеет внутренний пакетный счетчик, используемый для инкрементного увеличения адреса столбца в режиме пакетного обращения. Это позволяет инициировать новое обращение к SDRAM памяти до завершения предыдущего Использует конвейеризацию тракта продвижения информации в цикле обращения к СБИС Применяет организацию накопителя из m банков с чередованием банков

DDRDRAM (Double Data Rate) – память с удвоенной скоростью передачи • • • Передача данных осуществляется по фронту и срезу тактовых импульсов, чем достигается удвоение скорости передачи при той же тактовой частоте Позволяет выполнить две операции доступа к данным из двух разных модулей, находящихся в одном банке памяти за время одного обращения стандартной SDRAM. Это есть дальнейшее развитие принципа чередования данных для увеличения скорости доступа к ним Пропускная способность для DDR составляет 1, 6 Гбайт/сек • DDR 2 – в ней размер выборки данных увеличен в 2 раза. Передается 32 байта за такт, что обеспечивает пропускную способность на частоте 150 МГц – 4, 8 Гбайт/сек, а на частоте 200 МГц – 6, 4 Гбайт/сек. Отличается более низким напряжением питания – 1, 8 в • Сейчас начинается переход на DDR 3

DDRDRAM (Double Data Rate) – память с удвоенной скоростью передачи • • • Передача данных осуществляется по фронту и срезу тактовых импульсов, чем достигается удвоение скорости передачи при той же тактовой частоте Позволяет выполнить две операции доступа к данным из двух разных модулей, находящихся в одном банке памяти за время одного обращения стандартной SDRAM. Это есть дальнейшее развитие принципа чередования данных для увеличения скорости доступа к ним Пропускная способность для DDR составляет 1, 6 Гбайт/сек • DDR 2 – в ней размер выборки данных увеличен в 2 раза. Передается 32 байта за такт, что обеспечивает пропускную способность на частоте 150 МГц – 4, 8 Гбайт/сек, а на частоте 200 МГц – 6, 4 Гбайт/сек. Отличается более низким напряжением питания – 1, 8 в • Сейчас начинается переход на DDR 3

RDRAM (Rambus) • • Технология Rambus основана на высокоскоростном интерфейсе с последовательной передачей байтов, для чего разработан новый интерфейс Rambus Channel, содержащий 13 линий. Протокол обмена по интерфейсу включает последовательно выполняемые три фазы: пакет запросов в СБИС, пакет подтверждения от СБИС, пакет данных. Синхронизация осуществляется как по фронту так и по спаду тактового импульса. Пропускная способность достигает 600 Гбайт/сек RDRAM эффективна при выполнении графических и мультимедийных приложений, для которых характерен обмен большими пакетами данных. При обмене отдельными словами такие СБИС совершенно неэффективны.

RDRAM (Rambus) • • Технология Rambus основана на высокоскоростном интерфейсе с последовательной передачей байтов, для чего разработан новый интерфейс Rambus Channel, содержащий 13 линий. Протокол обмена по интерфейсу включает последовательно выполняемые три фазы: пакет запросов в СБИС, пакет подтверждения от СБИС, пакет данных. Синхронизация осуществляется как по фронту так и по спаду тактового импульса. Пропускная способность достигает 600 Гбайт/сек RDRAM эффективна при выполнении графических и мультимедийных приложений, для которых характерен обмен большими пакетами данных. При обмене отдельными словами такие СБИС совершенно неэффективны.

Смешанная память • CDRAM (Cashed) – разработка фирмы Mitsubishi. Внутри кристалла памяти на каждые 16 Мбит встраивается 16 Кбит КЭШ памяти. Обмен между ними осуществляется 128 разрядными словами • EDRAM (Enhanced) – разработка фирмы Ramtron. Внутри кристалла памяти на каждые 4 Мбит встраивается 8 Кбит КЭШ памяти. Обмен между ними осуществляется 2048 -разрядными словами • Использование этой памяти позволяет отказаться от КЭШ второго уровня

Смешанная память • CDRAM (Cashed) – разработка фирмы Mitsubishi. Внутри кристалла памяти на каждые 16 Мбит встраивается 16 Кбит КЭШ памяти. Обмен между ними осуществляется 128 разрядными словами • EDRAM (Enhanced) – разработка фирмы Ramtron. Внутри кристалла памяти на каждые 4 Мбит встраивается 8 Кбит КЭШ памяти. Обмен между ними осуществляется 2048 -разрядными словами • Использование этой памяти позволяет отказаться от КЭШ второго уровня

Организация ОЗУ с многоканальным доступом Память ресурсы которой распределяются между несколькими потребителями (каналами), называется памятью с многоканальным доступом. Пусть λ 1, λ 2, … , λm сигналы запроса от 1, 2, …, m каналов, причем 1 -ый канал имеет высший приоритет, а m-ый –низший p 1 p 2… , pm – сигналы разрешения доступа к памяти 1… m каналам соответственно, тогда а) имеется запрос λk pk=1 если б) нет запросов более высокого приоритета λ 1… λk-1 в) не начато обслуживание каналов k+1… m, т. е. pk+1=pk+2=… =pm в общем случае: pk=λ 1λ 2… λk-1λkpk+1 pk+2… pm В случае четырехканального доступа к ОЗУ имеем: p 1=λ 1 p 2 p 3 p 4 p 2=λ 1λ 2 p 3 p 4 p 3=λ 1λ 2λ 3 p 4 p 4=λ 1λ 2λ 3λ 4

Организация ОЗУ с многоканальным доступом Память ресурсы которой распределяются между несколькими потребителями (каналами), называется памятью с многоканальным доступом. Пусть λ 1, λ 2, … , λm сигналы запроса от 1, 2, …, m каналов, причем 1 -ый канал имеет высший приоритет, а m-ый –низший p 1 p 2… , pm – сигналы разрешения доступа к памяти 1… m каналам соответственно, тогда а) имеется запрос λk pk=1 если б) нет запросов более высокого приоритета λ 1… λk-1 в) не начато обслуживание каналов k+1… m, т. е. pk+1=pk+2=… =pm в общем случае: pk=λ 1λ 2… λk-1λkpk+1 pk+2… pm В случае четырехканального доступа к ОЗУ имеем: p 1=λ 1 p 2 p 3 p 4 p 2=λ 1λ 2 p 3 p 4 p 3=λ 1λ 2λ 3 p 4 p 4=λ 1λ 2λ 3λ 4

Организация ОЗУ с многоканальным доступом Л 1 λ 1 p 1 Л 2 λ 2 Л 3 λ 3 Л 4 λ 4 p 2 p 3 p 4

Организация ОЗУ с многоканальным доступом Л 1 λ 1 p 1 Л 2 λ 2 Л 3 λ 3 Л 4 λ 4 p 2 p 3 p 4

Классификация БИС ПЗУ

Классификация БИС ПЗУ

СБИС ПЗУ масочного типа с технологией ROM (условное обозначение и структурная схема)

СБИС ПЗУ масочного типа с технологией ROM (условное обозначение и структурная схема)

СБИС ПЗУ масочного типа с технологией ROM (матрица ЗЭ с диодами и матрица с n-МОП транзисторами)

СБИС ПЗУ масочного типа с технологией ROM (матрица ЗЭ с диодами и матрица с n-МОП транзисторами)

СБИС ППЗУ с технологией PROM

СБИС ППЗУ с технологией PROM

Построение СБИС ПЗУ с технологией EPROM

Построение СБИС ПЗУ с технологией EPROM

Принципы работы ЛИПЗМОП-транзистора а) эквивалентная схема участка исток-сток при Uз=0 б) инжекция заряда в ПЗ при записи в) вольт-амперные характеристики

Принципы работы ЛИПЗМОП-транзистора а) эквивалентная схема участка исток-сток при Uз=0 б) инжекция заряда в ПЗ при записи в) вольт-амперные характеристики

Построение СБИС ПЗУ с технологией EEPROM а) эквивалентная схема б) вольт-амперная характеристика

Построение СБИС ПЗУ с технологией EEPROM а) эквивалентная схема б) вольт-амперная характеристика

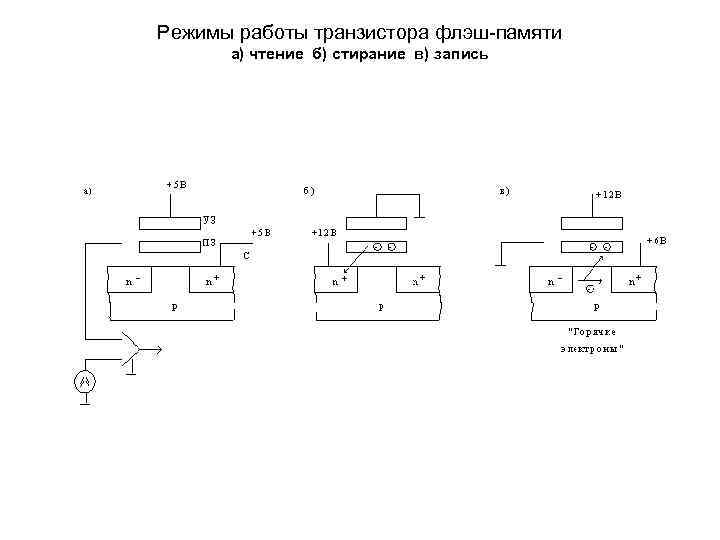

Режимы работы транзистора флэш-памяти а) чтение б) стирание в) запись

Режимы работы транзистора флэш-памяти а) чтение б) стирание в) запись

Матрица ЗЭ флэш-памяти

Матрица ЗЭ флэш-памяти

Программируемая логическая матрица (ПЛМ)

Программируемая логическая матрица (ПЛМ)

Классификация СОЗУ по методу поиска • Ассоциативные • С прямой адресацией • Стековые

Классификация СОЗУ по методу поиска • Ассоциативные • С прямой адресацией • Стековые

Обобщенная схема поиска информации в АСОЗУ

Обобщенная схема поиска информации в АСОЗУ

Организация АСОЗУ

Организация АСОЗУ

Стратегии удаления слов, потерявших активность

Стратегии удаления слов, потерявших активность

Функциональная схема использования АСОЗУ в процессоре

Функциональная схема использования АСОЗУ в процессоре

Алгоритм обслуживания обращений к АСОЗУ

Алгоритм обслуживания обращений к АСОЗУ

Оценка эффективности использования АСОЗУ в процессоре

Оценка эффективности использования АСОЗУ в процессоре

Зависимость организационного коэффициента от размера АСОЗУ

Зависимость организационного коэффициента от размера АСОЗУ

Полностью ассоциативный КЭШ

Полностью ассоциативный КЭШ

КЭШ с прямым отображением

КЭШ с прямым отображением

Двухканальный множественно-ассоциативный КЭШ

Двухканальный множественно-ассоциативный КЭШ

Количественный расчет параметров КЭШ для различных способов его организации Для всех примеров: ОЗУ 16 Мбайт, кэш 64 Кбайт, блока 16 байт Для полностью ассоциативного КЭШ В КЭШе помещается 216/24 = 212 = 4096 блоков В ОЗУ помещается 224/24 = 220 = 1048576 блоков Для КЭШ с прямым обращением В КЭШ помещается 216/24 = 212 = 4096 блоков Количество областей ОЗУ 224/216 = 28 = 256 Для частично ассоциативной (двухканальной) КЭШ разбивается на два подкэш по 32 Кбайт, каждый из которых содержит 215/24 = 211 = 2048 блоков Количество областей ОЗУ 224/215 = 29 = 512

Количественный расчет параметров КЭШ для различных способов его организации Для всех примеров: ОЗУ 16 Мбайт, кэш 64 Кбайт, блока 16 байт Для полностью ассоциативного КЭШ В КЭШе помещается 216/24 = 212 = 4096 блоков В ОЗУ помещается 224/24 = 220 = 1048576 блоков Для КЭШ с прямым обращением В КЭШ помещается 216/24 = 212 = 4096 блоков Количество областей ОЗУ 224/216 = 28 = 256 Для частично ассоциативной (двухканальной) КЭШ разбивается на два подкэш по 32 Кбайт, каждый из которых содержит 215/24 = 211 = 2048 блоков Количество областей ОЗУ 224/215 = 29 = 512

СПОСОБЫ ПОДДЕРЖАНИЯ ЦЕЛОСТНОСТИ ДАННЫХ В КЭШ • Сквозная запись • Буферированная сквозная запись • Обратная запись

СПОСОБЫ ПОДДЕРЖАНИЯ ЦЕЛОСТНОСТИ ДАННЫХ В КЭШ • Сквозная запись • Буферированная сквозная запись • Обратная запись

Организация СОЗУ с прямой адресацией Швых n R 1 1 Швх n R 2 1 n Rm 1 DA ОЗУ 1 1 m k зап чт k RA ОЗУ 1 адрес

Организация СОЗУ с прямой адресацией Швых n R 1 1 Швх n R 2 1 n Rm 1 DA ОЗУ 1 1 m k зап чт k RA ОЗУ 1 адрес

Функциональная схема использования СОЗУ с прямой адресацией в процессоре

Функциональная схема использования СОЗУ с прямой адресацией в процессоре

Оценка эффективности использования СОЗУ с прямой адресацией в процессоре

Оценка эффективности использования СОЗУ с прямой адресацией в процессоре

Организация стекового СОЗУ

Организация стекового СОЗУ

Функциональная схема использования стекового СОЗУ в процессоре

Функциональная схема использования стекового СОЗУ в процессоре

Особенности использования стекового СОЗУ

Особенности использования стекового СОЗУ

Оценка эффективности использования стекового СОЗУ в процессоре

Оценка эффективности использования стекового СОЗУ в процессоре