RTL-презентация.pptx

- Количество слайдов: 31

Языки моделирования уровня RTL (Register Translate Level) или языки описания архитектуры Такие языка позволяют производить высокоточное моделирование вычислительных средств и их документирование. Они обеспечивают «транспортабельность» проекта между различными группами разработчиков. Их можно использовать для доказательства работоспособности вычислительного модуля. Представители: VHDL – язык моделирование на основе языка Паскаль Verilog – языка моделирования на основе языка Си HHDL, ISP, UDL/I

Языки моделирования уровня RTL (Register Translate Level) или языки описания архитектуры Такие языка позволяют производить высокоточное моделирование вычислительных средств и их документирование. Они обеспечивают «транспортабельность» проекта между различными группами разработчиков. Их можно использовать для доказательства работоспособности вычислительного модуля. Представители: VHDL – язык моделирование на основе языка Паскаль Verilog – языка моделирования на основе языка Си HHDL, ISP, UDL/I

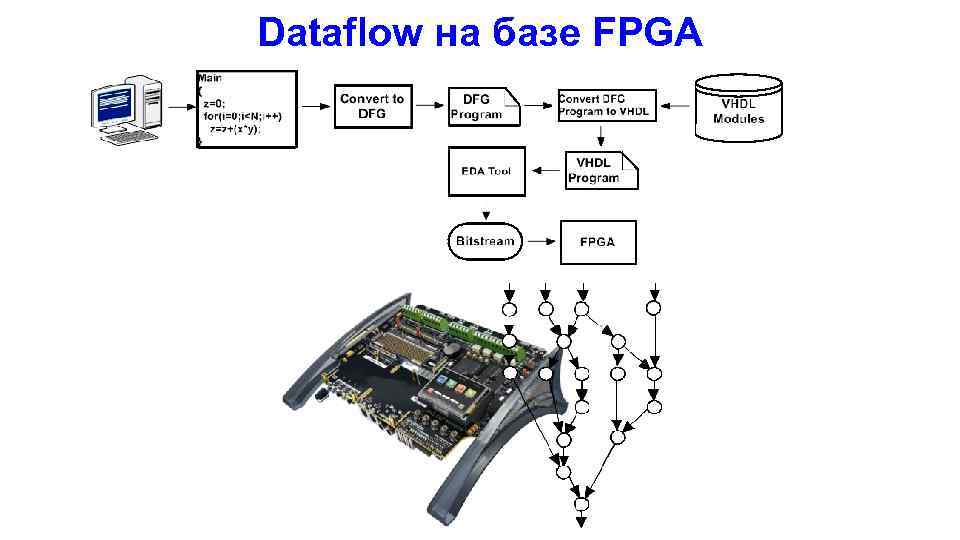

Dataflow на базе FPGA

Dataflow на базе FPGA

История VHDL был создан по инициативе Министерства обороны США, которое с 1983 г. финансировало данную разработку. Первоначально язык был создан для обеспечения обмена проектами между группами разработчиков схем. Однако затем язык вырос до уровня описания схем. В августе 1985 г. была выпущена версия 7. 2 языка VHDL, представляющая собой вполне законченный язык. В декабре 1987 г. официально был утвержден в качестве стандарта язык IEEE Standard 1076 VHDL.

История VHDL был создан по инициативе Министерства обороны США, которое с 1983 г. финансировало данную разработку. Первоначально язык был создан для обеспечения обмена проектами между группами разработчиков схем. Однако затем язык вырос до уровня описания схем. В августе 1985 г. была выпущена версия 7. 2 языка VHDL, представляющая собой вполне законченный язык. В декабре 1987 г. официально был утвержден в качестве стандарта язык IEEE Standard 1076 VHDL.

Язык VHDL Основные термины VHDL: Объект (entity) – описание компоненты системы, имеющий входы и выходы. Объектом может быть вся системе, один компонент системы, устройство, логический элемент и т. п. Один объект может являться частью другого объекта, таким образом можно организовывать вложенные системы. Объект состоит как минимум из описаний интерфейса и одного или нескольких архитектурных тел. Интерфейс (Entity_declaration) служит для описания входов и выходов объекта. Архитектурное тело (architecture_bidy) – описание поведения объекта Объявление конфигурации (configuration_declaration) – перечисление всех объектов, которые составляют объект. Пакет объединяет в себе часто используемые константы, процедуры, функции и т. д. Их интерфейсы описываются в объявлении пакета, а тела содержатся в тебе пакета.

Язык VHDL Основные термины VHDL: Объект (entity) – описание компоненты системы, имеющий входы и выходы. Объектом может быть вся системе, один компонент системы, устройство, логический элемент и т. п. Один объект может являться частью другого объекта, таким образом можно организовывать вложенные системы. Объект состоит как минимум из описаний интерфейса и одного или нескольких архитектурных тел. Интерфейс (Entity_declaration) служит для описания входов и выходов объекта. Архитектурное тело (architecture_bidy) – описание поведения объекта Объявление конфигурации (configuration_declaration) – перечисление всех объектов, которые составляют объект. Пакет объединяет в себе часто используемые константы, процедуры, функции и т. д. Их интерфейсы описываются в объявлении пакета, а тела содержатся в тебе пакета.

Язык VHDL В языке VHDL существует три класса объектов: - Константы (не изменяются); constant Toff : MVL : =„ 1‟; - переменные (изменяются с помощью команды присваивания) – удобны для алгоритмического описания поведения объекта. variable Pri : boolean : = FALSE; - сигналы (изменяются с помощью оператора назначения сигнала). A <= B+C after 50 ns; Создание объекта происходит при его объявлении: variable Pri : boolean : = FALSE;

Язык VHDL В языке VHDL существует три класса объектов: - Константы (не изменяются); constant Toff : MVL : =„ 1‟; - переменные (изменяются с помощью команды присваивания) – удобны для алгоритмического описания поведения объекта. variable Pri : boolean : = FALSE; - сигналы (изменяются с помощью оператора назначения сигнала). A <= B+C after 50 ns; Создание объекта происходит при его объявлении: variable Pri : boolean : = FALSE;

Объект проектирования VHDL Основное понятие VHDL – объект проектирования (ОПр). ОПр состоит из четырех частей: 1. Entity_declaration – интерфейс служит для описания входов и выходов объекта. 2. Architecture_body Архитектурное тело – описание поведения объекта Поддерживается три вида описания архитектуры аппаратного обеспечения : 1. structural description – описание в виде иерархической структуры взаимосвязанных компонент. 2. data flow description – архитектура представляет собой множество параллельных операторов присваивания, каждый из которых может находиться под управлением тактового сигнала; 3. behavioral description – поведенческое описание, представленное в виде последовательной (императивной) программы. Все три стиля могут самостоятельно или совместно использоваться при проектировании архитектуры вычислительных средств.

Объект проектирования VHDL Основное понятие VHDL – объект проектирования (ОПр). ОПр состоит из четырех частей: 1. Entity_declaration – интерфейс служит для описания входов и выходов объекта. 2. Architecture_body Архитектурное тело – описание поведения объекта Поддерживается три вида описания архитектуры аппаратного обеспечения : 1. structural description – описание в виде иерархической структуры взаимосвязанных компонент. 2. data flow description – архитектура представляет собой множество параллельных операторов присваивания, каждый из которых может находиться под управлением тактового сигнала; 3. behavioral description – поведенческое описание, представленное в виде последовательной (императивной) программы. Все три стиля могут самостоятельно или совместно использоваться при проектировании архитектуры вычислительных средств.

Язык VHDL Основные термины VHDL: Объект (entity) – описание компоненты системы, имеющий входы и выходы. Объектом может быть вся системе, один компонент системы, устройство, логический элемент и т. п. Один объект может являться частью другого объекта, таким образом можно организовывать вложенные системы. Объект состоит как минимум из описаний интерфейса и одного или нескольких архитектурных тел. Интерфейс (Entity_declaration) служит для описания входов и выходов объекта. Архитектурное тело (architecture_bidy) – описание поведения объекта Объявление конфигурации (configuration_declaration) – перечисление всех объектов, которые составляют объект. Пакет объединяет в себе часто используемые константы, процедуры, функции и т. д. Их интерфейсы описываются в объявлении пакета, а тела содержатся в тебе пакета. Модуль проекта (design_unit) – все возможные описания объектов Библиотека модулей (library_unit) Файл модуля (design_file) – файл в который сохранено описание объекта

Язык VHDL Основные термины VHDL: Объект (entity) – описание компоненты системы, имеющий входы и выходы. Объектом может быть вся системе, один компонент системы, устройство, логический элемент и т. п. Один объект может являться частью другого объекта, таким образом можно организовывать вложенные системы. Объект состоит как минимум из описаний интерфейса и одного или нескольких архитектурных тел. Интерфейс (Entity_declaration) служит для описания входов и выходов объекта. Архитектурное тело (architecture_bidy) – описание поведения объекта Объявление конфигурации (configuration_declaration) – перечисление всех объектов, которые составляют объект. Пакет объединяет в себе часто используемые константы, процедуры, функции и т. д. Их интерфейсы описываются в объявлении пакета, а тела содержатся в тебе пакета. Модуль проекта (design_unit) – все возможные описания объектов Библиотека модулей (library_unit) Файл модуля (design_file) – файл в который сохранено описание объекта

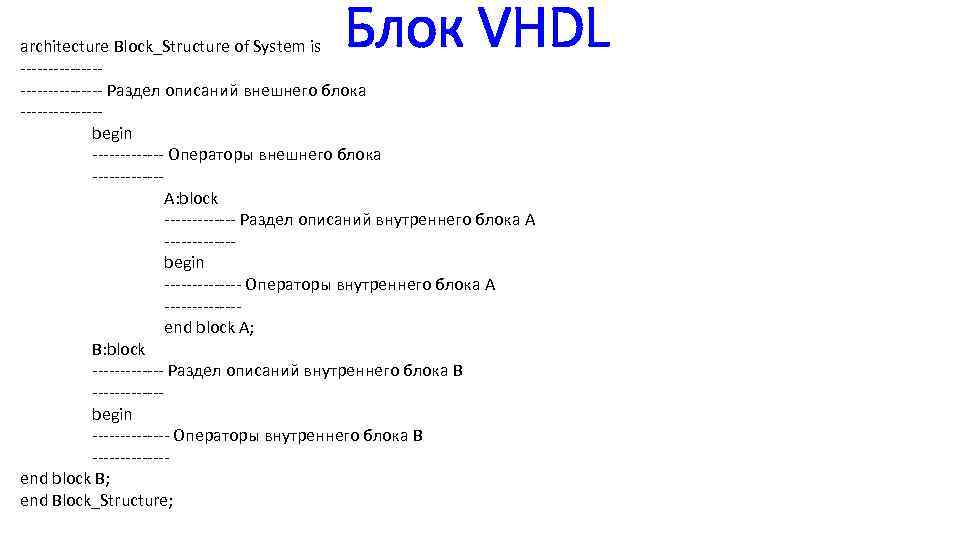

Блок VHDL Блок – это определенный фрагмент текста, состоящий из раздела описания и исполняемого раздела. Таким образом, архитектурное тело само является блоком и в свою очередь может состоять из ряда блоков более низкого уровня и т. д. в соответствии с иерархией структуры. Блочная структура служит для организации у ОПр иерархической структуры.

Блок VHDL Блок – это определенный фрагмент текста, состоящий из раздела описания и исполняемого раздела. Таким образом, архитектурное тело само является блоком и в свою очередь может состоять из ряда блоков более низкого уровня и т. д. в соответствии с иерархией структуры. Блочная структура служит для организации у ОПр иерархической структуры.

Блок VHDL architecture Block_Structure of System is --------------- Раздел описаний внешнего блока -------begin ------- Операторы внешнего блока ------A: block ------- Раздел описаний внутреннего блока А ------begin ------- Операторы внутреннего блока А -------end block A; B: block ------- Раздел описаний внутреннего блока B ------begin ------- Операторы внутреннего блока B -------end block B; end Block_Structure;

Блок VHDL architecture Block_Structure of System is --------------- Раздел описаний внешнего блока -------begin ------- Операторы внешнего блока ------A: block ------- Раздел описаний внутреннего блока А ------begin ------- Операторы внутреннего блока А -------end block A; B: block ------- Раздел описаний внутреннего блока B ------begin ------- Операторы внутреннего блока B -------end block B; end Block_Structure;

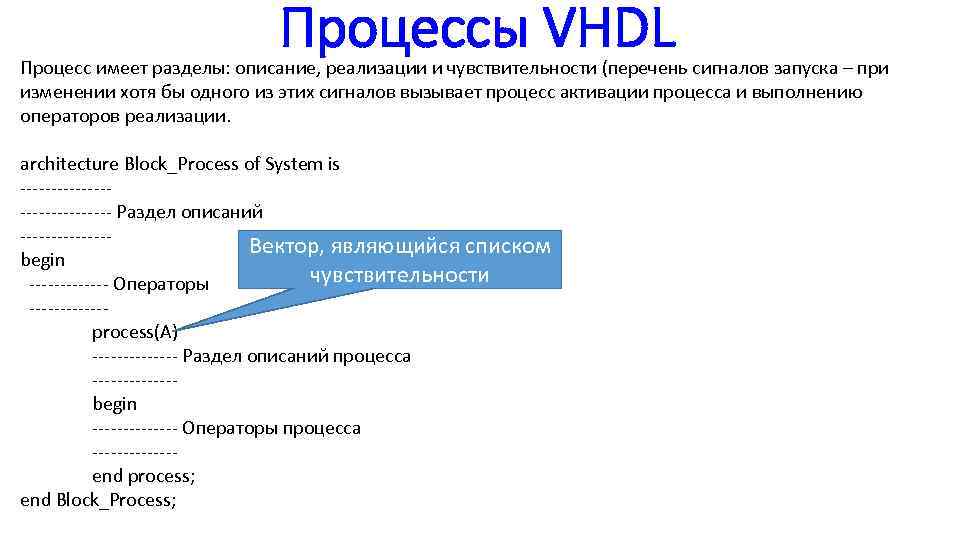

Процессы VHDL Процесс имеет разделы: описание, реализации и чувствительности (перечень сигналов запуска – при изменении хотя бы одного из этих сигналов вызывает процесс активации процесса и выполнению операторов реализации. architecture Block_Process of System is --------------- Раздел описаний -------Вектор, являющийся списком begin чувствительности ------- Операторы ------process(A) ------- Раздел описаний процесса -------begin ------- Операторы процесса -------end process; end Block_Process;

Процессы VHDL Процесс имеет разделы: описание, реализации и чувствительности (перечень сигналов запуска – при изменении хотя бы одного из этих сигналов вызывает процесс активации процесса и выполнению операторов реализации. architecture Block_Process of System is --------------- Раздел описаний -------Вектор, являющийся списком begin чувствительности ------- Операторы ------process(A) ------- Раздел описаний процесса -------begin ------- Операторы процесса -------end process; end Block_Process;

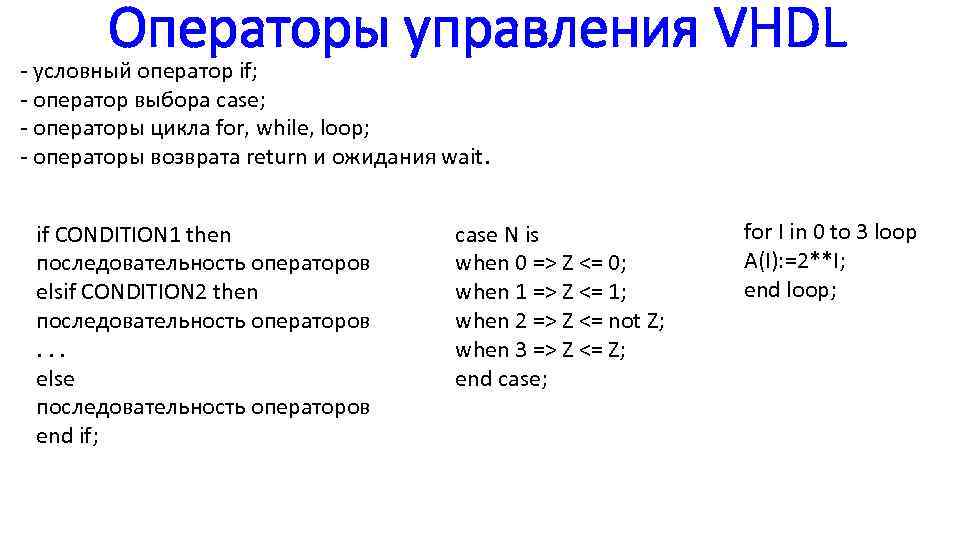

Операторы управления VHDL - условный оператор if; - оператор выбора case; - операторы цикла for, while, loop; - операторы возврата return и ожидания wait. if CONDITION 1 then последовательность операторов elsif CONDITION 2 then последовательность операторов. . . else последовательность операторов end if; case N is when 0 => Z <= 0; when 1 => Z <= 1; when 2 => Z <= not Z; when 3 => Z <= Z; end case; for I in 0 to 3 loop A(I): =2**I; end loop;

Операторы управления VHDL - условный оператор if; - оператор выбора case; - операторы цикла for, while, loop; - операторы возврата return и ожидания wait. if CONDITION 1 then последовательность операторов elsif CONDITION 2 then последовательность операторов. . . else последовательность операторов end if; case N is when 0 => Z <= 0; when 1 => Z <= 1; when 2 => Z <= not Z; when 3 => Z <= Z; end case; for I in 0 to 3 loop A(I): =2**I; end loop;

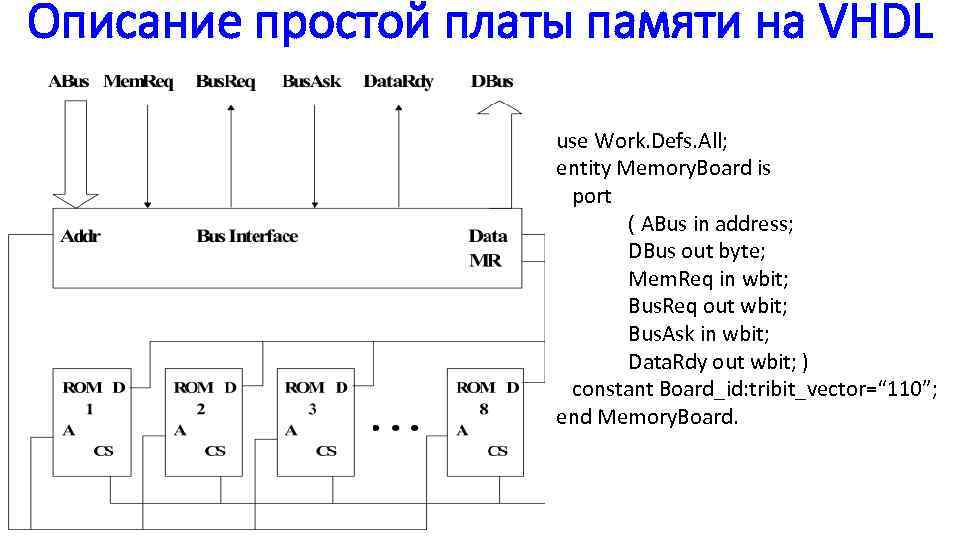

Описание простой платы памяти на VHDL use Work. Defs. All; entity Memory. Board is port ( ABus in address; DBus out byte; Mem. Req in wbit; Bus. Req out wbit; Bus. Ask in wbit; Data. Rdy out wbit; ) constant Board_id: tribit_vector=“ 110”; end Memory. Board.

Описание простой платы памяти на VHDL use Work. Defs. All; entity Memory. Board is port ( ABus in address; DBus out byte; Mem. Req in wbit; Bus. Req out wbit; Bus. Ask in wbit; Data. Rdy out wbit; ) constant Board_id: tribit_vector=“ 110”; end Memory. Board.

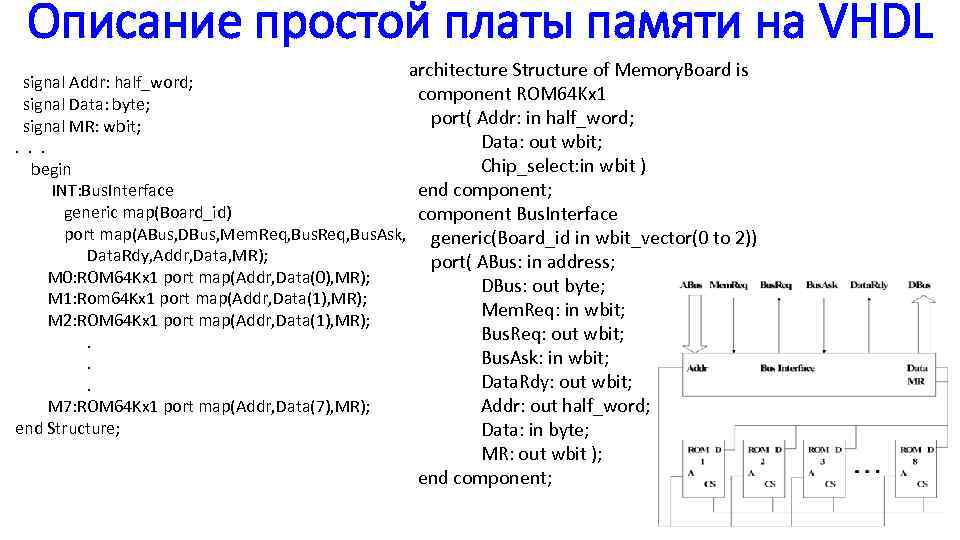

Описание простой платы памяти на VHDL architecture Structure of Memory. Board is signal Addr: half_word; component ROM 64 Kx 1 signal Data: byte; port( Addr: in half_word; signal MR: wbit; Data: out wbit; . . . Chip_select: in wbit ) begin end component; INT: Bus. Interface generic map(Board_id) component Bus. Interface port map(ABus, DBus, Mem. Req, Bus. Ask, generic(Board_id in wbit_vector(0 to 2)) Data. Rdy, Addr, Data, MR); port( ABus: in address; M 0: ROM 64 Kx 1 port map(Addr, Data(0), MR); DBus: out byte; M 1: Rom 64 Kx 1 port map(Addr, Data(1), MR); Mem. Req: in wbit; M 2: ROM 64 Kx 1 port map(Addr, Data(1), MR); Bus. Req: out wbit; . Bus. Ask: in wbit; . Data. Rdy: out wbit; . Addr: out half_word; M 7: ROM 64 Kx 1 port map(Addr, Data(7), MR); end Structure; Data: in byte; MR: out wbit ); end component;

Описание простой платы памяти на VHDL architecture Structure of Memory. Board is signal Addr: half_word; component ROM 64 Kx 1 signal Data: byte; port( Addr: in half_word; signal MR: wbit; Data: out wbit; . . . Chip_select: in wbit ) begin end component; INT: Bus. Interface generic map(Board_id) component Bus. Interface port map(ABus, DBus, Mem. Req, Bus. Ask, generic(Board_id in wbit_vector(0 to 2)) Data. Rdy, Addr, Data, MR); port( ABus: in address; M 0: ROM 64 Kx 1 port map(Addr, Data(0), MR); DBus: out byte; M 1: Rom 64 Kx 1 port map(Addr, Data(1), MR); Mem. Req: in wbit; M 2: ROM 64 Kx 1 port map(Addr, Data(1), MR); Bus. Req: out wbit; . Bus. Ask: in wbit; . Data. Rdy: out wbit; . Addr: out half_word; M 7: ROM 64 Kx 1 port map(Addr, Data(7), MR); end Structure; Data: in byte; MR: out wbit ); end component;

Описание простой платы памяти на VHDL Если одинаковые имена появляются в port map у двух экземпляров различных компонент, тогда эти порты компонент считаются соединенными вместе. Вместо полного перебора компонент памяти (см. рис. 4) можно использовать следующее описание: ROMarray: for j in 0 to 7 generate M: ROM 64 Kx 1 port map(Addr, Data(j), MR); end generate;

Описание простой платы памяти на VHDL Если одинаковые имена появляются в port map у двух экземпляров различных компонент, тогда эти порты компонент считаются соединенными вместе. Вместо полного перебора компонент памяти (см. рис. 4) можно использовать следующее описание: ROMarray: for j in 0 to 7 generate M: ROM 64 Kx 1 port map(Addr, Data(j), MR); end generate;

Описание компонентов в стиле потоков данных (data-flow) на VHDL Данный метод подчеркивает потока информации между памятью и обрабатывающими элементами. Этот поток управляется и направляется при помощи устройств управления, которые логически отделены от маршрутов данных.

Описание компонентов в стиле потоков данных (data-flow) на VHDL Данный метод подчеркивает потока информации между памятью и обрабатывающими элементами. Этот поток управляется и направляется при помощи устройств управления, которые логически отделены от маршрутов данных.

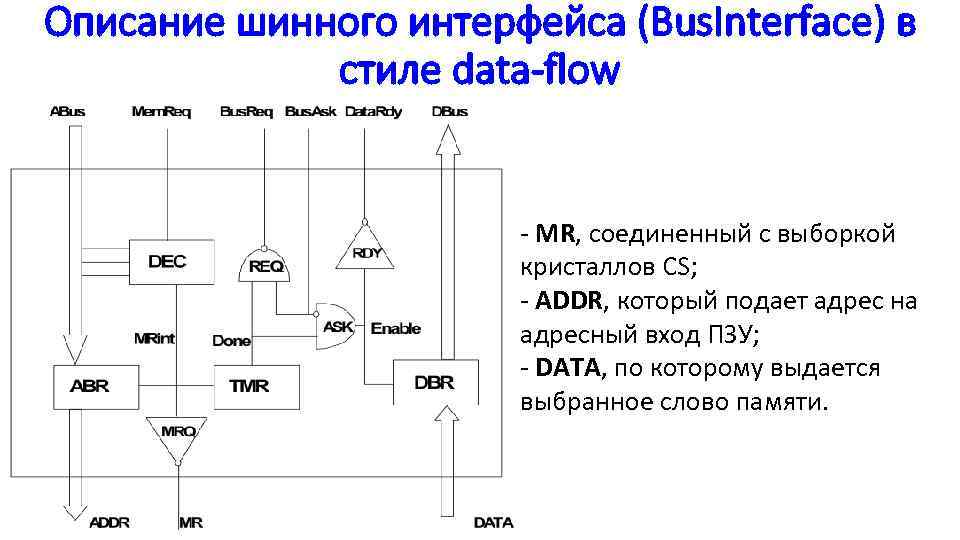

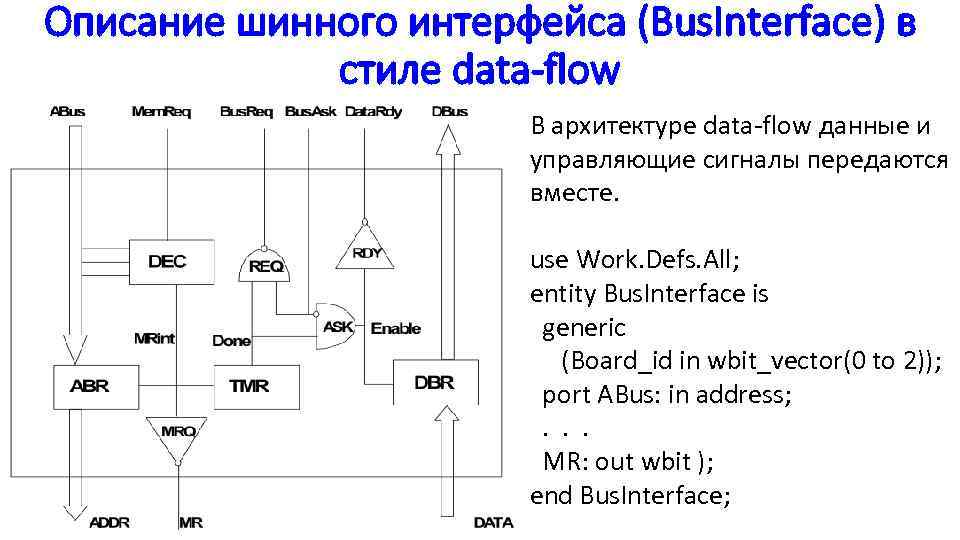

Описание шинного интерфейса (Bus. Interface) в стиле data-flow - MR, соединенный с выборкой кристаллов CS; - ADDR, который подает адрес на адресный вход ПЗУ; - DATA, по которому выдается выбранное слово памяти.

Описание шинного интерфейса (Bus. Interface) в стиле data-flow - MR, соединенный с выборкой кристаллов CS; - ADDR, который подает адрес на адресный вход ПЗУ; - DATA, по которому выдается выбранное слово памяти.

Описание шинного интерфейса (Bus. Interface) в стиле data-flow В архитектуре data-flow данные и управляющие сигналы передаются вместе. use Work. Defs. All; entity Bus. Interface is generic (Board_id in wbit_vector(0 to 2)); port ABus: in address; . . . MR: out wbit ); end Bus. Interface;

Описание шинного интерфейса (Bus. Interface) в стиле data-flow В архитектуре data-flow данные и управляющие сигналы передаются вместе. use Work. Defs. All; entity Bus. Interface is generic (Board_id in wbit_vector(0 to 2)); port ABus: in address; . . . MR: out wbit ); end Bus. Interface;

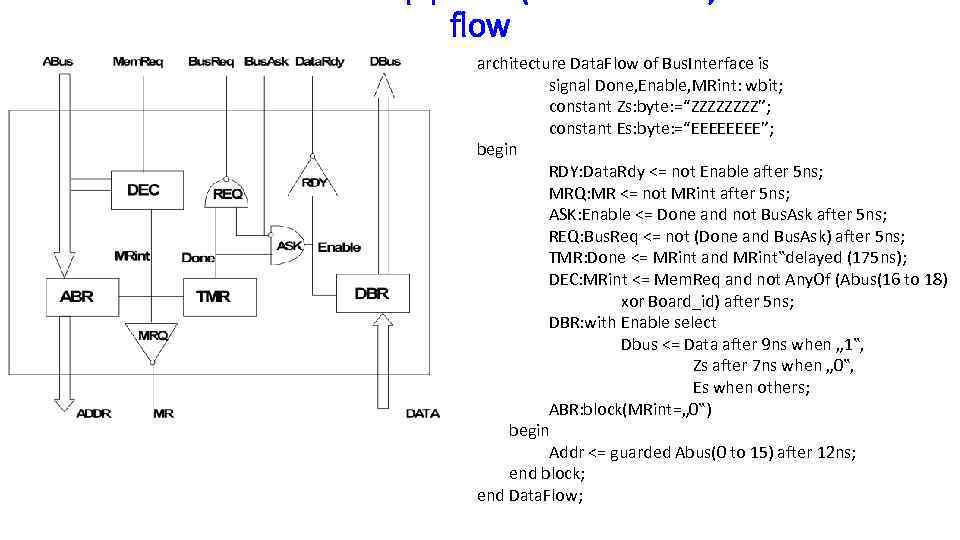

flow architecture Data. Flow of Bus. Interface is signal Done, Enable, MRint: wbit; constant Zs: byte: =“ZZZZ”; constant Es: byte: =“EEEE”; begin RDY: Data. Rdy <= not Enable after 5 ns; MRQ: MR <= not MRint after 5 ns; ASK: Enable <= Done and not Bus. Ask after 5 ns; REQ: Bus. Req <= not (Done and Bus. Ask) after 5 ns; TMR: Done <= MRint and MRint‟delayed (175 ns); DEC: MRint <= Mem. Req and not Any. Of (Abus(16 to 18) xor Board_id) after 5 ns; DBR: with Enable select Dbus <= Data after 9 ns when „ 1‟, Zs after 7 ns when „ 0‟, Es when others; ABR: block(MRint=„ 0‟) begin Addr <= guarded Abus(0 to 15) after 12 ns; end block; end Data. Flow;

flow architecture Data. Flow of Bus. Interface is signal Done, Enable, MRint: wbit; constant Zs: byte: =“ZZZZ”; constant Es: byte: =“EEEE”; begin RDY: Data. Rdy <= not Enable after 5 ns; MRQ: MR <= not MRint after 5 ns; ASK: Enable <= Done and not Bus. Ask after 5 ns; REQ: Bus. Req <= not (Done and Bus. Ask) after 5 ns; TMR: Done <= MRint and MRint‟delayed (175 ns); DEC: MRint <= Mem. Req and not Any. Of (Abus(16 to 18) xor Board_id) after 5 ns; DBR: with Enable select Dbus <= Data after 9 ns when „ 1‟, Zs after 7 ns when „ 0‟, Es when others; ABR: block(MRint=„ 0‟) begin Addr <= guarded Abus(0 to 15) after 12 ns; end block; end Data. Flow;

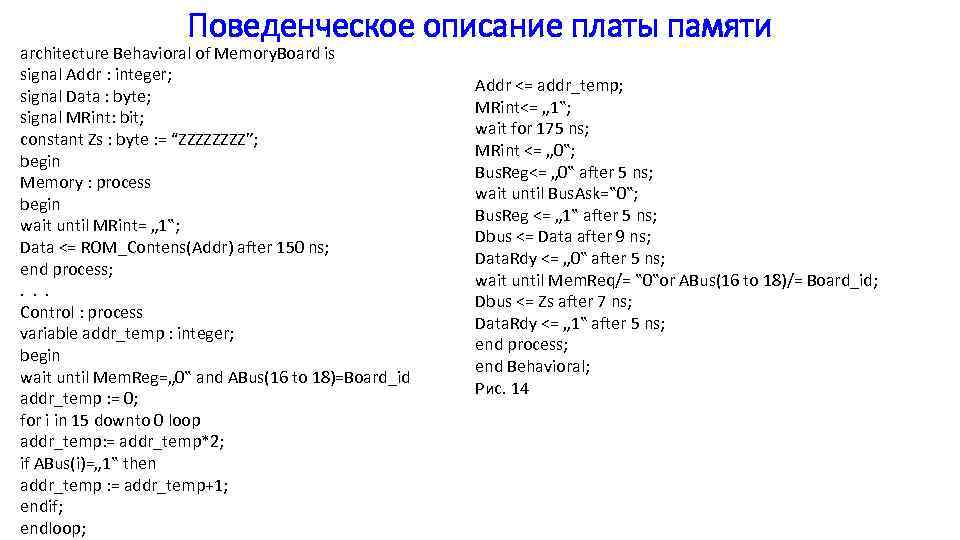

Поведенческое описание платы памяти architecture Behavioral of Memory. Board is signal Addr : integer; signal Data : byte; signal MRint: bit; constant Zs : byte : = “ZZZZ”; begin Memory : process begin wait until MRint= „ 1‟; Data <= ROM_Contens(Addr) after 150 ns; end process; . . . Control : process variable addr_temp : integer; begin wait until Mem. Reg=„ 0‟ and ABus(16 to 18)=Board_id addr_temp : = 0; for i in 15 downto 0 loop addr_temp: = addr_temp*2; if ABus(i)=„ 1‟ then addr_temp : = addr_temp+1; endif; endloop; Addr <= addr_temp; MRint<= „ 1‟; wait for 175 ns; MRint <= „ 0‟; Bus. Reg<= „ 0‟ after 5 ns; wait until Bus. Ask=‟ 0‟; Bus. Reg <= „ 1‟ after 5 ns; Dbus <= Data after 9 ns; Data. Rdy <= „ 0‟ after 5 ns; wait until Mem. Req/= ‟ 0‟or ABus(16 to 18)/= Board_id; Dbus <= Zs after 7 ns; Data. Rdy <= „ 1‟ after 5 ns; end process; end Behavioral; Рис. 14

Поведенческое описание платы памяти architecture Behavioral of Memory. Board is signal Addr : integer; signal Data : byte; signal MRint: bit; constant Zs : byte : = “ZZZZ”; begin Memory : process begin wait until MRint= „ 1‟; Data <= ROM_Contens(Addr) after 150 ns; end process; . . . Control : process variable addr_temp : integer; begin wait until Mem. Reg=„ 0‟ and ABus(16 to 18)=Board_id addr_temp : = 0; for i in 15 downto 0 loop addr_temp: = addr_temp*2; if ABus(i)=„ 1‟ then addr_temp : = addr_temp+1; endif; endloop; Addr <= addr_temp; MRint<= „ 1‟; wait for 175 ns; MRint <= „ 0‟; Bus. Reg<= „ 0‟ after 5 ns; wait until Bus. Ask=‟ 0‟; Bus. Reg <= „ 1‟ after 5 ns; Dbus <= Data after 9 ns; Data. Rdy <= „ 0‟ after 5 ns; wait until Mem. Req/= ‟ 0‟or ABus(16 to 18)/= Board_id; Dbus <= Zs after 7 ns; Data. Rdy <= „ 1‟ after 5 ns; end process; end Behavioral; Рис. 14

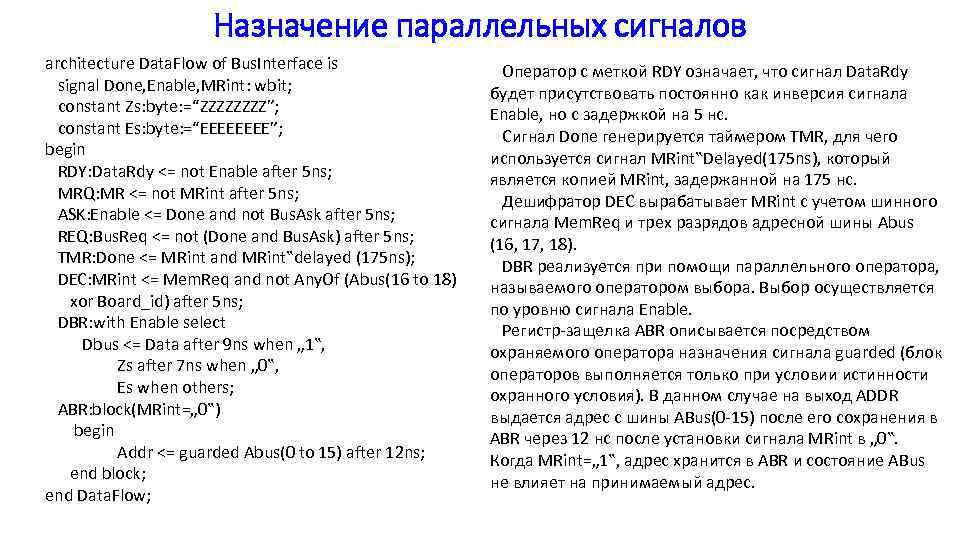

Назначение параллельных сигналов architecture Data. Flow of Bus. Interface is signal Done, Enable, MRint: wbit; constant Zs: byte: =“ZZZZ”; constant Es: byte: =“EEEE”; begin RDY: Data. Rdy <= not Enable after 5 ns; MRQ: MR <= not MRint after 5 ns; ASK: Enable <= Done and not Bus. Ask after 5 ns; REQ: Bus. Req <= not (Done and Bus. Ask) after 5 ns; TMR: Done <= MRint and MRint‟delayed (175 ns); DEC: MRint <= Mem. Req and not Any. Of (Abus(16 to 18) xor Board_id) after 5 ns; DBR: with Enable select Dbus <= Data after 9 ns when „ 1‟, Zs after 7 ns when „ 0‟, Es when others; ABR: block(MRint=„ 0‟) begin Addr <= guarded Abus(0 to 15) after 12 ns; end block; end Data. Flow; Оператор с меткой RDY означает, что сигнал Data. Rdy будет присутствовать постоянно как инверсия сигнала Enable, но с задержкой на 5 нс. Сигнал Done генерируется таймером TMR, для чего используется сигнал MRint‟Delayed(175 ns), который является копией MRint, задержанной на 175 нс. Дешифратор DEC вырабатывает MRint с учетом шинного сигнала Mem. Req и трех разрядов адресной шины Abus (16, 17, 18). DBR реализуется при помощи параллельного оператора, называемого оператором выбора. Выбор осуществляется по уровню сигнала Enable. Регистр-защелка ABR описывается посредством охраняемого оператора назначения сигнала guarded (блок операторов выполняется только при условии истинности охранного условия). В данном случае на выход ADDR выдается адрес с шины ABus(0 -15) после его сохранения в ABR через 12 нс после установки сигнала MRint в „ 0‟. Когда MRint=„ 1‟, адрес хранится в ABR и состояние ABus не влияет на принимаемый адрес.

Назначение параллельных сигналов architecture Data. Flow of Bus. Interface is signal Done, Enable, MRint: wbit; constant Zs: byte: =“ZZZZ”; constant Es: byte: =“EEEE”; begin RDY: Data. Rdy <= not Enable after 5 ns; MRQ: MR <= not MRint after 5 ns; ASK: Enable <= Done and not Bus. Ask after 5 ns; REQ: Bus. Req <= not (Done and Bus. Ask) after 5 ns; TMR: Done <= MRint and MRint‟delayed (175 ns); DEC: MRint <= Mem. Req and not Any. Of (Abus(16 to 18) xor Board_id) after 5 ns; DBR: with Enable select Dbus <= Data after 9 ns when „ 1‟, Zs after 7 ns when „ 0‟, Es when others; ABR: block(MRint=„ 0‟) begin Addr <= guarded Abus(0 to 15) after 12 ns; end block; end Data. Flow; Оператор с меткой RDY означает, что сигнал Data. Rdy будет присутствовать постоянно как инверсия сигнала Enable, но с задержкой на 5 нс. Сигнал Done генерируется таймером TMR, для чего используется сигнал MRint‟Delayed(175 ns), который является копией MRint, задержанной на 175 нс. Дешифратор DEC вырабатывает MRint с учетом шинного сигнала Mem. Req и трех разрядов адресной шины Abus (16, 17, 18). DBR реализуется при помощи параллельного оператора, называемого оператором выбора. Выбор осуществляется по уровню сигнала Enable. Регистр-защелка ABR описывается посредством охраняемого оператора назначения сигнала guarded (блок операторов выполняется только при условии истинности охранного условия). В данном случае на выход ADDR выдается адрес с шины ABus(0 -15) после его сохранения в ABR через 12 нс после установки сигнала MRint в „ 0‟. Когда MRint=„ 1‟, адрес хранится в ABR и состояние ABus не влияет на принимаемый адрес.

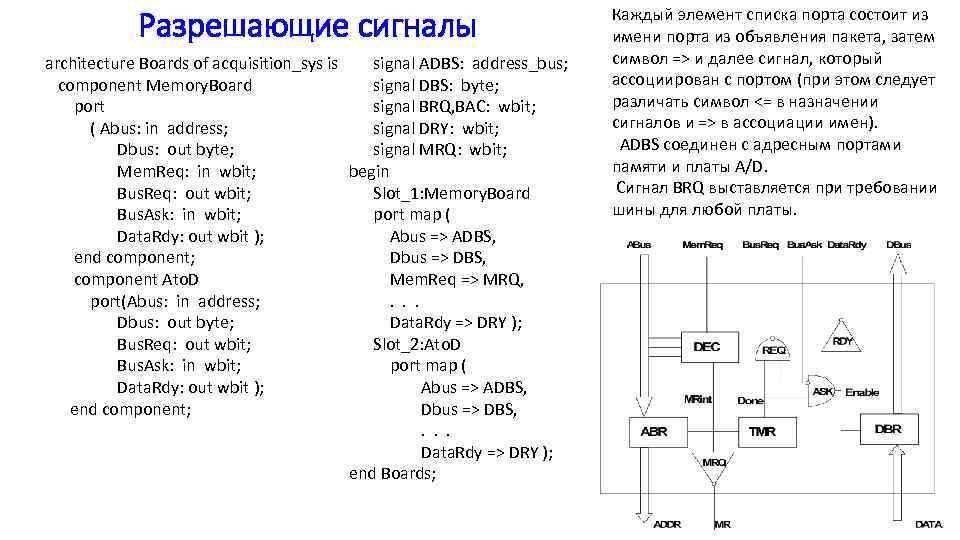

Разрешающие сигналы architecture Boards of acquisition_sys is signal ADBS: address_bus; component Memory. Board signal DBS: byte; port signal BRQ, BAC: wbit; ( Abus: in address; signal DRY: wbit; Dbus: out byte; signal MRQ: wbit; Mem. Req: in wbit; begin Bus. Req: out wbit; Slot_1: Memory. Board Bus. Ask: in wbit; port map ( Data. Rdy: out wbit ); Abus => ADBS, end component; Dbus => DBS, component Ato. D Mem. Req => MRQ, port(Abus: in address; . . . Dbus: out byte; Data. Rdy => DRY ); Bus. Req: out wbit; Slot_2: Ato. D Bus. Ask: in wbit; port map ( Data. Rdy: out wbit ); Abus => ADBS, end component; Dbus => DBS, . . . Data. Rdy => DRY ); end Boards; Каждый элемент списка порта состоит из имени порта из объявления пакета, затем символ => и далее сигнал, который ассоциирован с портом (при этом следует различать символ <= в назначении сигналов и => в ассоциации имен). ADBS соединен с адресным портами памяти и платы A/D. Сигнал BRQ выставляется при требовании шины для любой платы.

Разрешающие сигналы architecture Boards of acquisition_sys is signal ADBS: address_bus; component Memory. Board signal DBS: byte; port signal BRQ, BAC: wbit; ( Abus: in address; signal DRY: wbit; Dbus: out byte; signal MRQ: wbit; Mem. Req: in wbit; begin Bus. Req: out wbit; Slot_1: Memory. Board Bus. Ask: in wbit; port map ( Data. Rdy: out wbit ); Abus => ADBS, end component; Dbus => DBS, component Ato. D Mem. Req => MRQ, port(Abus: in address; . . . Dbus: out byte; Data. Rdy => DRY ); Bus. Req: out wbit; Slot_2: Ato. D Bus. Ask: in wbit; port map ( Data. Rdy: out wbit ); Abus => ADBS, end component; Dbus => DBS, . . . Data. Rdy => DRY ); end Boards; Каждый элемент списка порта состоит из имени порта из объявления пакета, затем символ => и далее сигнал, который ассоциирован с портом (при этом следует различать символ <= в назначении сигналов и => в ассоциации имен). ADBS соединен с адресным портами памяти и платы A/D. Сигнал BRQ выставляется при требовании шины для любой платы.

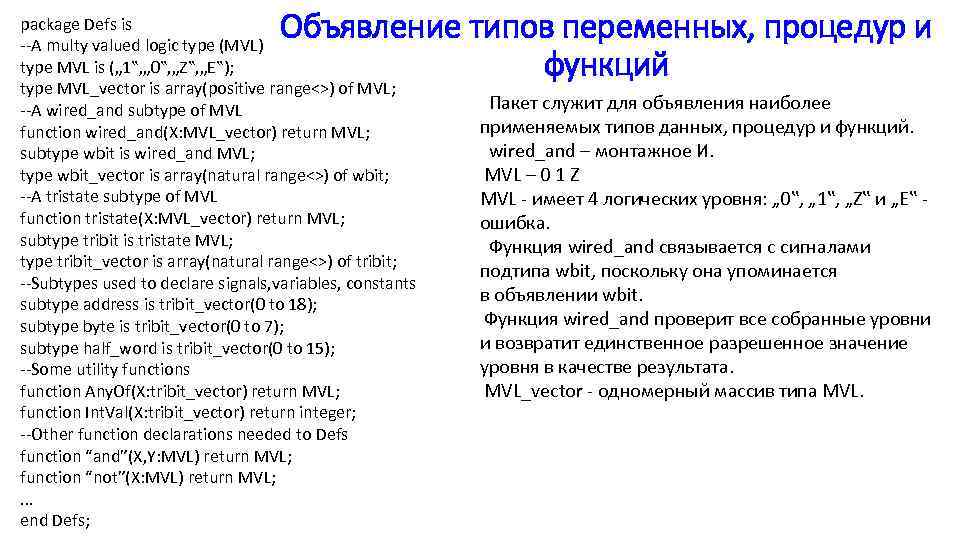

Объявление типов переменных, процедур и функций package Defs is --A multy valued logic type (MVL) type MVL is („ 1‟, „ 0‟, „Z‟, „E‟); type MVL_vector is array(positive range<>) of MVL; --A wired_and subtype of MVL function wired_and(X: MVL_vector) return MVL; subtype wbit is wired_and MVL; type wbit_vector is array(natural range<>) of wbit; --A tristate subtype of MVL function tristate(X: MVL_vector) return MVL; subtype tribit is tristate MVL; type tribit_vector is array(natural range<>) of tribit; --Subtypes used to declare signals, variables, constants subtype address is tribit_vector(0 to 18); subtype byte is tribit_vector(0 to 7); subtype half_word is tribit_vector(0 to 15); --Some utility functions function Any. Of(X: tribit_vector) return MVL; function Int. Val(X: tribit_vector) return integer; --Other function declarations needed to Defs function “and”(X, Y: MVL) return MVL; function “not”(X: MVL) return MVL; . . . end Defs; Пакет служит для объявления наиболее применяемых типов данных, процедур и функций. wired_and – монтажное И. MVL – 0 1 Z MVL - имеет 4 логических уровня: „ 0‟, „ 1‟, „Z‟ и „E‟ ошибка. Функция wired_and связывается с сигналами подтипа wbit, поскольку она упоминается в объявлении wbit. Функция wired_and проверит все собранные уровни и возвратит единственное разрешенное значение уровня в качестве результата. MVL_vector - одномерный массив типа MVL.

Объявление типов переменных, процедур и функций package Defs is --A multy valued logic type (MVL) type MVL is („ 1‟, „ 0‟, „Z‟, „E‟); type MVL_vector is array(positive range<>) of MVL; --A wired_and subtype of MVL function wired_and(X: MVL_vector) return MVL; subtype wbit is wired_and MVL; type wbit_vector is array(natural range<>) of wbit; --A tristate subtype of MVL function tristate(X: MVL_vector) return MVL; subtype tribit is tristate MVL; type tribit_vector is array(natural range<>) of tribit; --Subtypes used to declare signals, variables, constants subtype address is tribit_vector(0 to 18); subtype byte is tribit_vector(0 to 7); subtype half_word is tribit_vector(0 to 15); --Some utility functions function Any. Of(X: tribit_vector) return MVL; function Int. Val(X: tribit_vector) return integer; --Other function declarations needed to Defs function “and”(X, Y: MVL) return MVL; function “not”(X: MVL) return MVL; . . . end Defs; Пакет служит для объявления наиболее применяемых типов данных, процедур и функций. wired_and – монтажное И. MVL – 0 1 Z MVL - имеет 4 логических уровня: „ 0‟, „ 1‟, „Z‟ и „E‟ ошибка. Функция wired_and связывается с сигналами подтипа wbit, поскольку она упоминается в объявлении wbit. Функция wired_and проверит все собранные уровни и возвратит единственное разрешенное значение уровня в качестве результата. MVL_vector - одномерный массив типа MVL.

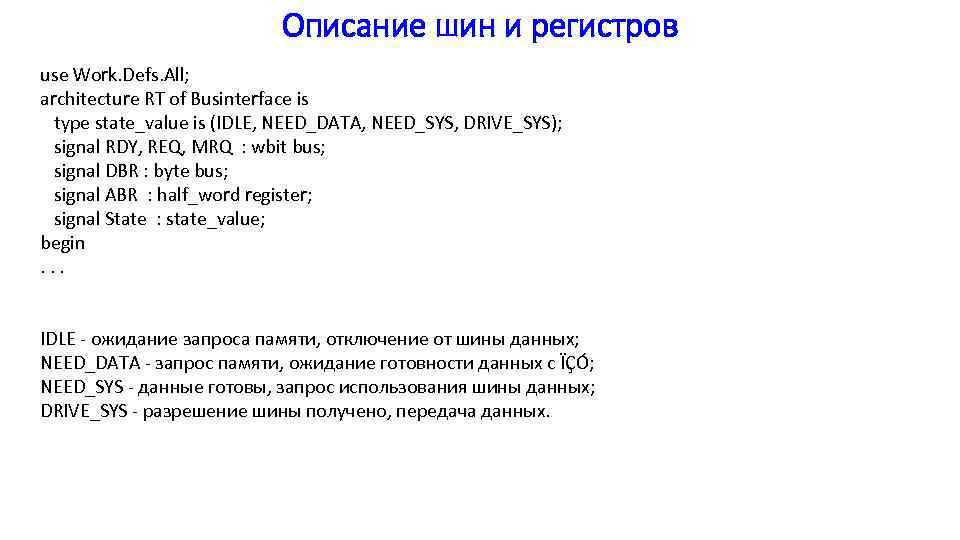

Описание шин и регистров use Work. Defs. All; architecture RT of Businterface is type state_value is (IDLE, NEED_DATA, NEED_SYS, DRIVE_SYS); signal RDY, REQ, MRQ : wbit bus; signal DBR : byte bus; signal ABR : half_word register; signal State : state_value; begin. . . IDLE - ожидание запроса памяти, отключение от шины данных; NEED_DATA - запрос памяти, ожидание готовности данных с ÏÇÓ; NEED_SYS - данные готовы, запрос использования шины данных; DRIVE_SYS - разрешение шины получено, передача данных.

Описание шин и регистров use Work. Defs. All; architecture RT of Businterface is type state_value is (IDLE, NEED_DATA, NEED_SYS, DRIVE_SYS); signal RDY, REQ, MRQ : wbit bus; signal DBR : byte bus; signal ABR : half_word register; signal State : state_value; begin. . . IDLE - ожидание запроса памяти, отключение от шины данных; NEED_DATA - запрос памяти, ожидание готовности данных с ÏÇÓ; NEED_SYS - данные готовы, запрос использования шины данных; DRIVE_SYS - разрешение шины получено, передача данных.

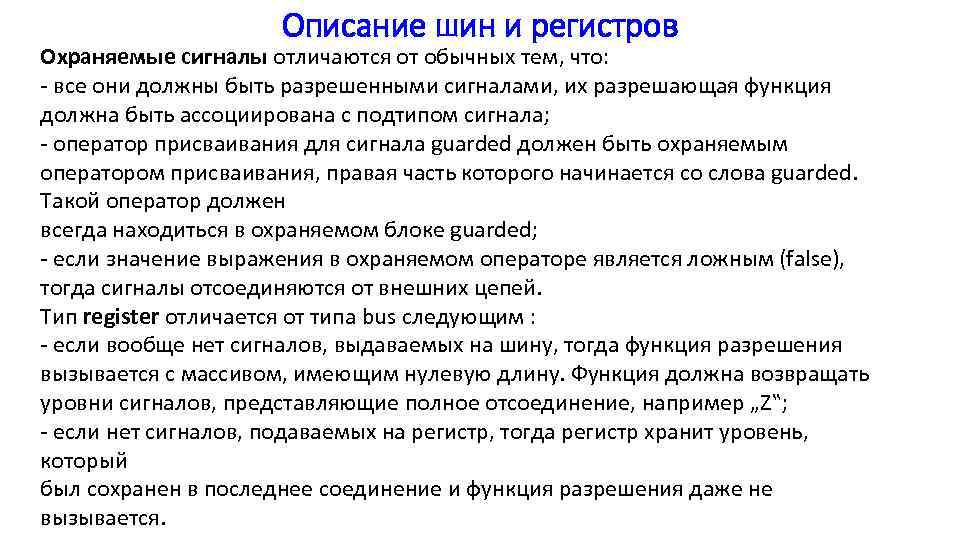

Описание шин и регистров Охраняемые сигналы отличаются от обычных тем, что: - все они должны быть разрешенными сигналами, их разрешающая функция должна быть ассоциирована с подтипом сигнала; - оператор присваивания для сигнала guarded должен быть охраняемым оператором присваивания, правая часть которого начинается со слова guarded. Такой оператор должен всегда находиться в охраняемом блоке guarded; - если значение выражения в охраняемом операторе является ложным (false), тогда сигналы отсоединяются от внешних цепей. Тип register отличается от типа bus следующим : - если вообще нет сигналов, выдаваемых на шину, тогда функция разрешения вызывается с массивом, имеющим нулевую длину. Функция должна возвращать уровни сигналов, представляющие полное отсоединение, например „Z‟; - если нет сигналов, подаваемых на регистр, тогда регистр хранит уровень, который был сохранен в последнее соединение и функция разрешения даже не вызывается.

Описание шин и регистров Охраняемые сигналы отличаются от обычных тем, что: - все они должны быть разрешенными сигналами, их разрешающая функция должна быть ассоциирована с подтипом сигнала; - оператор присваивания для сигнала guarded должен быть охраняемым оператором присваивания, правая часть которого начинается со слова guarded. Такой оператор должен всегда находиться в охраняемом блоке guarded; - если значение выражения в охраняемом операторе является ложным (false), тогда сигналы отсоединяются от внешних цепей. Тип register отличается от типа bus следующим : - если вообще нет сигналов, выдаваемых на шину, тогда функция разрешения вызывается с массивом, имеющим нулевую длину. Функция должна возвращать уровни сигналов, представляющие полное отсоединение, например „Z‟; - если нет сигналов, подаваемых на регистр, тогда регистр хранит уровень, который был сохранен в последнее соединение и функция разрешения даже не вызывается.

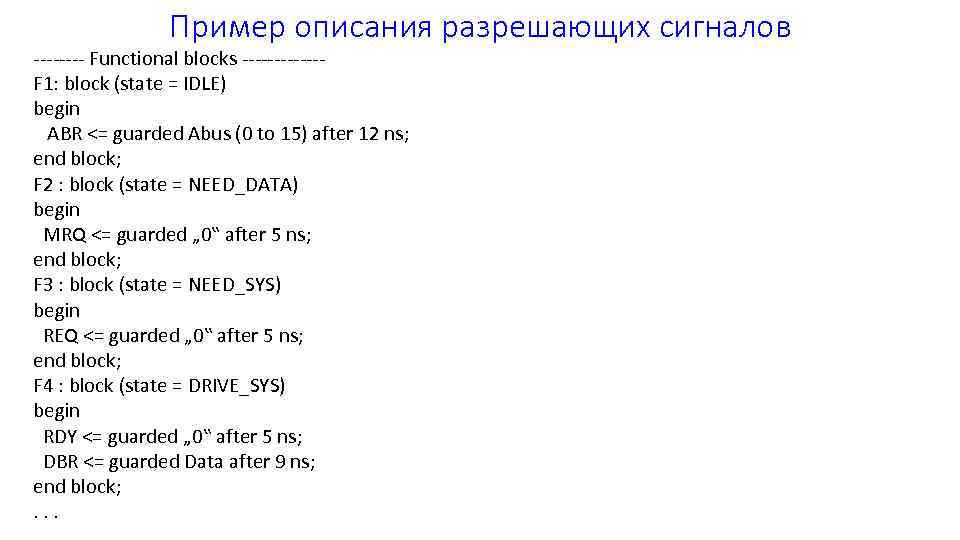

Пример описания разрешающих сигналов ---- Functional blocks ------F 1: block (state = IDLE) begin ABR <= guarded Abus (0 to 15) after 12 ns; end block; F 2 : block (state = NEED_DATA) begin MRQ <= guarded „ 0‟ after 5 ns; end block; F 3 : block (state = NEED_SYS) begin REQ <= guarded „ 0‟ after 5 ns; end block; F 4 : block (state = DRIVE_SYS) begin RDY <= guarded „ 0‟ after 5 ns; DBR <= guarded Data after 9 ns; end block; . . .

Пример описания разрешающих сигналов ---- Functional blocks ------F 1: block (state = IDLE) begin ABR <= guarded Abus (0 to 15) after 12 ns; end block; F 2 : block (state = NEED_DATA) begin MRQ <= guarded „ 0‟ after 5 ns; end block; F 3 : block (state = NEED_SYS) begin REQ <= guarded „ 0‟ after 5 ns; end block; F 4 : block (state = DRIVE_SYS) begin RDY <= guarded „ 0‟ after 5 ns; DBR <= guarded Data after 9 ns; end block; . . .

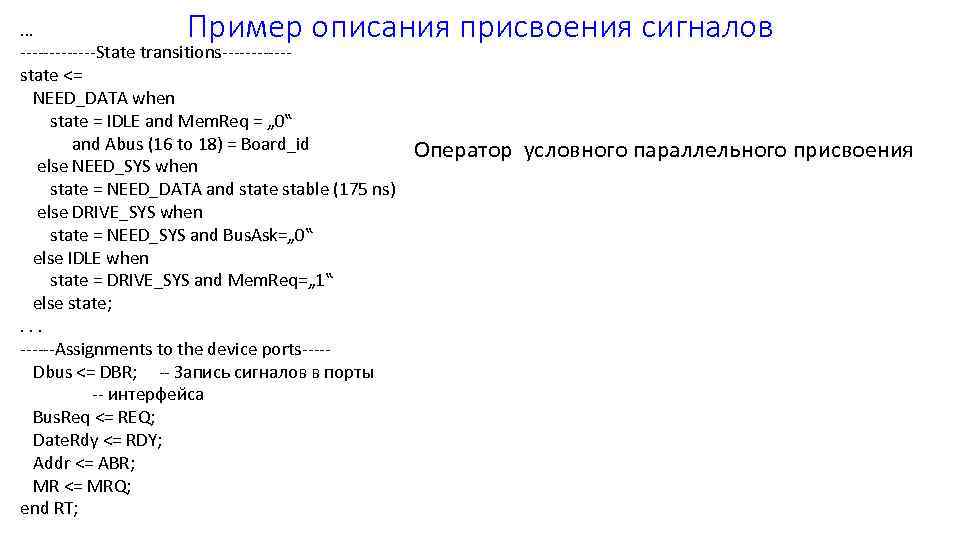

Пример описания присвоения сигналов … -------State transitions------state <= NEED_DATA when state = IDLE and Mem. Req = „ 0‟ and Abus (16 to 18) = Board_id else NEED_SYS when state = NEED_DATA and state stable (175 ns) else DRIVE_SYS when state = NEED_SYS and Bus. Ask=„ 0‟ else IDLE when state = DRIVE_SYS and Mem. Req=„ 1‟ else state; . . . ------Assignments to the device ports----Dbus <= DBR; -- Запись сигналов в порты -- интерфейса Bus. Req <= REQ; Date. Rdy <= RDY; Addr <= ABR; MR <= MRQ; end RT; Оператор условного параллельного присвоения

Пример описания присвоения сигналов … -------State transitions------state <= NEED_DATA when state = IDLE and Mem. Req = „ 0‟ and Abus (16 to 18) = Board_id else NEED_SYS when state = NEED_DATA and state stable (175 ns) else DRIVE_SYS when state = NEED_SYS and Bus. Ask=„ 0‟ else IDLE when state = DRIVE_SYS and Mem. Req=„ 1‟ else state; . . . ------Assignments to the device ports----Dbus <= DBR; -- Запись сигналов в порты -- интерфейса Bus. Req <= REQ; Date. Rdy <= RDY; Addr <= ABR; MR <= MRQ; end RT; Оператор условного параллельного присвоения

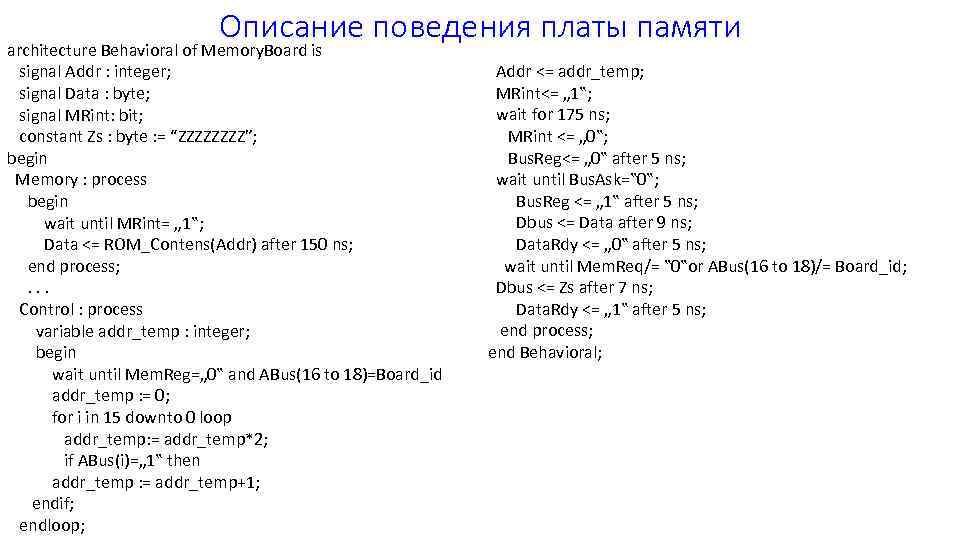

Описание поведения платы памяти architecture Behavioral of Memory. Board is signal Addr : integer; signal Data : byte; signal MRint: bit; constant Zs : byte : = “ZZZZ”; begin Memory : process begin wait until MRint= „ 1‟; Data <= ROM_Contens(Addr) after 150 ns; end process; . . . Control : process variable addr_temp : integer; begin wait until Mem. Reg=„ 0‟ and ABus(16 to 18)=Board_id addr_temp : = 0; for i in 15 downto 0 loop addr_temp: = addr_temp*2; if ABus(i)=„ 1‟ then addr_temp : = addr_temp+1; endif; endloop; Addr <= addr_temp; MRint<= „ 1‟; wait for 175 ns; MRint <= „ 0‟; Bus. Reg<= „ 0‟ after 5 ns; wait until Bus. Ask=‟ 0‟; Bus. Reg <= „ 1‟ after 5 ns; Dbus <= Data after 9 ns; Data. Rdy <= „ 0‟ after 5 ns; wait until Mem. Req/= ‟ 0‟or ABus(16 to 18)/= Board_id; Dbus <= Zs after 7 ns; Data. Rdy <= „ 1‟ after 5 ns; end process; end Behavioral;

Описание поведения платы памяти architecture Behavioral of Memory. Board is signal Addr : integer; signal Data : byte; signal MRint: bit; constant Zs : byte : = “ZZZZ”; begin Memory : process begin wait until MRint= „ 1‟; Data <= ROM_Contens(Addr) after 150 ns; end process; . . . Control : process variable addr_temp : integer; begin wait until Mem. Reg=„ 0‟ and ABus(16 to 18)=Board_id addr_temp : = 0; for i in 15 downto 0 loop addr_temp: = addr_temp*2; if ABus(i)=„ 1‟ then addr_temp : = addr_temp+1; endif; endloop; Addr <= addr_temp; MRint<= „ 1‟; wait for 175 ns; MRint <= „ 0‟; Bus. Reg<= „ 0‟ after 5 ns; wait until Bus. Ask=‟ 0‟; Bus. Reg <= „ 1‟ after 5 ns; Dbus <= Data after 9 ns; Data. Rdy <= „ 0‟ after 5 ns; wait until Mem. Req/= ‟ 0‟or ABus(16 to 18)/= Board_id; Dbus <= Zs after 7 ns; Data. Rdy <= „ 1‟ after 5 ns; end process; end Behavioral;

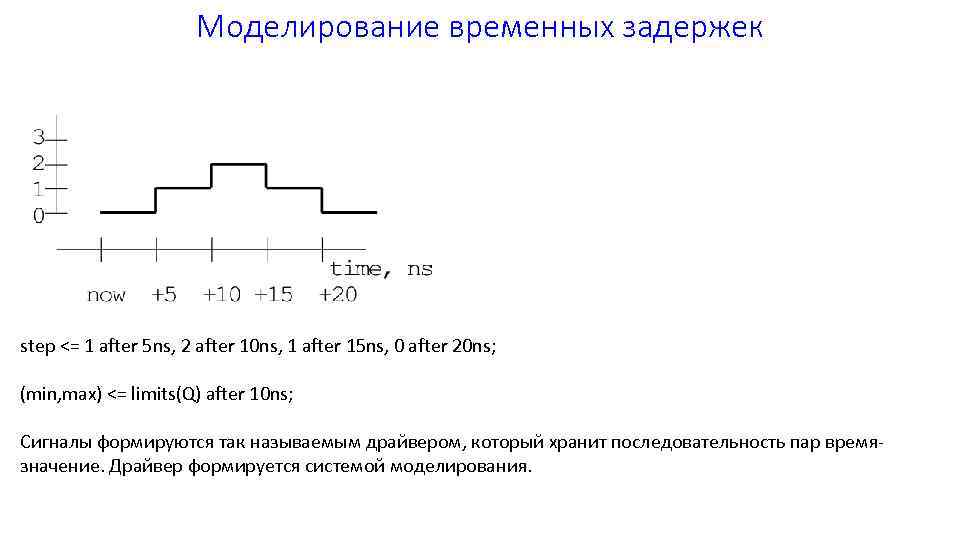

Моделирование временных задержек step <= 1 after 5 ns, 2 after 10 ns, 1 after 15 ns, 0 after 20 ns; (min, max) <= limits(Q) after 10 ns; Сигналы формируются так называемым драйвером, который хранит последовательность пар времязначение. Драйвер формируется системой моделирования.

Моделирование временных задержек step <= 1 after 5 ns, 2 after 10 ns, 1 after 15 ns, 0 after 20 ns; (min, max) <= limits(Q) after 10 ns; Сигналы формируются так называемым драйвером, который хранит последовательность пар времязначение. Драйвер формируется системой моделирования.

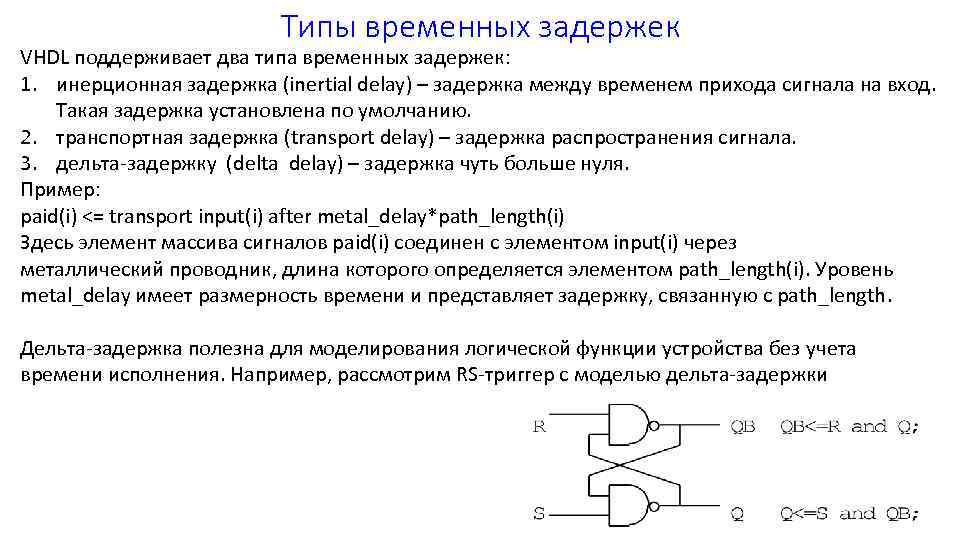

Типы временных задержек VHDL поддерживает два типа временных задержек: 1. инерционная задержка (inertial delay) – задержка между временем прихода сигнала на вход. Такая задержка установлена по умолчанию. 2. транспортная задержка (transport delay) – задержка распространения сигнала. 3. дельта-задержку (delta delay) – задержка чуть больше нуля. Пример: paid(i) <= transport input(i) after metal_delay*path_length(i) Здесь элемент массива сигналов paid(i) соединен с элементом input(i) через металлический проводник, длина которого определяется элементом path_length(i). Уровень metal_delay имеет размерность времени и представляет задержку, связанную с path_length. Дельта-задержка полезна для моделирования логической функции устройства без учета времени исполнения. Например, рассмотрим RS-триггер с моделью дельта-задержки

Типы временных задержек VHDL поддерживает два типа временных задержек: 1. инерционная задержка (inertial delay) – задержка между временем прихода сигнала на вход. Такая задержка установлена по умолчанию. 2. транспортная задержка (transport delay) – задержка распространения сигнала. 3. дельта-задержку (delta delay) – задержка чуть больше нуля. Пример: paid(i) <= transport input(i) after metal_delay*path_length(i) Здесь элемент массива сигналов paid(i) соединен с элементом input(i) через металлический проводник, длина которого определяется элементом path_length(i). Уровень metal_delay имеет размерность времени и представляет задержку, связанную с path_length. Дельта-задержка полезна для моделирования логической функции устройства без учета времени исполнения. Например, рассмотрим RS-триггер с моделью дельта-задержки

complex_single : process begin clk <= „ 1‟ after 10 ns, „ 0‟ after 20 ns, „ 1‟ after 40 ns, „ 0‟ after 50 ns, „ 1‟ after 70 ns, „ 0‟ after 80 ns, „ 1‟ after 100 ns, „ 0‟ after 140 ns; wait for 150 ns; end process; Генерация сигналов entity period_clock is generic (period : time: =1 sec); port (clk : out bit: =„ 0‟); — clk is low initially end period_clock;

complex_single : process begin clk <= „ 1‟ after 10 ns, „ 0‟ after 20 ns, „ 1‟ after 40 ns, „ 0‟ after 50 ns, „ 1‟ after 70 ns, „ 0‟ after 80 ns, „ 1‟ after 100 ns, „ 0‟ after 140 ns; wait for 150 ns; end process; Генерация сигналов entity period_clock is generic (period : time: =1 sec); port (clk : out bit: =„ 0‟); — clk is low initially end period_clock;

Язык VHDL Основные термины VHDL: Рабочая библиотека – библиотека текущего проекта Библиотека ресурсов – библиотеки, используемые в проекте Константа и переменная – содержат значение одного типа. Сигнал подобен переменной, но кроме этого на него можно ссылаться, он имеет историю изменения своих значений, а также множество будущих значений, полученных от формирователя сигнала. Файл – хранилище значений, формально определяется как объект. Тип объекта управления – определение множества его возможных значений и множества возможных операций над объектом. Предопределенные операции Пользовательские операции

Язык VHDL Основные термины VHDL: Рабочая библиотека – библиотека текущего проекта Библиотека ресурсов – библиотеки, используемые в проекте Константа и переменная – содержат значение одного типа. Сигнал подобен переменной, но кроме этого на него можно ссылаться, он имеет историю изменения своих значений, а также множество будущих значений, полученных от формирователя сигнала. Файл – хранилище значений, формально определяется как объект. Тип объекта управления – определение множества его возможных значений и множества возможных операций над объектом. Предопределенные операции Пользовательские операции