Язык ассемблера ASM 86 К. т. н. , доцент кафедры ИУС Феликс Васильевич Филиппов 9000096@mail. ru

Разделы дисциплины • Архитектура компьютера и язык ассемблера • Многоядерные процессоры и параллельное программирование

Литература Гук М. Аппаратные средства IBM PC – СПб. : Питер, 2006 Юров В. Assembler: учебник – СПб. : Питер, 2001 - 2003 • Barry Wilkinson, Michael Allen «Parallel Programming» • James Reinders «Intel Threading Building Blocks» • Intel Press «Multi-Сore Programming»

Раздел 1 Архитектура компьютера и язык ассемблера Архитектура компьютера Центральный процессор Intel 8086 Система команд ЦП Арифметический сопроцессор Intel 8087 Система команд АСП Эволюция развития от Intel 80286 до Intel Pentium 4 Язык ассемблера ASM–x 86

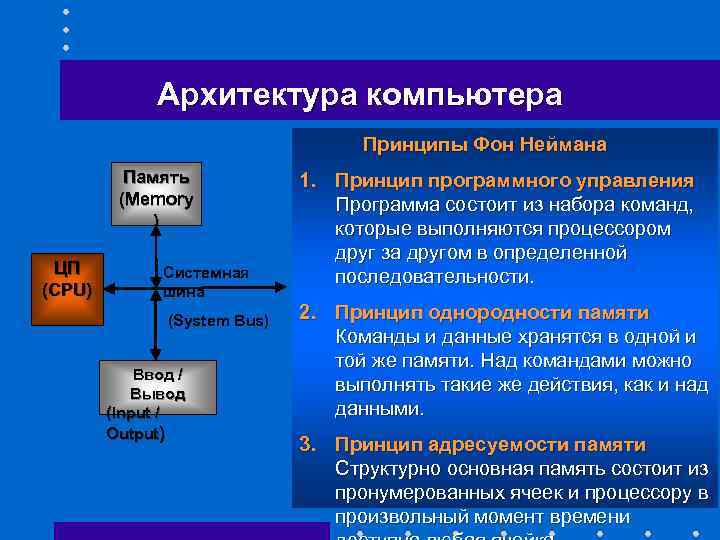

Архитектура компьютера Принципы Фон Неймана Память (Memory ) ЦП (CPU) Системная шина (System Bus) Ввод / Вывод (Input / Output) 1. Принцип программного управления Программа состоит из набора команд, которые выполняются процессором друг за другом в определенной последовательности. 2. Принцип однородности памяти Команды и данные хранятся в одной и той же памяти. Над командами можно выполнять такие же действия, как и над данными. 3. Принцип адресуемости памяти Структурно основная память состоит из пронумерованных ячеек и процессору в произвольный момент времени

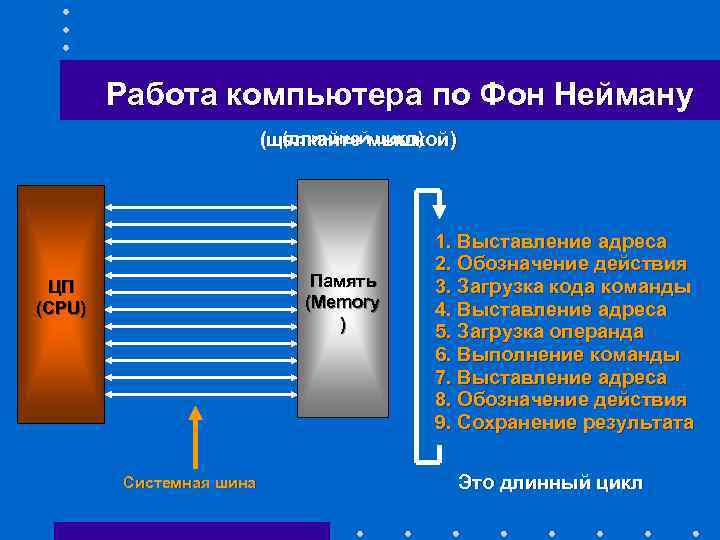

Работа компьютера по Фон Нейману (простой цикл) (щелкайте мышкой) 1 REA D 0 0 1 ЦП 1 1 (CPU) 0 0 1 1 0 MUL BX Память (Memory ) Последовательность действий: 1. Выставление адреса 2. Обозначение действия 3. Загрузка кода команды 4. Выполнение команды Системная шина Это самый простой цикл

Работа компьютера по Фон Нейману (длинный цикл) (щелкайте мышкой) 1 MUL 1 Mem 1 1 1 Память 0 (Memory 0 ) 1 0 1 1 1 WRITE REA D 0 0 1 ЦП 1 1 (CPU) 0 0 1 1 0 Системная шина Последовательность действий: 1. Выставление адреса 2. Обозначение действия 3. Загрузка кода команды 4. Выставление адреса 5. Загрузка операнда 6. Выполнение команды 7. Выставление адреса 8. Обозначение действия 9. Сохранение результата Это длинный цикл

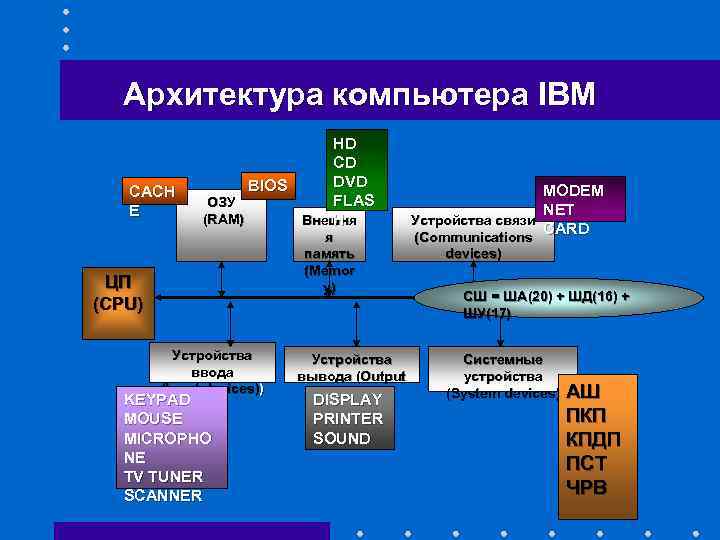

Архитектура компьютера IBM CACH E HD CD DVD BIOS FLAS ОЗУ (RAM) Внешня H я память (Memor y) ЦП (CPU) Устройства ввода (Input devices)) KEYPAD MOUSE MICROPHO NE TV TUNER SCANNER Устройства вывода (Output devices) DISPLAY PRINTER SOUND MODEM NET Устройства связи CARD (Communications devices) СШ = ША(20) + ШД(16) + ШУ(17) Системные устройства (System devices) АШ ПКП КПДП ПСТ ЧРВ

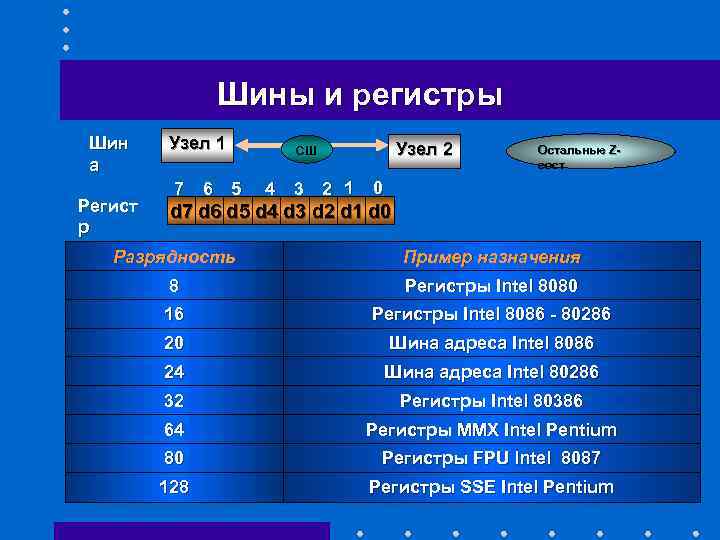

Шины и регистры Шин а Регист р Узел 1 7 6 5 Узел 2 СШ Остальные Zсост 4 3 2 1 0 d 7 d 6 d 5 d 4 d 3 d 2 d 1 d 0 Разрядность Пример назначения 8 Регистры Intel 8080 16 Регистры Intel 8086 - 80286 20 Шина адреса Intel 8086 24 Шина адреса Intel 80286 32 Регистры Intel 80386 64 Регистры MMX Intel Pentium 80 Регистры FPU lntel 8087 128 Регистры SSE Intel Pentium

Архитектура центрального процессора Intel 8086 Блок сопряжения с шиной Специальные регистры СФА Очередь 6 команд 5 4 3 2 1 ША (20) 16 СШ = ШД (16) ШУ (17) Регистры общего назначения (РОН) АЛУ Исполнительный блок УУ и С CL K

назначения (РОН) регистры Специальные Регистры общего Программная модель центрального процессора Intel 8086 15 Арифметически AX AH е BX BH регистры CX CH DX Регистры указатели Регистры индексы Счетчик команд Регистр флагов DH 87 AL BL CL DL 0 ACCUMULATOR BASE COUNT DATA SP BP SI DI STACK POINTER BASE POINTER SOURCE INDEX DESTINATION INDEX IP F INSTRUCTION POINTER FLAGS Сегментные регистры CS DS SS ES CODE SEGMENT DATA SEGMENT STACK SEGMENT EXTRA SEGMENT

Сегментирование памяти 00000 h Сегментные регистры CS IP SP SS DS ES 64 Кб Текущий программный сегмент Текущий сегмент стека 1 Мб EA DI 64 Кб Текущий сегмент данных 64 Кб Текущий дополнительный сегмент FFFFF h

Виды обращения к памяти и используемые регистры Вид обращения к памяти Выборка команды Сегментный регистр Логический адрес CS IP SS SP Обращение к исходной строке DS* SI Обращение к строке результату ES* DI Использование регистра BP SS* EA Прочие обращения к переменной DS* EA Операции со стеком * Выбирается процессором автоматически по умолчанию, но может быть заменен

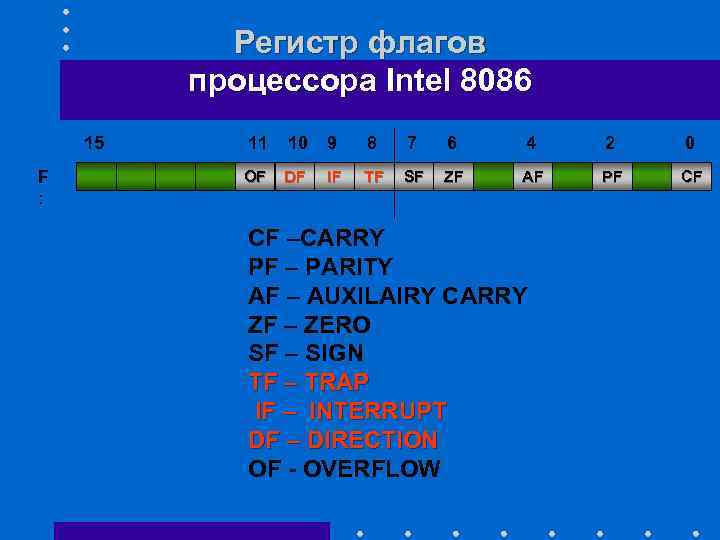

Регистр флагов процессора Intel 8086 15 F : 11 10 9 8 7 6 4 2 0 OF DF IF TF SF ZF AF PF CF CF –CARRY PF – PARITY AF – AUXILAIRY CARRY ZF – ZERO SF – SIGN TF – TRAP IF – INTERRUPT DF – DIRECTION OF - OVERFLOW

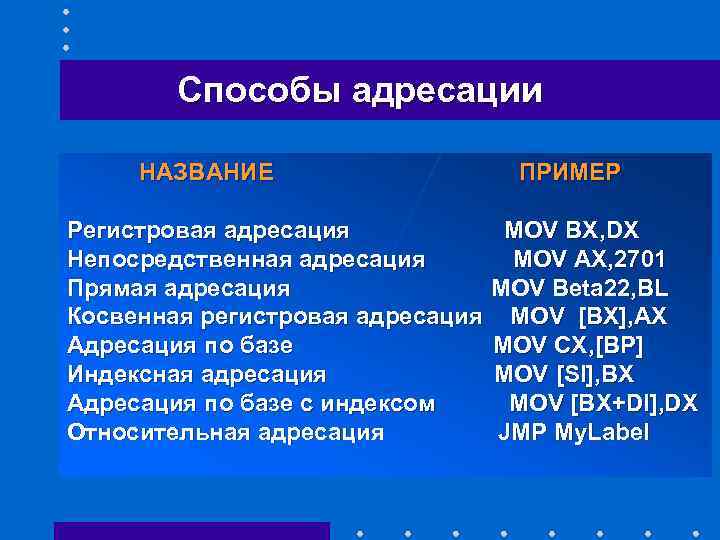

Способы адресации НАЗВАНИЕ ПРИМЕР Регистровая адресация MOV BX, DX Непосредственная адресация MOV AX, 2701 Прямая адресация MOV Beta 22, BL Косвенная регистровая адресация MOV [BX], AX Адресация по базе MOV CX, [BP] Индексная адресация MOV [SI], BX Адресация по базе с индексом MOV [BX+DI], DX Относительная адресация JMP My. Label

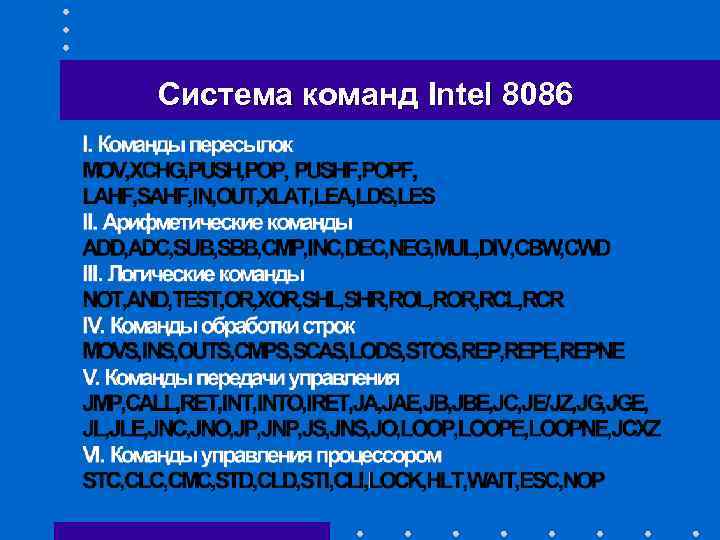

Система команд Intel 8086

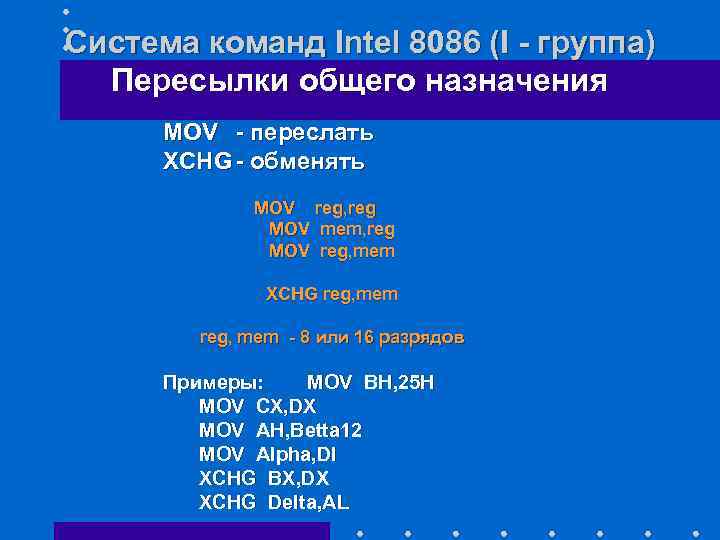

Система команд Intel 8086 (I - группа) Пересылки общего назначения МOV - переслать XCHG - обменять MOV reg, reg MOV mem, reg MOV reg, mem XCHG reg, mem - 8 или 16 разрядов Примеры: MOV BH, 25 H MOV CX, DX MOV AH, Betta 12 MOV Alpha, DI XCHG BX, DX XCHG Delta, AL

Система команд Intel 8086 (I - группа) Пересылки с участием стека PUSH - занести в стек POP - извлечь из стека SP <- SP-2 POP reg POP mem PUSH reg PUSH mem Начало SS SP Вершина SP <- SP+2 reg, mem - 16 разрядов !!! FIFO - очередь LIFO - стек

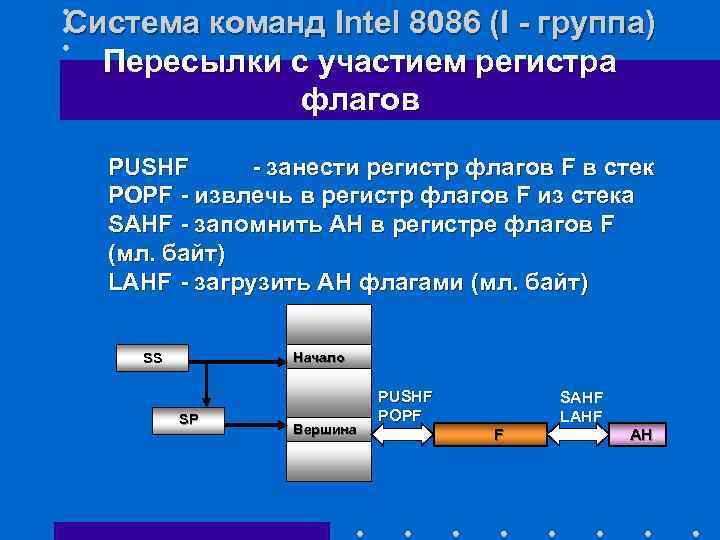

Система команд Intel 8086 (I - группа) Пересылки с участием регистра флагов PUSHF - занести регистр флагов F в стек POPF - извлечь в регистр флагов F из стека SAHF - запомнить АН в регистре флагов F (мл. байт) LAHF - загрузить АН флагами (мл. байт) Начало SS SP Вершина PUSHF POPF SAHF LAHF F AH

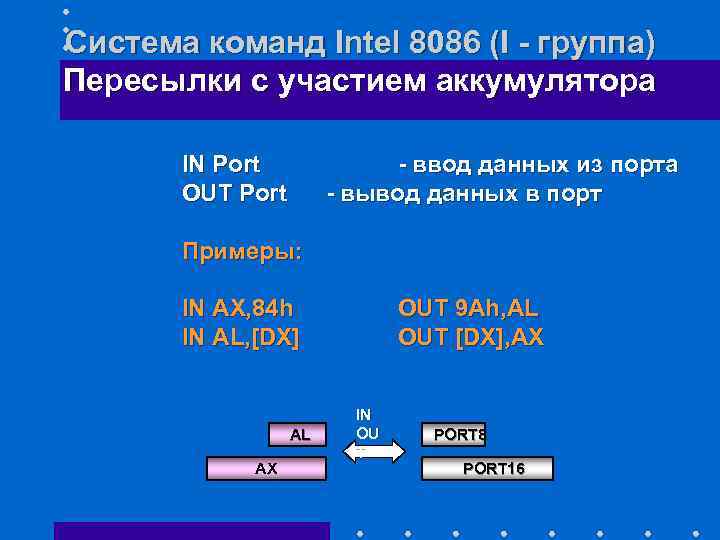

Система команд Intel 8086 (I - группа) Пересылки с участием аккумулятора IN Port OUT Port - ввод данных из порта - вывод данных в порт Примеры: IN AX, 84 h IN AL, [DX] AL AX OUT 9 Ah, AL OUT [DX], AX IN OU T PORT 8 PORT 16

Система команд Intel 8086 (I - группа) Команда перекодировки XLAT Поместить начальный адрес таблицы в ВХ Принять код цифры из порта ввода Подать команду перекодировки Передать новый код в порт вывода Цифра Код “ 2 из 5” 0 11000 1 00011 2 00101 3 00110 4 01001 5 01010 6 01100 7 10001 8 10010 9 10100 MOV BX, Addr. Table IN Port 1 XLAT OUT Port 2

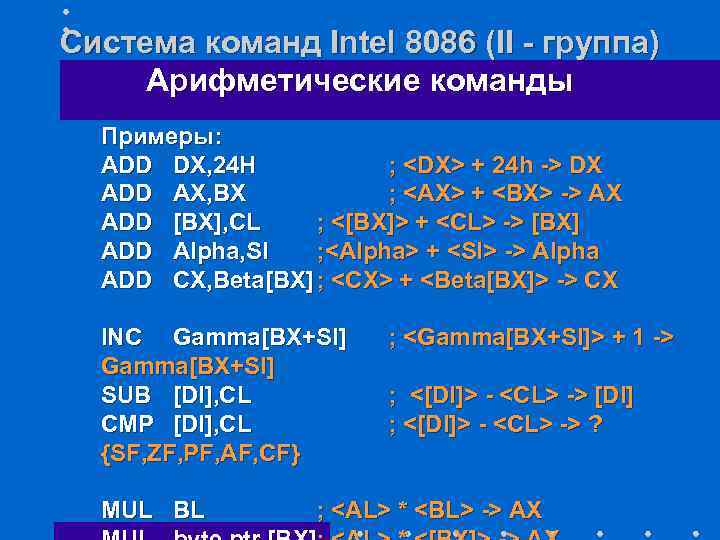

Система команд Intel 8086 (II - группа) Арифметические команды ADD ADC INC SUB SBB DEC CMP NEG MUL IMUL DIV IDIV - сложить с учетом переноса (CF) - сложить с единицей (increment) - вычесть с учетом заема (borrow) - вычесть единицу (decrement) - сравнить (compare) - изменить знак - умножить числа со знаком - разделить числа со знаком

Система команд Intel 8086 (II - группа) Арифметические команды Примеры: ADD DX, 24 H ; <DX> + 24 h -> DX ADD AX, BX ; <AX> + <BX> -> AX ADD [BX], CL ; <[BX]> + <CL> -> [BX] ADD Alpha, SI ; <Alpha> + <SI> -> Alpha ADD CX, Beta[BX] ; <CX> + <Beta[BX]> -> CX INC Gamma[BX+SI] ; <Gamma[BX+SI]> + 1 -> Gamma[BX+SI] SUB [DI], CL ; <[DI]> - <CL> -> [DI] CMP [DI], CL ; <[DI]> - <CL> -> ? {SF, ZF, PF, AF, CF} MUL BL ; <AL> * <BL> -> AX

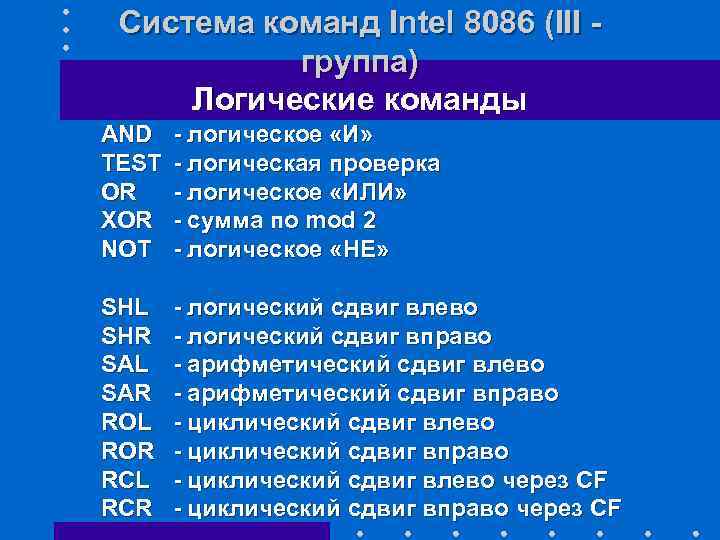

Система команд Intel 8086 (III - группа) Логические команды AND TEST OR XOR NOT - логическое «И» - логическая проверка - логическое «ИЛИ» - сумма по mod 2 - логическое «НЕ» SHL SHR SAL SAR ROL ROR RCL RCR - логический сдвиг влево - логический сдвиг вправо - арифметический сдвиг влево - арифметический сдвиг вправо - циклический сдвиг влево - циклический сдвиг вправо - циклический сдвиг влево через CF - циклический сдвиг вправо через СF

Система команд Intel 8086 (III - группа) Логические команды Примеры: AND BL, AL ; <AL> AND <BL> -> AL TEST BL, AL ; <AL> AND <BL> -> ? {PF, ZF, SF} OR [SI], DX ; <[SI]> OR <DX> -> [SI] XOR BH, 1 fh ; <BH> XOR 1 fh -> BH x x AND x OR y x XOR NOT x NOT DI y ; NOT <DI> y y 0 0 0 1 0 1 1 0 0 1 1 1 1 0 0

![Система команд Intel 8086 (III - группа) Логические команды Пример: SHL word ptr[SI], 3 Система команд Intel 8086 (III - группа) Логические команды Пример: SHL word ptr[SI], 3](https://present5.com/presentation/21341723_147000611/image-26.jpg)

Система команд Intel 8086 (III - группа) Логические команды Пример: SHL word ptr[SI], 3 RCR AL, 4 CF “ 0” SHL/SA L SHR CF CF CF SAR ROL RCR CF RCL

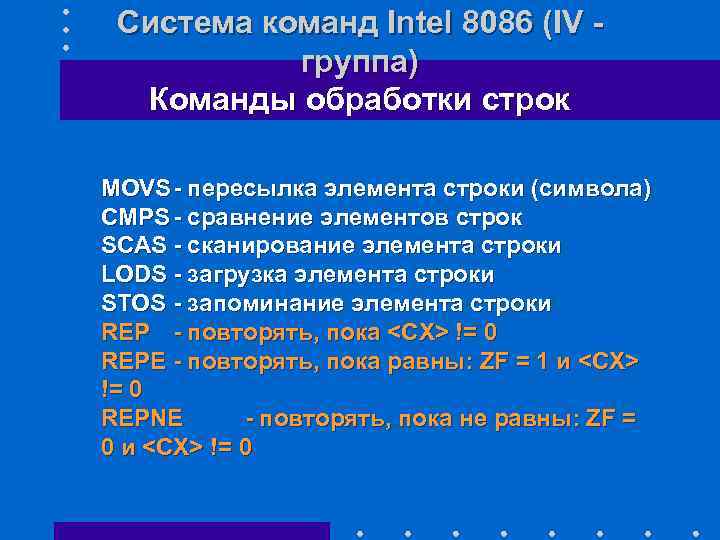

Система команд Intel 8086 (IV - группа) Команды обработки строк MOVS - пересылка элемента строки (символа) CMPS - сравнение элементов строк SCAS - сканирование элемента строки LODS - загрузка элемента строки STOS - запоминание элемента строки REP - повторять, пока <CX> != 0 REPE - повторять, пока равны: ZF = 1 и <CX> != 0 REPNE - повторять, пока не равны: ZF = 0 и <CX> != 0

![Система команд Intel 8086 (IV - группа) Команды обработки строк Примеры: MOVS ; <[SI]> Система команд Intel 8086 (IV - группа) Команды обработки строк Примеры: MOVS ; <[SI]>](https://present5.com/presentation/21341723_147000611/image-28.jpg)

Система команд Intel 8086 (IV - группа) Команды обработки строк Примеры: MOVS ; <[SI]> -> [DI] , SI++, DI++ (или --) SI – адрес источника (исходной строки) в DS DI – адрес приемника (результирующей строки) в ES DF – направление обработки (0 ++, 1 --) Пересылка 100 элементов «восклицательного знака» CLD MOV MOV SI, Inp. Str DI, Out. Str CX, 100 Поиск CLD MOV DI, String 1 MOV AL, 21 H ; ASCII ! MOV CX, SIZE

Система команд Intel 8086 (IV - группа) Команды обработки строк Пример: DS = ES Зачем нужен флаг DF – направление обработки (0 ++, 1 --)? 0101 0104 H 0101 H 0102 H 0103 H 0104 H 0105 H М А С 105 h. Л О H 0104 H 0105 H 0106 H 0107 H 0108 H М А С М А Пересылка 5 элементов CLD ; STD ; MOV SI, 101 h ; MOV DI, 104 h ; 108 h DI, 104 h ; MOV CX, 5 REP MOVS

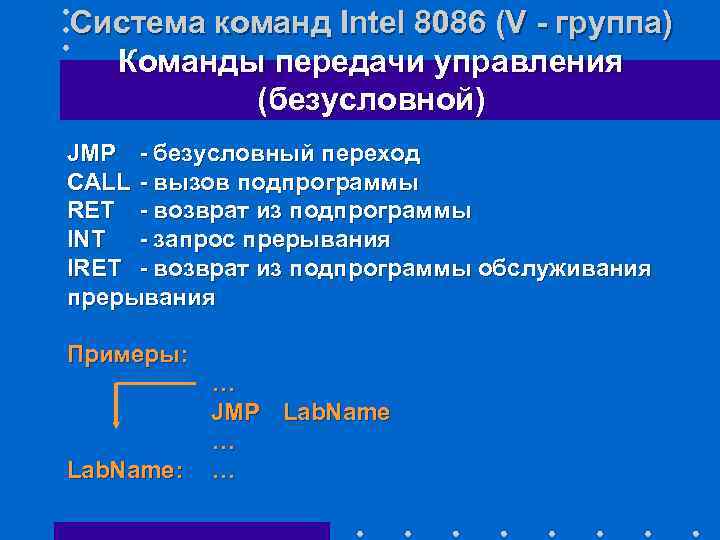

Система команд Intel 8086 (V - группа) Команды передачи управления (безусловной) JMP - безусловный переход CALL - вызов подпрограммы RET - возврат из подпрограммы INT - запрос прерывания IRET - возврат из подпрограммы обслуживания прерывания Примеры: Lab. Name: … JMP Lab. Name … …

Система команд Intel 8086 (V - группа) Команды передачи управления (безусловной) Примеры: … CALL Sub. Name ; (Автоматом PUSH CS и PUSH IP) *** … Sub. Name: Тело подпрограммы … … … RET CS) ; (Автоматом POP IP и POP

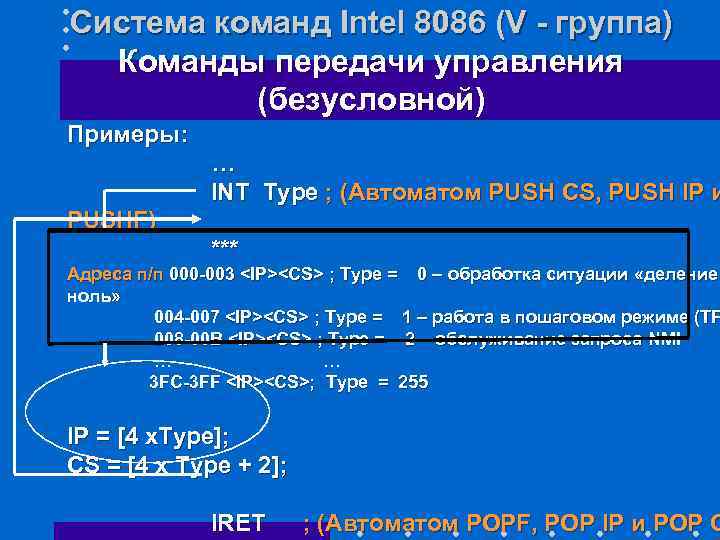

Система команд Intel 8086 (V - группа) Команды передачи управления (безусловной) Примеры: … INT Type ; (Автоматом PUSH CS, PUSH IP и PUSHF) *** Адреса п/п 000 -003 <IP><CS> ; Type = 0 – обработка ситуации «деление ноль» 004 -007 <IP><CS> ; Type = 1 – работа в пошаговом режиме (TF 008 -00 B <IP><CS> ; Type = 2 – обслуживание запроса NMI … 3 FC-3 FF <IP><CS>; Type = 255 IP = [4 x. Type]; CS = [4 x Type + 2]; IRET ; (Автоматом POPF, POP IP и POP C

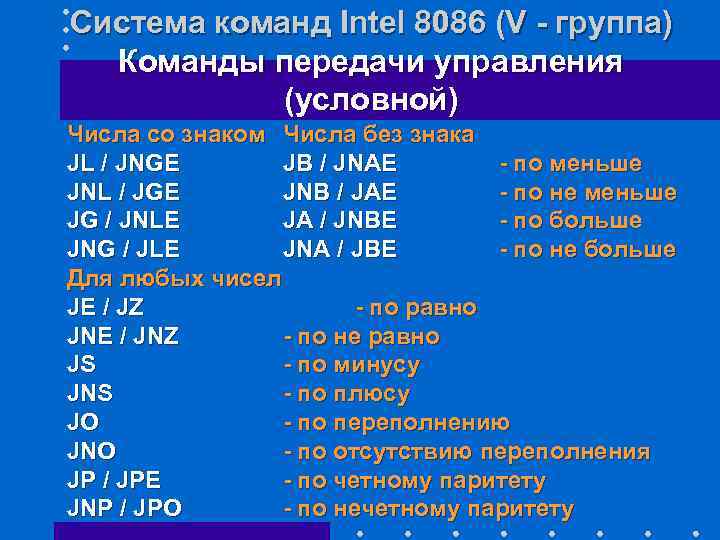

Система команд Intel 8086 (V - группа) Команды передачи управления (условной) Числа со знаком Числа без знака JL / JNGE JB / JNAE - по меньше JNL / JGE JNB / JAE - по не меньше JG / JNLE JA / JNBE - по больше JNG / JLE JNA / JBE - по не больше Для любых чисел JE / JZ - по равно JNE / JNZ - по не равно JS - по минусу JNS - по плюсу JO - по переполнению JNO - по отсутствию переполнения JP / JPE - по четному паритету JNP / JPO - по нечетному паритету

Система команд Intel 8086 (V - группа) Команды передачи управления (условной) LOOP - по <CX> != 0 LOOPNZ /LOOPNE - по ZF = 0 и <CX> != 0 LOOPZ / LOOPE - по ZF != 0 и <CX> != 0 Примеры: Типовой условный переход Типовой цикл CMP BX, DX MOV CX, 100 JA Go. Label Beg. Body: Тело цикла … … … Go. Label: … LOOP Beg. Body

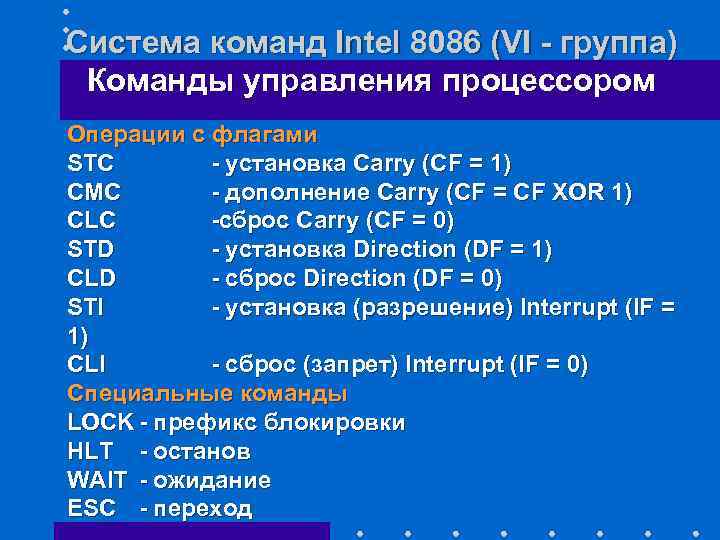

Система команд Intel 8086 (VI - группа) Команды управления процессором Операции с флагами STC - установка Carry (CF = 1) CMC - дополнение Carry (CF = CF XOR 1) CLC -сброс Carry (CF = 0) STD - установка Direction (DF = 1) CLD - сброс Direction (DF = 0) STI - установка (разрешение) Interrupt (IF = 1) CLI - сброс (запрет) Interrupt (IF = 0) Специальные команды LOCK - префикс блокировки HLT - останов WAIT - ожидание ESC - переход

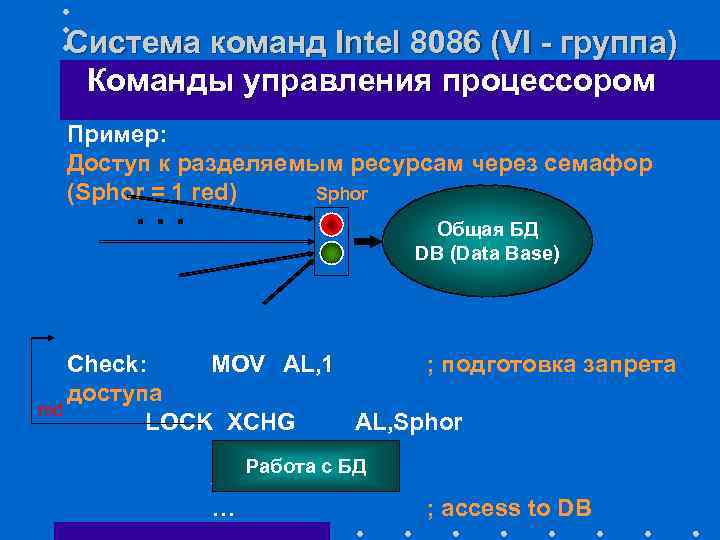

Система команд Intel 8086 (VI - группа) Команды управления процессором Пример: Доступ к разделяемым ресурсам через семафор (Sphor = 1 red) Sphor . . . Общая БД DB (Data Base) Check: MOV AL, 1 ; подготовка запрета доступа red LOCK XCHG AL, Sphor TEST AL, AL Работа с БД JNZ Check … ; access to DB

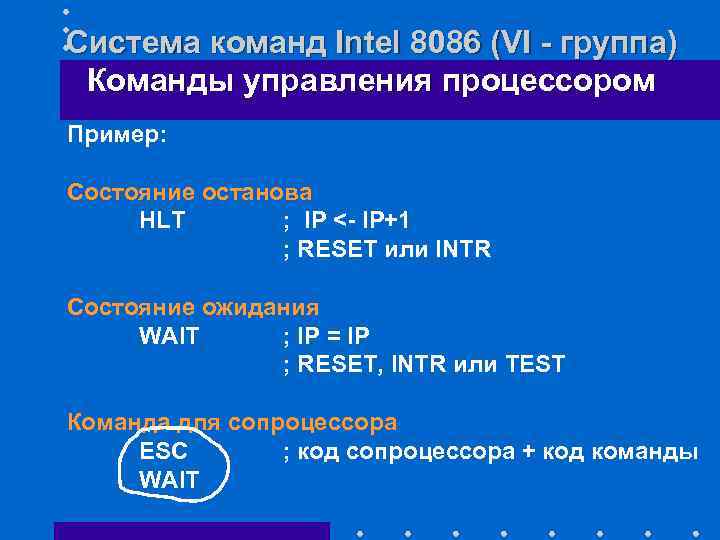

Система команд Intel 8086 (VI - группа) Команды управления процессором Пример: Состояние останова HLT ; IP <- IP+1 ; RESET или INTR Состояние ожидания WAIT ; IP = IP ; RESET, INTR или TEST Команда для сопроцессора ESC ; код сопроцессора + код команды WAIT

Взаимодействие CPU Intel 8086 и FPU Intel 8087 Float Point Unit (FPU) Расширяет систему команд F… ( ~ 60 команд) TEST – вход (активный = 0) BUSY – выход (пассивный = 0) 8086 CPU 1) Команда F… - это ESC+WAIT 8087 2) По ESC включается FPU и BUSY = 1 3) По WAIT в ожидание CPU: ждет TEST = FPU 0 4) Выборка следующей команды, когда BUSY = 0 TES T BUS Y

Эффективность использования FPU Intel 8087 Команда Примерное время исполнения (мкс) (Тактовая частота - 5 Мгц) 8087 8086 - эмуляция Умножение (одинарная точность) 19 1600 Умножение (двойная точность) 27 2100 Сложение 17 1600 Деление 39 3200 Сравнение 9 1300 Загрузка 9 1700 Запоминание 18 1200 Извлечение квадратного корня 36 19600 Вычисление тангенса 90 13000

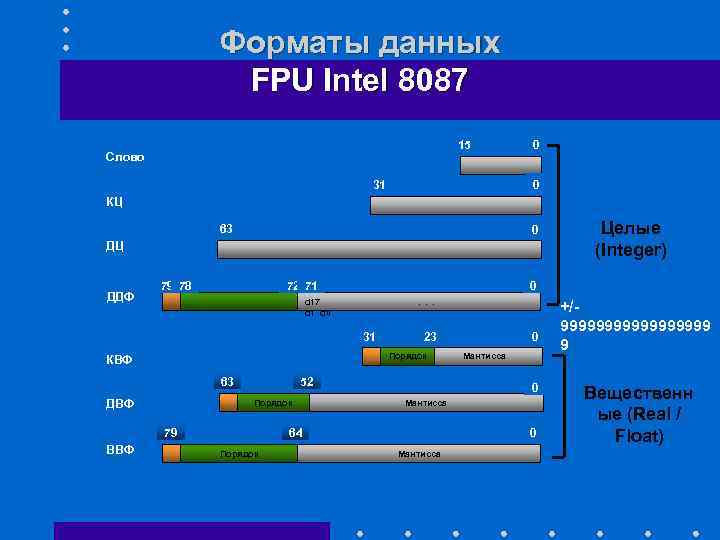

Форматы данных FPU Intel 8087 15 Слово 31 0 0 КЦ 63 0 ДЦ ДДФ 79 78 0 72 71 d 17 . . . d 1 d 0 31 52 63 ДВФ Порядок 79 ВВФ 23 Порядок КВФ 0 Мантисса 64 Порядок Целые (Integer) 0 Мантисса +/- 999999999 9 Вещественн ые (Real / Float)

Диапазон значений вещественных чисел Диапазон представлений Диапазон значений Знак Порядок Мантисса КВФ ДВФ ВВФ 1 11… 11 NAN NAN … … 1 11… 11 00… 01 1 11… 11 00… 00 1 11… 10 11… 11 NAN NAN -3, 37 x 10^38 -1, 67 x 10^308 -1, 2 x 10^4932 … … 1 00… 00 00… 01 -8, 43 x 10^-37 -4, 19 x 10^307 -3, 4 x 10^4931 1 00… 00 -0 -0 -0 0 00… 00 +0 +0 +0 0 00… 01 +8, 43 x 10^-37 +4, 19 x 10^307 +3, 4 x 10^4931 … … 0 11… 11 00… 00 0 11… 11 00… 01 … +3, 37 x 10^38 +1, 67 x 10^308 +1, 2 x 10^4932 NAN NAN …

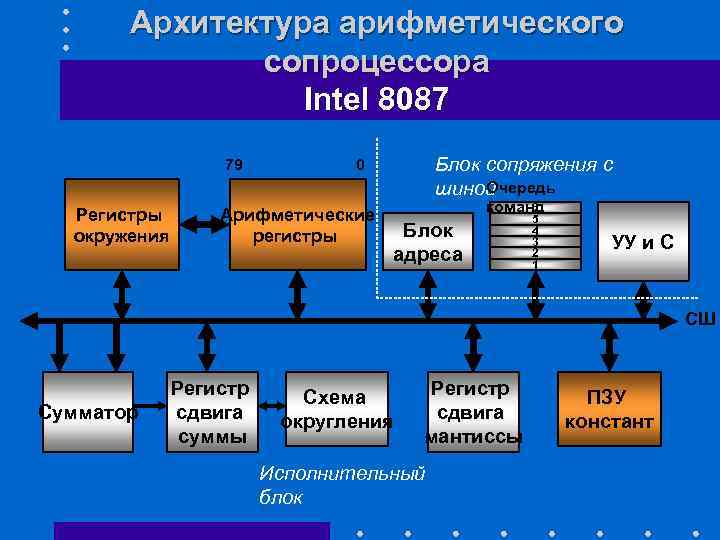

Архитектура арифметического сопроцессора Intel 8087 79 Регистры окружения Блок сопряжения с О шиной чередь 0 Арифметические регистры 6 команд Блок адреса 5 4 3 2 1 УУ и С СШ Сумматор Регистр сдвига суммы Схема округления Регистр сдвига мантиссы Исполнительный блок ПЗУ констант

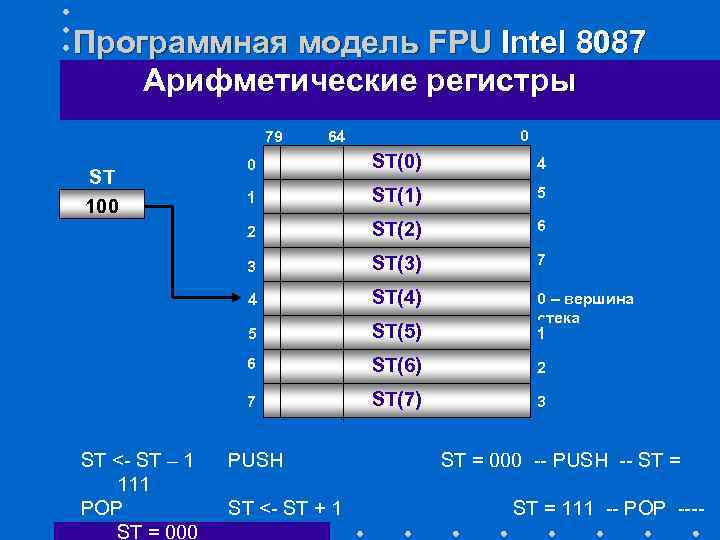

Программная модель FPU Intel 8087 Арифметические регистры 79 0 64 4 1 ST(1) 5 ST(2) 6 3 ST(3) 7 4 ST(4) 5 ST(5) 0 – вершина стека 1 6 ST(6) 2 7 ST <- ST – 1 111 POP ST = 000 ST(0) 2 ST 100 0 ST(7) 3 PUSH ST <- ST + 1 ST = 000 -- PUSH -- ST = 111 -- POP ----

Программная модель FPU Intel 8087 Регистры окружения Регистр состояния (State) SR B C 3 ST C 2 C 1 C 0 IR PE UE OE ZE DE IE ZM D M IM Регистр управления (Control) CR IC RC PC IE M P M U M OM Регистр этикеток (Tag) TR TAG 7 TAG 6 TAG 5 TAG 4 TAG 3 TAG 2 TAG 1 TAG 0 Регистр указатель исключительных ситуаций (Exception) EP команды операнда 20 – ти разрядный адрес 11 младших разрядов команды 20 – ти разрядный адрес

Программная модель FPU Intel 8087 Регистр окружения (SR) Регистр состояния (State) SR B C 3 ST C 2 C 1 C 0 IR PE UE OE ZE DE IE B – текущее состояние BUSY ST - текущее значение ST C 0 – C 3 – флаги результатов выполнения команд FCOM, FXAM и FPREM IR - флаг запроса прерывания X 0 в ST(0), X 1 в C 3 C 0 PE - потеря точности reg/me UE - денормализация X 0 > X 1 0 0 OE - переполнение X 0 < X 1 0 1 ZE - деление на « 0» X 0 = X 1 1 0 DE - денормализованный операнд X 0 несравнимо с 1 1 IE - недействительная операция X 1 FCLEX – команда сброса флагов

Программная модель FPU Intel 8087 Регистр окружения (CR) Регистр управления (Control) CR IC RC PC IE M P M U M OM ZM D M IM IC – тип арифметики (1 – афинная, 0 – проективная) RC 00 Округлени е К четному 01 К - 10 К + PC 00 ВВФ 01 КВФ 10 ДВФ 11 К нулю PM - маска потери точности UM - маска денормализации OM - маска переполнения ZM - маска деления на « 0» DM - маскирует денормализованный операнд IM - маскирует недействительную + - Точность 0 Проективна я - - + 0 Афинна я +

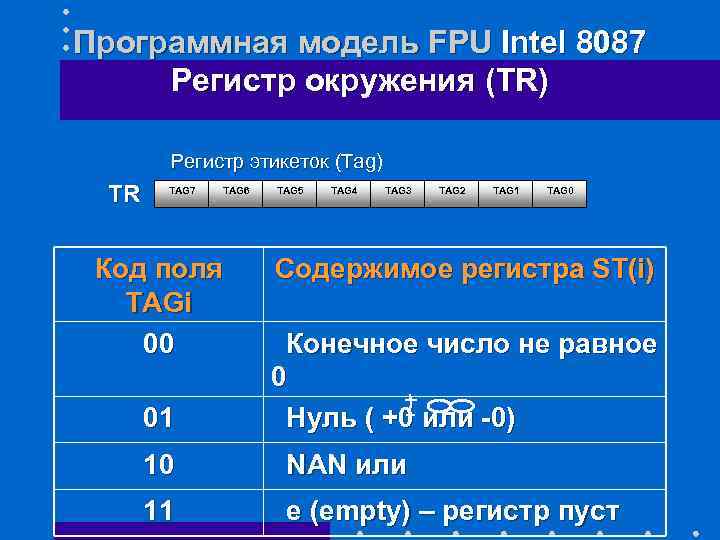

Программная модель FPU Intel 8087 Регистр окружения (TR) Регистр этикеток (Tag) TR TAG 7 TAG 6 Код поля TAGi 00 TAG 5 TAG 4 TAG 3 TAG 2 TAG 1 TAG 0 Содержимое регистра ST(i) 01 Конечное число не равное 0 Нуль ( +0 или -0) 10 NAN или 11 e (empty) – регистр пуст

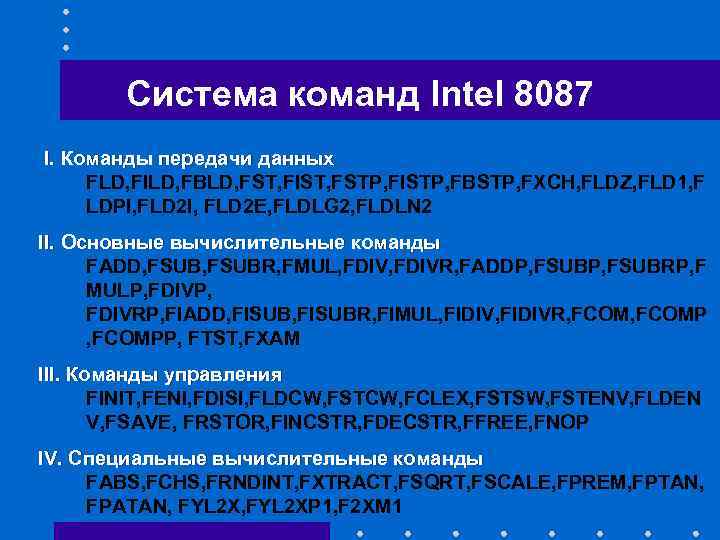

Система команд Intel 8087 I. Команды передачи данных FLD, FILD, FBLD, FST, FIST, FSTP, FISTP, FBSTP, FXCH, FLDZ, FLD 1, F LDPI, FLD 2 E, FLDLG 2, FLDLN 2 II. Основные вычислительные команды FADD, FSUBR, FMUL, FDIVR, FADDP, FSUBRP, F MULP, FDIVP, FDIVRP, FIADD, FISUBR, FIMUL, FIDIVR, FCOMPP, FTST, FXAM III. Команды управления FINIT, FENI, FDISI, FLDCW, FSTCW, FCLEX, FSTSW, FSTENV, FLDEN V, FSAVE, FRSTOR, FINCSTR, FDECSTR, FFREE, FNOP IV. Специальные вычислительные команды FABS, FCHS, FRNDINT, FXTRACT, FSQRT, FSCALE, FPREM, FPTAN, FPATAN, FYL 2 XP 1, F 2 XM 1

Система команд Intel 8087 (I - группа) Команды передачи данных (загрузки) Мнемокод Действия Тип данных FLD addr (addr) -> ST(0) числа FILD addr (addr) -> ST(0) FBLD addr (addr) -> ST(0) десятичные числа FLDZ FLD 1 FLDPI FLD 2 E FLDLG 2 FLDLN 2 вещественные целые числа двоично- “ 0” -> ST(0) “ 1” -> ST(0) 3, 1415…-> ST(0) log 10 -> ST(0) log e -> ST(0) lg 2 -> ST(0) ln 2 -> ST(0)

Система команд Intel 8087 (I - группа) Команды передачи данных Мнемокод Действия Тип данных (запоминания) FST addr КВФ, ДВФ FIST addr Cлово, КЦ FSTP addr КВФ, ДВФ, ВВФ FISTP addr Слово, КЦ, ДЦ FBSTP addr ST(0) -> (addr) ST(0) -> (addr) + pop ДДФ

Система команд Intel 8087 (I - группа) Команды передачи данных (пересылки) Мнемокод Действия FLD ST(i) (PUSH) FST ST(i) FSTP ST(i) (POP) FXCH ST(i) -> ST(0) запись ST(0) -> ST(i) выталкивание ST(0) <-> ST(i)

Система команд Intel 8087 (II - группа) Основные вычислительные Мнемокод Действия + POP Целые команды (арифметика) FADD ST(0) + ST(1) -> ST(0) FADDP FIADD addr FSUB ST(0) - ST(1) -> ST(0) FSUBP FISUB addr FSUBR ST(1) - ST(0) -> ST(0) FSUBRP FISUBR addr FMUL ST(0) * ST(1) -> ST(0) FMULP FIMUL addr FDIV ST(0) / ST(1) -> ST(0) FDIVP FIDIV addr FDIVR ST(1) / ST(0) -> ST(0) FDIVRP FIDIVR addr FADD ST(3), ST ; ST ~ ST(0)

Система команд Intel 8087 (II - группа) Основные вычислительные команды (сравнения и анализ) Мнемокод Действия FCOM ST(0) сравнивается с ST(1) FCOMP ST(0) сравнивается с ST(1) + pop FCOMPP ST(0) сравнивается с ST(1) + pop FTST ST(0) сравнивается с нулем FXAM ST(0) анализируется FICOM addr ST(0) сравнивается с (addr) FICOMP addr ST(0) сравнивается с (addr) + pop FCOM ST(i) FCOM addr FCOMP ST(i) FCOMP addr

Система команд Intel 8087 (II - группа) Основные вычислительные команды (результаты сравнения и анализа) C 0 X 0 > X 1 0 0 0 1 1 0 X 0 несравнимо с X 1 С 2 – знак числа C 3 X 0 = X 1 FXAM X 0 в ST(0), X 1 в reg/me X 0 < X 1 FCOM, FTST 1 1 C 0 C 1 C 3 = 0 C 3 = 1 0 0 Ненормализованно е NAN 0 1 Нормализованное 1 0 Денормализованно е 1 1 Нуль e empty

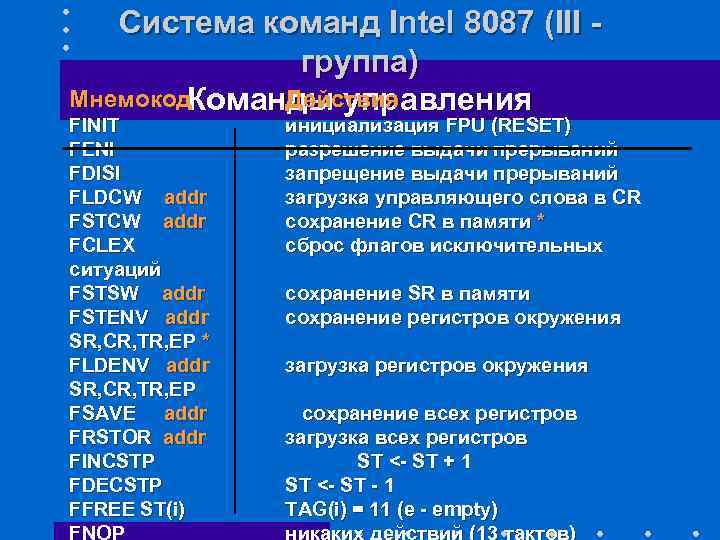

Система команд Intel 8087 (III - группа) Мнемокод. Команды управления Действия FINIT инициализация FPU (RESET) FENI разрешение выдачи прерываний FDISI запрещение выдачи прерываний FLDCW addr загрузка управляющего слова в CR FSTCW addr сохранение CR в памяти * FCLEX сброс флагов исключительных ситуаций FSTSW addr сохранение SR в памяти FSTENV addr сохранение регистров окружения SR, CR, TR, EP * FLDENV addr загрузка регистров окружения SR, CR, TR, EP FSAVE addr сохранение всех регистров FRSTOR addr загрузка всех регистров FINCSTP ST <- ST + 1 FDECSTP ST <- ST - 1 FFREE ST(i) TAG(i) = 11 (e - empty) FNOP никаких действий (13 тактов)

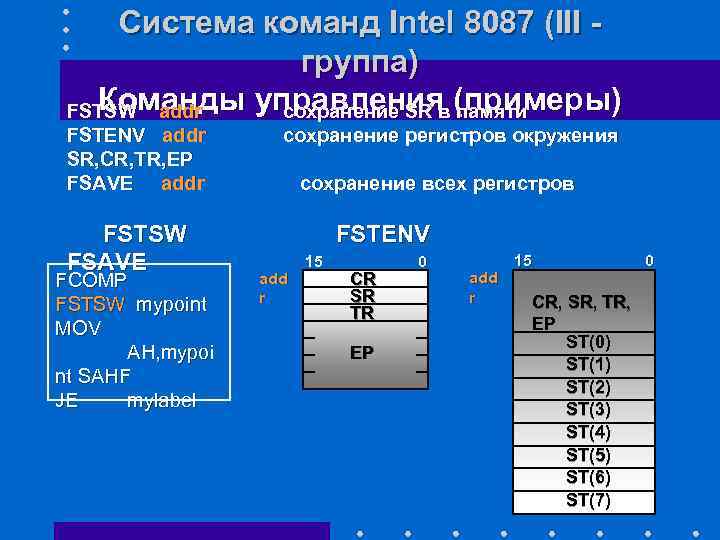

Система команд Intel 8087 (III - группа) Команды управленияв памяти FSTSW addr сохранение SR (примеры) FSTENV addr сохранение регистров окружения SR, CR, TR, EP FSAVE addr сохранение всех регистров FSTSW FSAVE FCOMP FSTSW mypoint MOV AH, mypoi nt SAHF JE mylabel FSTENV add r 15 CR SR TR EP 0 add r 15 CR, SR, TR, EP ST(0) ST(1) ST(2) ST(3) ST(4) ST(5) ST(6) ST(7) 0

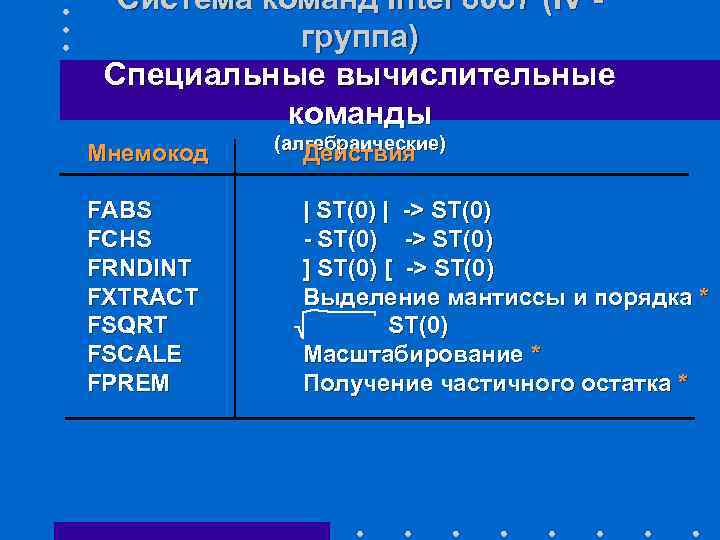

Система команд Intel 8087 (IV - группа) Специальные вычислительные команды Мнемокод FABS FCHS FRNDINT FXTRACT FSQRT FSCALE FPREM (алгебраические) Действия | ST(0) | -> ST(0) - ST(0) -> ST(0) ] ST(0) [ -> ST(0) Выделение мантиссы и порядка * ST(0) Масштабирование * Получение частичного остатка *

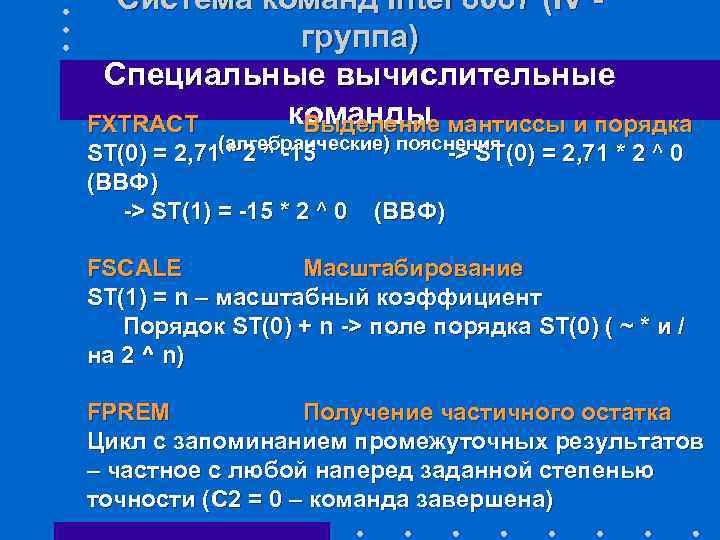

Система команд Intel 8087 (IV - группа) Специальные вычислительные команды FXTRACT Выделение мантиссы и порядка (алгебраические) пояснения ST(0) = 2, 71 * 2 ^ -15 -> ST(0) = 2, 71 * 2 ^ 0 (ВВФ) -> ST(1) = -15 * 2 ^ 0 (ВВФ) FSCALE Масштабирование ST(1) = n – масштабный коэффициент Порядок ST(0) + n -> поле порядка ST(0) ( ~ * и / на 2 ^ n) FPREM Получение частичного остатка Цикл с запоминанием промежуточных результатов – частное с любой наперед заданной степенью точности (C 2 = 0 – команда завершена)

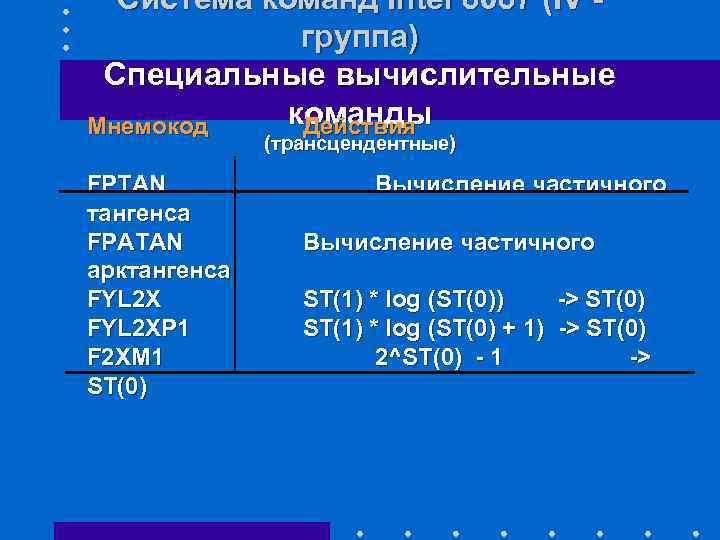

Система команд Intel 8087 (IV - группа) Специальные вычислительные команды Мнемокод Действия (трансцендентные) FPTAN тангенса FPATAN арктангенса FYL 2 XP 1 F 2 XM 1 ST(0) Вычисление частичного ST(1) * log (ST(0)) -> ST(0) ST(1) * log (ST(0) + 1) -> ST(0) 2^ST(0) - 1 ->

Система команд Intel 8087 (IV - группа) Специальные вычислительные команды FPTAN Вычисление частичного (трансцендентные) пояснения тангенса ST(0) = z (0 < z < /4) -> ST(0) = x, ST(1) = y tg z / 2 = y / x sin z = 2 (y / x) / [ 1 + (y / x) ^ 2] FPATAN Вычисление частичного арктангенса ST(0) = x, ST(1) = y -> ST(0) = z = arctg y / x lg x = lg 2 log x = FYL 2 X ( FLDLG 2, x ) e ^ x = 1 + (2^ x log e - 1) = 1 + F 2 XM 1 ( x FLDL 2 E) x ^ y = 1 + (2^ y log x - 1) = 1 + F 2 XM 1 ( FYL 2 X ( x, y) )

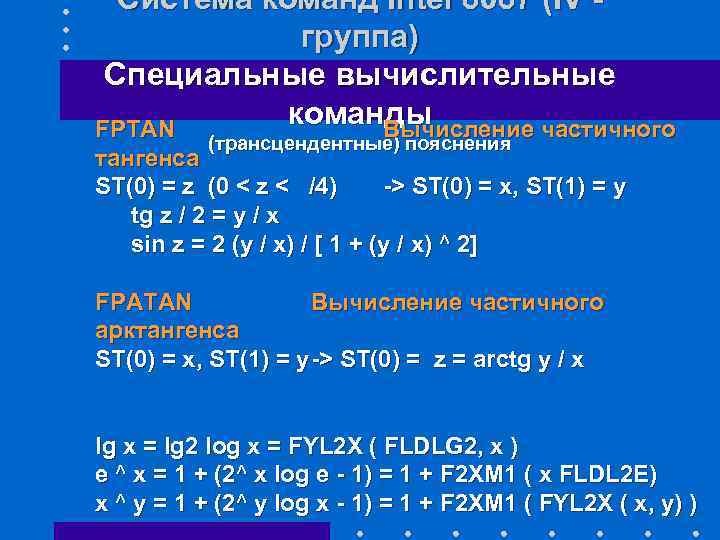

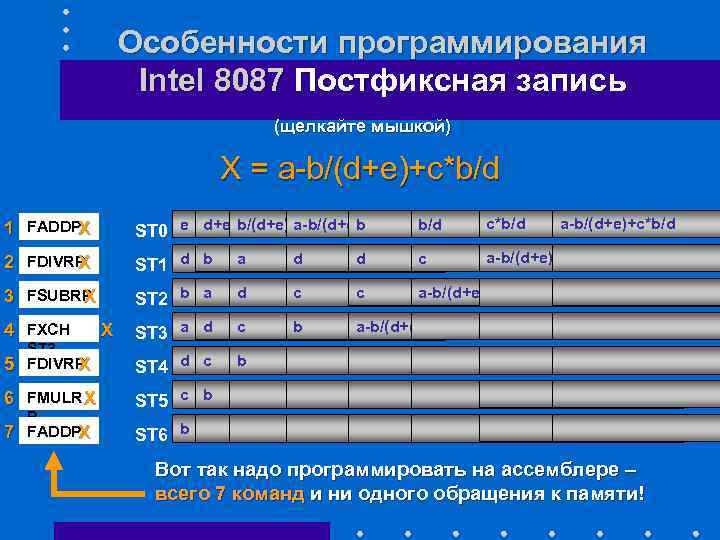

Особенности программирования Intel 8087 Постфиксная запись a-b/(d+e)+c*b/d + a * / c b / + b d e abde+/-cbd/*+ d

Особенности программирования Intel 8087 Постфиксная запись (щелкайте мышкой) X = a-b/(d+e)+c*b/d 1 FADDP Х b ST 0 e d+e b/(d+e) a-b/(d+e) b/d c*b/d 2 FDIVRP Х ST 1 d b a d d c a-b/(d+e) 3 FSUBRP Х ST 2 b a d c c a-b/(d+e) ST 3 a d c b a-b/(d+e) ST 4 d c b 4 FXCH ST 3 5 FDIVRP Х 6 FMULR Х P 7 FADDP Х Х a-b/(d+e)+c*b/d c ST 5 b b b ST 6 c Вот так надо программировать на ассемблере – всего 7 команд и ни одного обращения к памяти!

Эволюция технических характеристик ЦП Intel 8086 Кодовое название Н/Д Дата выпуска 1979 Архитектура 16 битов Шина данных 16 битов Шина адреса 20 битов Макс. объём памяти 1 Мбайт Кэш L 1 Нет Кэш L 2 Нет Тактовая частота 4, 77 -10 МГц FSB Равная частоте CPU FPU 8087 SIMD Нет Техпроцесс 3 000 нм Число транзисторов 29 000 Энергопотребление Н/Д Напряжение 5 В Площадь кристалла 16 мм² Сокет 40 -контактный

Эволюция технических характеристик ЦП Intel 80286 Кодовое название Н/Д Дата выпуска 1982 Архитектура 16 битов Шина данных 16 битов Шина адреса 24 бита Макс. объём памяти 16 Мбайт Кэш L 1 Нет Кэш L 2 Нет Тактовая частота 6 -12 МГц FSB Равная частоте CPU FPU 80287 SIMD Нет Техпроцесс 1500 нм Число транзисторов 134 000 Энергопотребление Н/Д Напряжение 5 В Площадь кристалла 49 мм² Сокет 68 -контактный

Эволюция технических характеристик ЦП Intel 80386 DX Кодовое название P 3 Дата выпуска 1985 Архитектура 32 бита Шина данных 32 бита Шина адреса 32 бита Макс. объём памяти 4096 Мбайт Кэш L 1 0 кбайт Кэш L 2 Нет Тактовая частота 16 -33 МГц FSB Равная частоте CPU FPU 80387 SIMD Нет Техпроцесс 1500 -1000 нм Число транзисторов 275 000 Энергопотребление 2 Вт @ 33 МГц Напряжение 5 В Площадь кристалла 42 мм² @ 1 мкм Сокет 132 контакта

Эволюция технических характеристик ЦП Intel 80486 DX Кодовое название P 4, P 24 C Дата выпуска 1989 Архитектура 32 бита Шина данных 32 бита Шина адреса 32 бита Макс. объём памяти 4096 Мбайт Кэш L 1 8 кбайт Кэш L 2 На материнской плате (на частоте FSB) Тактовая частота 16 -100 МГц FSB 16 -50 МГц FPU На кристалле SIMD Нет Техпроцесс 1000 -800 нм Число транзисторов 1 185 000 Энергопотребление Н/Д Напряжение 5 В - 3, 3 В Площадь кристалла 81 - 67 мм² Сокет 168 контактов

Эволюция технических характеристик ЦП Intel Pentium и Pentium MMX Intel Pentium (MMX) Кодовое название P 5, P 54 P 55 (Pentium MMX) Дата выпуска 1993 1997 Архитектура 32 бита Шина данных 64 бита Шина адреса 32 бита Макс. объём памяти 4096 Мбайт Кэш L 1 8 + 8 кбайт 16 + 16 кбайт Кэш L 2 Материнская плата Тактовая частота 60 -200 МГц 133 -300 МГц FSB 50 -66 МГц 60 -66 МГц FPU На кристалле SIMD Нет MMX Техпроцесс 800 -600 -350 нм Число транзисторов 3, 1 -3, 3 млн. 4, 5 млн. Энергопотребл ение 8 -16 Вт 4 -17 Вт Напряжение 5 - 3, 3 В 2, 8 В Площадь кристалла 294 -163 -90 мм² 141 мм²

Эволюция технических характеристик ЦП Intel Pentium Pro Кодовое название P 6 Дата выпуска 1995 Архитектура 32 бита Шина данных 64 бита Шина адреса 36 битов Макс. объём памяти 64 Гбайт Кэш L 1 8 + 8 кбайт Кэш L 2 Внешний, 256 -1024 кбайт (на частоте CPU) Тактовая частота 150 -200 МГц FSB 60 -66 МГц FPU Встроенный SIMD Н/Д Техпроцесс 600 -350 нм Число транзисторов 5 500 000 + кэш Энергопотребление 29 -47 Вт Напряжение 3, 3 В Площадь кристалла 306 -196 мм² + кэш Сокет Socket 8

Эволюция технических характеристик ЦП Intel Pentium II и III Intel Pentium II and III Кодовое название Klamath (PII 0, 35 мкм), Deschutes (PII 0, 25 мкм), Katmai (PIII) Дата выпуска 1997, 1998, 1999 Архитектура 32 бита Шина данных 64 бита Шина адреса 36 битов (32 бита на P III) Макс. объём памяти 64 Гбайт (4 Гбайт на P III) Кэш L 1 16 + 16 кбайт Кэш L 2 Внешний, 512 кбайт Тактовая частота 233 -300 МГц (Kl), 300 -450 МГц (D), 450 -600 МГц (Ka) FSB 66 -100 -133 МГц FPU Встроенный SIMD MMX (SSE) Техпроцесс 350 нм (Klamath), 250 нм (Deschutes, Katmai) Число транзисторов 7 500 000 + кэш (Pentium II), 9 500 000 + кэш (Pentium III) Энергопотребление 25 -35 Вт Напряжение 2, 8 В (0, 35 мкм), 2 В (0, 25 мкм) Площадь кристалла 204 мм² (0, 35 мкм), 131 мм 2 (0, 25 мкм), 128 мм 2 (PIII) + кэш Сокет Slot 1

Эволюция технических характеристик ЦП Intel Celeron и Xeon Intel Celeron и Intel Xeon Кодовое название Covington, Mendocino Drake Дата выпуска 1998 Архитектура 32 бита Шина данных 64 бита Шина адреса 32 бита 36 битов Макс. объём памяти 4 Гбайт 64 Гбайт Кэш L 1 16 + 16 кбайт Кэш L 2 0 кбайт/128 кбайт Внешний - 2408 кбайт Тактовая частота 266 -300 МГц/300533 МГц 400 -450 МГц FSB 66 МГц 100 МГц FPU Встроенный SIMD MMX Техпроцесс 250 нм Число транзисторов 7 500 000/19 000 7 500 000 + кэш Энергопотребление 16 -28 Вт 30 -46 Вт Напряжение 2 В 2 В Площадь кристалла 131 мм²/154 мм 2 131 мм² + кэш Сокет Slot 1/Socket 370 PPGA Slot 2

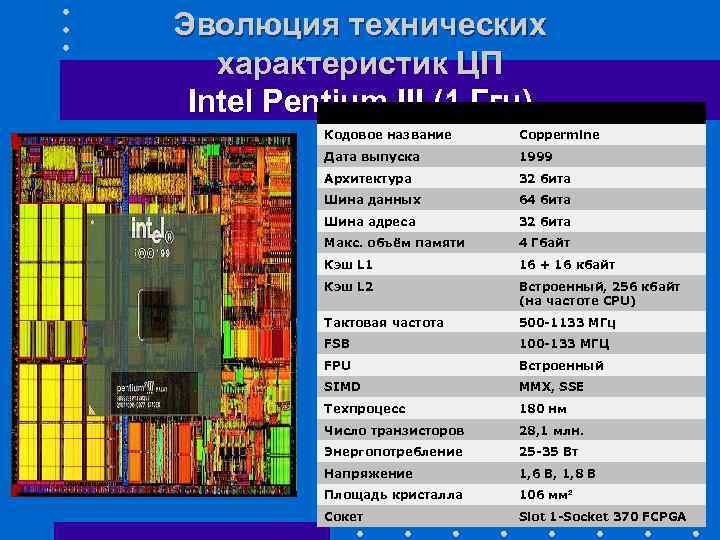

Эволюция технических характеристик ЦП Intel Pentium III (1 Ггц) Intel Pentium III Кодовое название Coppermine Дата выпуска 1999 Архитектура 32 бита Шина данных 64 бита Шина адреса 32 бита Макс. объём памяти 4 Гбайт Кэш L 1 16 + 16 кбайт Кэш L 2 Встроенный, 256 кбайт (на частоте CPU) Тактовая частота 500 -1133 МГц FSB 100 -133 МГЦ FPU Встроенный SIMD MMX, SSE Техпроцесс 180 нм Число транзисторов 28, 1 млн. Энергопотребление 25 -35 Вт Напряжение 1, 6 В, 1, 8 В Площадь кристалла 106 мм² Сокет Slot 1 -Socket 370 FCPGA

Эволюция технических характеристик ЦП Intel Pentium 4 (32 бита) Intel Pentium 4 32 -bit Кодовое название Willamette Northwood Prescott Дата выпуска 2000 2001 2004 Архитектура 32 бита Шина данных 64 бита Шина адреса 32 бита Макс. объём памяти 4 Гбайт Кэш L 1 8 кбайт + 12 Kµops 16 кбайт + 12 Kµops Кэш L 2 256 кбайт 512 кбайт 1024 кбайт Тактовая частота 1, 3 -2 ГГц 1, 8 -3, 4 ГГц 2, 4 -3, 8 ГГц FSB 400 МГц QDR 533, 800 МГц SIMD MMX, SSE, SSE 2 MMX, SSE 2, SSE 3 SMT/SMP Нет Hyper-Threading Техпроцесс 180 нм 130 нм 90 нм Число транзисторов 42 млн. 55 млн. 125 млн. Энергопотребле ние 66 -100 Вт 54 -137 Вт 94 -151 Вт Напряжение 1, 7 В 1, 55 В 1, 25 -1, 5 В Площадь кристалла 217 мм² 146 мм² 112 мм²

Эволюция технических характеристик ЦП Intel Pentium M Кодовое название Banias Dothan Дата выпуска 2003 2004 Архитектура 32 бита Шина данных 64 бита Шина адреса 32 бита Макс. объём памяти 4 Гбайт Кэш L 1 32 + 32 кбайт Кэш L 2 1024 кбайт 2048 кбайт Тактовая частота 0, 9 -1, 7 ГГц 1 -2, 13 ГГц FSB 400 МГц 400, 533 МГц SIMD MMX, SSE, SSE 2 SMT/SMP Нет Техпроцесс 130 нм 90 нм Число транзисторов 77 млн. 140 млн. Энергопотреблен ие 9 -30 Вт 6 -35 Вт Напряжение 0, 9 -1, 5 В 0, 9 -1, 4 В

Эволюция технических характеристик ЦП Intel Pentium 4 (64 бита + 2 ядра) Intel Pentium 4 Кодовое название Prescott-2 M Smithfield Дата выпуска 2005 Архитектура 64 бита Шина данных 64 бита Шина адреса 64 (действительно 36) бита Макс. объём памяти 64 Гбайт Кэш L 1 16 кбайт + 12 Kµops 2 x 16 кбайт + 12 Kµops Кэш L 2 2048 кбайт 2 x 1024 кбайт Тактовая частота 3 -3, 6 ГГц 2, 8 -3, 2 ГГц FSB 800 МГц QDR SIMD MMX, SSE, SSE 2, SSE 3 SMT/SMP Hyper-Threading Два ядра Техпроцесс 90 нм Число транзисторов 169 млн. 230 млн. TDP 84 -115 Вт 95 -130 Вт Напряжение 1, 2 В Площадь кристалла 135 мм² 206 мм² Сокет LGA 775

Эволюция технических характеристик ЦП Intel Core Duo (первый двухядерный для ноутбуков) Intel Core Duo Кодовое название Yonah Дата выпуска 2006 Архитектура 32 бита Шина данных 64 бита Шина адреса 32 бита Макс. объём памяти 4 Гбайт Кэш L 1 32 + 32 кбайт Кэш L 2 2048 кбайт общий Тактовая частота 1, 06 -2, 33 ГГц FSB 667 МГц SIMD MMX, SSE 2, SSE 3 SMT/SMP Два ядра Техпроцесс 65 нм Число транзисторов 151 млн. TDP 9 -31 Вт Напряжение 0, 9 -1, 3 В Площадь кристалла 91 мм² Сокет Socket 479

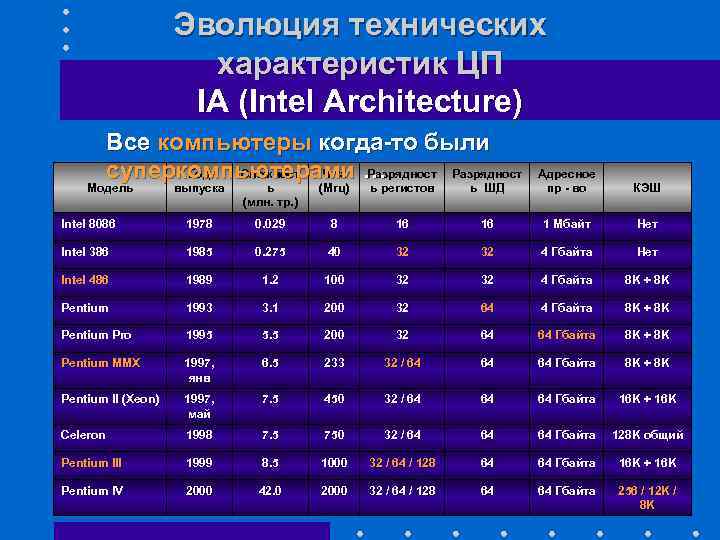

Эволюция технических характеристик ЦП IA (Intel Architecture) Все компьютеры когда-то были Год Сложност Ч-та Разрядност суперкомпьютерами … выпуска ь (млн. тр. ) (Мгц) ь регистов ь ШД Адресное пр - во КЭШ Intel 8086 1978 0. 029 8 16 16 1 Мбайт Нет Intel 386 1985 0. 275 40 32 32 4 Гбайта Нет Intel 486 1989 1. 2 100 32 32 4 Гбайта 8 K + 8 K Pentium 1993 3. 1 200 32 64 4 Гбайта 8 K + 8 K Pentium Pro 1995 5. 5 200 32 64 64 Гбайта 8 K + 8 K Pentium MMX 1997, янв 6. 5 233 32 / 64 64 Гбайта 8 K + 8 K Pentium II (Xeon) 1997, май 7. 5 450 32 / 64 32 64 64 Гбайта 16 K + 16 K Celeron 1998 7. 5 750 32 / 64 32 64 64 Гбайта 128 K общий Pentium III 1999 8. 5 1000 32 / 64 / 128 32 64 64 Гбайта 16 K + 16 K Pentium IV 2000 42. 0 2000 32 / 64 / 128 64 64 Гбайта 256 / 12 K / 8 K Модель

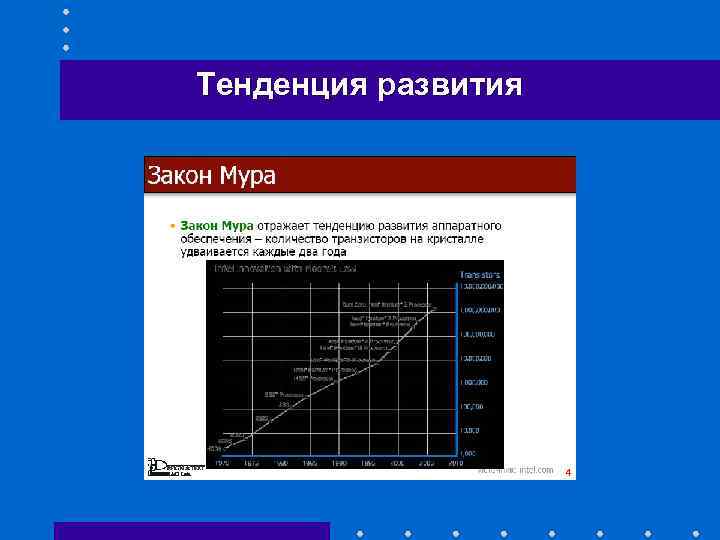

Тенденция развития

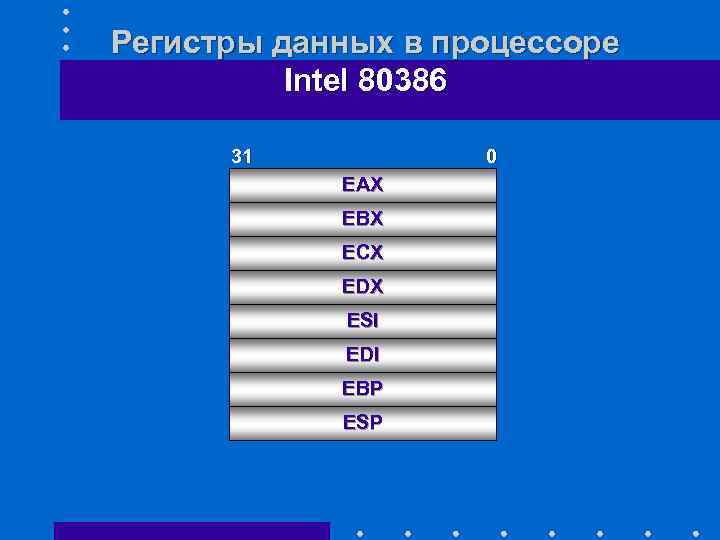

Регистры данных в процессоре Intel 80386 31 0 EAX EBX ECX EDX ESI EDI EBP ESP

Регистры данных в процессоре Intel 80486 31 0 79 64 0 EAX ST(0) EBX ST(1) ECX ST(2) EDX ST(3) ESI ST(4) EDI ST(5) EBP ST(6) ESP ST(7)

Логическая структура внутренней кэш-памяти процессора Intel 80486 (Основной массив) Тэги + индекс 28 бит Строки 16 байт T 0 / 0 T 1 / 0 L 1 / 0 T 2 / 0 L 2 / 0 T 3 / 0 L 1 / 1 T 2 / 1 L 2 / 1 T 3 / 1 L 3 / 1 . . . . T 0 / 127 T 1 / L 0 / 127 T 2 / 127 T 3 / L 2 / 127 Сквозная запись L 1 Обратная запись L 2 L 0 / 1 T 1 / 1 Набор 1 L 3 / 0 T 0 / 1 Набор 0 Кэш-попадание cache hit (свойство локальности программ) Кэш-промах cache miss L 0 / 0 127 L 1 / 127 L 3 / 127 Набор 127 Алгоритм LRU – least recently used Замещение наименее используемой информации

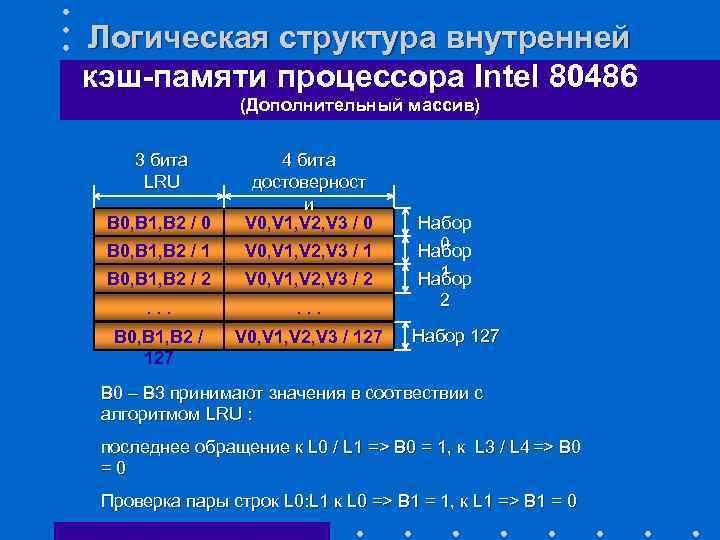

Логическая структура внутренней кэш-памяти процессора Intel 80486 (Дополнительный массив) 3 бита LRU B 0, B 1, B 2 / 0 4 бита достоверност и V 0, V 1, V 2, V 3 / 0 B 0, B 1, B 2 / 1 V 0, V 1, V 2, V 3 / 1 B 0, B 1, B 2 / 2 V 0, V 1, V 2, V 3 / 2 . . . B 0, B 1, B 2 / 127 V 0, V 1, V 2, V 3 / 127 Набор 0 Набор 1 Набор 2 Набор 127 B 0 – B 3 принимают значения в соотвествии с алгоритмом LRU : последнее обращение к L 0 / L 1 => B 0 = 1, к L 3 / L 4 => B 0 =0 Проверка пары строк L 0: L 1 к L 0 => B 1 = 1, к L 1 => B 1 = 0

Стратегия замены строки внутренней кэш-памяти Начало Все 4 строки верны ? Не т Замена неверной строки Да B 0 = 0 ? Да Не т Да B 1 = 0 ? Не т Замена L 0 B 2 = 0 ? Да Замена L 1 Замена L 2 Не т Замена L 3

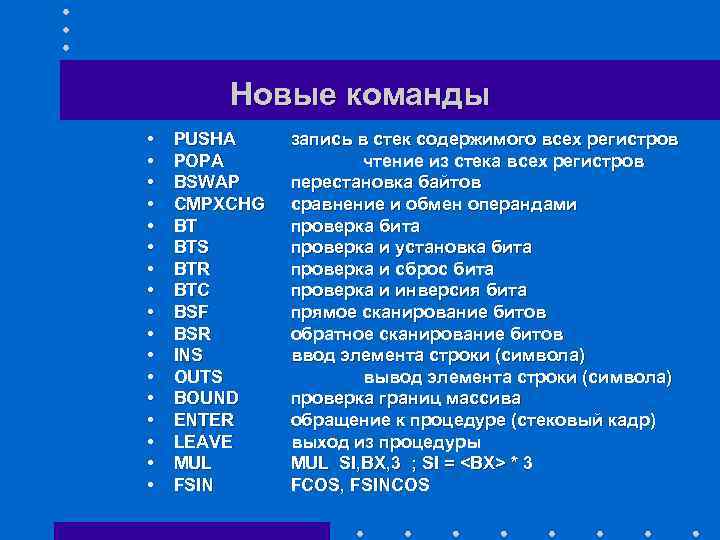

Новые команды • • • • • PUSHA POPA BSWAP CMPXCHG BT BTS BTR BTC BSF BSR INS OUTS BOUND ENTER LEAVE MUL FSIN запись в стек содержимого всех регистров чтение из стека всех регистров перестановка байтов сравнение и обмен операндами проверка бита проверка и установка бита проверка и сброс бита проверка и инверсия бита прямое сканирование битов обратное сканирование битов ввод элемента строки (символа) вывод элемента строки (символа) проверка границ массива обращение к процедуре (стековый кадр) выход из процедуры MUL SI, BX, 3 ; SI = <BX> * 3 FCOS, FSINCOS

Эволюция обработки данных ЦП Intel 8086 –> Intel Pentium IV SISD Single Instruction Single Data SIMD Single Instruction Multiply Data Обработка целых чисел Intel 80386 Обработка чисел с «плавающей точкой» Обработка группы целых чисел (MMX) Обработка группы чисел с «плавающей точкой» (SSE) Мультимедийные наборы команд 1985 Intel 80486 Pentium Pro 1989 1995 Pentium MMX 1997 янв ян Pentium II 1997 май Pentium III 1999 Pentium IV 2000 Процессор MMX Multi Media Extension Intel Pentium MMX 1997 год SSE Streaming SIMD Extension Intel Pentium III 1999 год

Регистры данных в процессоре Pentium MMX 79 63 0 MM 1 MM 2 MM 3 MM 4 MM 5 63 Целые типы данных 0 8 x bytes 4 x 16 -bit 2 x 32 -bit 1 x 64 -bit MM 6 MM 7 Регистры блоков FPU (ST(0) – ST(7)) и MMX (MM 0 – MM 7)

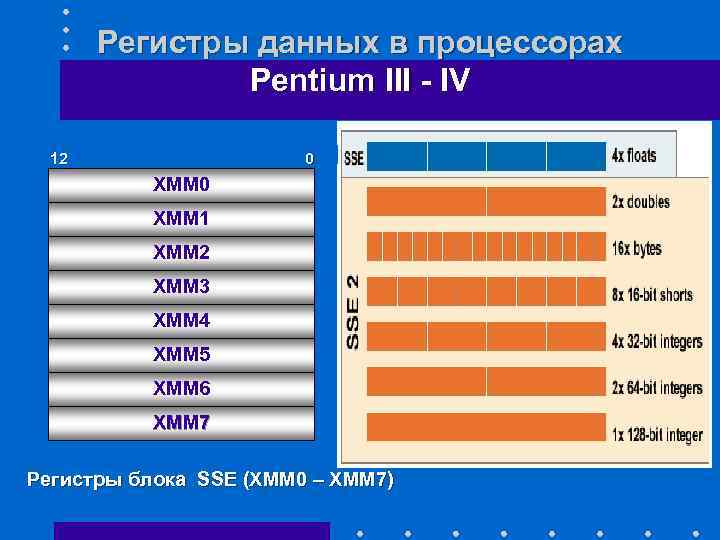

Регистры данных в процессорах Pentium III - IV 12 7 0 XMM 1 XMM 2 XMM 3 XMM 4 XMM 5 XMM 6 XMM 7 Регистры блока SSE (XMM 0 – XMM 7)

Команды SSE Пример выполнения команды SIMD ADDPS xmm 0, xmm 1 X 3 X 2 X 1 X 0 XMM 0 Y 3 Y 2 Y 1 Y 0 XMM 1 X 3 + Y 3 X 2 + Y 2 X 1 + Y 1 X 0 + Y 0 XMM 0

Расширение наборов команд SSE Intel Pentium IV

Новая команда CPUID определяет наличие FPU, MMX и SSE Intel 80486 - New! mov eax, 1 cpuid test edx, 1 ; bit #0 => FPU jz no_fpu … ; FPU есть! no_fpu: test edx, 800000 h ; bit #23 => MMX jz no_mmx … ; MMX есть! no_mmx: test edx, 2000000 h ; bit #25 => SSE jz no_sse … ; SSE => есть! no_sse: … iaxmm. inc – макросы всех новых ком ко

CISC и RISC процессоры CISC - Complex Instruction Set Computers RISC - Reduced Instruction Set Computers Термин «сокращённый» в названии описывает тот факт, что сокращён объём (и время) работы, выполняемый каждой отдельной инструкцией — как максимум один цикл доступа к памяти, — тогда как сложные инструкции CISC-процессоров могут требовать сотен циклов доступа к памяти для своего выполнения.

Суперскалярная и VLIW архитектура СУПЕРСКАЛЯРНАЯ АРХИТЕКТУРА (начиная с Pentium использована СУПЕРСКАЛЯРНАЯ АРХИТЕКТУРА в семействе x 86) - распараллеливание исполнения команд между несколькими устройствами исполнения, причём решение о параллельном исполнении двух или более команд принимается аппаратурой процессора на этапе исполнения. Эффективное использование такой архитектуры требует этапе исполнения специальной оптимизации машинного кода в компиляторе для генерации пар независимых команд (когда результат одной команды не является аргументом другой). АРХИТЕКТУРА VLIW (very long instruction word — очень длинное VLIW слово команды) - отличается от суперскалярной архитектуры тем, что решение о распараллеливании принимается не аппаратурой на этапе исполнения, а компилятором на этапе генерации кода. Команды очень исполнения, а компилятором на этапе генерации кода длинны и содержат явные инструкции по распараллеливанию нескольких субкоманд на несколько устройств исполнения. Разработка эффективного компилятора для VLIW является сложнейшей задачей. Преимущество VLIW перед суперскалярной архитектурой заключается в том, что компилятор может быть более развитым, нежели устройства управления процессора, и он способен хранить больше контекстной информации для принятия более верных решений по оптимизации.

CISC = суперскалярная RISC Наиболее широко используемые в настольных архитектура компьютерах процессоры архитектуры x 86 ранее являлись CISC-процессорами, однако новые процессоры, начиная с Intel 486 DX, являются CISCпроцессоры, начиная с Intel 486 DX, процессорами с RISC-ядром. Они непосредственно перед исполнением преобразуют CISC-инструкции x 86 процессоров в более простой набор внутренних инструкций RISC. После того, как процессоры архитектуры x 86 были переведены на суперскалярную RISCбыли переведены на архитектуру, можно сказать, что подавляющее большинство существующих ныне процессоров основаны на архитектуре RISC.

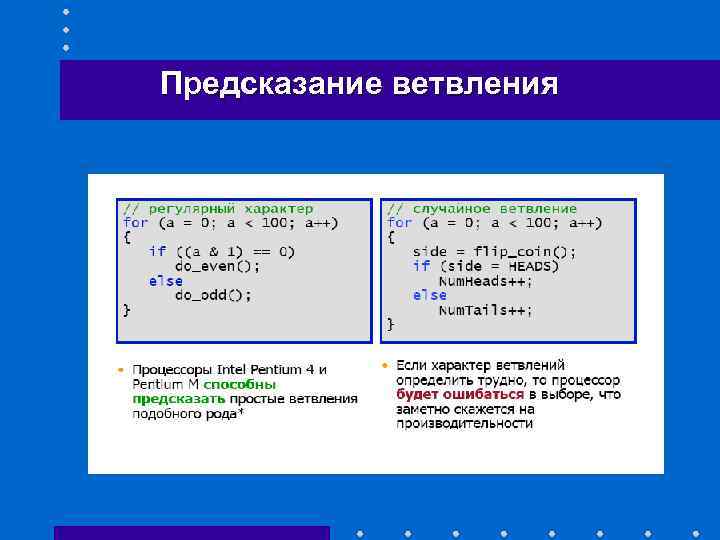

Новая микроархитектура Pentium IV Net. Burst (пакетно-сетевая) • Гарвардская структура с разделением потоков команд и данных; • суперскалярная архитектура, обеспечивающая одновременное выполнение нескольких команд в параллельно работающих исполнительных устройствах; • динамическое изменение последовательности команд (выполнение команд с опережением – спекулятивное выполнение); • конвейерное исполнение команд; • предсказание направления ветвлений.

Архитектура центрального процессора Pentium IV Дешифратор команд Память микропрограмм Блок трансляции адреса команд КЭШ-память Блок трассировки и микрокоманд предск. ветвлений Блок распр. регистров Очередь микрокоманд 126 декодированных команд Блок распределения микрокоманд БФА – блок формирователь адреса БРЗ – блок регистров замещения (128) БФАБРЗ FPUMMXSSE ALUALUБРЗБФА Шина данных Кэш-память данных (L 1) 8 Кбайт Блок трансляции адреса данных Данны е Кэш-память (L 2) 256 Кбайт Блок системного интерфейса СШ Команды

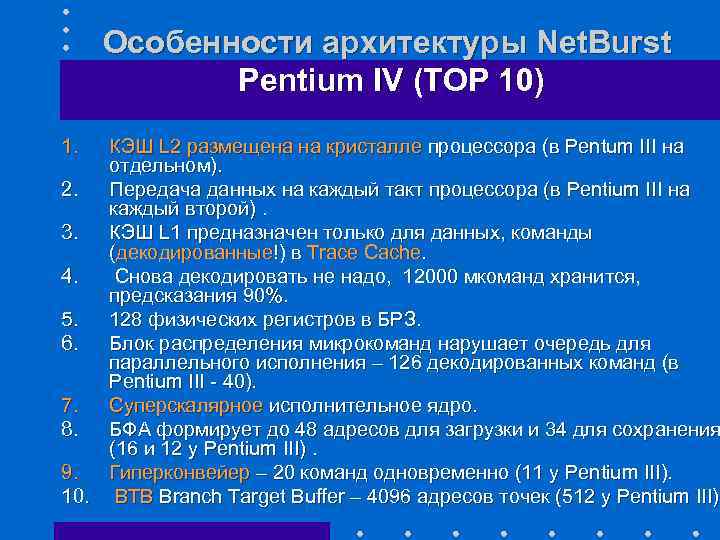

Особенности архитектуры Net. Burst Pentium IV (TOP 10) 1. КЭШ L 2 размещена на кристалле процессора (в Pentum III на отдельном). 2. Передача данных на каждый такт процессора (в Pentium III на каждый второй). 3. КЭШ L 1 предназначен только для данных, команды (декодированные!) в Trace Cache. 4. Снова декодировать не надо, 12000 мкоманд хранится, предсказания 90%. 5. 128 физических регистров в БРЗ. 6. Блок распределения микрокоманд нарушает очередь для параллельного исполнения – 126 декодированных команд (в Pentium III - 40). 7. Суперскалярное исполнительное ядро. 8. БФА формирует до 48 адресов для загрузки и 34 для сохранения (16 и 12 у Pentium III). 9. Гиперконвейер – 20 команд одновременно (11 у Pentium III). 10. BTB Branch Target Buffer – 4096 адресов точек (512 у Pentium III).

Конвейер (pipeline) Три этапа: • Выборка и дешифрация команды (Instruction Fetch and Decode) • Выполнение команды (Instruction Execution) • Завершение команды (Instruction Retirement) Этап t 1 t 2 t 3 t 4 Врем я Fetch/Decode 4 1 2 3 Execution 1 Execution 2 Execution 3 Retirement 1 Retirement 2

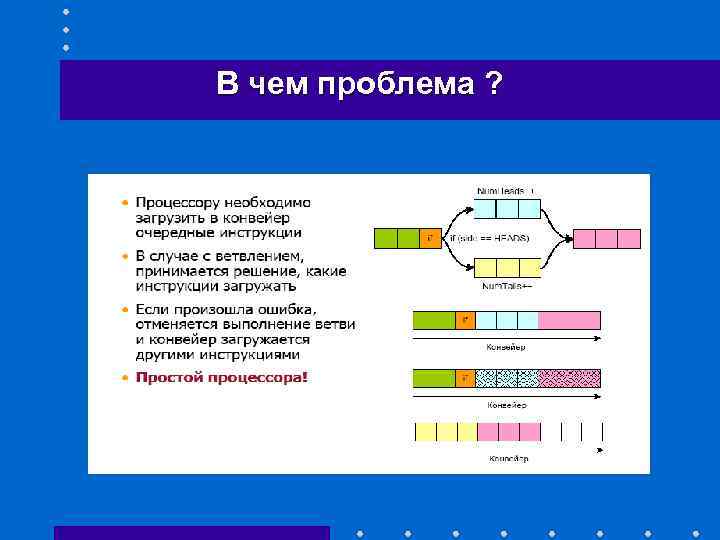

Предсказание ветвления

В чем проблема ?

Команды ММХ Pentium MMX 1 • • • • EMMS (Empty ММХ State) MOVD (МOVe Double word) MOVQ (МOVе Quarter word) PACKSSWB (Pack with Signed Saturation Words to Bytes) PACKSSDW (Pack with Signed Saturation Double Words to Words) PACKUSWB (Pack with Unsigned Saturation Words to Bytes) PADDB (Packed ADDition Bytes) PADDW (Packed ADDition Words) PADDD (Packed ADDition Double words) PADDSB (Packed ADDition with signed Saturation Bytes) PADDSW (Packed ADDition with signed Saturation Words) PADDUSB (Packed ADDition with Unsigned Saturation Bytes) PADDUSW (Packed ADDition with Unsigned Saturation Words)

Команды ММХ Pentium MMX 2 • • • • PAND (Packed logical AND) PANDN (Packed logical AND Not) PCMPEQB (Packed Co. MPare for Equal Byte) PCMPEQW (Packed Co. MPare for Equal Word) PCMPEQD (Packed Co. MPare for Equal Double word) PCMPGTB (Packed Co. MPare for Greater Than Byte) PCMPGTW (Packed Co. MPare for Greater Than Word) PCMPGTD (Packed Co. MPare for Greater Than Double word) PMADDWD (Packed Multiply and ADD Word to Double word) PMULHW (Packed MULtiply and return High Words) PMULLW (Packed MULtiply and return Low Words) POR (Packed logical OR) PSLLW (Packed Shift Left Logical Words)

Команды ММХ Pentium MMX 3 • • • • PSLLD (Packed Shift Left Logical Double words) PSLULQ (Packed Shift Left Logical Quarter word) PSRAW (Packed Shift Right Arithmetic Words) PSRAD (Packed Shift Right Arithmetic Double words) PSRLW (Packed Shift Right Logical Words) PSRLD (Packed Shift Right Logical Double words) PSRLQ (Packed Shift Right Logical Quarter word) PSUBB (Packed Subtraction Bytes) PSUBW (Packed Subtraction Words) PSUBD (Packed Subtraction Double words) PSUBSB (Packed Subtraction with signed Saturation Bytes) PSUBSW (Packed Subtraction with signed Saturation Words) PSUBUSB (Packed Subtraction with Unsigned Saturation Bytes)

Команды ММХ Pentium MMX 4 • • PSUBUSW (Packed Subtraction with Unsigned Saturation Words) PUNPCKHBW (Unpack High Packed Bytes to Words) PUNPCKHWD (Unpack High Packed Words to Double words) РUNРСКHDQ (Unpack High Packed Double words to Quarter word) PUNPCKLBW (Unpack Low Packed Bytes to Words) PUNPCKLWD (Unpack Low Packed Words to Double words) PUNPCKLDQ (Unpack Low Packed Double words to Quarter word) PXOR (Packed logical Exclusive OR)

Команды ММХ Pentium III • • • • MASKMOVQ (Byte Маsk Write). . MOVNTQ (MOVE 64 bits Non Temporal) PAVGB/PAVGW (Packed Average) PEXTRW (Extract Word) PINSRW (Insert Word) PMAXUB (return Packed MAXimum Unsigned integer Byte) PMAXSW (return Packed MAXimum Signed integer Word) PMINUB (return Packed MINimum Unsigned integer Byte) PMINSW (return Packed MINimum Signed integer Word) PM 0 VMSKB (Packed MOVe Byte Ma. SK to integer) PMULHUW (Packed MULtiply апd return High Unsigned Words) PREFETCH (PREFETCH) SFENCE (Store FENCE) PSADBW (Packed Sum of Absolute Differences) PSHUFW (Packed Shuffle Word)

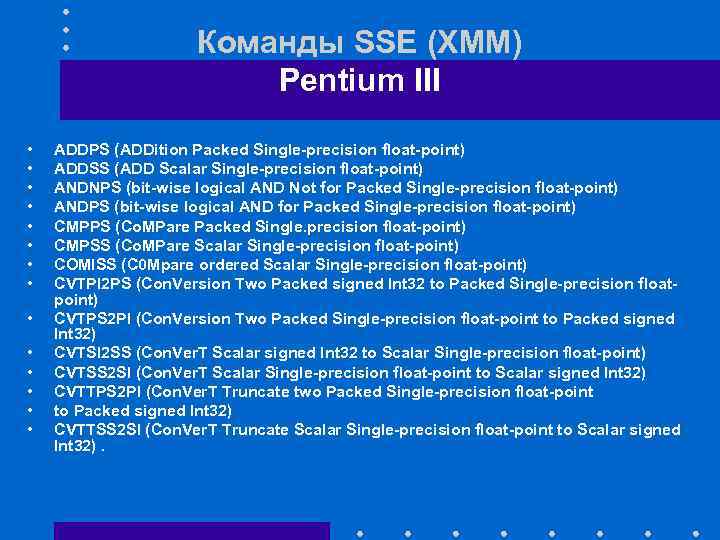

Команды SSE (XMM) Pentium III • • • • ADDPS (ADDition Packed Single-precision float-point) ADDSS (ADD Scalar Single-precision float-point) ANDNPS (bit-wise logical AND Not for Packed Single-precision float-point) ANDPS (bit-wise logical AND for Packed Single-precision float-point) CMPPS (Co. MPare Packed Single. precision float-point) CMPSS (Co. MPare Scalar Single-precision float-point) COMISS (C 0 Mpare ordered Scalar Single-precision float-point) СVTPI 2 PS (Con. Version Two Packed signed Int 32 to Packed Single-precision floatpoint) CVTPS 2 PI (Con. Version Two Packed Single-precision float-point to Packed signed Int 32) СVTSI 2 SS (Con. Ver. T Scalar signed Int 32 to Scalar Single-precision float-point) CVTSS 2 SI (Соn. Ver. Т Scalar Single-precision float-point to Scalar signed Int 32) СVТТРS 2 РI (Con. Ver. T Truncate two Packed Single-precision float-point to Packed signed Int 32) СVTTSS 2 SI (Con. Ver. T Truncate Scalar Single-precision float-point to Scalar signed Int 32).

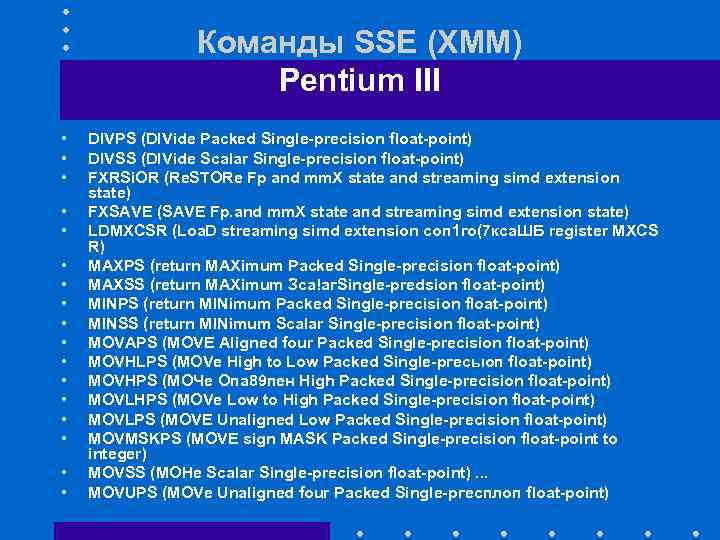

Команды SSE (XMM) Pentium III • • • • • DIVPS (DIVide Packed Single-precision float-point) DIVSS (DIVide Scalar Single-precision float-point) FXRSi. OR (Re. STORe Fp and mm. X state and streaming simd extension state) FXSAVE (SAVE Fp. and mm. Х state апd streaming simd extension state) LDMXCSR (Loa. D streaming simd extension соп 1 го(7 кса. ШБ register MXCS R) MAXPS (return MAXimum Packed Single-precision float-point) MAXSS (return MAXimum Зса!аг. Single-predsion float-point) MINPS (return MINimum Packed Single-precision float-point) MINSS (return MINimum Scalar Single-precision float-point) MOVAPS (MOVE Aligned four Packed Single-precision float-point) MOVHLPS (MOVe High to Low Packed Single-ргесыоп float-point) MOVHPS (МОЧе Опа 89 пен High Packed Single-precision float-point) MOVLHPS (MOVe Low to High Packed Single-precision float-point) MOVLPS (MOVE Unaligned Low Packed Single-precision float-point) MOVMSKPS (MOVE sign MASK Packed Single-precision float-point to integer) MOVSS (МОНе Scalar Single-precision float-point). . . MOVUPS (MOVe Unaligned four Packed Single-ргесплоп float-point)

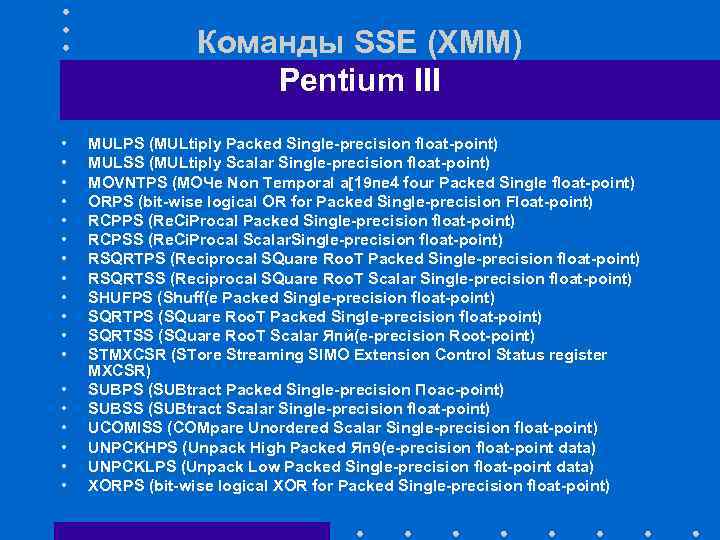

Команды SSE (XMM) Pentium III • • • • • MULPS (MULtiply Packed Single-precision float-point) MULSS (MULtiply Scalar Single-precision f. Ioat-point) MOVNTPS (МОЧе Non Temporal а[19 пе 4 four Packed Single float-point) ORPS (bit-wise logical OR for Packed Single-precision Float-point) RCPPS (Re. Ci. Procal Packed Single-precision float-point) RCPSS (Re. Ci. Procal Scalar. Single-precision float-point) RSQRTPS (Reciprocal SQuare Roo. T Packed Single-precision float-point) RSQRTSS (Reciprocal SQuare Roo. T Scalar Single-precision f. Ioat-point) SHUFPS (Shuff(e Packed Single-precision float-point) SQRTPS (SQuare Roo. T Packed Single-precision float-point) SQRTSS (SQuare Roo. T Scalar Япй(е-precision Root-point) STMXCSR (STore Streaming SIMO Extension Control Status register MXCSR) SUBPS (SUBtract Packed Single-precision Поас-point) SUBSS (SUBtract Scalar Single-precision float-point) UCOMISS (COMpare Unordered Scalar Single-precision float-point) UNPCKHPS (Unpack High Packed Яп 9(е-precision float-point data) UNPCKLPS (Unpack Low Packed Single-precision float-point data) XORPS (bit-wise logical XOR for Packed Single-precision float-point)

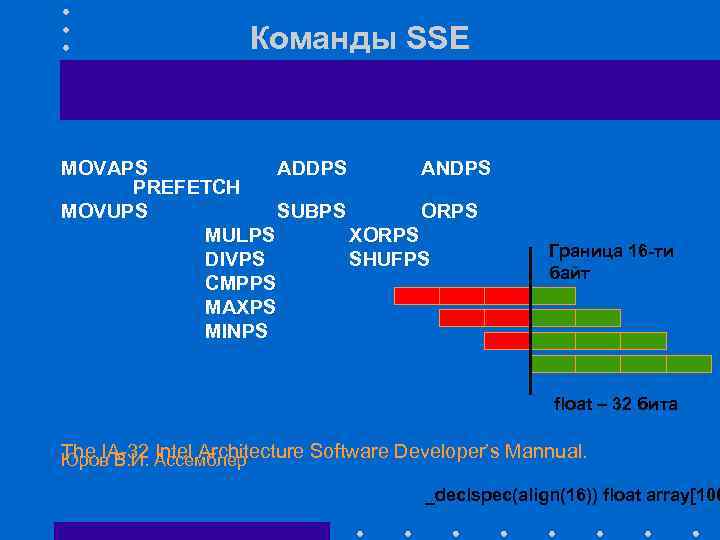

Команды SSE MOVAPS ADDPS ANDPS PREFETCH MOVUPS SUBPS ORPS MULPS XORPS DIVPS SHUFPS CMPPS MAXPS MINPS Граница 16 -ти байт float – 32 бита The IA-32 Intel Architecture Software Developer’s Mannual. Юров В. И. Ассемблер _declspec(align(16)) float array[100

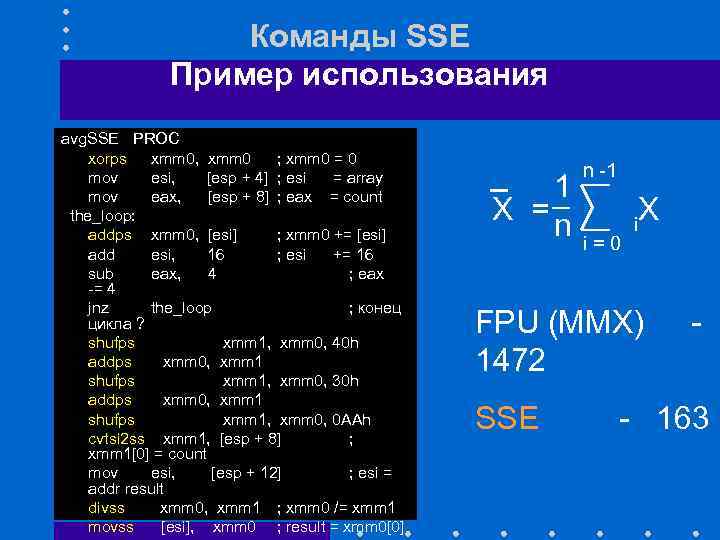

Команды SSE Пример использования avg. SSE PROC xorps xmm 0, xmm 0 ; xmm 0 = 0 mov esi, [esp + 4] ; esi = array mov eax, [esp + 8] ; eax = count the_loop: addps xmm 0, [esi] ; xmm 0 += [esi] add esi, 16 ; esi += 16 sub eax, 4 ; eax -= 4 jnz the_loop ; конец цикла ? shufps xmm 1, xmm 0, 40 h addps xmm 0, xmm 1 shufps xmm 1, xmm 0, 30 h addps xmm 0, xmm 1 shufps xmm 1, xmm 0, 0 AAh cvtsi 2 ss xmm 1, [esp + 8] ; xmm 1[0] = count mov esi, [esp + 12] ; esi = addr result divss xmm 0, xmm 1 ; xmm 0 /= xmm 1 movss [esi], xmm 0 ; result = xmm 0[0] 1 X = n n -1 i=0 i X FPU (MMX) 1472 SSE - - 163

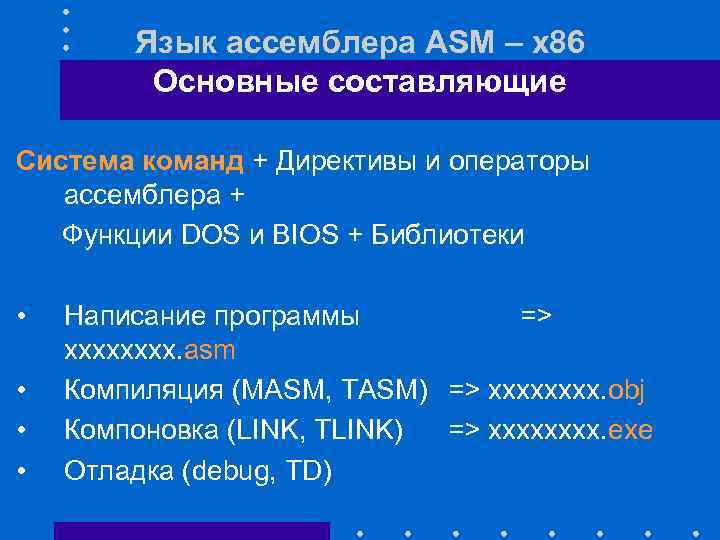

Язык ассемблера ASM – x 86 Основные составляющие Система команд + Директивы и операторы ассемблера + Функции DOS и BIOS + Библиотеки • • Написание программы => xxxx. asm Компиляция (MASM, TASM) => xxxx. obj Компоновка (LINK, TLINK) => xxxx. exe Отладка (debug, TD)

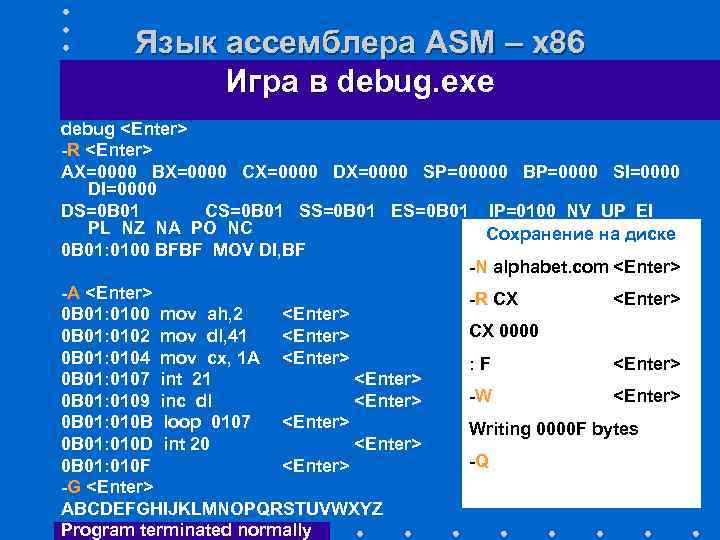

Язык ассемблера ASM – x 86 Игра в debug. exe debug <Enter> -R <Enter> AX=0000 BX=0000 CX=0000 DX=0000 SP=00000 BP=0000 SI=0000 DI=0000 DS=0 B 01 CS=0 B 01 SS=0 B 01 ES=0 B 01 IP=0100 NV UP EI PL NZ NA PO NC Сохранение на диске 0 B 01: 0100 BFBF MOV DI, BF -N alphabet. com <Enter> -A <Enter> -R CX <Enter> 0 B 01: 0100 mov ah, 2 <Enter> CX 0000 0 B 01: 0102 mov dl, 41 <Enter> 0 B 01: 0104 mov cx, 1 A <Enter> : F <Enter> 0 B 01: 0107 int 21 <Enter> -W <Enter> 0 B 01: 0109 inc dl <Enter> 0 B 01: 010 B loop 0107 <Enter> Writing 0000 F bytes 0 B 01: 010 D int 20 <Enter> -Q 0 B 01: 010 F <Enter> -G <Enter> ABCDEFGHIJKLMNOPQRSTUVWXYZ Program terminated normally

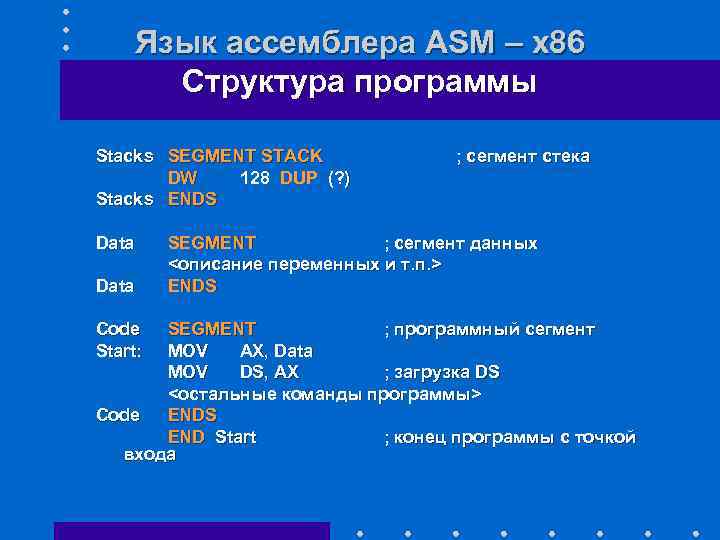

Язык ассемблера ASM – x 86 Структура программы Stacks SEGMENT STACK DW 128 DUP (? ) Stacks ENDS Data Code Start: ; сегмент стека SEGMENT ; сегмент данных <описание переменных и т. п. > ENDS SEGMENT ; программный сегмент MOV AX, Data MOV DS, AX ; загрузка DS <остальные команды программы> Code ENDS END Start ; конец программы с точкой входа

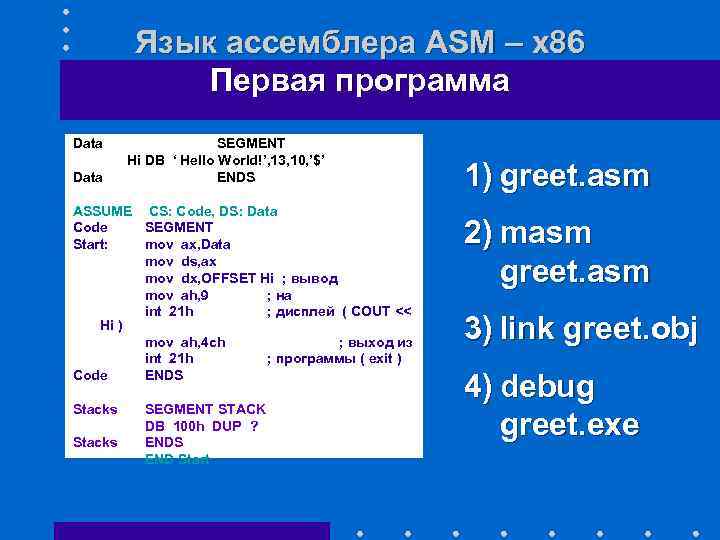

Язык ассемблера ASM – x 86 Первая программа Data SEGMENT Hi DB ‘ Hello World!’, 13, 10, ’$’ Data ENDS ASSUME CS: Code, DS: Data Code SEGMENT Start: mov ax, Data mov ds, ax mov dx, OFFSET Hi ; вывод mov ah, 9 ; на int 21 h ; дисплей ( COUT << Hi ) mov ah, 4 ch ; выход из int 21 h ; программы ( exit ) Code ENDS Stacks SEGMENT STACK DB 100 h DUP ? ENDS END Start 1) greet. asm 2) masm greet. asm 3) link greet. obj 4) debug greet. exe

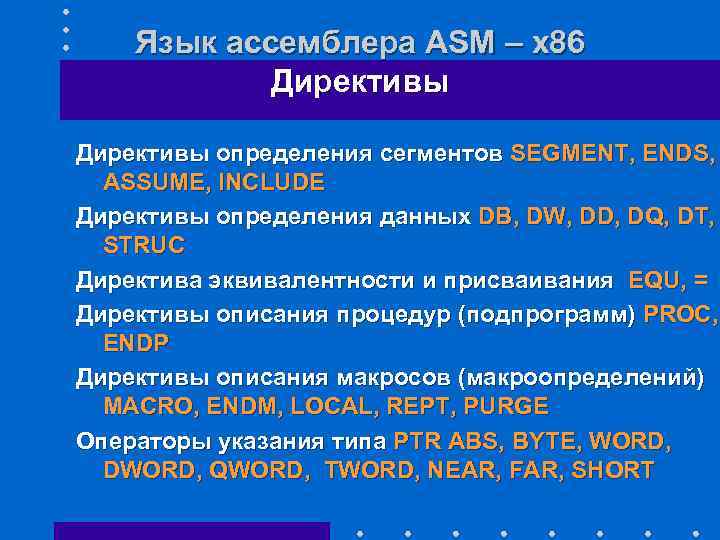

Язык ассемблера ASM – x 86 Директивы определения сегментов SEGMENT, ENDS, ASSUME, INCLUDE Директивы определения данных DB, DW, DD, DQ, DT, STRUC Директива эквивалентности и присваивания EQU, = Директивы описания процедур (подпрограмм) PROC, ENDP Директивы описания макросов (макроопределений) MACRO, ENDM, LOCAL, REPT, PURGE Операторы указания типа PTR ABS, BYTE, WORD, DWORD, QWORD, TWORD, NEAR, FAR, SHORT

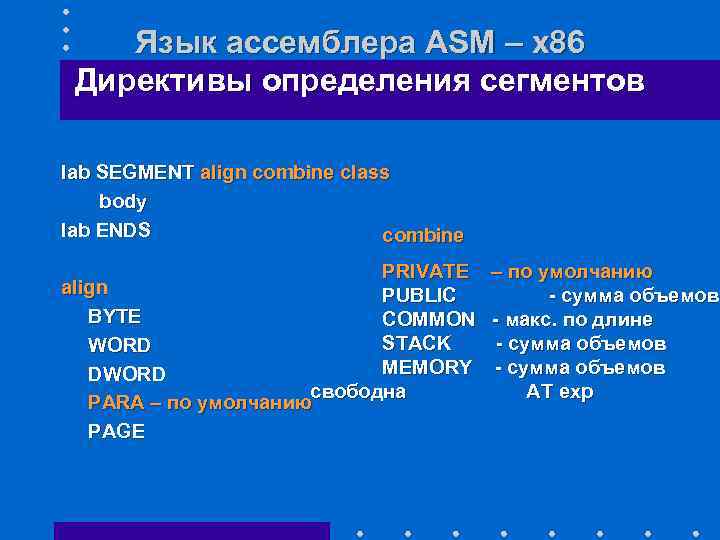

Язык ассемблера ASM – x 86 Директивы определения сегментов lab SEGMENT align combine class body lab ENDS combine PRIVATE – по умолчанию align PUBLIC - сумма объемов BYTE COMMON - макс. по длине STACK - сумма объемов WORD MEMORY - сумма объемов DWORD свободна AT exp PARA – по умолчанию PAGE

Язык ассемблера ASM – x 86 Примеры директив определения данных Str Rem Big C Float Stud Fam Gr Mark Stud DB DB DW DD DT ‘a’, ‘b’, ‘c’ 0, 0, 0, 0 ? -35 32. 1074 Str DB ‘abc’ Rem DB 6 DUP (0) -32768 - 65535 -2 ^ 31 - 2 ^ 32 – 1 STRUC DB 20 DUP (? ) ; фамилия DW ? ; номер группы DB 5 DUP (? ) ; оценки ENDS S Stud 70 (<>) S S + 54 27 S + 81 S + … S + 1863 Mark 0 1 234

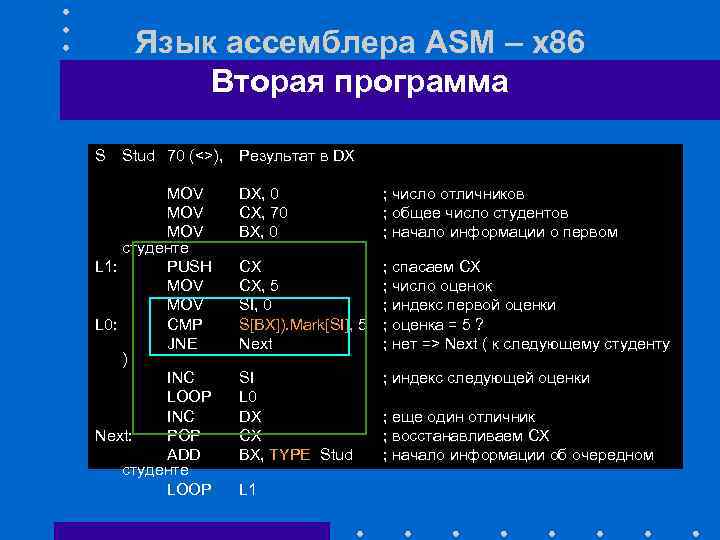

Язык ассемблера ASM – x 86 Вторая программа S Stud 70 (<>), MOV MOV студенте L 1: PUSH MOV L 0: CMP JNE ) INC LOOP INC Next: POP ADD студенте LOOP Результат в DX DX, 0 CX, 70 BX, 0 ; число отличников ; общее число студентов ; начало информации о первом CX CX, 5 SI, 0 S[BX]). Mark[SI], 5 Next ; спасаем CX ; число оценок ; индекс первой оценки ; оценка = 5 ? ; нет => Next ( к следующему студенту SI L 0 DX CX BX, TYPE Stud ; индекс следующей оценки L 1 ; еще один отличник ; восстанавливаем CX ; начало информации об очередном

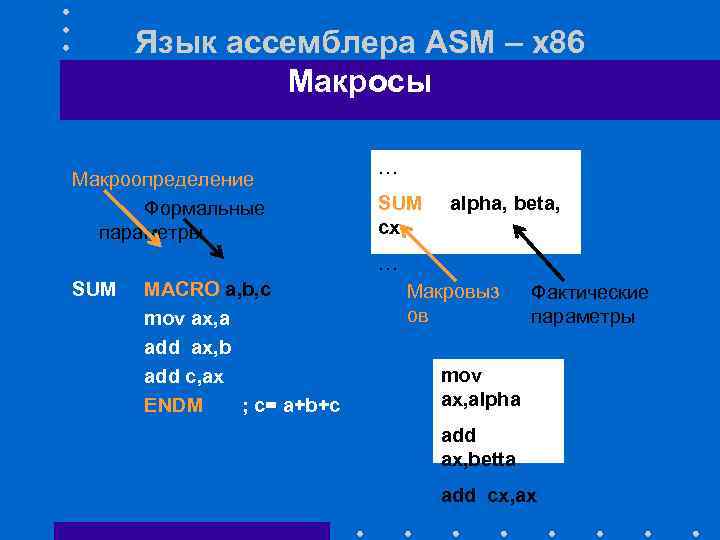

Язык ассемблера ASM – x 86 Макросы Макроопределение Формальные параметры … SUM cx alpha, beta, … SUM MACRO a, b, c mov ax, a add ax, b add c, ax ENDM ; c= a+b+c Макровыз ов Фактические параметры mov ax, alpha add ax, betta add cx, ax

Язык ассемблера ASM – x 86 Пример использования макросов Макрос настройки ds на сегмент данных init_ds macro mov ax, data mov ds, ax endm Макрос вывода строки на экран. out_str macro str mov ah, 09 h mov dx, offset str int 21 h endm Макрос конца программы exit macro mov ah, 4 ch int 21 h endm Code Start: q SEGMENT mov ax, Data mov ds, ax mov dx, OFFSET Hi ; вывод mov ah, 9 ; на int 21 h ; дисплей ( COUT << Hi ) mov ah, 4 ch ; выход из int 21 h ; программы ( exit ) Code ENDS Code Start: Code SEGMENT init_ds out_str Hi exit ENDS

Язык ассемблера ASM – x 86 Макросы – блоки повторения REPT 3 SHR ax, 1 ENDM SHR SHR ax, 1 IRP X, <AX, BX, CX> PUSH X ENDM PUSH AX PUSH BX PUSH CX IRPC p, 17 W ADD AX, p ENDM ADD ADD AX, 1 AX, 7 AX, W

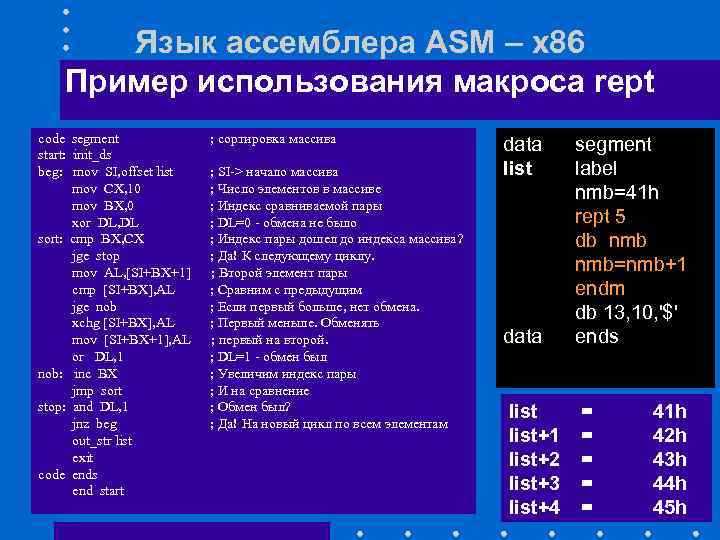

Язык ассемблера ASM – x 86 Пример использования макроса rept code segment start: init_ds beg: mov SI, offset list mov CX, 10 mov BX, 0 xor DL, DL sort: cmp BX, CX jge stop mov AL, [SI+BX+1] cmp [SI+BX], AL jge nob xchg [SI+BX], AL mov [SI+BX+1], AL or DL, 1 nob: inc BX jmp sort stop: and DL, 1 jnz beg out_str list exit code ends end start ; сортировка массива ; SI-> начало массива ; Число элементов в массиве ; Индекс сравниваемой пары ; DL=0 - обмена не было ; Индекс пары дошел до индекса массива? ; Да! К следующему циклу. ; Второй элемент пары ; Сравним с предыдущим ; Если первый больше, нет обмена. ; Первый меньше. Обменять ; первый на второй. ; DL=1 - обмен был ; Увеличим индекс пары ; И на сравнение ; Oбмен был? ; Да! На новый цикл по всем элементам data list data segment label nmb=41 h rept 5 db nmb=nmb+1 endm db 13, 10, '$' ends list+1 list+2 list+3 list+4 = = = 41 h 42 h 43 h 44 h 45 h

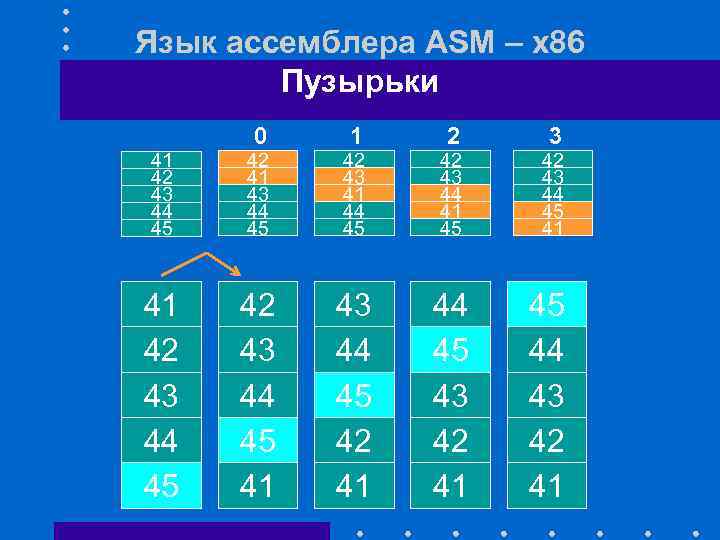

Язык ассемблера ASM – x 86 Пузырьки 0 1 2 3 41 42 43 44 45 42 41 43 44 45 42 43 41 44 45 42 43 44 41 45 42 43 44 45 41 41 42 43 44 45 41 43 44 45 42 41 44 45 43 42 41 45 44 43 42 41

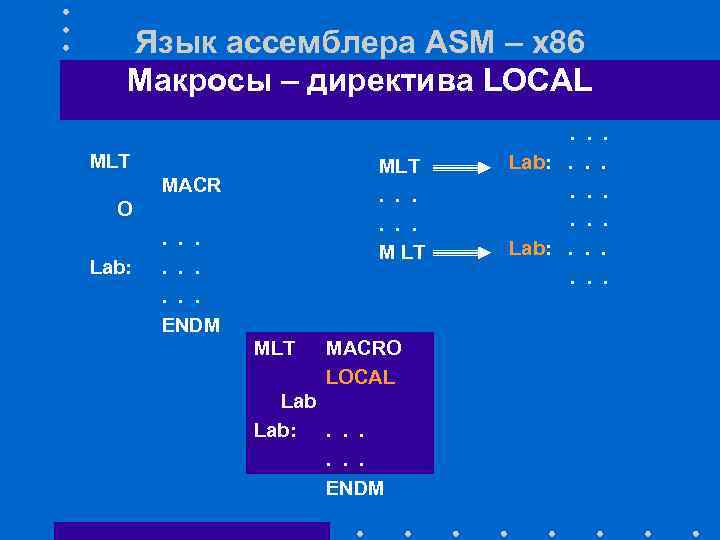

Язык ассемблера ASM – x 86 Макросы – директива LOCAL MLT. . . M LT MACR O Lab: . . ENDM MLT MACRO LOCAL Lab: . . . ENDM . . . Lab: . . .

Язык ассемблера ASM – x 86 Макросы – директива LOCAL (пример) R 1 = R 1 mod R 2 while (R 1 >= R 2) R 1 = R 1 - R 2; Mod M 0: MACRO R 1, R 2 LOCAL M 0, M 1 CMP R 1, R 2 JB M 1 SUB R 1, R 2 JMP M 0 M 1: ENDM Mod AX, BX ? ? 0017: CMP JB ? ? 0018 SUB AX, BX JMP ? ? 0017 ? ? 0018: Mod CX, DX DX ? ? 001 A CX, DX ? ? 0019: CMP CX, JB SUB JMP ? ? 001 A:

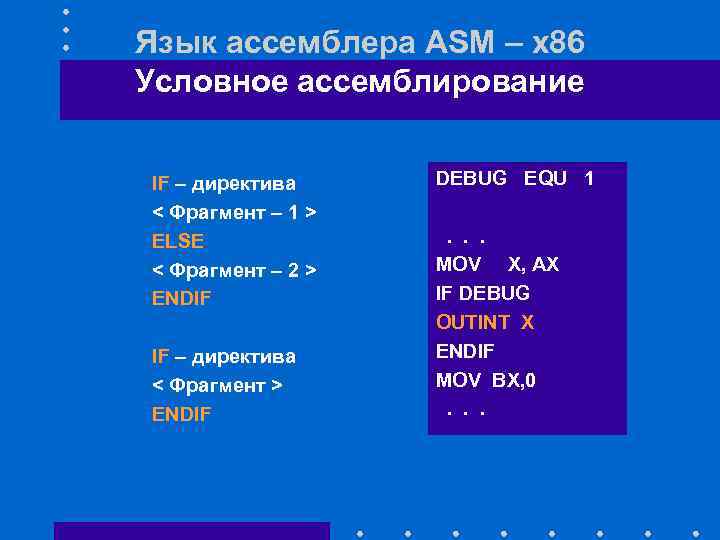

Язык ассемблера ASM – x 86 Условное ассемблирование IF – директива < Фрагмент – 1 > ELSE < Фрагмент – 2 > ENDIF IF – директива < Фрагмент > ENDIF DEBUG EQU 1 . . . MOV X, AX IF DEBUG OUTINT X ENDIF MOV BX, 0 . . .

Язык ассемблера ASM – x 86 Упрощенные директивы сегментации. model тип модели ; (TINY, SMALL, MEDIUM, COMPACT, LARGE, FLAT). CODE. DATA. STACK [размер]. CONST . model small. stack 100 h. data Hi DB ‘ Hello World!’, 13, 10, ’$’. code start: mov ax, @data mov ds, ax mov dx, OFFSET Hi ; вывод mov ah, 9 ; на int 21 h ; дисплей mov ah, 4 ch ; выход из int 21 h ; программы end start

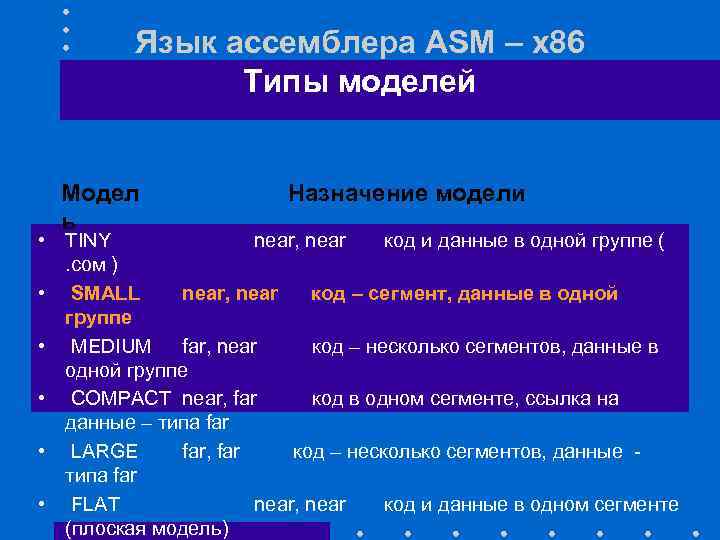

Язык ассемблера ASM – x 86 Типы моделей Модел ь Назначение модели • TINY near, near код и данные в одной группе (. сом ) • SMALL near, near код – сегмент, данные в одной группе • MEDIUM far, near код – несколько сегментов, данные в одной группе • COMPACT near, far код в одном сегменте, ссылка на данные – типа far • LARGE far, far код – несколько сегментов, данные типа far • FLAT near, near код и данные в одном сегменте (плоская модель)

Язык ассемблера ASM – x 86 Подпрограммы (процедуры) Описание Имя PROC Тело п/п RET Имя ENDP Вызов CALL Имя extern имя : тип, … , имя : тип public имя, … , имя – переменной, процедуры, константы тип – переменной : byte, word, dword, … - процедуры: near или far - константы: abs

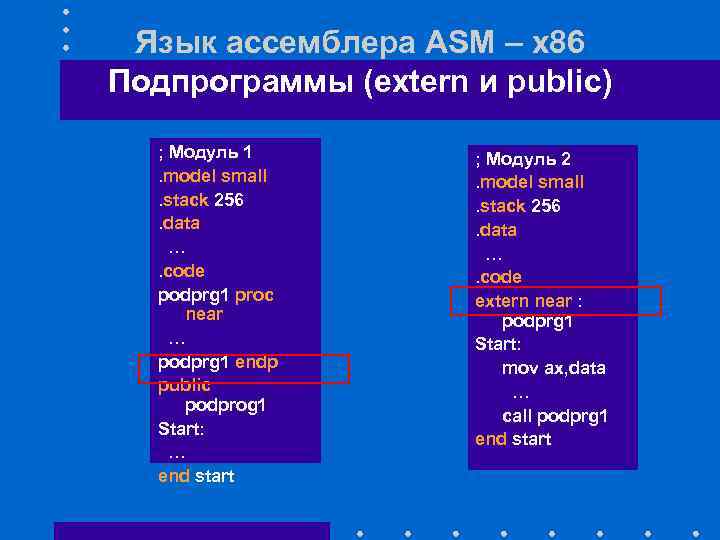

Язык ассемблера ASM – x 86 Подпрограммы (extern и public) ; Модуль 1. model small. stack 256. data …. code podprg 1 proc near … podprg 1 endp public podprog 1 Start: … end start ; Модуль 2. model small. stack 256. data …. code extern near : podprg 1 Start: mov ax, data … call podprg 1 end start

Язык ассемблера ASM – x 86 Пример использования подпрограммы Где разместить? c = max (a, b) + max (5, a 1) max (x, y) x => AX, y => BX Результат => AX … MOV AX, a MOV BX, b CALL max ; AX = max (a, b) MOV c, AX MOV AX, 5 max PROC FAR CMP AX, BX JGE Max 1 MOV AX, BX Max 1: RET max ENDP MOV BX, a DEC BX CALL max ; AX = max (5, a-1) ADD c, AX a-1) ; c = max (a, b) + max (5, …

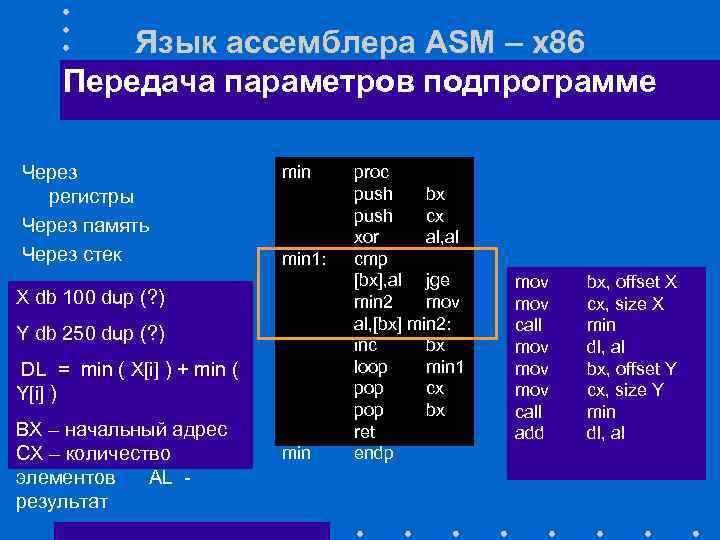

Язык ассемблера ASM – x 86 Передача параметров подпрограмме Через регистры Через память Через стек min 1: X db 100 dup (? ) Y db 250 dup (? ) DL = min ( X[i] ) + min ( Y[i] ) BX – начальный адрес СХ – количество элементов AL результат min proc push bx push cx xor al, al cmp [bx], al jge min 2 mov al, [bx] min 2: inc bx loop min 1 pop cx pop bx ret endp mov call mov mov call add bx, offset X cx, size X min dl, al bx, offset Y cx, size Y min dl, al

Язык ассемблера ASM – x 86 Передача параметров через стек pushp 1 pushp 2 … pushp. K call our_proc Lab: Lab p. K. . . p 2 p 1 ; Пролог our_proc BP mov SP PROC push BP, SP. . . (BP) Lab p. K. . . p 2 p 1 ; Эпилог. . . mov SP, BP POP BP RET N our_proc SP, ENDP BP BP + 4 enter 0, 0 ; новый пролог leave ; новый эпилог

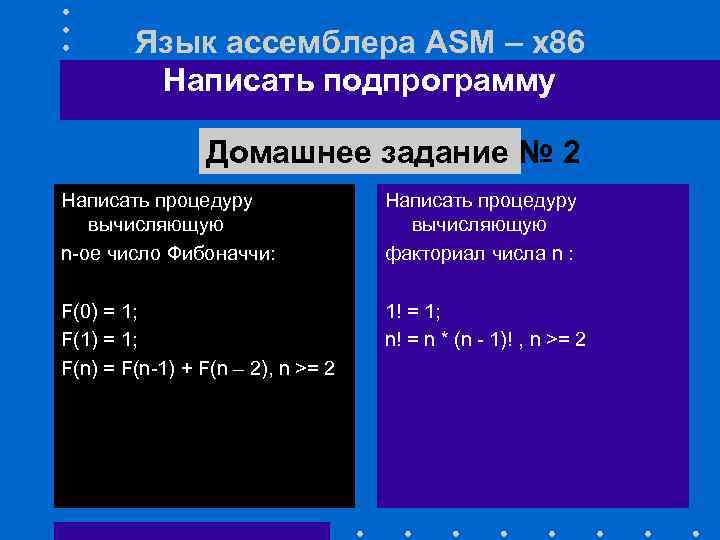

Язык ассемблера ASM – x 86 Написать подпрограмму Домашнее задание № 2 Написать процедуру вычисляющую n-ое число Фибоначчи: Написать процедуру вычисляющую факториал числа n : F(0) = 1; F(1) = 1; F(n) = F(n-1) + F(n – 2), n >= 2 1! = 1; n! = n * (n - 1)! , n >= 2

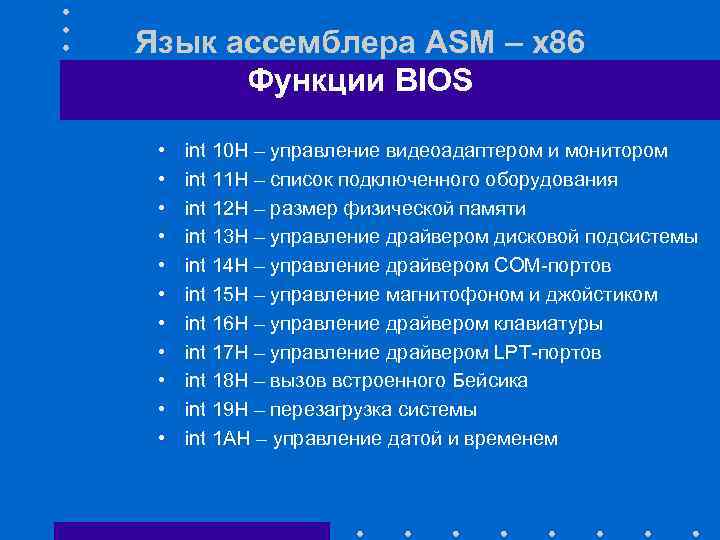

Язык ассемблера ASM – x 86 Функции BIOS • • • int 10 H – управление видеоадаптером и монитором int 11 H – список подключенного оборудования int 12 H – размер физической памяти int 13 H – управление драйвером дисковой подсистемы int 14 H – управление драйвером COM-портов int 15 H – управление магнитофоном и джойстиком int 16 H – управление драйвером клавиатуры int 17 H – управление драйвером LPT-портов int 18 H – вызов встроенного Бейсика int 19 H – перезагрузка системы int 1 AH – управление датой и временем

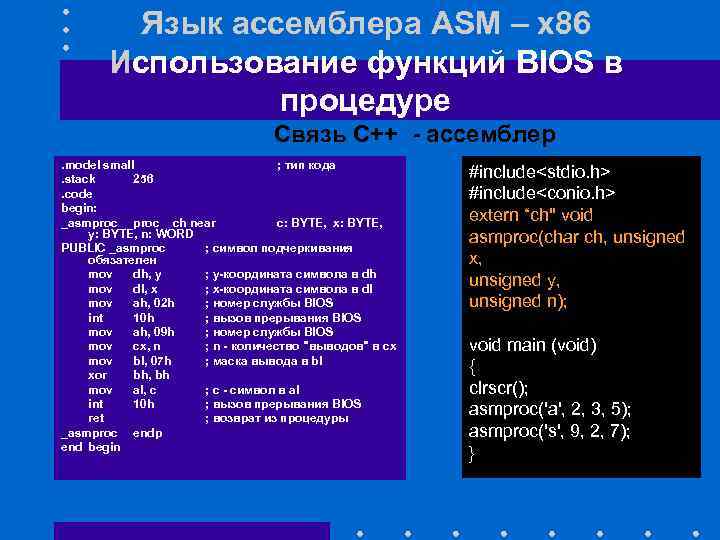

Язык ассемблера ASM – x 86 Использование функций BIOS в процедуре Связь С++ - ассемблер. model small ; тип кода. stack 256. code begin: _asmproc ch near c: BYTE, x: BYTE, y: BYTE, n: WORD PUBLIC _asmproc ; символ подчеркивания обязателен mov dh, y ; y-координата символа в dh mov dl, x ; x-координата символа в dl mov ah, 02 h ; номер службы BIOS int 10 h ; вызов прерывания BIOS mov ah, 09 h ; номер службы BIOS mov cx, n ; n - количество "выводов" в cx mov bl, 07 h ; маска вывода в bl xor bh, bh mov al, c ; c - символ в al int 10 h ; вызов прерывания BIOS ret ; возврат из процедуры _asmproc endp end begin #include<stdio. h> #include<conio. h> extern “ch" void asmproc(char ch, unsigned x, unsigned y, unsigned n); void main (void) { clrscr(); asmproc('a', 2, 3, 5); asmproc('s', 9, 2, 7); }

Язык ассемблера ASM – x 86 Функции DOS – 01 h Get. Char macro ; Ввод символа с клавиатуры. ; На выходе - в al введённый символ. push ax mov ah, 01 h int 21 h pop ax endm

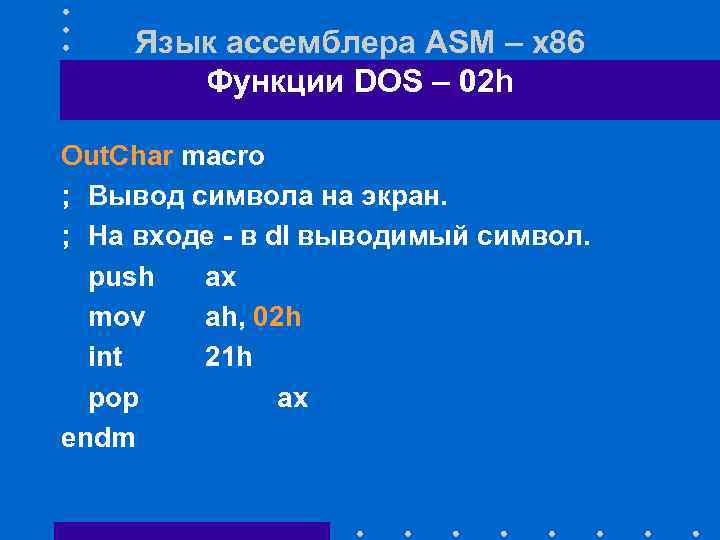

Язык ассемблера ASM – x 86 Функции DOS – 02 h Out. Char macro ; Вывод символа на экран. ; На входе - в dl выводимый символ. push ax mov ah, 02 h int 21 h pop ax endm

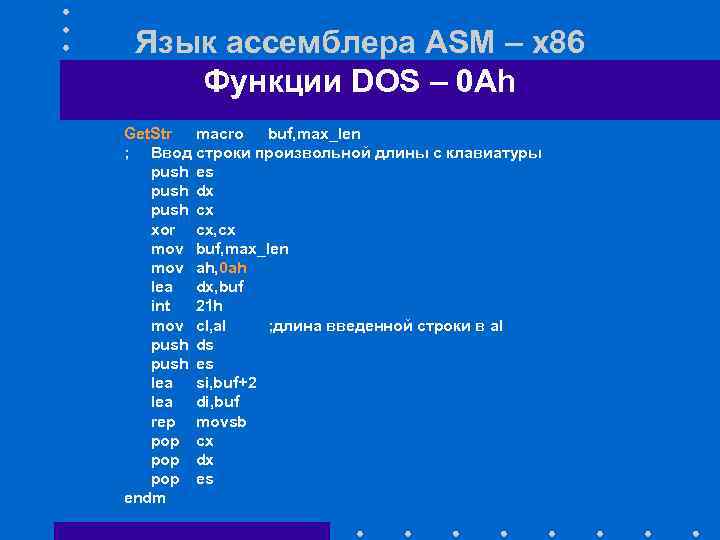

Язык ассемблера ASM – x 86 Функции DOS – 0 Ah Get. Str macro buf, max_len ; Ввод строки произвольной длины с клавиатуры push es push dx push cx xor cx, cx mov buf, max_len mov ah, 0 ah lea dx, buf int 21 h mov cl, al ; длина введенной строки в al push ds push es lea si, buf+2 lea di, buf rep movsb pop cx pop dx pop es endm

Язык ассемблера ASM – x 86 Функции DOS – 09 h Out. Str macro str ; Вывод строки на экран. ; На входе - идентификатор начала выводимой строки str. ; Строка должна заканчиваться символом '$'. ; На выходе- сообщение на экране. push ax mov ah, 09 h lea dx, str ; mov dx, offset str int 21 h pop ax endm

Раздел 2 Многоядерные процессоры и параллельное программирование

1996

Литература – В. В. Воеводин, Вл. В. Воеводин «Параллельные вычисления» – В. П. Гергель «Теория и практика параллельных вычислений» – Barry Wilkinson, Michael Allen «Parallel Programming» – James Reinders «Intel Threading Building Blocks» – Intel Press «Multi-Сore Programming»

Повышение производительности ВМ Принципиально важными решениями в повышении производительности вычислительных систем были: • введение конвейерной организации выполнения команд; • включение в систему команд векторных операций; • распределение вычислений на множество процессоров (ядер). Сочетание этих 3 -х механизмов в архитектуре суперкомпьютера Earth Simulator, состоящего из 5120 векторно-конвейерных процессоров, позволило ему достичь рекордной производительности, которая в 20000 раз превышает производительность современных персональных компьютеров

Многоядерные процессоры и параллельная революция Ключевой момент грядущей «параллельной революции» заключается не в собственно процессорах, а в грядущих радикальных изменениях в программном обеспечении. Оно должно стать таким, чтобы сохранилась возможность использовать преимущества экспоненциального роста производительности процессоров.

Революционер из МТИ профессор Ананд Агарвал С периодом 1, 5 или 2 года удваиваться должно не только число транзисторов (закон Мура), но еще и число ядер на кристалле. Для того чтобы синхронизировать рост числа ядер в соответствии с ростом числа транзисторов, необходимо сохранять простоту ядер, сокращая размеры кэш-памяти, и отказаться от других усовершенствований (суперскалярность, внеочередное исполнение и др. ). Можно представить это так, что ядро возвращается к чистой архитектуре фон Неймана, а система на кристалле вбирает в себя всю инфраструктурную сложность. Правило - KILL (kill if less than linear): некоторый ресурс ядра может наращиваться, если при этом обеспечивается, как минимум, линейный рост производительности. Таким образом можно найти оптимум для разного рода устройств, например кэш-памяти. Если уменьшить тактовую частоту с 4 до 1 ГГц, то вероятность промаха при обращении в стек уменьшается в четыре раза, и стек можно сделать в 16 раз меньше.

Революционер из МТИ профессор Ананд Агарвал После того как выбрана архитектура ядра, следует решить второй вопрос — как объединить между собой ядра. Агарвал считает, что классическая шинная архитектура обречена, ей на смену придет решетчатая инфраструктура (mesh networking). Преимущество решетчатой или ячеистой, сети состоит в том, что она обладает качеством самолечения, продолжая работать в случае выхода из строя узла или межсоединения.

Измерение производительности ВС Единицы измерения производительности вычислительных систем: 1 Mflops (мегафлопс) = 1 миллион оп/сек 1 Gflops (гигафлопс) = 1 миллиард оп/сек 1 Tflops (терафлопс) = 1 триллион оп/сек

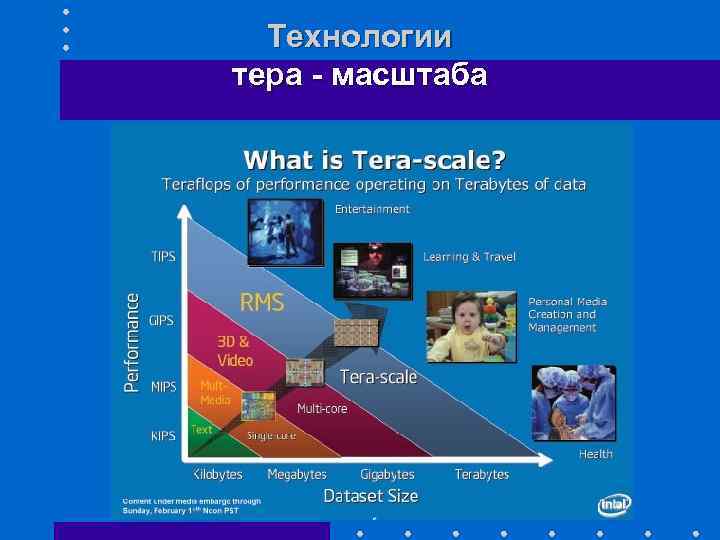

Технологии тера - масштаба

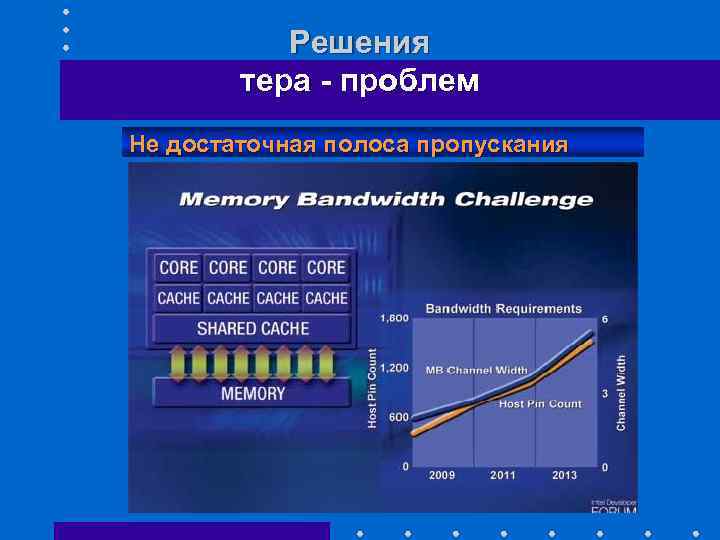

Решения тера - проблем Не достаточная полоса пропускания шины памяти

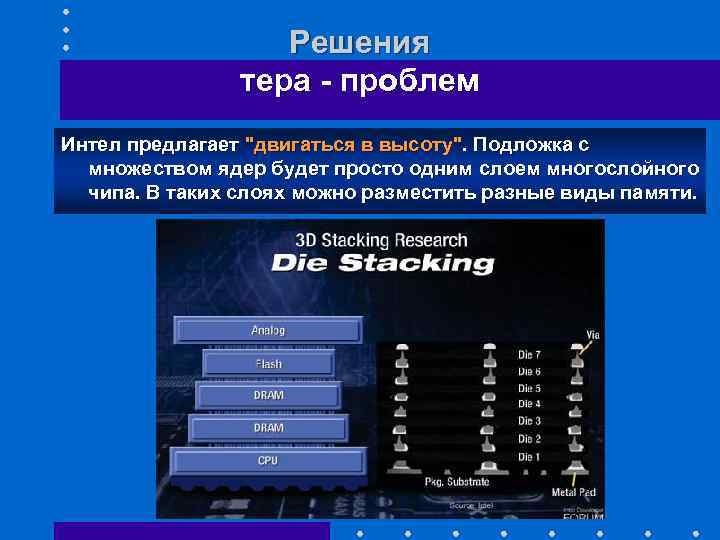

Решения тера - проблем Интел предлагает "двигаться в высоту". Подложка с множеством ядер будет просто одним слоем многослойного чипа. В таких слоях можно разместить разные виды памяти.

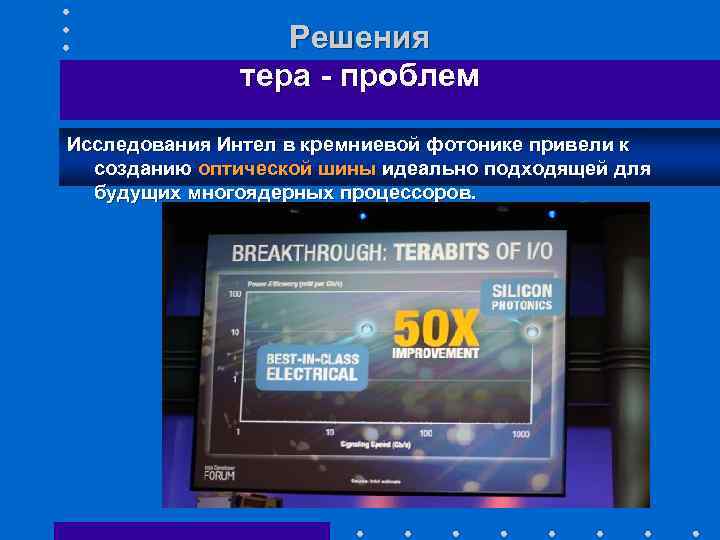

Решения тера - проблем Исследования Интел в кремниевой фотонике привели к созданию оптической шины идеально подходящей для будущих многоядерных процессоров.

Решения для Teraflops Research Chip Процессор Teraflops основан на техпроцессе 65 нм. На 275 квадратных миллиметрах площади подложки находится 100 миллионов транзисторов.

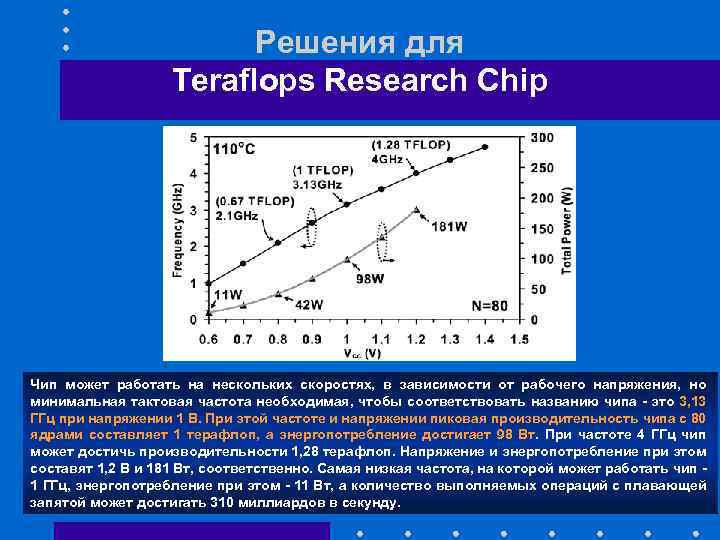

Решения для Teraflops Research Chip Чип может работать на нескольких скоростях, в зависимости от рабочего напряжения, но минимальная тактовая частота необходимая, чтобы соответствовать названию чипа - это 3, 13 ГГц при напряжении 1 В. При этой частоте и напряжении пиковая производительность чипа с 80 ядрами составляет 1 терафлоп, а энергопотребление достигает 98 Вт. При частоте 4 ГГц чип может достичь производительности 1, 28 терафлоп. Напряжение и энергопотребление при этом составят 1, 2 В и 181 Вт, соответственно. Самая низкая частота, на которой может работать чип - 1 ГГц, энергопотребление при этом - 11 Вт, а количество выполняемых операций с плавающей запятой может достигать 310 миллиардов в секунду.

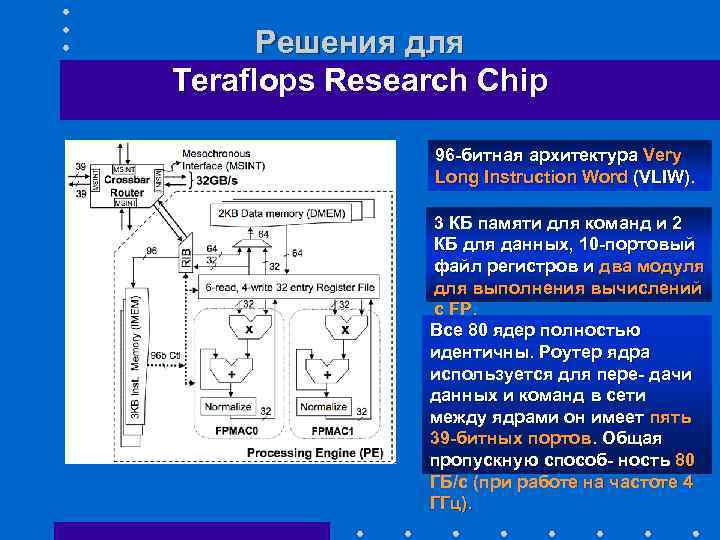

Решения для Teraflops Research Chip Каждое ядро состоит из блока обработки Processing Engine (PE), выполняющего все вычисления и пяти-портового роутера, обеспечивающего прохождение данных от одного ядра к другому.

Решения для Teraflops Research Chip 96 -битная архитектура Very Long Instruction Word (VLIW). 3 КБ памяти для команд и 2 КБ для данных, 10 -портовый файл регистров и два модуля для выполнения вычислений c FP. Все 80 ядер полностью идентичны. Роутер ядра используется для пере- дачи данных и команд в сети между ядрами он имеет пять 39 -битных портов. Общая пропускную способ- ность 80 ГБ/с (при работе на частоте 4 ГГц).

Решения для Teraflops Research Chip Четыре из пяти портов предназначены для связи с другими ядрами. Пятый порт предназначен для связи с памятью на других слоях.

Решения для Teraflops Research Chip Чип teraflop не обычен еще и тем, что все ядра независимы и частотный сигнал должен появляться одновременно только в пределах одного ядра площадью всего 3 кв. мм, а не по всему чипу площадью 275 кв. мм. Каждое ядро процессора поделено на 21 регион, которые могут выключаться независимо друг от друга в зависимости от вида

Решения для Teraflops Research Chip К 2010 году Интел ожидает, что массовыми станут 4 -х ядерные процессоры, а к 2015 - многоядерные, в которых мы и увидим технологии, представ- ленные Интел сейчас. Исследования под знаком "тера" положили начало эре терамасштабов в массовой компьютерной технике.

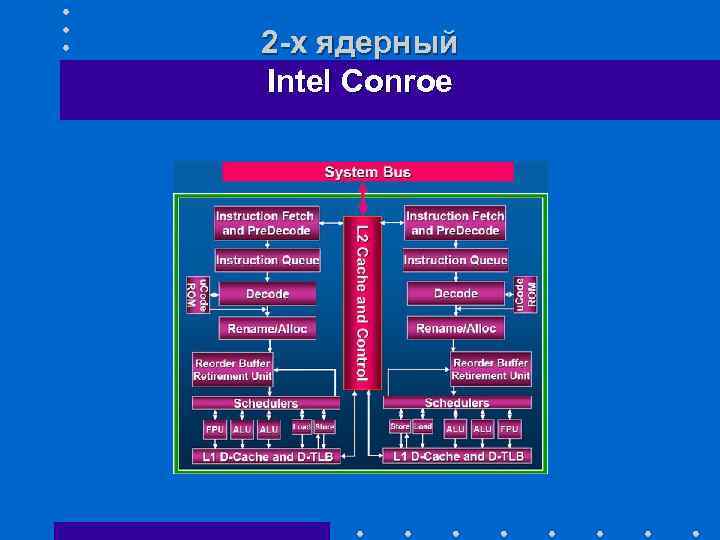

2 -х ядерный Intel Conroe

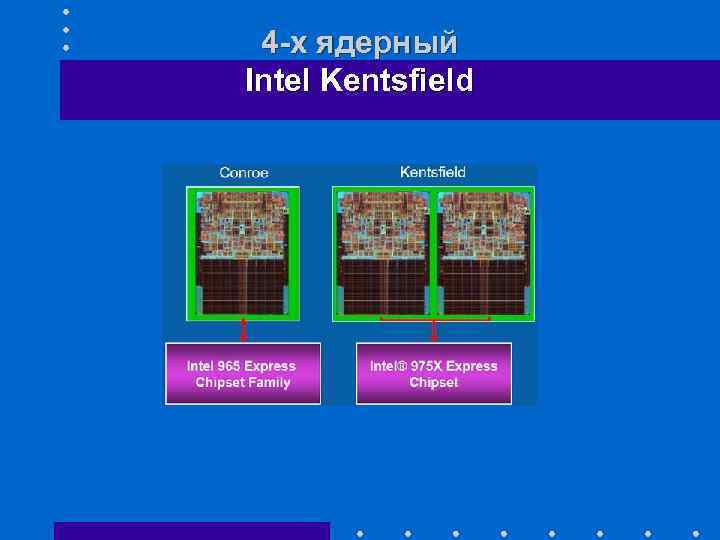

4 -х ядерный Intel Kentsfield

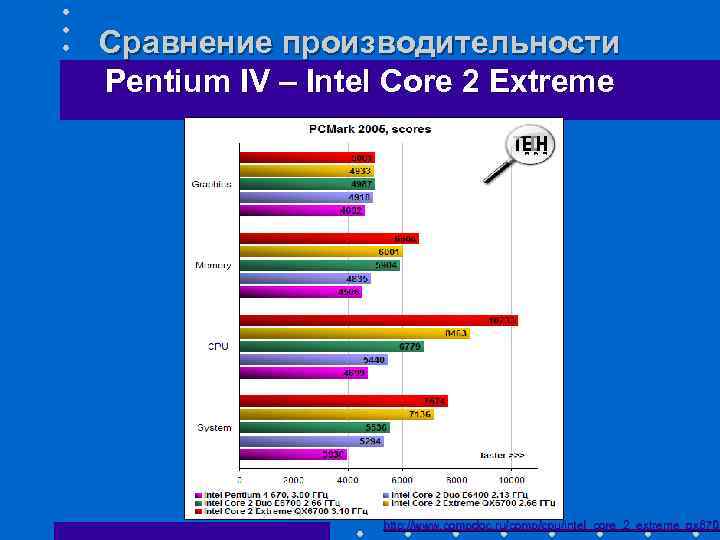

Сравнение производительности Pentium IV – Intel Core 2 Extreme http: //www. compdoc. ru/comp/cpu/intel_core_2_extreme_qx 6700

Архитектура 4 -х ядерного процессора Core 1 Core 2 Core 3 Core 4 CPU / FPU Registers Execution Units L 1 Cache L 2 Cache System Bus RAM

Параллельное программирование Concurrency Revolution Один из ведущих экспертов по современным языкам программирования, сотрудник корпорации Microsoft Херб Саттер (весна 2005 года сразу в двух журналах — Dr. Dobb’s Journal и C/C++ Users Journal ) написал статью «The Free Lunch Is Over A Fundamental Turn Toward Concurrency in Software» Немного позже Саттер с коллегой Джеймсом Ларуссом написали статью «Software and the Concurrency Revolution» Многоядерные машины — наше неизбежное будущее, а потому главная задача заключается в необходимости научиться программировать для них. Новые компьютеры будут все более и более производительными, но программирование не сможет далее развиваться за счет умения «оседлать волну производительности» . Основное направление развития — параллелизм.

Классификация Флинна параллелизм данных и команд

Параллелизм данных и команд (пример)

Основные определения Процесс — отдельная программная задача, которая имеет своё собственное адресное пространство. Поток (нить) (thread) — последовательность логически связанных команд, которая выполняется независимо от других последовательностей команд. • Потоки выполняются в рамках процессов, и разделяют между собой общее адресное пространство (модель работы с общей памятью). • Фактически, поток является функцией программы. • Каждая программа содержит как минимум один поток - функцию main(), которая может создать другие потоки. • Каждый поток имеет свою локальную память, где хранит обрабатываемые данные, промежуточные результаты и состояние процессора.

Процессы и потоки • Один процесс — одна программная задача. • Процесс начинает выполняться с функции main() — своего основного потока. • Потоки могут создавать другие потоки. • Каждый поток имеет доступ к общему сегменту данных (модель с общей памятью) и к своему собственному стеку (локальной памяти потока). • Поток не имеет доступа к чужому стеку. Процесс Стек Поток main() Стек Поток 2 Стек. . . Поток N Сегмент данных

Три уровня представления потоков 1. Потоки пользователя - потоки, создаваемые программистом в коде. Представлены в виде функций. Программист определяет, какие функции будут исполняться в виде потоков. 2. Потоки ядра - потоки, которыми управляет операционная система. Представлены в виде внутренних объектов ОС. Задача ОС - управлять потоками пользователя, исполнять их на процессорах. ОС - посредник между процессорами и программистами. 3. Аппаратные потоки - это такие потоки инструкций, которые исполняются процессором. ОС решает, в какой очередности и сколько времени будут выполняться те или иные потоки.

Жизненный цикл потоков Жизненный

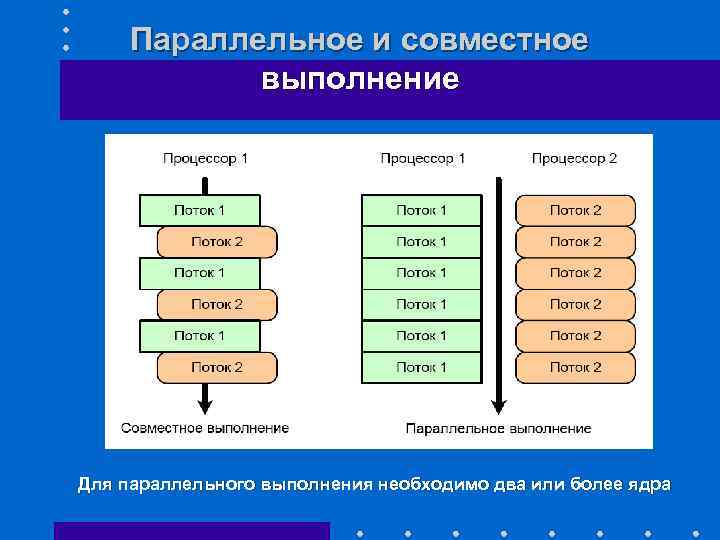

Параллельное и совместное выполнение Для параллельного выполнения необходимо два или более ядра

Проектирование программ • Основная задача проектирования — определиться с подходом, каким образом архитектурно будет реализована параллельная программа. • Несколько подходов к проектированию: – Декомпозиция задач – Декомпозиция данных – Декомпозиция потока данных – Смешанный подход • Декомпозиция — разделение программы на отдельные задачи и определение зависимости между ними.

Декомпозиция задач • Разделение программы на функции, которая она выполняет, называется декомпозицией задач (параллелизм на уровне задач). Это один из простейших подходов к распараллеливанию программы. • Составляется список всех задач (функций), если какие-то из них могут выполняться независимо друг от друга, программист планирует их параллельное выполнение.

Взаимодействие процессов и потоков Синхронизация (обмен данными) Мьютекс (mutual exclusion) Критическая секция Семафор

Синхронизация процессов и потоков Современные операционные системы предлагают широкий набор средств для синхронизации параллельных процессов. Самым простым средством синхронизации одновременно выполняющихся участков кода является ожидание одним процессом (потоком) завершения выполнения другого процесса (потока). Этот же механизм обеспечивает и поддержку выполнения операционной системой асинхронных операций, таких как файловый ввод-вывод или обмен данными по сети. Кроме того, функции ожидания могут использоваться при взаимном оповещении процессов о происходящих событиях.

Взаимное исключение процессов и потоков Мьютекс (от англ. mutex, mutual exclusion) — объект синхронизации, глобальный для операционной системы, может быть использован между различными процессами. Если существует вероятность того, что разные участки программы могут одновременно осуществить модификацию какойнибудь переменной, то необходимо применять защиту этой переменной. Чтобы этого достичь, в операционные системы введен специальный объект — мьютекс. Прежде чем начать изменение переменной, поток должен осуществить захват соответствующего этой переменной мьютекса. Таким образом гарантируется работа только одного участка кода в конкретный момент времени с конкретной переменной.

Критическая секция Когда в одном участке кода необходимо модифицировать несколько глобальных переменных и существует вероятность одновременного выполнения этого кода несколькими потоками, необходимо предусмотреть его защиту. Специально для такого случая операционные системы предлагают организовать соответствующий код в критическую секцию. Критические секции отличаются от мьютексов тем, что один и тот же поток может многократно входить в захваченную им критическую секцию. При попытке повторного захвата мьютекса выполнение потока будет остановлено и может возникнуть так называемый тупик.

Семафор — это системный объект, который представляет собой счетчик. Перед началом работы с ресурсом из набора поток должен обратиться к ассоциированному с ним семафору. Если значение счетчика семафора больше нуля, то поток допускается к работе с ресурсом, а значение счетчика уменьшается на единицу. Если со всеми ресурсами из набора уже ведется работа, то поток будет поставлен в очередь. По завершении использования ресурса каждый поток сообщает об этом семафору, значение его счетчика увеличивается и ресурс снова может быть предоставлен в пользование.

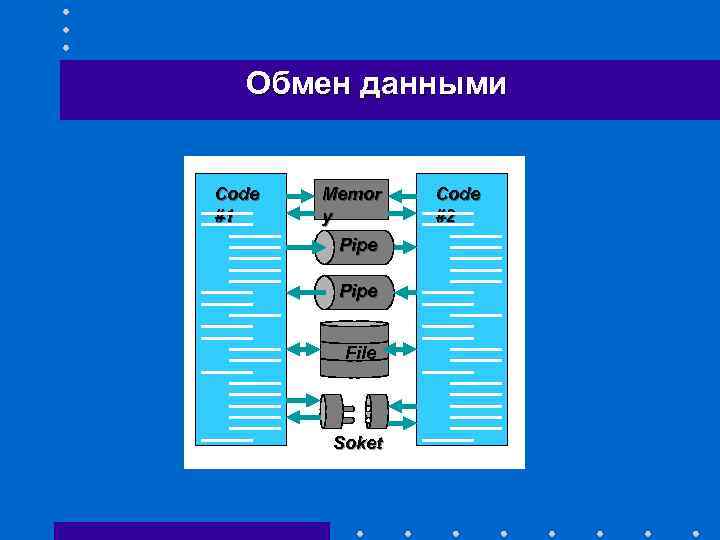

Обмен данными Code #1 Memor y Pipe File Soket Code #2

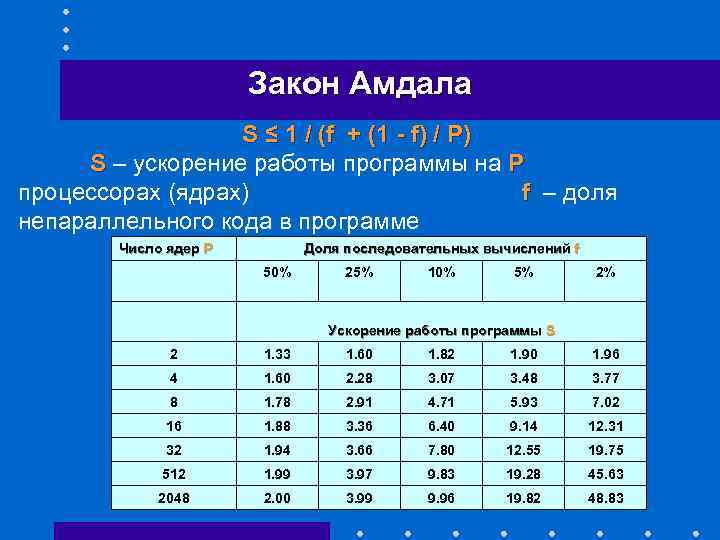

Закон Амдала S ≤ 1 / (f + (1 - f) / P) S – ускорение работы программы на P процессорах (ядрах) f – доля непараллельного кода в программе Число ядер P Доля последовательных вычислений f 50% 25% 10% 5% 2% Ускорение работы программы S 2 1. 33 1. 60 1. 82 1. 90 1. 96 4 1. 60 2. 28 3. 07 3. 48 3. 77 8 1. 78 2. 91 4. 71 5. 93 7. 02 16 1. 88 3. 36 6. 40 9. 14 12. 31 32 1. 94 3. 66 7. 80 12. 55 19. 75 512 1. 99 3. 97 9. 83 19. 28 45. 63 2048 2. 00 3. 99 9. 96 19. 82 48. 83

Параллельное программирование в Windows • Что такое Windows API? • Создание потоков • Синхронизация потоков • Этапы распараллеливания • События Windows

Тип HANDLE • К каждому объекту, создаваемому операционной системой, можно получить доступ по его дескриптору (описатель). Этот дескриптор имеет тип HANDLE (#inlclude <windows. h>) – Можно ссылаться на потоки, процессы, файлы, события, мютексы, семафоры и т. д. • Функции Win. API возвращают дескриптор объекта. • Программист может управлять объектом через его дескриптор.

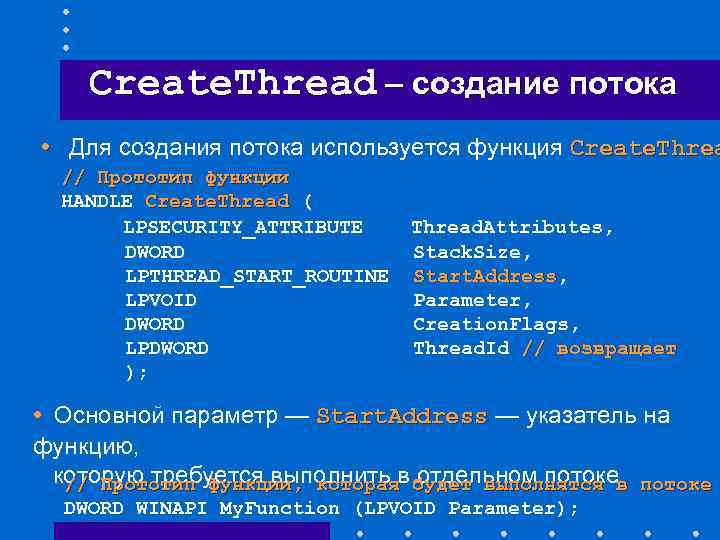

Create. Thread – создание потока • Для создания потока используется функция Create. Threa • // Прототип функции HANDLE Create. Thread ( LPSECURITY_ATTRIBUTE DWORD LPTHREAD_START_ROUTINE LPVOID DWORD LPDWORD ); Thread. Attributes, Stack. Size, Start. Address Parameter, Creation. Flags, Thread. Id // возвращает • Основной параметр — Start. Address — указатель на Start. Address функцию, которую требуется выполнить в будет выполнятся в потоке // Прототип функции, которая отдельном потоке. DWORD WINAPI My. Function (LPVOID Parameter);

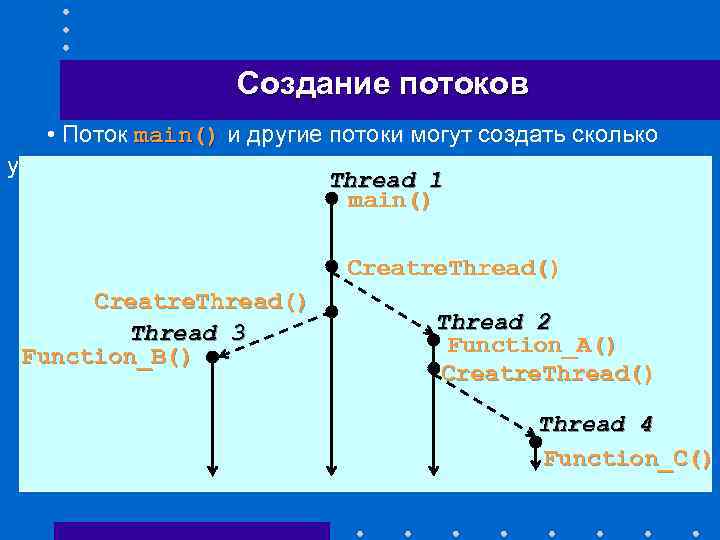

Создание потоков • Поток main() и другие потоки могут создать сколько угодно потоков. Thread 1 main() Creatre. Thread() Thread 3 Function_B() Thread 2 Function_A() Creatre. Thread() Thread 4 Function_C()

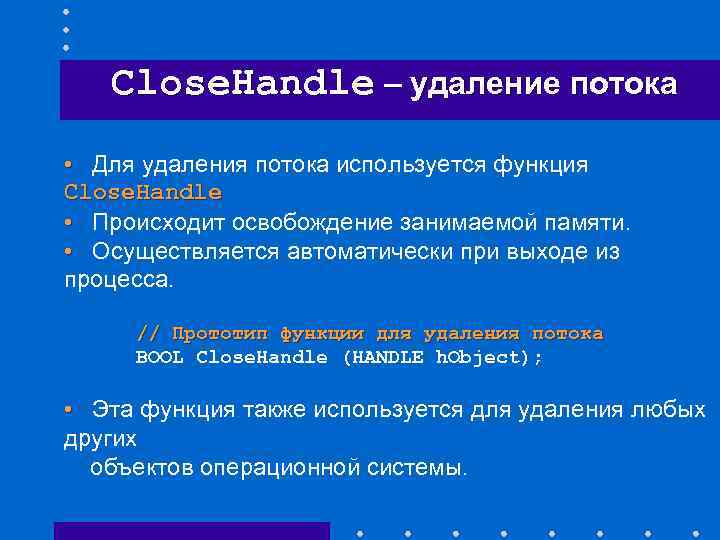

Close. Handle – удаление потока • Для удаления потока используется функция Close. Handle • Происходит освобождение занимаемой памяти. • Осуществляется автоматически при выходе из процесса. // Прототип функции для удаления потока BOOL Close. Handle (HANDLE h. Object); • Эта функция также используется для удаления любых других объектов операционной системы.

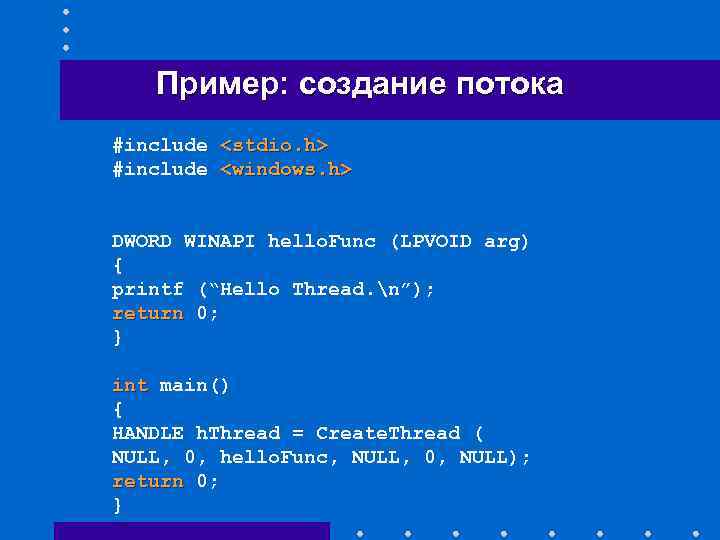

Пример: создание потока #include <stdio. h> #include <windows. h> DWORD WINAPI hello. Func (LPVOID arg) { printf (“Hello Thread. n”); return 0; } int main() { HANDLE h. Thread = Create. Thread ( NULL, 0, hello. Func, NULL, 0, NULL); return 0; }

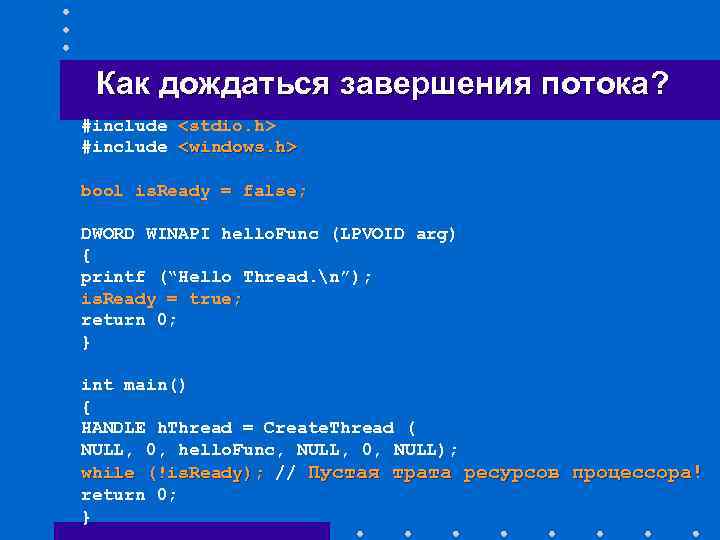

Как дождаться завершения потока? #include <stdio. h> #include <windows. h> bool is. Ready = false; DWORD WINAPI hello. Func (LPVOID arg) { printf (“Hello Thread. n”); is. Ready = true; return 0; } int main() { HANDLE h. Thread = Create. Thread ( NULL, 0, hello. Func, NULL, 0, NULL); while (!is. Ready); // Пустая трата ресурсов процессора! return 0; }

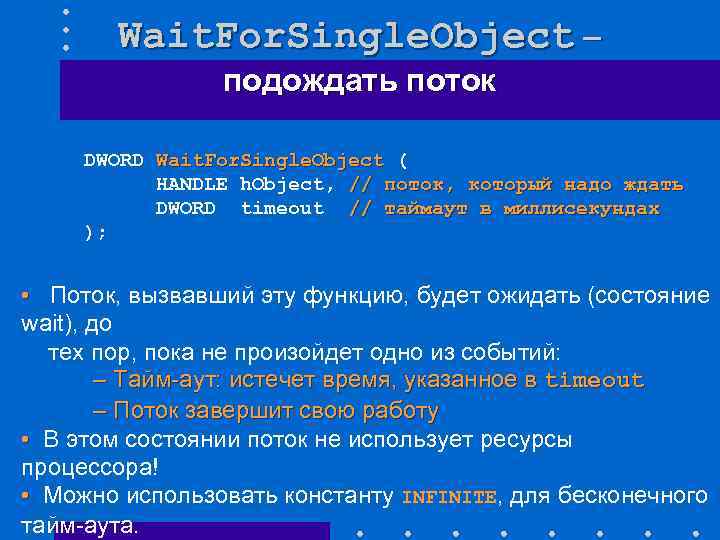

Wait. For. Single. Object – подождать поток DWORD Wait. For. Single. Object ( HANDLE h. Object, // поток, который надо ждать DWORD timeout // таймаут в миллисекундах ); • Поток, вызвавший эту функцию, будет ожидать (состояние wait), до тех пор, пока не произойдет одно из событий: – Тайм-аут: истечет время, указанное в timeout – Поток завершит свою работу • В этом состоянии поток не использует ресурсы процессора! • Можно использовать константу INFINITE, для бесконечного тайм-аута.

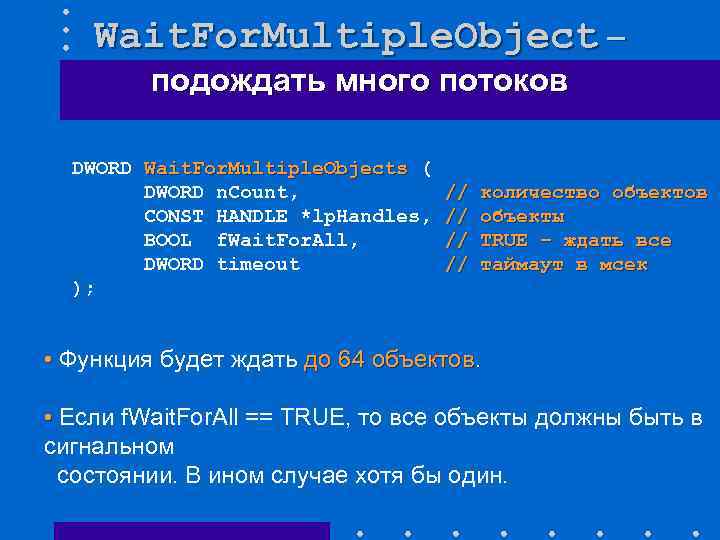

Wait. For. Multiple. Object – подождать много потоков DWORD Wait. For. Multiple. Objects ( DWORD n. Count, CONST HANDLE *lp. Handles, BOOL f. Wait. For. All, DWORD timeout ); // // количество объектов объекты TRUE – ждать все таймаут в мсек • Функция будет ждать до 64 объектов • Если f. Wait. For. All == TRUE, то все объекты должны быть в сигнальном состоянии. В ином случае хотя бы один.

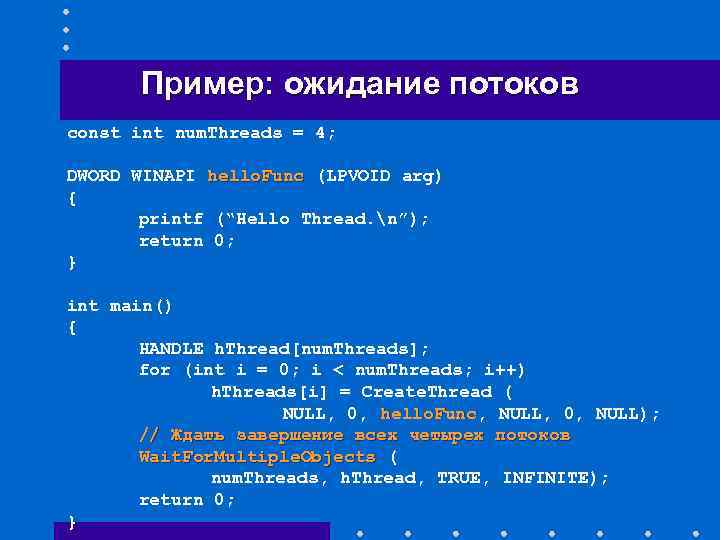

Пример: ожидание потоков const int num. Threads = 4; DWORD WINAPI hello. Func (LPVOID arg) { printf (“Hello Thread. n”); return 0; } int main() { HANDLE h. Thread[num. Threads]; for (int i = 0; i < num. Threads; i++) h. Threads[i] = Create. Thread ( NULL, 0, hello. Func, NULL, 0, NULL); hello. Func // Ждать завершение всех четырех потоков Wait. For. Multiple. Objects ( num. Threads, h. Thread, TRUE, INFINITE); return 0; }