Лекция 3 Процессоры.pptx

- Количество слайдов: 38

ХАРЬКОВСКИЙ НАЦИОНАЛЬНЫЙ ЭКОНОМИЧЕСКИЙ УНИВЕРСИТЕТ ЛЕКЦИЯ 3 Процессоры доцент кафедры информационных систем к. т. н. , с. н. с. Евсеев Сергей Петрович 1

ХАРЬКОВСКИЙ НАЦИОНАЛЬНЫЙ ЭКОНОМИЧЕСКИЙ УНИВЕРСИТЕТ ЛЕКЦИЯ 3 Процессоры доцент кафедры информационных систем к. т. н. , с. н. с. Евсеев Сергей Петрович 1

УСТРОЙСТВА УПРАВЛЕНИЯ КОМПЬЮТЕРА Процесс функционирования машины - это последовательность элементарных действий, которые делятся на две группы: пересылки данных между узлами; элементарные действия в узлах. Любое элементарное действие осуществляется при поступлении соответствующего сигнала управления Уi микропрограммного автомата, который является составной частью устройства управления. Частота формирования управляющих сигналов на выходе автомата определяется синхронизирующими импульсами, которые поступают от генератора тактовых импульсов. Микрооперация – это элементарное действие, выполняемое за один такт синхронизации. Микрокоманда – это совокупность сигналов управления, которые вызывают микрооперации, выполняемые в одном такте. Микропрограмма – это последовательность микрокоманд, приводящая к выполнению относительно сложного действия в машине – команды. 2

УСТРОЙСТВА УПРАВЛЕНИЯ КОМПЬЮТЕРА Процесс функционирования машины - это последовательность элементарных действий, которые делятся на две группы: пересылки данных между узлами; элементарные действия в узлах. Любое элементарное действие осуществляется при поступлении соответствующего сигнала управления Уi микропрограммного автомата, который является составной частью устройства управления. Частота формирования управляющих сигналов на выходе автомата определяется синхронизирующими импульсами, которые поступают от генератора тактовых импульсов. Микрооперация – это элементарное действие, выполняемое за один такт синхронизации. Микрокоманда – это совокупность сигналов управления, которые вызывают микрооперации, выполняемые в одном такте. Микропрограмма – это последовательность микрокоманд, приводящая к выполнению относительно сложного действия в машине – команды. 2

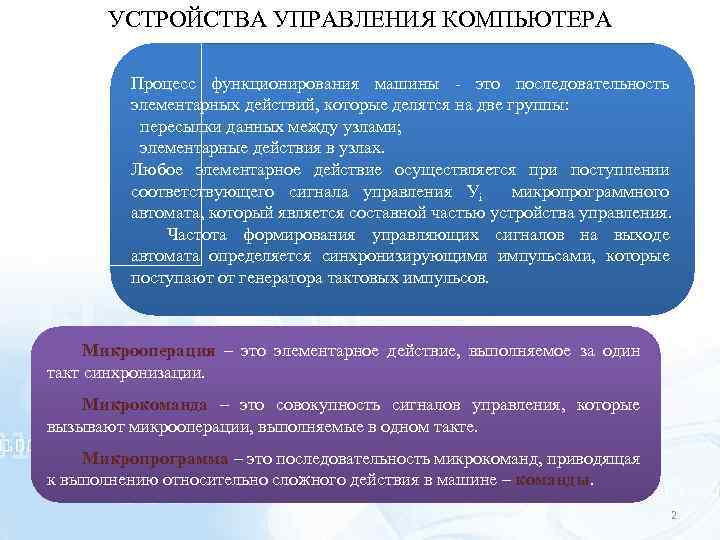

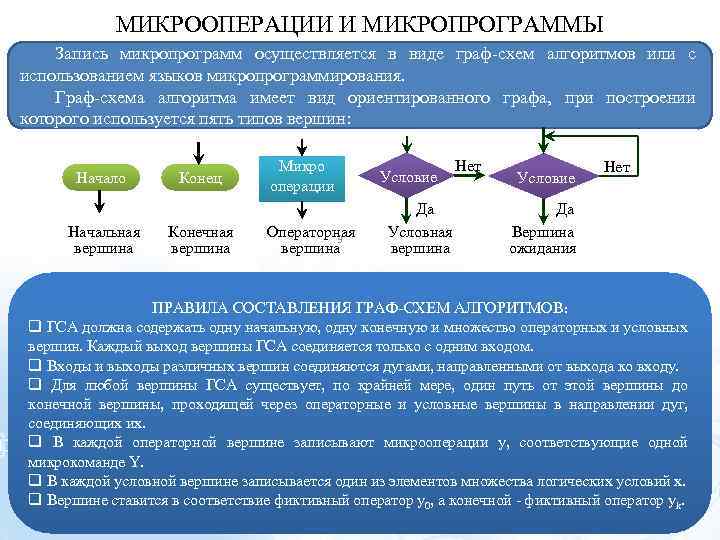

МИКРООПЕРАЦИИ И МИКРОПРОГРАММЫ Запись микропрограмм осуществляется в виде граф-схем алгоритмов или с использованием языков микропрограммирования. Граф-схема алгоритма имеет вид ориентированного графа, при построении которого используется пять типов вершин: Начало Начальная вершина Конец Конечная вершина Микро операции Операторная 3 вершина Условие Нет Да Условная вершина Условие Нет Да Вершина ожидания ПРАВИЛА СОСТАВЛЕНИЯ ГРАФ-СХЕМ АЛГОРИТМОВ: q ГСА должна содержать одну начальную, одну конечную и множество операторных и условных вершин. Каждый выход вершины ГСА соединяется только с одним входом. q Входы и выходы различных вершин соединяются дугами, направленными от выхода ко входу. q Для любой вершины ГСА существует, по крайней мере, один путь от этой вершины до конечной вершины, проходящей через операторные и условные вершины в направлении дуг, соединяющих их. q В каждой операторной вершине записывают микрооперации у, соответствующие одной микрокоманде Y. q В каждой условной вершине записывается один из элементов множества логических условий х. q Вершине ставится в соответствие фиктивный оператор y 0, а конечной - фиктивный оператор yk.

МИКРООПЕРАЦИИ И МИКРОПРОГРАММЫ Запись микропрограмм осуществляется в виде граф-схем алгоритмов или с использованием языков микропрограммирования. Граф-схема алгоритма имеет вид ориентированного графа, при построении которого используется пять типов вершин: Начало Начальная вершина Конец Конечная вершина Микро операции Операторная 3 вершина Условие Нет Да Условная вершина Условие Нет Да Вершина ожидания ПРАВИЛА СОСТАВЛЕНИЯ ГРАФ-СХЕМ АЛГОРИТМОВ: q ГСА должна содержать одну начальную, одну конечную и множество операторных и условных вершин. Каждый выход вершины ГСА соединяется только с одним входом. q Входы и выходы различных вершин соединяются дугами, направленными от выхода ко входу. q Для любой вершины ГСА существует, по крайней мере, один путь от этой вершины до конечной вершины, проходящей через операторные и условные вершины в направлении дуг, соединяющих их. q В каждой операторной вершине записывают микрооперации у, соответствующие одной микрокоманде Y. q В каждой условной вершине записывается один из элементов множества логических условий х. q Вершине ставится в соответствие фиктивный оператор y 0, а конечной - фиктивный оператор yk.

МИКРООПЕРАЦИИ И МИКРОПРОГРАММЫ Пример граф-схемы Языки микропрограммирования обеспечивают запись микропрограммы функционирования вычислительной машины в терминах микроопераций, подразделяемые: Начало q Язык функционального микропрограммирования - ориентирован на запись Y 1 микропрограмм без привязки к конкретной аппаратной структуре реализации этой микропрограммы. q Язык структурно-функционального микропрограммирования - средства языки привязаны к конкретным аппаратным средствам реализации микропрограмм. y 1, y 6 x 1 Да Y 2 y 2 Y 3 y 3, y 4, y 5, y 7 x 2 Да Конец Нет Конструкции языков микропрограммирования: Слово (регистр или шина): <идентификатор>(номера разрядов). Примеры: А(31 -0); B(15 -8) <описание слова> Рг 1(0 -31); Рг. К(31 -34) <описание регистра> Рг. ПЗ(31 30 -23 22 -0); Рг. ПЗ(s p m) <составленное слово> ШІ(15 -0) <описание шини> Память: <идентификатор модуля памяти>[адреса ячеек] (номера разрядов) Примеры: ПАМ[000: 999] (15 -0) <описание поля памяти> RAM 1[0000: 1023] (7 -0) <описание модуля памяти> RAM 2[1024: 2047] (7 -0) <описание модуля памяти > ROM[2 A 7 C] (31 -0) <описание ячейки памяти прямой адресации> RAM[Aисп)] (7 -0); <описание ячейки памяти при символьной адресации> ОЗП[(Рг. А)] <описание ячейки памяти при непосредственной адресации>

МИКРООПЕРАЦИИ И МИКРОПРОГРАММЫ Пример граф-схемы Языки микропрограммирования обеспечивают запись микропрограммы функционирования вычислительной машины в терминах микроопераций, подразделяемые: Начало q Язык функционального микропрограммирования - ориентирован на запись Y 1 микропрограмм без привязки к конкретной аппаратной структуре реализации этой микропрограммы. q Язык структурно-функционального микропрограммирования - средства языки привязаны к конкретным аппаратным средствам реализации микропрограмм. y 1, y 6 x 1 Да Y 2 y 2 Y 3 y 3, y 4, y 5, y 7 x 2 Да Конец Нет Конструкции языков микропрограммирования: Слово (регистр или шина): <идентификатор>(номера разрядов). Примеры: А(31 -0); B(15 -8) <описание слова> Рг 1(0 -31); Рг. К(31 -34) <описание регистра> Рг. ПЗ(31 30 -23 22 -0); Рг. ПЗ(s p m) <составленное слово> ШІ(15 -0) <описание шини> Память: <идентификатор модуля памяти>[адреса ячеек] (номера разрядов) Примеры: ПАМ[000: 999] (15 -0) <описание поля памяти> RAM 1[0000: 1023] (7 -0) <описание модуля памяти> RAM 2[1024: 2047] (7 -0) <описание модуля памяти > ROM[2 A 7 C] (31 -0) <описание ячейки памяти прямой адресации> RAM[Aисп)] (7 -0); <описание ячейки памяти при символьной адресации> ОЗП[(Рг. А)] <описание ячейки памяти при непосредственной адресации>

ОБОБЩЕННАЯ СТРУКТУРА УСТРОЙСТВА УПРАВЛЕНИЯ ПК От ОП Регистр команд КОП СА Адрес Микропрограммный автомат Узел прерываний и Сигналы управления приоритетов Флаги и сигналы оповещения Управляющая часть УУ Узел адресной арифметики Регистр адреса операнда 5 Счетчик команд Непосредственные операционные действия над операндами вызывают только микрокоманды при одноступенчатом микропрограммировании и нанокоманды при двухступенчатом микропрограммировании. К ОП Адресная часть УУ Процесс работы устройства управления можно разделить на самостоятельные этапы: q Выборка команд и операндов оперативной памяти - выполняется адресной частью; q Выборка микрокоманд из управляющей памяти и формирование сигналов управления для выполнения элементарных действия в операционных устройствах - выполняется микропрограммным автоматом.

ОБОБЩЕННАЯ СТРУКТУРА УСТРОЙСТВА УПРАВЛЕНИЯ ПК От ОП Регистр команд КОП СА Адрес Микропрограммный автомат Узел прерываний и Сигналы управления приоритетов Флаги и сигналы оповещения Управляющая часть УУ Узел адресной арифметики Регистр адреса операнда 5 Счетчик команд Непосредственные операционные действия над операндами вызывают только микрокоманды при одноступенчатом микропрограммировании и нанокоманды при двухступенчатом микропрограммировании. К ОП Адресная часть УУ Процесс работы устройства управления можно разделить на самостоятельные этапы: q Выборка команд и операндов оперативной памяти - выполняется адресной частью; q Выборка микрокоманд из управляющей памяти и формирование сигналов управления для выполнения элементарных действия в операционных устройствах - выполняется микропрограммным автоматом.

ОБОБЩЕННАЯ СТРУКТУРА УСТРОЙСТВА УПРАВЛЕНИЯ ПК От ОП Регистр команд КОП СА Адрес Микропрограммный автомат Узел прерываний и Сигналы управления приоритетов Флаги и сигналы оповещения Управляющая часть УУ Узел адресной арифметики Регистр адреса операнда 6 Счетчик команд К ОП Адресная часть УУ Управляющая часть предназначена для формирования сигналов управления, которые инициируют работу операционных устройств, адресной части устройства управления, основной памяти и других узлов компьютера. Адресная часть формирует исполнительные адреса команд и операндов в основной памяти с учетом различных способов ее адресации.

ОБОБЩЕННАЯ СТРУКТУРА УСТРОЙСТВА УПРАВЛЕНИЯ ПК От ОП Регистр команд КОП СА Адрес Микропрограммный автомат Узел прерываний и Сигналы управления приоритетов Флаги и сигналы оповещения Управляющая часть УУ Узел адресной арифметики Регистр адреса операнда 6 Счетчик команд К ОП Адресная часть УУ Управляющая часть предназначена для формирования сигналов управления, которые инициируют работу операционных устройств, адресной части устройства управления, основной памяти и других узлов компьютера. Адресная часть формирует исполнительные адреса команд и операндов в основной памяти с учетом различных способов ее адресации.

РАБОТА БЛОКА ВЫБОРКИ КОМАНД ПРИ ЕСТЕСТВЕННОЙ Счетчик команд ВЫБОРКЕ КОМАНД Адрес первой команды программы отд ОС Рг. Aк Ai - адрес текущей команды СМ 1 Рг. Aк A(i+1) - адрес последующей команды Рг. К КОП Адресная часть Lі - длина команды в байтах Программа в памяти Команда 1 Команда 2 Команда 3 Ai Команда i-1 Команда i+1 Команда j+1 Команда n Основные задачи процедуры: q формирование адреса очередной команды программы; q считывание этой команды из памяти; q правильное размещение команды в регистре команд (Рг. К) процессора. Три способа выборки команд: естественная выборка - выполняется когда предыдущая команда была операционной; условный переход - выполняется по команде условного перехода; безусловный переход - выполняется по команде безусловного перехода. Естественная выборка основана на том факте, что, как правило, команды программ содержатся в последовательных ячейках памяти в соответствии с их размещением в программе. При этом основным способом адресации команд есть допускаемая адресация, когда адрес следующей команды считается равной сумме адреса и длины текущей команды в байтах. Поэтому при выполнении естественной выборки для формирования и хранения адреса следующей команды используется счетчик команд

РАБОТА БЛОКА ВЫБОРКИ КОМАНД ПРИ ЕСТЕСТВЕННОЙ Счетчик команд ВЫБОРКЕ КОМАНД Адрес первой команды программы отд ОС Рг. Aк Ai - адрес текущей команды СМ 1 Рг. Aк A(i+1) - адрес последующей команды Рг. К КОП Адресная часть Lі - длина команды в байтах Программа в памяти Команда 1 Команда 2 Команда 3 Ai Команда i-1 Команда i+1 Команда j+1 Команда n Основные задачи процедуры: q формирование адреса очередной команды программы; q считывание этой команды из памяти; q правильное размещение команды в регистре команд (Рг. К) процессора. Три способа выборки команд: естественная выборка - выполняется когда предыдущая команда была операционной; условный переход - выполняется по команде условного перехода; безусловный переход - выполняется по команде безусловного перехода. Естественная выборка основана на том факте, что, как правило, команды программ содержатся в последовательных ячейках памяти в соответствии с их размещением в программе. При этом основным способом адресации команд есть допускаемая адресация, когда адрес следующей команды считается равной сумме адреса и длины текущей команды в байтах. Поэтому при выполнении естественной выборки для формирования и хранения адреса следующей команды используется счетчик команд

РАБОТА БЛОКА ВЫБОРКИ КОМАНД ПРИ ЕСТЕСТВЕННОЙ Счетчик команд ВЫБОРКЕ КОМАНД Адрес первой команды программы отд ОС Рг. Aк Ai - адрес текущей команды СМ 1 Рг. Aк A(i+1) - адрес последующей команды Рг. К КОП Адресная часть Lі - длина команды в байтах В конце цикла выполнения очередной команды значение адреса следующей команды Аi +1 переписывается в Рг. Ак и становится адресом команды для следующего цикла. В начале этого цикла производится обращение к ячейке памяти по адресу, записанному в Рг. Ак, и очередная команда считывается в регистр Рг. К для исполнения. Программа в памяти Команда 1 Команда 2 Команда 3 Ai Команда i-1 Команда i+1 Команда j+1 Команда n Рг. Ак - регистр адреса команд, служит для хранения адреса текущей команды Аi. Рг. Ак вспомогательный регистр, служит для временного хранения адреса следующей команды Аi+1. Рг. К - Регистр команд, служит для записи и хранения кода текущей команды. - Комбинационная схема является декодером длины команды и служит для формирования кода длины текущей команды L в байтах на основе анализа кода операции текущей команды, которая записана в Рг. К. СМ 1 - Комбинационный сумматор обеспечивает формирование адреса следующей команды Аi +1 путем составления адреса текущей команды Аi и кода длины команды L согласно формуле Аi+1 = Аi + L

РАБОТА БЛОКА ВЫБОРКИ КОМАНД ПРИ ЕСТЕСТВЕННОЙ Счетчик команд ВЫБОРКЕ КОМАНД Адрес первой команды программы отд ОС Рг. Aк Ai - адрес текущей команды СМ 1 Рг. Aк A(i+1) - адрес последующей команды Рг. К КОП Адресная часть Lі - длина команды в байтах В конце цикла выполнения очередной команды значение адреса следующей команды Аi +1 переписывается в Рг. Ак и становится адресом команды для следующего цикла. В начале этого цикла производится обращение к ячейке памяти по адресу, записанному в Рг. Ак, и очередная команда считывается в регистр Рг. К для исполнения. Программа в памяти Команда 1 Команда 2 Команда 3 Ai Команда i-1 Команда i+1 Команда j+1 Команда n Рг. Ак - регистр адреса команд, служит для хранения адреса текущей команды Аi. Рг. Ак вспомогательный регистр, служит для временного хранения адреса следующей команды Аi+1. Рг. К - Регистр команд, служит для записи и хранения кода текущей команды. - Комбинационная схема является декодером длины команды и служит для формирования кода длины текущей команды L в байтах на основе анализа кода операции текущей команды, которая записана в Рг. К. СМ 1 - Комбинационный сумматор обеспечивает формирование адреса следующей команды Аi +1 путем составления адреса текущей команды Аi и кода длины команды L согласно формуле Аi+1 = Аi + L

СПОСОБЫ ПОВЫШЕНИЯ БЫСТРОДЕЙСТВИЯ ПРОЦЕДУРЫ ВЫБОРКИ КОМАНД Структурная схема буфера команд Шина передачи данных от памяти Буферный регистр 1 0 n-1 Буферный регистр 2 Преддешифратор команд 0 n-1 Буферный регистр 3 0 Буфер кодов 0 длины команд L n-1 Буферный регистр 4 Длина команды до счетчика команд n-1 Выравниватель Очередная команда в Рг. К Операция чтения очередной команды из памяти является довольно длительной процедурой и значительно влияет на продолжительность командного цикла. Для уменьшения воздействия процедуры чтения командной информации на продолжительность цикла выполнения команды используется: qопережающая выборка (предвыборка) команд; qбуферизация команд. Опережающая выборка заключается: 1. Чтение команд не привязывается к конкретному времени рабочего цикла процессора, а осуществляется в те медленные моменты времени, когда свободны средства обращения процессора к памяти. 2. За один цикл обращения к памяти читается не один, а сразу несколько команд. 3. В блоке выборки команд необходимо предусмотреть следующие средства: опережающего формирования адресов следующих команд временного хранения команд ожидания своего рабочего цикла процессора. Для временного хранения команд, считанных заранее, используется буфер команд, созданный в виде 9 стека.

СПОСОБЫ ПОВЫШЕНИЯ БЫСТРОДЕЙСТВИЯ ПРОЦЕДУРЫ ВЫБОРКИ КОМАНД Структурная схема буфера команд Шина передачи данных от памяти Буферный регистр 1 0 n-1 Буферный регистр 2 Преддешифратор команд 0 n-1 Буферный регистр 3 0 Буфер кодов 0 длины команд L n-1 Буферный регистр 4 Длина команды до счетчика команд n-1 Выравниватель Очередная команда в Рг. К Операция чтения очередной команды из памяти является довольно длительной процедурой и значительно влияет на продолжительность командного цикла. Для уменьшения воздействия процедуры чтения командной информации на продолжительность цикла выполнения команды используется: qопережающая выборка (предвыборка) команд; qбуферизация команд. Опережающая выборка заключается: 1. Чтение команд не привязывается к конкретному времени рабочего цикла процессора, а осуществляется в те медленные моменты времени, когда свободны средства обращения процессора к памяти. 2. За один цикл обращения к памяти читается не один, а сразу несколько команд. 3. В блоке выборки команд необходимо предусмотреть следующие средства: опережающего формирования адресов следующих команд временного хранения команд ожидания своего рабочего цикла процессора. Для временного хранения команд, считанных заранее, используется буфер команд, созданный в виде 9 стека.

СПОСОБЫ ПОВЫШЕНИЯ БЫСТРОДЕЙСТВИЯ ПРОЦЕДУРЫ ВЫБОРКИ КОМАНД Структурная схема буфера команд Шина передачи данных от памяти Буферный регистр 1 0 n-1 Буферный регистр 2 Преддешифратор команд 0 n-1 Буферный регистр 3 0 Буфер кодов 0 длины команд L n-1 Буферный регистр 4 Длина команды до счетчика команд n-1 Выравниватель Очередная команда в Рг. К Опережающая адресация команд - формирование адреса следующей команды по принципу естественной выборки задолго до ее фактического исполнения. Выполняется путем предварительной дешифрации кода операции последней считанной из памяти команды, находящейся в первом регистре стека. Для этого используется специальная комбинационная схема, что называется преддешифратором команд. Эта схема после считывания очередной команды из памяти анализирует ее код операции и формирует код длины этой команды в байтах. Код длины направляется в счетчик команд, где осуществляется опережающее формирование адреса следующей команды. Этот адрес загружается в Рг. Ак, где ожидает времени, когда станет возможным чтение очередной команды из памяти. Опережающая выборка и использование буфера команд позволяет значительно повысить производительность процессора при выполнении линейных участков программ, поскольку не требует выделения специальной части командного цикла на чтение команды из памяти. 10

СПОСОБЫ ПОВЫШЕНИЯ БЫСТРОДЕЙСТВИЯ ПРОЦЕДУРЫ ВЫБОРКИ КОМАНД Структурная схема буфера команд Шина передачи данных от памяти Буферный регистр 1 0 n-1 Буферный регистр 2 Преддешифратор команд 0 n-1 Буферный регистр 3 0 Буфер кодов 0 длины команд L n-1 Буферный регистр 4 Длина команды до счетчика команд n-1 Выравниватель Очередная команда в Рг. К Опережающая адресация команд - формирование адреса следующей команды по принципу естественной выборки задолго до ее фактического исполнения. Выполняется путем предварительной дешифрации кода операции последней считанной из памяти команды, находящейся в первом регистре стека. Для этого используется специальная комбинационная схема, что называется преддешифратором команд. Эта схема после считывания очередной команды из памяти анализирует ее код операции и формирует код длины этой команды в байтах. Код длины направляется в счетчик команд, где осуществляется опережающее формирование адреса следующей команды. Этот адрес загружается в Рг. Ак, где ожидает времени, когда станет возможным чтение очередной команды из памяти. Опережающая выборка и использование буфера команд позволяет значительно повысить производительность процессора при выполнении линейных участков программ, поскольку не требует выделения специальной части командного цикла на чтение команды из памяти. 10

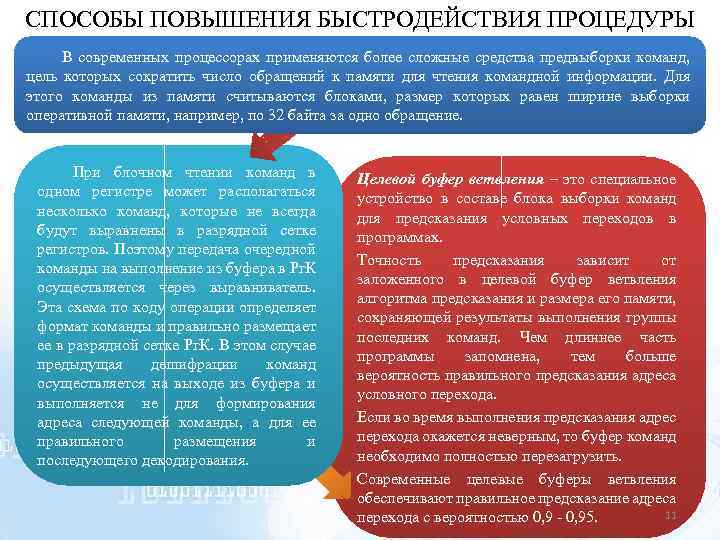

СПОСОБЫ ПОВЫШЕНИЯ БЫСТРОДЕЙСТВИЯ ПРОЦЕДУРЫ ВЫБОРКИ КОМАНД В современных процессорах применяются более сложные средства предвыборки команд, цель которых сократить число обращений к памяти для чтения командной информации. Для этого команды из памяти считываются блоками, размер которых равен ширине выборки оперативной памяти, например, по 32 байта за одно обращение. При блочном чтении команд в одном регистре может располагаться несколько команд, которые не всегда будут выравнены в разрядной сетке регистров. Поэтому передача очередной команды на выполнение из буфера в Рг. К осуществляется через выравниватель. Эта схема по коду операции определяет формат команды и правильно размещает ее в разрядной сетке Рг. К. В этом случае предыдущая дешифрации команд осуществляется на выходе из буфера и выполняется не для формирования адреса следующей команды, а для ее правильного размещения и последующего декодирования. Целевой буфер ветвления – это специальное устройство в составе блока выборки команд для предсказания условных переходов в программах. Точность предсказания зависит от заложенного в целевой буфер ветвления алгоритма предсказания и размера его памяти, сохраняющей результаты выполнения группы последних команд. Чем длиннее часть программы запомнена, тем больше вероятность правильного предсказания адреса условного перехода. Если во время выполнения предсказания адрес перехода окажется неверным, то буфер команд необходимо полностью перезагрузить. Современные целевые буферы ветвления обеспечивают правильное предсказание адреса 11 перехода с вероятностью 0, 9 - 0, 95.

СПОСОБЫ ПОВЫШЕНИЯ БЫСТРОДЕЙСТВИЯ ПРОЦЕДУРЫ ВЫБОРКИ КОМАНД В современных процессорах применяются более сложные средства предвыборки команд, цель которых сократить число обращений к памяти для чтения командной информации. Для этого команды из памяти считываются блоками, размер которых равен ширине выборки оперативной памяти, например, по 32 байта за одно обращение. При блочном чтении команд в одном регистре может располагаться несколько команд, которые не всегда будут выравнены в разрядной сетке регистров. Поэтому передача очередной команды на выполнение из буфера в Рг. К осуществляется через выравниватель. Эта схема по коду операции определяет формат команды и правильно размещает ее в разрядной сетке Рг. К. В этом случае предыдущая дешифрации команд осуществляется на выходе из буфера и выполняется не для формирования адреса следующей команды, а для ее правильного размещения и последующего декодирования. Целевой буфер ветвления – это специальное устройство в составе блока выборки команд для предсказания условных переходов в программах. Точность предсказания зависит от заложенного в целевой буфер ветвления алгоритма предсказания и размера его памяти, сохраняющей результаты выполнения группы последних команд. Чем длиннее часть программы запомнена, тем больше вероятность правильного предсказания адреса условного перехода. Если во время выполнения предсказания адрес перехода окажется неверным, то буфер команд необходимо полностью перезагрузить. Современные целевые буферы ветвления обеспечивают правильное предсказание адреса 11 перехода с вероятностью 0, 9 - 0, 95.

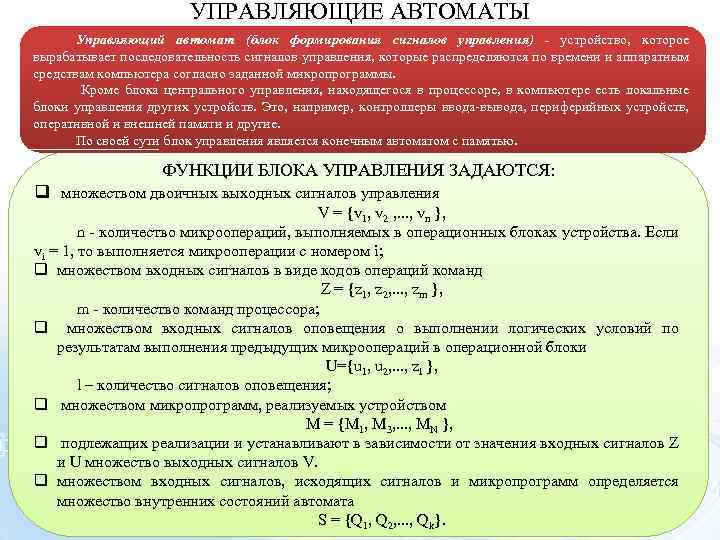

УПРАВЛЯЮЩИЕ АВТОМАТЫ Управляющий автомат (блок формирования сигналов управления) - устройство, которое вырабатывает последовательность сигналов управления, которые распределяются по времени и аппаратным средствам компьютера согласно заданной микропрограммы. Кроме блока центрального управления, находящегося в процессоре, в компьютере есть локальные блоки управления других устройств. Это, например, контроллеры ввода-вывода, периферийных устройств, оперативной и внешней памяти и другие. По своей сути блок управления является конечным автоматом с памятью. ФУНКЦИИ БЛОКА УПРАВЛЕНИЯ ЗАДАЮТСЯ: q множеством двоичных выходных сигналов управления V = {v 1, v 2 , . . . , vn }, n - количество микроопераций, выполняемых в операционных блоках устройства. Если vi = 1, то выполняется микрооперации с номером i; q множеством входных сигналов в виде кодов операций команд Z = {z 1, z 2, . . . , zm }, m - количество команд процессора; q множеством входных сигналов оповещения о выполнении логических условий по результатам выполнения предыдущих микроопераций в операционной блоки U={u 1, u 2, . . . , zl }, l – количество сигналов оповещения; q множеством микропрограмм, реализуемых устройством М = {М 1, М 3, . . . , МN }, q подлежащих реализации и устанавливают в зависимости от значения входных сигналов Z и U множество выходных сигналов V. q множеством входных сигналов, исходящих сигналов и микропрограмм определяется множество внутренних состояний автомата 12 S = {Q 1, Q 2, . . . , Qk}.

УПРАВЛЯЮЩИЕ АВТОМАТЫ Управляющий автомат (блок формирования сигналов управления) - устройство, которое вырабатывает последовательность сигналов управления, которые распределяются по времени и аппаратным средствам компьютера согласно заданной микропрограммы. Кроме блока центрального управления, находящегося в процессоре, в компьютере есть локальные блоки управления других устройств. Это, например, контроллеры ввода-вывода, периферийных устройств, оперативной и внешней памяти и другие. По своей сути блок управления является конечным автоматом с памятью. ФУНКЦИИ БЛОКА УПРАВЛЕНИЯ ЗАДАЮТСЯ: q множеством двоичных выходных сигналов управления V = {v 1, v 2 , . . . , vn }, n - количество микроопераций, выполняемых в операционных блоках устройства. Если vi = 1, то выполняется микрооперации с номером i; q множеством входных сигналов в виде кодов операций команд Z = {z 1, z 2, . . . , zm }, m - количество команд процессора; q множеством входных сигналов оповещения о выполнении логических условий по результатам выполнения предыдущих микроопераций в операционной блоки U={u 1, u 2, . . . , zl }, l – количество сигналов оповещения; q множеством микропрограмм, реализуемых устройством М = {М 1, М 3, . . . , МN }, q подлежащих реализации и устанавливают в зависимости от значения входных сигналов Z и U множество выходных сигналов V. q множеством входных сигналов, исходящих сигналов и микропрограмм определяется множество внутренних состояний автомата 12 S = {Q 1, Q 2, . . . , Qk}.

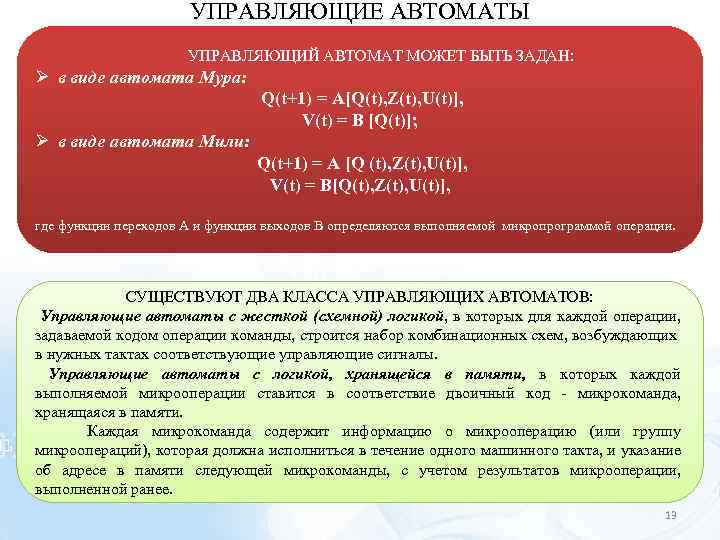

УПРАВЛЯЮЩИЕ АВТОМАТЫ УПРАВЛЯЮЩИЙ АВТОМАТ МОЖЕТ БЫТЬ ЗАДАН: в виде автомата Мура: Q(t+1) = A[Q(t), Z(t), U(t)], V(t) = B [Q(t)]; в виде автомата Мили: Q(t+1) = A [Q (t), Z(t), U(t)], V(t) = B[Q(t), Z(t), U(t)], где функции переходов А и функции выходов В определяются выполняемой микропрограммой операции. СУЩЕСТВУЮТ ДВА КЛАССА УПРАВЛЯЮЩИХ АВТОМАТОВ: Управляющие автоматы с жесткой (схемной) логикой, в которых для каждой операции, задаваемой кодом операции команды, строится набор комбинационных схем, возбуждающих в нужных тактах соответствующие управляющие сигналы. Управляющие автоматы с логикой, хранящейся в памяти, в которых каждой выполняемой микрооперации ставится в соответствие двоичный код - микрокоманда, хранящаяся в памяти. Каждая микрокоманда содержит информацию о микрооперацию (или группу микроопераций), которая должна исполниться в течение одного машинного такта, и указание об адресе в памяти следующей микрокоманды, с учетом результатов микрооперации, выполненной ранее. 13

УПРАВЛЯЮЩИЕ АВТОМАТЫ УПРАВЛЯЮЩИЙ АВТОМАТ МОЖЕТ БЫТЬ ЗАДАН: в виде автомата Мура: Q(t+1) = A[Q(t), Z(t), U(t)], V(t) = B [Q(t)]; в виде автомата Мили: Q(t+1) = A [Q (t), Z(t), U(t)], V(t) = B[Q(t), Z(t), U(t)], где функции переходов А и функции выходов В определяются выполняемой микропрограммой операции. СУЩЕСТВУЮТ ДВА КЛАССА УПРАВЛЯЮЩИХ АВТОМАТОВ: Управляющие автоматы с жесткой (схемной) логикой, в которых для каждой операции, задаваемой кодом операции команды, строится набор комбинационных схем, возбуждающих в нужных тактах соответствующие управляющие сигналы. Управляющие автоматы с логикой, хранящейся в памяти, в которых каждой выполняемой микрооперации ставится в соответствие двоичный код - микрокоманда, хранящаяся в памяти. Каждая микрокоманда содержит информацию о микрооперацию (или группу микроопераций), которая должна исполниться в течение одного машинного такта, и указание об адресе в памяти следующей микрокоманды, с учетом результатов микрооперации, выполненной ранее. 13

УПРАВЛЯЮЩИЙ АВТОМАТ С ЖЕСТКОЙ ЛОГИКОЙ Регистр команд Т 1 Т 2 ТN Дешифратор кода операций I 0 I 1 14 Ik U 1 U 2 Логические схемы формирования сигналов UI управления V 0 V 1 Дешифратор тактов V 1 & s x 1 i & 1 & Vk x 2 Сигнали оповещения Дешифратор тактов Счетчик тактов & 1 Дешифратор кода операции Сигнали оповещения Узел синхронизации & 1 & Vn Vn Сигнал управления Vk будет формироваться при выполнении j команды в такте s безусловно, а в такте і при выполнении условий х1 и х2. Жесткая логика обусловлена тем, что каждой микропрограмме соответствует свой набор логических схем с фиксированными связями. Преимущество – высокое быстродействие за счет использования в качестве логики только комбинационных схем. Недостатки – высокая стоимость изготовления и невозможность перепрограммирования в процессе эксплуатации. Область применения – несложные устройства управления, реализующих небольшое количество микропрограмм и микроопераций.

УПРАВЛЯЮЩИЙ АВТОМАТ С ЖЕСТКОЙ ЛОГИКОЙ Регистр команд Т 1 Т 2 ТN Дешифратор кода операций I 0 I 1 14 Ik U 1 U 2 Логические схемы формирования сигналов UI управления V 0 V 1 Дешифратор тактов V 1 & s x 1 i & 1 & Vk x 2 Сигнали оповещения Дешифратор тактов Счетчик тактов & 1 Дешифратор кода операции Сигнали оповещения Узел синхронизации & 1 & Vn Vn Сигнал управления Vk будет формироваться при выполнении j команды в такте s безусловно, а в такте і при выполнении условий х1 и х2. Жесткая логика обусловлена тем, что каждой микропрограмме соответствует свой набор логических схем с фиксированными связями. Преимущество – высокое быстродействие за счет использования в качестве логики только комбинационных схем. Недостатки – высокая стоимость изготовления и невозможность перепрограммирования в процессе эксплуатации. Область применения – несложные устройства управления, реализующих небольшое количество микропрограмм и микроопераций.

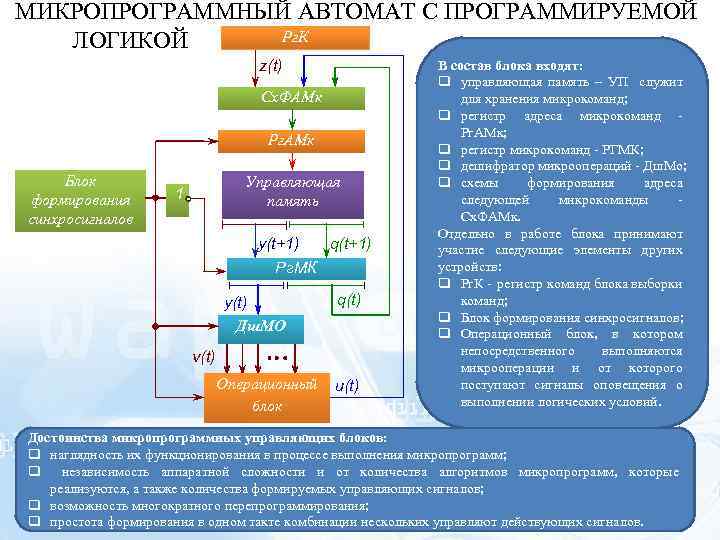

МИКРОПРОГРАММНЫЙ АВТОМАТ С ПРОГРАММИРУЕМОЙ Рг. К ЛОГИКОЙ z(t) Сх. ФАМк Рг. АМк Блок формирования синхросигналов Управляющая память 1 q(t+1) y(t+1) Рг. МК y(t) Дш. МО q(t) v(t) Операционный блок u(t) В состав блока входят: q управляющая память – УП служит для хранения микрокоманд; q регистр адреса микрокоманд - Рг. АМк; q регистр микрокоманд - РГМК; q дешифратор микроопераций - Дш. Мо; q схемы формирования адреса следующей микрокоманды - Сх. ФАМк. Отдельно в работе блока принимают участие следующие элементы других устройств: q Рг. К - регистр команд блока выборки команд; q Блок формирования синхросигналов; q Операционный блок, в котором непосредственного выполняются микрооперации и от которого поступают сигналы оповещения о выполнении логических условий. Достоинства микропрограммных управляющих блоков: q наглядность их функционирования в процессе выполнения микропрограмм; q независимость аппаратной сложности и от количества алгоритмов микропрограмм, которые реализуются, а также количества формируемых управляющих сигналов; q возможность многократного перепрограммирования; 15 q простота формирования в одном такте комбинации нескольких управляют действующих сигналов.

МИКРОПРОГРАММНЫЙ АВТОМАТ С ПРОГРАММИРУЕМОЙ Рг. К ЛОГИКОЙ z(t) Сх. ФАМк Рг. АМк Блок формирования синхросигналов Управляющая память 1 q(t+1) y(t+1) Рг. МК y(t) Дш. МО q(t) v(t) Операционный блок u(t) В состав блока входят: q управляющая память – УП служит для хранения микрокоманд; q регистр адреса микрокоманд - Рг. АМк; q регистр микрокоманд - РГМК; q дешифратор микроопераций - Дш. Мо; q схемы формирования адреса следующей микрокоманды - Сх. ФАМк. Отдельно в работе блока принимают участие следующие элементы других устройств: q Рг. К - регистр команд блока выборки команд; q Блок формирования синхросигналов; q Операционный блок, в котором непосредственного выполняются микрооперации и от которого поступают сигналы оповещения о выполнении логических условий. Достоинства микропрограммных управляющих блоков: q наглядность их функционирования в процессе выполнения микропрограмм; q независимость аппаратной сложности и от количества алгоритмов микропрограмм, которые реализуются, а также количества формируемых управляющих сигналов; q возможность многократного перепрограммирования; 15 q простота формирования в одном такте комбинации нескольких управляют действующих сигналов.

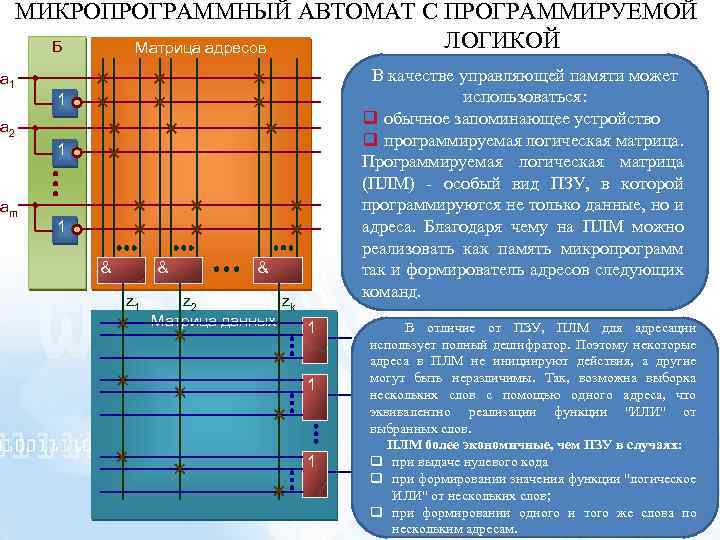

МИКРОПРОГРАММНЫЙ АВТОМАТ С ПРОГРАММИРУЕМОЙ ЛОГИКОЙ Б Матрица адресов а 1 1 а 2 аm 1 1 & & z 1 & z 2 zk Матрица данных 1 1 1 В качестве управляющей памяти может использоваться: q обычное запоминающее устройство q программируемая логическая матрица. Программируемая логическая матрица (ПЛМ) - особый вид ПЗУ, в которой программируются не только данные, но и адреса. Благодаря чему на ПЛМ можно реализовать как память микропрограмм так и формирователь адресов следующих команд. В отличие от ПЗУ, ПЛМ для адресации c 1 использует полный дешифратор. Поэтому некоторые адреса в ПЛМ не инициируют действия, а другие могут быть неразличимы. Так, возможна выборка c 2 нескольких слов с помощью одного адреса, что эквивалентно реализации функции "ИЛИ" от выбранных слов. ПЛМ более экономичные, чем ПЗУ в случаях: cnq при выдаче нулевого кода q при формировании значения функции "логическое ИЛИ" от нескольких слов; q при формировании одного и того же слова по 16 нескольким адресам.

МИКРОПРОГРАММНЫЙ АВТОМАТ С ПРОГРАММИРУЕМОЙ ЛОГИКОЙ Б Матрица адресов а 1 1 а 2 аm 1 1 & & z 1 & z 2 zk Матрица данных 1 1 1 В качестве управляющей памяти может использоваться: q обычное запоминающее устройство q программируемая логическая матрица. Программируемая логическая матрица (ПЛМ) - особый вид ПЗУ, в которой программируются не только данные, но и адреса. Благодаря чему на ПЛМ можно реализовать как память микропрограмм так и формирователь адресов следующих команд. В отличие от ПЗУ, ПЛМ для адресации c 1 использует полный дешифратор. Поэтому некоторые адреса в ПЛМ не инициируют действия, а другие могут быть неразличимы. Так, возможна выборка c 2 нескольких слов с помощью одного адреса, что эквивалентно реализации функции "ИЛИ" от выбранных слов. ПЛМ более экономичные, чем ПЗУ в случаях: cnq при выдаче нулевого кода q при формировании значения функции "логическое ИЛИ" от нескольких слов; q при формировании одного и того же слова по 16 нескольким адресам.

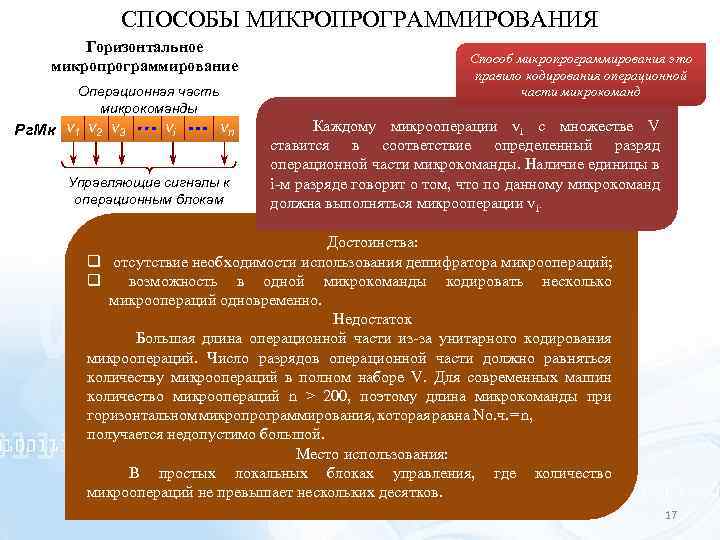

СПОСОБЫ МИКРОПРОГРАММИРОВАНИЯ Горизонтальное микропрограммирование Операционная часть микрокоманды Рг. Мк v 1 v 2 v 3 vi vn Управляющие сигналы к операционным блокам Способ микропрограммирования это правило кодирования операционной части микрокоманд Каждому микрооперации vi с множестве V ставится в соответствие определенный разряд операционной части микрокоманды. Наличие единицы в i-м разряде говорит о том, что по данному микрокоманд должна выполняться микрооперации vi. Достоинства: q отсутствие необходимости использования дешифратора микроопераций; q возможность в одной микрокоманды кодировать несколько микроопераций одновременно. Недостаток Большая длина операционной части из-за унитарного кодирования микроопераций. Число разрядов операционной части должно равняться количеству микроопераций в полном наборе V. Для современных машин количество микроопераций n > 200, поэтому длина микрокоманды при горизонтальном микропрограммирования, которая равна Nо. ч. = n, получается недопустимо большой. Место использования: В простых локальных блоках управления, где количество микроопераций не превышает нескольких десятков. 17

СПОСОБЫ МИКРОПРОГРАММИРОВАНИЯ Горизонтальное микропрограммирование Операционная часть микрокоманды Рг. Мк v 1 v 2 v 3 vi vn Управляющие сигналы к операционным блокам Способ микропрограммирования это правило кодирования операционной части микрокоманд Каждому микрооперации vi с множестве V ставится в соответствие определенный разряд операционной части микрокоманды. Наличие единицы в i-м разряде говорит о том, что по данному микрокоманд должна выполняться микрооперации vi. Достоинства: q отсутствие необходимости использования дешифратора микроопераций; q возможность в одной микрокоманды кодировать несколько микроопераций одновременно. Недостаток Большая длина операционной части из-за унитарного кодирования микроопераций. Число разрядов операционной части должно равняться количеству микроопераций в полном наборе V. Для современных машин количество микроопераций n > 200, поэтому длина микрокоманды при горизонтальном микропрограммирования, которая равна Nо. ч. = n, получается недопустимо большой. Место использования: В простых локальных блоках управления, где количество микроопераций не превышает нескольких десятков. 17

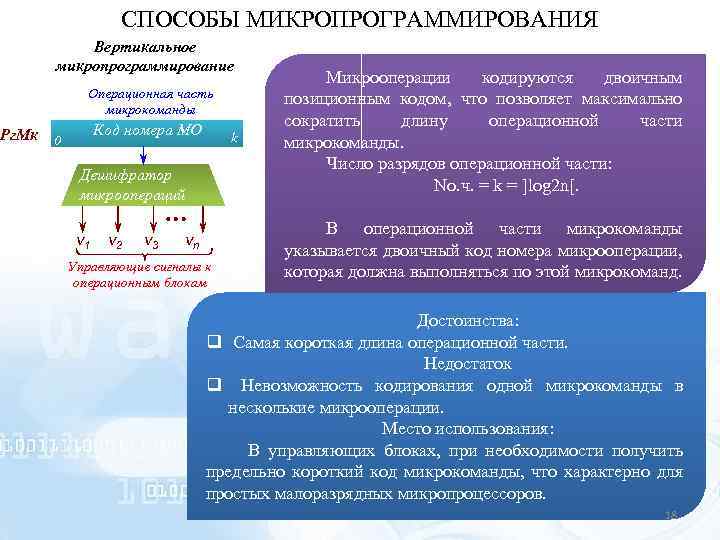

Рг. Мк СПОСОБЫ МИКРОПРОГРАММИРОВАНИЯ Вертикальное микропрограммирование Операционная часть микрокоманды 0 Код номера МО k Дешифратор микроопераций v 1 v 2 v 3 vn Управляющие сигналы к операционным блокам Микрооперации кодируются двоичным позиционным кодом, что позволяет максимально сократить длину операционной части микрокоманды. Число разрядов операционной части: Nо. ч. = k = ]log 2 n[. В операционной части микрокоманды указывается двоичный код номера микрооперации, которая должна выполняться по этой микрокоманд. Достоинства: q Самая короткая длина операционной части. Недостаток q Невозможность кодирования одной микрокоманды в несколькие микрооперации. Место использования: В управляющих блоках, при необходимости получить предельно короткий код микрокоманды, что характерно для простых малоразрядных микропроцессоров. 18

Рг. Мк СПОСОБЫ МИКРОПРОГРАММИРОВАНИЯ Вертикальное микропрограммирование Операционная часть микрокоманды 0 Код номера МО k Дешифратор микроопераций v 1 v 2 v 3 vn Управляющие сигналы к операционным блокам Микрооперации кодируются двоичным позиционным кодом, что позволяет максимально сократить длину операционной части микрокоманды. Число разрядов операционной части: Nо. ч. = k = ]log 2 n[. В операционной части микрокоманды указывается двоичный код номера микрооперации, которая должна выполняться по этой микрокоманд. Достоинства: q Самая короткая длина операционной части. Недостаток q Невозможность кодирования одной микрокоманды в несколькие микрооперации. Место использования: В управляющих блоках, при необходимости получить предельно короткий код микрокоманды, что характерно для простых малоразрядных микропроцессоров. 18

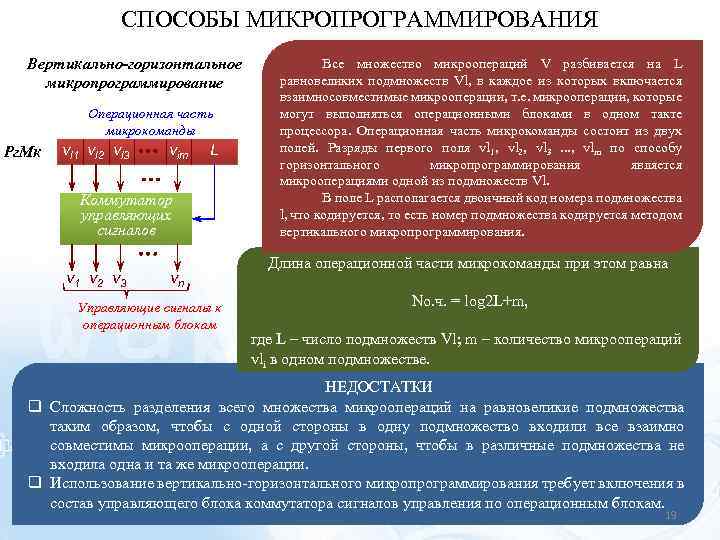

СПОСОБЫ МИКРОПРОГРАММИРОВАНИЯ Вертикально-горизонтальное микропрограммирование Операционная часть микрокоманды Рг. Мк vl 1 vl 2 vl 3 vim L Коммутатор управляющих сигналов v 1 v 2 v 3 vn Управляющие сигналы к операционным блокам Все множество микроопераций V разбивается на L равновеликих подмножеств Vl, в каждое из которых включается взаимносовместимые микрооперации, т. е. микрооперации, которые могут выполняться операционными блоками в одном такте процессора. Операционная часть микрокоманды состоит из двух полей. Разряды первого поля vl 1, vl 2, vl 3 . . . , vlm по способу горизонтального микропрограммирования является микрооперациями одной из подмножеств Vl. В поле L располагается двоичный код номера подмножества l, что кодируется, то есть номер подмножества кодируется методом вертикального микропрограммирования. Длина операционной части микрокоманды при этом равна Nо. ч. = log 2 L+m, где L – число подмножеств Vl; m – количество микроопераций vli в одном подмножестве. НЕДОСТАТКИ q Сложность разделения всего множества микроопераций на равновеликие подмножества таким образом, чтобы с одной стороны в одну подмножество входили все взаимно совместимы микрооперации, а с другой стороны, чтобы в различные подмножества не входила одна и та же микрооперации. q Использование вертикально-горизонтального микропрограммирования требует включения в состав управляющего блока коммутатора сигналов управления по операционным блокам. 19

СПОСОБЫ МИКРОПРОГРАММИРОВАНИЯ Вертикально-горизонтальное микропрограммирование Операционная часть микрокоманды Рг. Мк vl 1 vl 2 vl 3 vim L Коммутатор управляющих сигналов v 1 v 2 v 3 vn Управляющие сигналы к операционным блокам Все множество микроопераций V разбивается на L равновеликих подмножеств Vl, в каждое из которых включается взаимносовместимые микрооперации, т. е. микрооперации, которые могут выполняться операционными блоками в одном такте процессора. Операционная часть микрокоманды состоит из двух полей. Разряды первого поля vl 1, vl 2, vl 3 . . . , vlm по способу горизонтального микропрограммирования является микрооперациями одной из подмножеств Vl. В поле L располагается двоичный код номера подмножества l, что кодируется, то есть номер подмножества кодируется методом вертикального микропрограммирования. Длина операционной части микрокоманды при этом равна Nо. ч. = log 2 L+m, где L – число подмножеств Vl; m – количество микроопераций vli в одном подмножестве. НЕДОСТАТКИ q Сложность разделения всего множества микроопераций на равновеликие подмножества таким образом, чтобы с одной стороны в одну подмножество входили все взаимно совместимы микрооперации, а с другой стороны, чтобы в различные подмножества не входила одна и та же микрооперации. q Использование вертикально-горизонтального микропрограммирования требует включения в состав управляющего блока коммутатора сигналов управления по операционным блокам. 19

СПОСОБЫ МИКРОПРОГРАММИРОВАНИЯ Горизонтально-вертикальное микропрограммирование Операционная часть микрокоманды Рг. Мк Код V 1 Код V 2 Код Vk Дш1 Дш2 Дшk v 11 v 1 s v 21 v 2 s vk 1 vks Управляющие сигналы к операционным блокам Правила раздела множества микроопераций на подмножества: Взаимно совместимы микрооперации не включаются в одну подмножество. В одну подмножество входят только взаимно несовместимые микрооперации. Подмножества могут состоять из различного числа микроопераций. Микрооперации каждого подмножества кодируются по методу вертикального микропрограммирования. Для кода микрооперации каждого подмножества в операционной части микрокоманды выделяется свое поле. Подмножества между собой кодируются с горизонтальным методом. Длина операционной части микрокоманды: Nо. ч. = , где nis = log 2 s – количество разрядов, отведенных для кодирования микроопераций i - й подмножества; s - число микроопераций в i-й подмножестве, k - количество подмножеств. Минимальная длина операционной части микрокоманды будет тогда, когда число подмножеств k будет равен максимальному числу взаимно совместимых микроопераций в множестве V, а все подмножества Vi будут иметь одинаковое число элементов. ДОСТОИНСТВА q Относительная простота дешифраторов микроопераций и возможность их размещения непосредственно в операционных блоках. q В последнем случае в одну подмножество должны объединяться микрооперации, относящиеся к одной операционного блока. 20

СПОСОБЫ МИКРОПРОГРАММИРОВАНИЯ Горизонтально-вертикальное микропрограммирование Операционная часть микрокоманды Рг. Мк Код V 1 Код V 2 Код Vk Дш1 Дш2 Дшk v 11 v 1 s v 21 v 2 s vk 1 vks Управляющие сигналы к операционным блокам Правила раздела множества микроопераций на подмножества: Взаимно совместимы микрооперации не включаются в одну подмножество. В одну подмножество входят только взаимно несовместимые микрооперации. Подмножества могут состоять из различного числа микроопераций. Микрооперации каждого подмножества кодируются по методу вертикального микропрограммирования. Для кода микрооперации каждого подмножества в операционной части микрокоманды выделяется свое поле. Подмножества между собой кодируются с горизонтальным методом. Длина операционной части микрокоманды: Nо. ч. = , где nis = log 2 s – количество разрядов, отведенных для кодирования микроопераций i - й подмножества; s - число микроопераций в i-й подмножестве, k - количество подмножеств. Минимальная длина операционной части микрокоманды будет тогда, когда число подмножеств k будет равен максимальному числу взаимно совместимых микроопераций в множестве V, а все подмножества Vi будут иметь одинаковое число элементов. ДОСТОИНСТВА q Относительная простота дешифраторов микроопераций и возможность их размещения непосредственно в операционных блоках. q В последнем случае в одну подмножество должны объединяться микрооперации, относящиеся к одной операционного блока. 20

СПОСОБЫ МИКРОПРОГРАММИРОВАНИЯ Командно-ориентированное микропрограммирование Операционная часть микрокоманды Рг. Мк Номер Код Адрес операционного микро первого блока (g) операции операнда Адрес второго третьего операнда Коммутатор кода управления Местный Тактовые синхросигналы дешифратор микрооперацийй v 1 v 2 v 3 vn 21 Регистровая память процессора А 3 А 2 А 1 Операнд 1 Блок операций Операнд 2 с номером g Операнд 3 Наиболее универсальный метод микропрограммирования. Обеспечивает минимальную длину микрокоманд при большом числе микроопераций. Этот метод требует специального способа организации операционных блоков и наиболее приспособлен для работы в составе современных процессоров конвейерного типа. При этом все регистры данных процессора должны иметь единую адресацию и быть доступными для всех операционных блоков. Операционные блоки процессора должны быть пронумерованы и иметь свои средства адресации.

СПОСОБЫ МИКРОПРОГРАММИРОВАНИЯ Командно-ориентированное микропрограммирование Операционная часть микрокоманды Рг. Мк Номер Код Адрес операционного микро первого блока (g) операции операнда Адрес второго третьего операнда Коммутатор кода управления Местный Тактовые синхросигналы дешифратор микрооперацийй v 1 v 2 v 3 vn 21 Регистровая память процессора А 3 А 2 А 1 Операнд 1 Блок операций Операнд 2 с номером g Операнд 3 Наиболее универсальный метод микропрограммирования. Обеспечивает минимальную длину микрокоманд при большом числе микроопераций. Этот метод требует специального способа организации операционных блоков и наиболее приспособлен для работы в составе современных процессоров конвейерного типа. При этом все регистры данных процессора должны иметь единую адресацию и быть доступными для всех операционных блоков. Операционные блоки процессора должны быть пронумерованы и иметь свои средства адресации.

ОБЩИЕ ПРИНЦИПЫ ПОСТРОЕНИЯ ПРОЦЕССОРОВ Процессором называется устройство, непосредственно осуществляющее процесс обработки данных и программное управление этим процессом. По своим функциям процессор является центральным устройством компьютера. ФУНКЦИИ ПРОЦЕССОРА: q чтение из оперативной памяти команд в порядке их следования в программе; q дешифрация и выполнения команд программы; q организация обращения к оперативной памяти для чтения и записи операндов; q инициирование в нужных случаях работы периферийных устройств; q восприятие и обработка запросов прерывания, поступающие из устройств машины и из внешней среды. Иерархия этапов выполнения программ в процессоре: программа - команда (микропрограмма) - микрооперация. Микрооперация - это элементарное действие в процессоре (пересылка операнда из регистра в регистр, двоичное составления кодов, сдвиг кода влево или вправо и проч. ). Конкретный состав микроопераций определяется системой команд и логической структурой компьютера. Микропрограмма – это набор и последовательность выполнения микроопераций, которые приводят к выполнению определенной машинной операции. Для определения временных соотношений работы процессора используется понятие рабочего цикла и машинного такта. Время рабочего цикла процессора – время, за которое процессор выполняет одну команду. Машинный такт определяет интервал времени, в который выполняется одна или несколько микроопераций. Границы такта задаются синхросигналами, производимыми специальным формирователем. 22

ОБЩИЕ ПРИНЦИПЫ ПОСТРОЕНИЯ ПРОЦЕССОРОВ Процессором называется устройство, непосредственно осуществляющее процесс обработки данных и программное управление этим процессом. По своим функциям процессор является центральным устройством компьютера. ФУНКЦИИ ПРОЦЕССОРА: q чтение из оперативной памяти команд в порядке их следования в программе; q дешифрация и выполнения команд программы; q организация обращения к оперативной памяти для чтения и записи операндов; q инициирование в нужных случаях работы периферийных устройств; q восприятие и обработка запросов прерывания, поступающие из устройств машины и из внешней среды. Иерархия этапов выполнения программ в процессоре: программа - команда (микропрограмма) - микрооперация. Микрооперация - это элементарное действие в процессоре (пересылка операнда из регистра в регистр, двоичное составления кодов, сдвиг кода влево или вправо и проч. ). Конкретный состав микроопераций определяется системой команд и логической структурой компьютера. Микропрограмма – это набор и последовательность выполнения микроопераций, которые приводят к выполнению определенной машинной операции. Для определения временных соотношений работы процессора используется понятие рабочего цикла и машинного такта. Время рабочего цикла процессора – время, за которое процессор выполняет одну команду. Машинный такт определяет интервал времени, в который выполняется одна или несколько микроопераций. Границы такта задаются синхросигналами, производимыми специальным формирователем. 22

ОБЩИЕ ПРИНЦИПЫ ПОСТРОЕНИЯ ПРОЦЕССОРОВ КЛАССИФИКАЦИЯ ПРОЦЕССОРОВ По способу обработки числовой информации По назначению универсальные функциональноориентированные специализированные параллельные По принципу организации управления последовательные с жесткой логикой комбинированные с микропрограммным управлением По способу синхронизации синхронные 23 асинхронные Главными характеристиками ЦПУ являются: тактовая частота, производительность, энергопотребление, нормы литографического процесса используемого при производстве (для микропроцессоров) и архитектура. комбинированные

ОБЩИЕ ПРИНЦИПЫ ПОСТРОЕНИЯ ПРОЦЕССОРОВ КЛАССИФИКАЦИЯ ПРОЦЕССОРОВ По способу обработки числовой информации По назначению универсальные функциональноориентированные специализированные параллельные По принципу организации управления последовательные с жесткой логикой комбинированные с микропрограммным управлением По способу синхронизации синхронные 23 асинхронные Главными характеристиками ЦПУ являются: тактовая частота, производительность, энергопотребление, нормы литографического процесса используемого при производстве (для микропроцессоров) и архитектура. комбинированные

ОБЩИЕ ПРИНЦИПЫ ПОСТРОЕНИЯ ПРОЦЕССОРОВ КЛАССИФИКАЦИЯ ПРОЦЕССОРОВ ПО АРХИТЕКТУРЕ RISС (Reduced Instruction Set Computer) - упрощенная система команд одинакового формата типа регистр-регистр. Горизонтальное кодирование кода операции команды, не требует его дешифрации. Крайне упрощенная аппаратура процессора и низкая его стоимость. Универсальность достигается на программном уровне. Производительность повышается только за счет повышения тактовой частоты. CISC (Complex Instruction Set Computer) - используются различные формы и форматы представления данных, усложненные структуры команд с увеличенной длиной. Аппаратурная сложность процессора приводит к увеличению его стоимости MISC (Multipurpose Instruction Set Computer) - объединение RISC-процессора с микропрограммным управляющим устройством. RISC-процессор является основной частью процессора и выполняет элементарные команды за один такт. Расширенные команды преобразуются в начальные адреса микропрограмм в ПЗУ. Микропрограммы расширенных команд состоят из уже дешифрованных микрокоманд. Они выполняются быстрее, чем стандартные подпрограммы, сохраняющиеся вне процессора.

ОБЩИЕ ПРИНЦИПЫ ПОСТРОЕНИЯ ПРОЦЕССОРОВ КЛАССИФИКАЦИЯ ПРОЦЕССОРОВ ПО АРХИТЕКТУРЕ RISС (Reduced Instruction Set Computer) - упрощенная система команд одинакового формата типа регистр-регистр. Горизонтальное кодирование кода операции команды, не требует его дешифрации. Крайне упрощенная аппаратура процессора и низкая его стоимость. Универсальность достигается на программном уровне. Производительность повышается только за счет повышения тактовой частоты. CISC (Complex Instruction Set Computer) - используются различные формы и форматы представления данных, усложненные структуры команд с увеличенной длиной. Аппаратурная сложность процессора приводит к увеличению его стоимости MISC (Multipurpose Instruction Set Computer) - объединение RISC-процессора с микропрограммным управляющим устройством. RISC-процессор является основной частью процессора и выполняет элементарные команды за один такт. Расширенные команды преобразуются в начальные адреса микропрограмм в ПЗУ. Микропрограммы расширенных команд состоят из уже дешифрованных микрокоманд. Они выполняются быстрее, чем стандартные подпрограммы, сохраняющиеся вне процессора.

ОБЩИЕ ПРИНЦИПЫ ПОСТРОЕНИЯ ПРОЦЕССОРОВ Кэш память к ОП Блок связи с ОП Устройство управления памятью Блок динамического управления ОП Буфер каналов От каналов ввода-вывода ПЗУ АЛУ К другим блокам ЦУ Блок микропрограммного управления Блок выборки команд Блок адресации данных от схем контроля блоков ЦП Блок контроля и диагностики Блок программных прерываний Внешние прерывания 25 Таймер Центральное устройство управления

ОБЩИЕ ПРИНЦИПЫ ПОСТРОЕНИЯ ПРОЦЕССОРОВ Кэш память к ОП Блок связи с ОП Устройство управления памятью Блок динамического управления ОП Буфер каналов От каналов ввода-вывода ПЗУ АЛУ К другим блокам ЦУ Блок микропрограммного управления Блок выборки команд Блок адресации данных от схем контроля блоков ЦП Блок контроля и диагностики Блок программных прерываний Внешние прерывания 25 Таймер Центральное устройство управления

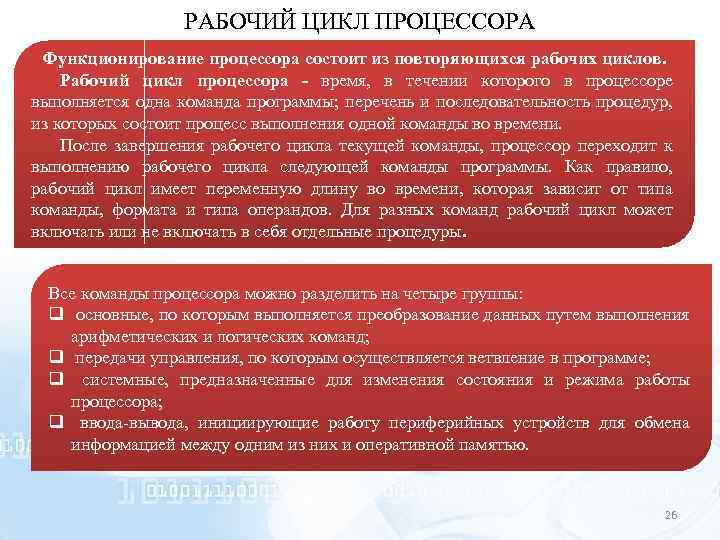

РАБОЧИЙ ЦИКЛ ПРОЦЕССОРА Функционирование процессора состоит из повторяющихся рабочих циклов. Рабочий цикл процессора - время, в течении которого в процессоре выполняется одна команда программы; перечень и последовательность процедур, из которых состоит процесс выполнения одной команды во времени. После завершения рабочего цикла текущей команды, процессор переходит к выполнению рабочего цикла следующей команды программы. Как правило, рабочий цикл имеет переменную длину во времени, которая зависит от типа команды, формата и типа операндов. Для разных команд рабочий цикл может включать или не включать в себя отдельные процедуры. Все команды процессора можно разделить на четыре группы: q основные, по которым выполняется преобразование данных путем выполнения арифметических и логических команд; q передачи управления, по которым осуществляется ветвление в программе; q системные, предназначенные для изменения состояния и режима работы процессора; q ввода-вывода, инициирующие работу периферийных устройств для обмена информацией между одним из них и оперативной памятью. 26

РАБОЧИЙ ЦИКЛ ПРОЦЕССОРА Функционирование процессора состоит из повторяющихся рабочих циклов. Рабочий цикл процессора - время, в течении которого в процессоре выполняется одна команда программы; перечень и последовательность процедур, из которых состоит процесс выполнения одной команды во времени. После завершения рабочего цикла текущей команды, процессор переходит к выполнению рабочего цикла следующей команды программы. Как правило, рабочий цикл имеет переменную длину во времени, которая зависит от типа команды, формата и типа операндов. Для разных команд рабочий цикл может включать или не включать в себя отдельные процедуры. Все команды процессора можно разделить на четыре группы: q основные, по которым выполняется преобразование данных путем выполнения арифметических и логических команд; q передачи управления, по которым осуществляется ветвление в программе; q системные, предназначенные для изменения состояния и режима работы процессора; q ввода-вывода, инициирующие работу периферийных устройств для обмена информацией между одним из них и оперативной памятью. 26

РАБОЧИЙ ЦИКЛ ПРОЦЕССОРА Начало Счет Запрос прерывания Счет или ожидание Да Да Нет Формирование адреса команды в Лч. К Ожидание Запрос прерывания Нет К обработке запросов прерывания Выборка команды Основные команды Формирование исполнительных адресов операндов Выборка операндов из памяти Выполнение операции в АЛУ Запоминание результата Анализ кода операций в команде Команды Системные Команды передачи команды ввода-вывода управления Формирование адреса Смена сост. устройств процессора Нет Условие ввода-вывода перехода Да Формирование адреса команды перехода Передача адреса перехода в Лч. К Устройство свободно Нет Да Передача в устройство ввода-вывода кода операции Перевод процессора в состояние ожидания 27

РАБОЧИЙ ЦИКЛ ПРОЦЕССОРА Начало Счет Запрос прерывания Счет или ожидание Да Да Нет Формирование адреса команды в Лч. К Ожидание Запрос прерывания Нет К обработке запросов прерывания Выборка команды Основные команды Формирование исполнительных адресов операндов Выборка операндов из памяти Выполнение операции в АЛУ Запоминание результата Анализ кода операций в команде Команды Системные Команды передачи команды ввода-вывода управления Формирование адреса Смена сост. устройств процессора Нет Условие ввода-вывода перехода Да Формирование адреса команды перехода Передача адреса перехода в Лч. К Устройство свободно Нет Да Передача в устройство ввода-вывода кода операции Перевод процессора в состояние ожидания 27

РАБОЧИЙ ЦИКЛ КОМАНДЫ ПЕРЕДАЧИ УПРАВЛЕНИЯ Проверяется заданное полем маски условие перехода. Если условие не выполняется, то адрес следующей команды берется из счетчика команд, т. е. продолжается естественный порядок выборки команд, а команда условного перехода игнорируется. При выполнении условия перехода адрес следующей команды формируется по информации, записанной в адресной части команды перехода. При этом содержимое счетчика команд заменяется адресом перехода, вновь сформированным. Команды ввода-вывода в микропроцессорах малых компьютеров инициируют передачу в адресную шину адреса порта периферийного устройства, а в шину данных - команды ввода-вывода. После чего процессор, как правило, переходит в режим ожидания и приостанавливает свою работу до получения запроса прерывания от запущенного периферийного устройства, чтобы определить по нему реакцию периферийного устройства и свои дальнейшие действия. Системные команды осуществляют переключение состояния процессора и программ путем загрузки нового вектора состояния процессора или его частей. В частности, эти команды меняют маски прерывания, устанавливают ключи защиты памяти (уровни привилегий), реализуют операции прямого управления. 28

РАБОЧИЙ ЦИКЛ КОМАНДЫ ПЕРЕДАЧИ УПРАВЛЕНИЯ Проверяется заданное полем маски условие перехода. Если условие не выполняется, то адрес следующей команды берется из счетчика команд, т. е. продолжается естественный порядок выборки команд, а команда условного перехода игнорируется. При выполнении условия перехода адрес следующей команды формируется по информации, записанной в адресной части команды перехода. При этом содержимое счетчика команд заменяется адресом перехода, вновь сформированным. Команды ввода-вывода в микропроцессорах малых компьютеров инициируют передачу в адресную шину адреса порта периферийного устройства, а в шину данных - команды ввода-вывода. После чего процессор, как правило, переходит в режим ожидания и приостанавливает свою работу до получения запроса прерывания от запущенного периферийного устройства, чтобы определить по нему реакцию периферийного устройства и свои дальнейшие действия. Системные команды осуществляют переключение состояния процессора и программ путем загрузки нового вектора состояния процессора или его частей. В частности, эти команды меняют маски прерывания, устанавливают ключи защиты памяти (уровни привилегий), реализуют операции прямого управления. 28

ПРОГРАММНАЯ МОДЕЛЬ 32 -РАЗРЯДНОГО ПРОЦЕССОРА Общие регистры данных и адресов 31 1 6 15 0 AH BH CH DH AX BX CX DX SI DI BP SP AL BL CL DL EAX EBX ECX EDX ESI EDI EBP ESP Регистры сегментов 15 0 CS Код SS Стек DS ES Данные FS GS в реальном режиме сохраняют 16 -битные указатель сегментов кода (CS), стека (SS) и данных (DS и ES) в защищенном режиме – 16 битные селекторы Временно сохраняют текущие операнды дескрипторов сегментов активной задачи, в том операций и адресную информацию. Имеют числе и дополнительных сегментов данных (FS размеры: и GS). в реальном режиме – 16 разрядов; в защищенном режиме – 32 разряда. Указатель инструкций и Управляющие регистры регистр флагов 31 16 15 0 IP FLAGS EIP EFLAGS IP – смещение следующей команды относительно начала сегмента кода. FLAGS – флаги состояния процессора и выполняемой задачи. CR 3 CR 2 CR 1 CR 0 Хранят общие для всех задач признаки состояния процессора. Не используется

ПРОГРАММНАЯ МОДЕЛЬ 32 -РАЗРЯДНОГО ПРОЦЕССОРА Общие регистры данных и адресов 31 1 6 15 0 AH BH CH DH AX BX CX DX SI DI BP SP AL BL CL DL EAX EBX ECX EDX ESI EDI EBP ESP Регистры сегментов 15 0 CS Код SS Стек DS ES Данные FS GS в реальном режиме сохраняют 16 -битные указатель сегментов кода (CS), стека (SS) и данных (DS и ES) в защищенном режиме – 16 битные селекторы Временно сохраняют текущие операнды дескрипторов сегментов активной задачи, в том операций и адресную информацию. Имеют числе и дополнительных сегментов данных (FS размеры: и GS). в реальном режиме – 16 разрядов; в защищенном режиме – 32 разряда. Указатель инструкций и Управляющие регистры регистр флагов 31 16 15 0 IP FLAGS EIP EFLAGS IP – смещение следующей команды относительно начала сегмента кода. FLAGS – флаги состояния процессора и выполняемой задачи. CR 3 CR 2 CR 1 CR 0 Хранят общие для всех задач признаки состояния процессора. Не используется

ПРОГРАММНАЯ МОДЕЛЬ 32 -РАЗРЯДНОГО ПРОЦЕССОРА Системные адресные регистры Используются только в защищенном режиме для ссылки на таблицы и сегменты Системные указатели 47 Линейный базовый адрес 16 15 Граница 0 FLAGS GDTR IDTR GDTR (Global Descriptor Table Register) – регистр, содержащий адрес начала и размер глобальной таблицы дескрипторов. IDTR (Interrupt Descriptor Table Register) – регистр, содержащий адрес начала и размер таблицы дескрипторов прерываний. Системные сегментные регистры 15 Селектор 0 TR LDTR Регистры дескрипторов, автоматически загружающиеся 71 Линейный адрес 40 39 Граница сегмента 8 7 Атрибуты 0 FLAGS TR (Task Register) – регистр задачи, содержащий селектор дескриптора сегмента состояния текущей задачи TSS. LDTR (Local Descriptor Table Register) – регистр, содержащий селектор дескриптора локальной таблицы дескрипторов LDT по текущей задаче. При загрузке селекторов активной задачи в эти системные регистры одновременно загружаются сами дескрипторы в 72 -разрядные теневые регистры процессора, которые программно не доступны.

ПРОГРАММНАЯ МОДЕЛЬ 32 -РАЗРЯДНОГО ПРОЦЕССОРА Системные адресные регистры Используются только в защищенном режиме для ссылки на таблицы и сегменты Системные указатели 47 Линейный базовый адрес 16 15 Граница 0 FLAGS GDTR IDTR GDTR (Global Descriptor Table Register) – регистр, содержащий адрес начала и размер глобальной таблицы дескрипторов. IDTR (Interrupt Descriptor Table Register) – регистр, содержащий адрес начала и размер таблицы дескрипторов прерываний. Системные сегментные регистры 15 Селектор 0 TR LDTR Регистры дескрипторов, автоматически загружающиеся 71 Линейный адрес 40 39 Граница сегмента 8 7 Атрибуты 0 FLAGS TR (Task Register) – регистр задачи, содержащий селектор дескриптора сегмента состояния текущей задачи TSS. LDTR (Local Descriptor Table Register) – регистр, содержащий селектор дескриптора локальной таблицы дескрипторов LDT по текущей задаче. При загрузке селекторов активной задачи в эти системные регистры одновременно загружаются сами дескрипторы в 72 -разрядные теневые регистры процессора, которые программно не доступны.

РЕЖИМЫ РАБОТЫ ПРОЦЕССОРА Режим реальной адресации (Real Address Mode) – режим работы первого микропроцессора Intel 8086. Возможна адресация до 1 Мбайт оперативной памяти. В одно время в компьютере может выполняться только одна задача. Этот режим используется для начальной загрузки компьютера при его включении и по сигналу системного сброса RESET, а также при выполнении некоторых системных процедур. Может работать только под управлением операционной системы типа DOS. Защищенный режим виртуальной адресации (Protected Virtual Address Mode) – основной режим работы современных процессоров. Позволяет адресовать до 4 Гбайт оперативной памяти и до 64 Тбайт виртуальной памяти. Одновременно позволяет запустить на выполнение несколько вычислительных процессов. Позволяет распределять ресурсы между задачами, защиту ресурсов от соседних задач. Этот режим является основным для современных компьютеров, работающих под управлением многозадачных ОС типа Windows, Unix и др. Режим эмуляции реального режима адресации (Virtual 8086 Mode) - режим виртуального процессора Intel 8086 является особым состоянием задачи защищенного режима, в котором процессор работает как і 8086. На одном процессоре в этом режиме может выполняться несколько задач с изолированными друг от друга ресурсами. При этом управление памятью выполняется так же, как и в защищенном режиме. Используется при выполнении старых программ, которые были созданы под операционную систему типа DOS. Режим системного управления (System Management Mode) – особый режим процессора, который использует изолированное от других режимов пространство памяти. Используется в служебных целях и для отладки.

РЕЖИМЫ РАБОТЫ ПРОЦЕССОРА Режим реальной адресации (Real Address Mode) – режим работы первого микропроцессора Intel 8086. Возможна адресация до 1 Мбайт оперативной памяти. В одно время в компьютере может выполняться только одна задача. Этот режим используется для начальной загрузки компьютера при его включении и по сигналу системного сброса RESET, а также при выполнении некоторых системных процедур. Может работать только под управлением операционной системы типа DOS. Защищенный режим виртуальной адресации (Protected Virtual Address Mode) – основной режим работы современных процессоров. Позволяет адресовать до 4 Гбайт оперативной памяти и до 64 Тбайт виртуальной памяти. Одновременно позволяет запустить на выполнение несколько вычислительных процессов. Позволяет распределять ресурсы между задачами, защиту ресурсов от соседних задач. Этот режим является основным для современных компьютеров, работающих под управлением многозадачных ОС типа Windows, Unix и др. Режим эмуляции реального режима адресации (Virtual 8086 Mode) - режим виртуального процессора Intel 8086 является особым состоянием задачи защищенного режима, в котором процессор работает как і 8086. На одном процессоре в этом режиме может выполняться несколько задач с изолированными друг от друга ресурсами. При этом управление памятью выполняется так же, как и в защищенном режиме. Используется при выполнении старых программ, которые были созданы под операционную систему типа DOS. Режим системного управления (System Management Mode) – особый режим процессора, который использует изолированное от других режимов пространство памяти. Используется в служебных целях и для отладки.

РЕЖИМЫ РАБОТЫ ПРОЦЕССОРА Режим реальной адресации (RM) RESET # или PЕ=0 SMI # RESET # или RSM PЕ=1 Защищенный режим (РM) VM=0 SMI # RSM Режим системного управления (SMM) VM=1 Режим эмуляции реальной адресации (VM) SMI # RSM Reset # – сигнал системного сброса, всегда переводит процессор в режим реальной адресации. SMI # – сигнал прерывания для включения режима системного управления. РЕ – флаг установления режима защиты памяти, находящийся в управляющем регистре CR 0. VM – флаг установки виртуального режима адресации из защищенного режима, который находится в регистре флагов EFLAGS.

РЕЖИМЫ РАБОТЫ ПРОЦЕССОРА Режим реальной адресации (RM) RESET # или PЕ=0 SMI # RESET # или RSM PЕ=1 Защищенный режим (РM) VM=0 SMI # RSM Режим системного управления (SMM) VM=1 Режим эмуляции реальной адресации (VM) SMI # RSM Reset # – сигнал системного сброса, всегда переводит процессор в режим реальной адресации. SMI # – сигнал прерывания для включения режима системного управления. РЕ – флаг установления режима защиты памяти, находящийся в управляющем регистре CR 0. VM – флаг установки виртуального режима адресации из защищенного режима, который находится в регистре флагов EFLAGS.

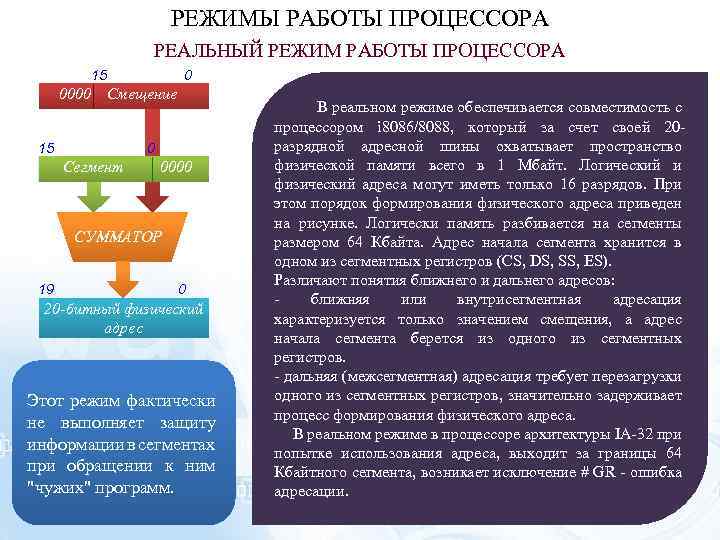

РЕЖИМЫ РАБОТЫ ПРОЦЕССОРА РЕАЛЬНЫЙ РЕЖИМ РАБОТЫ ПРОЦЕССОРА 15 0 0000 Смещение 15 0 Сегмент 0000 СУММАТОР 19 0 20 -битный физический адрес Этот режим фактически не выполняет защиту информации в сегментах при обращении к ним "чужих" программ. В реальном режиме обеспечивается совместимость с процессором і 8086/8088, который за счет своей 20 разрядной адресной шины охватывает пространство физической памяти всего в 1 Мбайт. Логический и физический адреса могут иметь только 16 разрядов. При этом порядок формирования физического адреса приведен на рисунке. Логически память разбивается на сегменты размером 64 Кбайта. Адрес начала сегмента хранится в одном из сегментных регистров (CS, DS, SS, ES). Различают понятия ближнего и дальнего адресов: - ближняя или внутрисегментная адресация характеризуется только значением смещения, а адрес начала сегмента берется из одного из сегментных регистров. - дальняя (межсегментная) адресация требует перезагрузки одного из сегментных регистров, значительно задерживает процесс формирования физического адреса. В реальном режиме в процессоре архитектуры IA-32 при попытке использования адреса, выходит за границы 64 Кбайтного сегмента, возникает исключение # GR - ошибка адресации.

РЕЖИМЫ РАБОТЫ ПРОЦЕССОРА РЕАЛЬНЫЙ РЕЖИМ РАБОТЫ ПРОЦЕССОРА 15 0 0000 Смещение 15 0 Сегмент 0000 СУММАТОР 19 0 20 -битный физический адрес Этот режим фактически не выполняет защиту информации в сегментах при обращении к ним "чужих" программ. В реальном режиме обеспечивается совместимость с процессором і 8086/8088, который за счет своей 20 разрядной адресной шины охватывает пространство физической памяти всего в 1 Мбайт. Логический и физический адреса могут иметь только 16 разрядов. При этом порядок формирования физического адреса приведен на рисунке. Логически память разбивается на сегменты размером 64 Кбайта. Адрес начала сегмента хранится в одном из сегментных регистров (CS, DS, SS, ES). Различают понятия ближнего и дальнего адресов: - ближняя или внутрисегментная адресация характеризуется только значением смещения, а адрес начала сегмента берется из одного из сегментных регистров. - дальняя (межсегментная) адресация требует перезагрузки одного из сегментных регистров, значительно задерживает процесс формирования физического адреса. В реальном режиме в процессоре архитектуры IA-32 при попытке использования адреса, выходит за границы 64 Кбайтного сегмента, возникает исключение # GR - ошибка адресации.

РЕЖИМЫ РАБОТЫ ПРОЦЕССОРА ЗАЩИЩЕННЫЙ РЕЖИМ РАБОТЫ ПРОЦЕССОРА Защищенный режим обеспечивает независимость выполнения нескольких задач, что подразумевает защиту ресурсов одних задач от возможного воздействия других. Основным защищаемым ресурсом есть память, в которой хранятся коды программ, данных и различные системные таблицы. Защите подлежат также и аппаратные средства, используемые совместно (например, система ввода-вывода, система прерываний). Защита памяти основана на механизме сегментации. Сегмент - это блок пространства памяти определенного назначения. Максимальный размер сегмента в защищенном режиме составляет 4 ГБ. Каждый сегмент описывается своим дескриптором. При инициализации операционной системы, она создает в оперативной памяти глобальную таблицу дескрипторов сегментов. При первом запуске программы операционная система выделяет ей нужны сегменты, которые жестко закрепляются за программой путем формирования дескрипторов этих сегментов и записи их в таблицы дескрипторов сегментов. При этом для программы может формироваться своя локальная таблица дескрипторов сегментов. В дальнейшем операционная система осуществляет выбор нужных сегментов для программы из таблиц дескрипторов сегментов. При этом она позволяет обращение только к тем сегментам, которые присвоены программе, и запрещает обращения программы к чужим сегментам. Процессор может обращаться только к тем сегментам, дескрипторы которых есть в таблицах дескрипторов сегментов. Обращение к дескрипторам сегментов в процессоре производится с помощью 16 -разрядных селекторов и поддерживается аппаратно. В зависимости от значения флага селектора ТІ выбор дескриптора производится либо с глобальной таблицы дескрипторов (когда ТІ = 0), или из локальной (когда ТІ = 1).

РЕЖИМЫ РАБОТЫ ПРОЦЕССОРА ЗАЩИЩЕННЫЙ РЕЖИМ РАБОТЫ ПРОЦЕССОРА Защищенный режим обеспечивает независимость выполнения нескольких задач, что подразумевает защиту ресурсов одних задач от возможного воздействия других. Основным защищаемым ресурсом есть память, в которой хранятся коды программ, данных и различные системные таблицы. Защите подлежат также и аппаратные средства, используемые совместно (например, система ввода-вывода, система прерываний). Защита памяти основана на механизме сегментации. Сегмент - это блок пространства памяти определенного назначения. Максимальный размер сегмента в защищенном режиме составляет 4 ГБ. Каждый сегмент описывается своим дескриптором. При инициализации операционной системы, она создает в оперативной памяти глобальную таблицу дескрипторов сегментов. При первом запуске программы операционная система выделяет ей нужны сегменты, которые жестко закрепляются за программой путем формирования дескрипторов этих сегментов и записи их в таблицы дескрипторов сегментов. При этом для программы может формироваться своя локальная таблица дескрипторов сегментов. В дальнейшем операционная система осуществляет выбор нужных сегментов для программы из таблиц дескрипторов сегментов. При этом она позволяет обращение только к тем сегментам, которые присвоены программе, и запрещает обращения программы к чужим сегментам. Процессор может обращаться только к тем сегментам, дескрипторы которых есть в таблицах дескрипторов сегментов. Обращение к дескрипторам сегментов в процессоре производится с помощью 16 -разрядных селекторов и поддерживается аппаратно. В зависимости от значения флага селектора ТІ выбор дескриптора производится либо с глобальной таблицы дескрипторов (когда ТІ = 0), или из локальной (когда ТІ = 1).

РЕЖИМЫ РАБОТЫ ПРОЦЕССОРА ЗАЩИЩЕННЫЙ РЕЖИМ РАБОТЫ ПРОЦЕССОРА Защищенный режим обеспечивает независимость выполнения нескольких задач, что подразумевает защиту ресурсов одних задач от возможного воздействия других. Основным защищаемым ресурсом есть память, в которой хранятся коды программ, данных и различные системные таблицы. Защите подлежат также и аппаратные средства, используемые совместно (например, система ввода-вывода, система прерываний). Защита памяти основана на механизме сегментации. Сегмент - это блок пространства памяти определенного назначения. Максимальный размер сегмента в защищенном режиме составляет 4 ГБ. Каждый сегмент описывается своим дескриптором. При инициализации операционной системы, она создает в оперативной памяти глобальную таблицу дескрипторов сегментов. При первом запуске программы операционная система выделяет ей нужны сегменты, которые жестко закрепляются за программой путем формирования дескрипторов этих сегментов и записи их в таблицы дескрипторов сегментов. При этом для программы может формироваться своя локальная таблица дескрипторов сегментов. В дальнейшем операционная система осуществляет выбор нужных сегментов для программы из таблиц дескрипторов сегментов. При этом она позволяет обращение только к тем сегментам, которые присвоены программе, и запрещает обращения программы к чужим сегментам. Процессор может обращаться только к тем сегментам, дескрипторы которых есть в таблицах дескрипторов сегментов. Обращение к дескрипторам сегментов в процессоре производится с помощью 16 -разрядных селекторов и поддерживается аппаратно. В зависимости от значения флага селектора ТІ выбор дескриптора производится либо с глобальной таблицы дескрипторов (когда ТІ = 0), или из локальной (когда ТІ = 1).

РЕЖИМЫ РАБОТЫ ПРОЦЕССОРА ЗАЩИЩЕННЫЙ РЕЖИМ РАБОТЫ ПРОЦЕССОРА Защищенный режим обеспечивает независимость выполнения нескольких задач, что подразумевает защиту ресурсов одних задач от возможного воздействия других. Основным защищаемым ресурсом есть память, в которой хранятся коды программ, данных и различные системные таблицы. Защите подлежат также и аппаратные средства, используемые совместно (например, система ввода-вывода, система прерываний). Защита памяти основана на механизме сегментации. Сегмент - это блок пространства памяти определенного назначения. Максимальный размер сегмента в защищенном режиме составляет 4 ГБ. Каждый сегмент описывается своим дескриптором. При инициализации операционной системы, она создает в оперативной памяти глобальную таблицу дескрипторов сегментов. При первом запуске программы операционная система выделяет ей нужны сегменты, которые жестко закрепляются за программой путем формирования дескрипторов этих сегментов и записи их в таблицы дескрипторов сегментов. При этом для программы может формироваться своя локальная таблица дескрипторов сегментов. В дальнейшем операционная система осуществляет выбор нужных сегментов для программы из таблиц дескрипторов сегментов. При этом она позволяет обращение только к тем сегментам, которые присвоены программе, и запрещает обращения программы к чужим сегментам. Процессор может обращаться только к тем сегментам, дескрипторы которых есть в таблицах дескрипторов сегментов. Обращение к дескрипторам сегментов в процессоре производится с помощью 16 -разрядных селекторов и поддерживается аппаратно. В зависимости от значения флага селектора ТІ выбор дескриптора производится либо с глобальной таблицы дескрипторов (когда ТІ = 0), или из локальной (когда ТІ = 1).

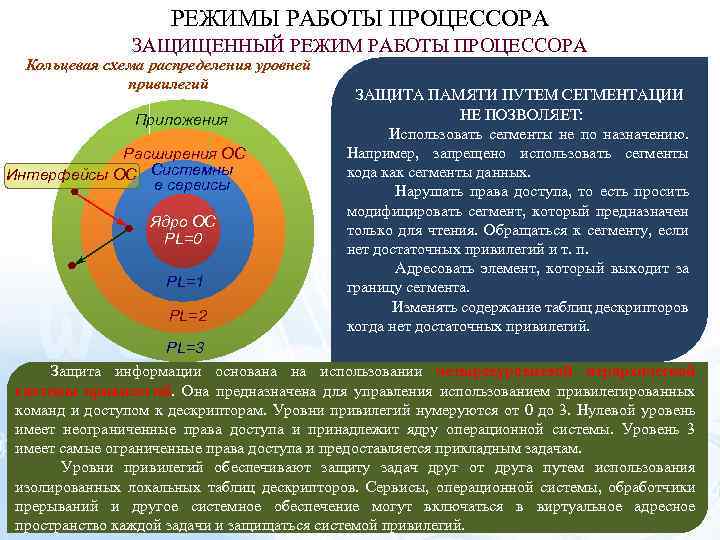

РЕЖИМЫ РАБОТЫ ПРОЦЕССОРА ЗАЩИЩЕННЫЙ РЕЖИМ РАБОТЫ ПРОЦЕССОРА Кольцевая схема распределения уровней привилегий Приложения Расширения ОС Интерфейсы ОС Системны е сервисы Ядро ОС PL=0 PL=1 PL=2 ЗАЩИТА ПАМЯТИ ПУТЕМ СЕГМЕНТАЦИИ НЕ ПОЗВОЛЯЕТ: Использовать сегменты не по назначению. Например, запрещено использовать сегменты кода как сегменты данных. Нарушать права доступа, то есть просить модифицировать сегмент, который предназначен только для чтения. Обращаться к сегменту, если нет достаточных привилегий и т. п. Адресовать элемент, который выходит за границу сегмента. Изменять содержание таблиц дескрипторов когда нет достаточных привилегий. PL=3 Защита информации основана на использовании четырехуровневой иерархической системы привилегий. Она предназначена для управления использованием привилегированных команд и доступом к дескрипторам. Уровни привилегий нумеруются от 0 до 3. Нулевой уровень имеет неограниченные права доступа и принадлежит ядру операционной системы. Уровень 3 имеет самые ограниченные права доступа и предоставляется прикладным задачам. Уровни привилегий обеспечивают защиту задач друг от друга путем использования изолированных локальных таблиц дескрипторов. Сервисы, операционной системы, обработчики прерываний и другое системное обеспечение могут включаться в виртуальное адресное пространство каждой задачи и защищаться системой привилегий.