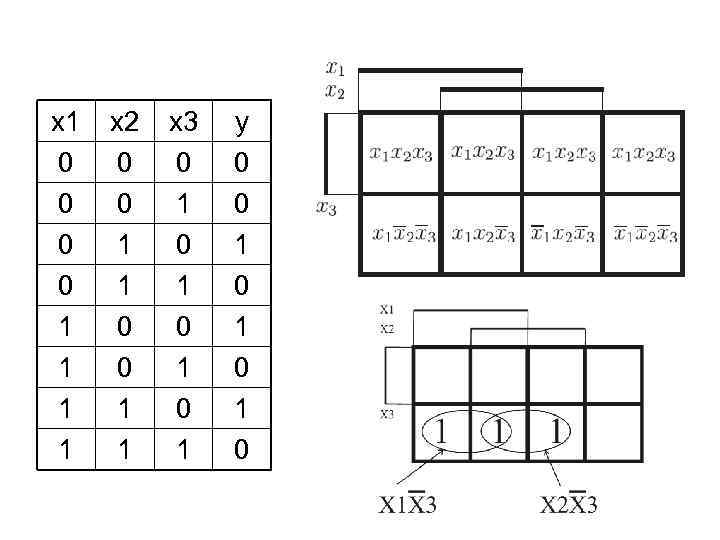

x 1 0 0 1 1 x 2 0 0 1 1 x 3 0 1 0 1 y 0 0 1 0 1 0

x 1 0 0 1 1 x 2 0 0 1 1 x 3 0 1 0 1 y 0 0 1 0 1 0

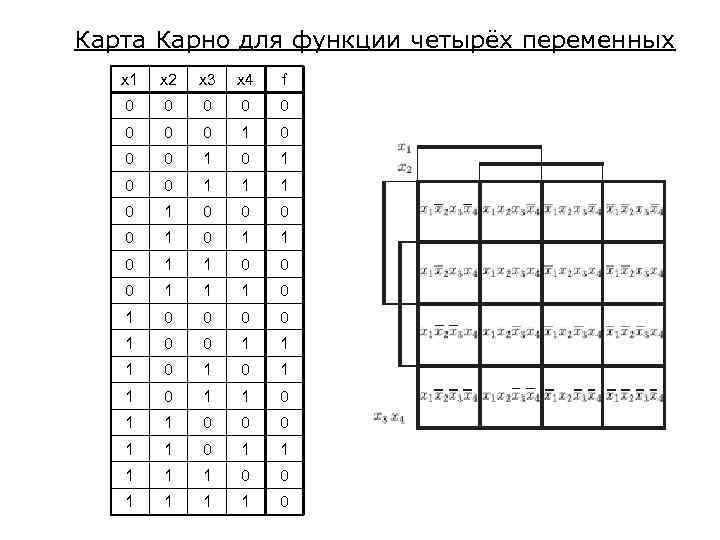

Карта Карно для функции четырёх переменных x 1 x 2 x 3 x 4 f 0 0 0 0 1 0 0 1 1 1 0 0 0 0 1 1 0 0 0 1 1 1 0 1 1 0 0 0 1 1 1 1 1 0 0 1 1 0

Карта Карно для функции четырёх переменных x 1 x 2 x 3 x 4 f 0 0 0 0 1 0 0 1 1 1 0 0 0 0 1 1 0 0 0 1 1 1 0 1 1 0 0 0 1 1 1 1 1 0 0 1 1 0

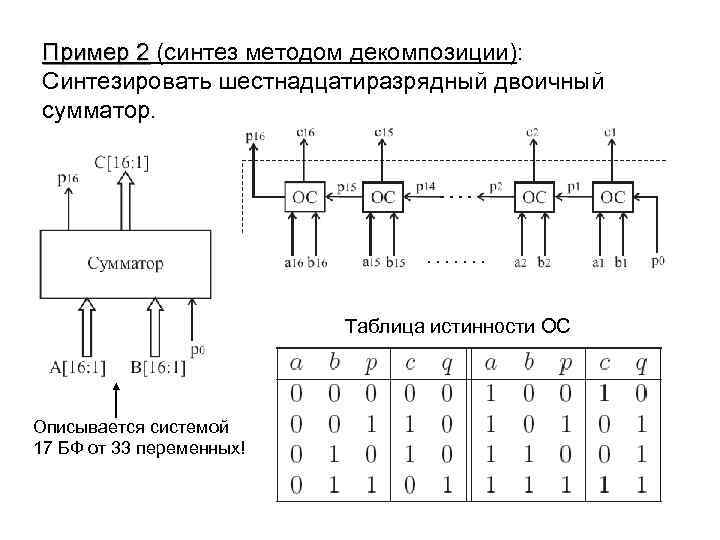

Пример 2 (синтез методом декомпозиции): Синтезировать шестнадцатиразрядный двоичный сумматор. Таблица истинности ОС Описывается системой 17 БФ от 33 переменных!

Пример 2 (синтез методом декомпозиции): Синтезировать шестнадцатиразрядный двоичный сумматор. Таблица истинности ОС Описывается системой 17 БФ от 33 переменных!

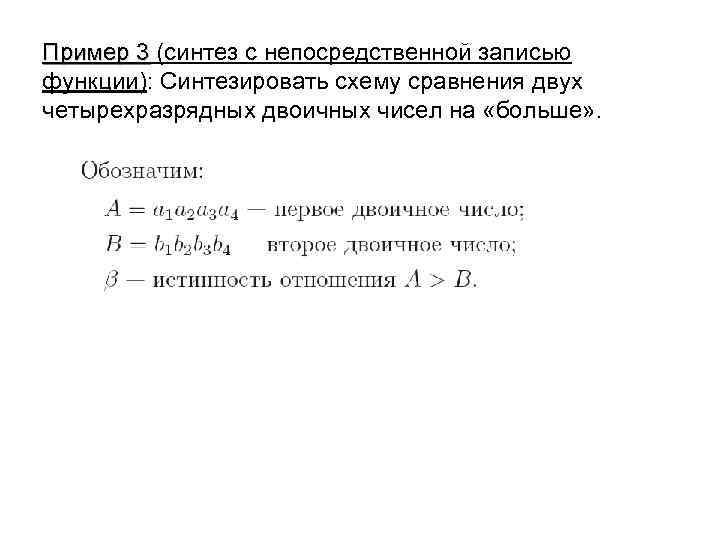

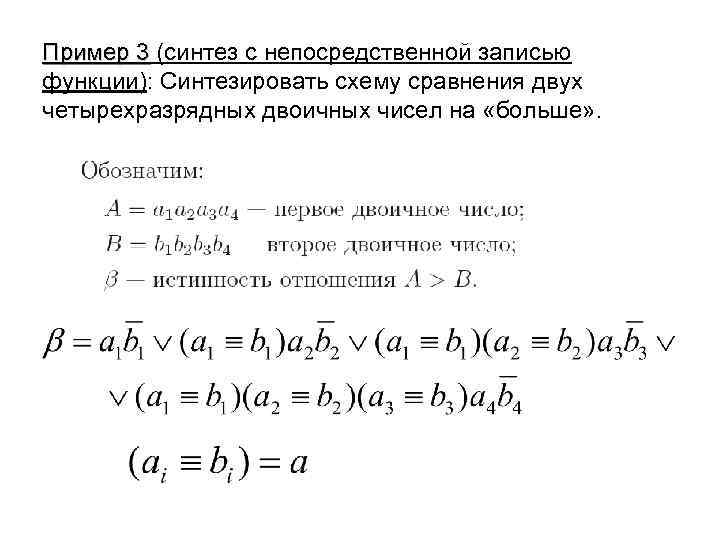

Пример 3 (синтез с непосредственной записью функции): Синтезировать схему сравнения двух четырехразрядных двоичных чисел на «больше» .

Пример 3 (синтез с непосредственной записью функции): Синтезировать схему сравнения двух четырехразрядных двоичных чисел на «больше» .

Пример 3 (синтез с непосредственной записью функции): Синтезировать схему сравнения двух четырехразрядных двоичных чисел на «больше» .

Пример 3 (синтез с непосредственной записью функции): Синтезировать схему сравнения двух четырехразрядных двоичных чисел на «больше» .

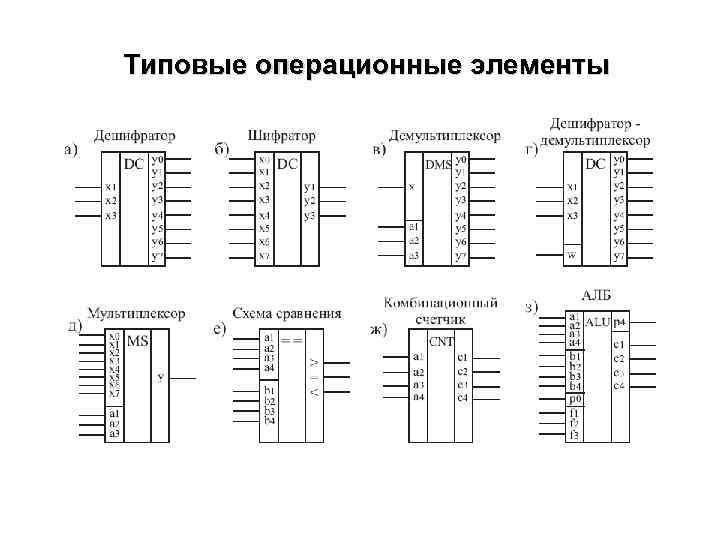

Типовые операционные элементы

Типовые операционные элементы

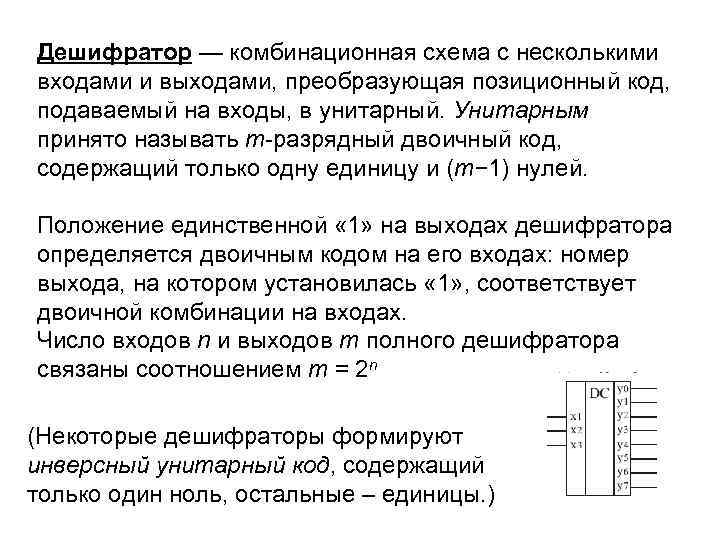

Дешифратор — комбинационная схема с несколькими входами и выходами, преобразующая позиционный код, подаваемый на входы, в унитарный. Унитарным принято называть m-разрядный двоичный код, содержащий только одну единицу и (m− 1) нулей. Положение единственной « 1» на выходах дешифратора определяется двоичным кодом на его входах: номер выхода, на котором установилась « 1» , соответствует двоичной комбинации на входах. Число входов n и выходов m полного дешифратора связаны соотношением m = 2 n (Некоторые дешифраторы формируют инверсный унитарный код, содержащий только один ноль, остальные – единицы. )

Дешифратор — комбинационная схема с несколькими входами и выходами, преобразующая позиционный код, подаваемый на входы, в унитарный. Унитарным принято называть m-разрядный двоичный код, содержащий только одну единицу и (m− 1) нулей. Положение единственной « 1» на выходах дешифратора определяется двоичным кодом на его входах: номер выхода, на котором установилась « 1» , соответствует двоичной комбинации на входах. Число входов n и выходов m полного дешифратора связаны соотношением m = 2 n (Некоторые дешифраторы формируют инверсный унитарный код, содержащий только один ноль, остальные – единицы. )

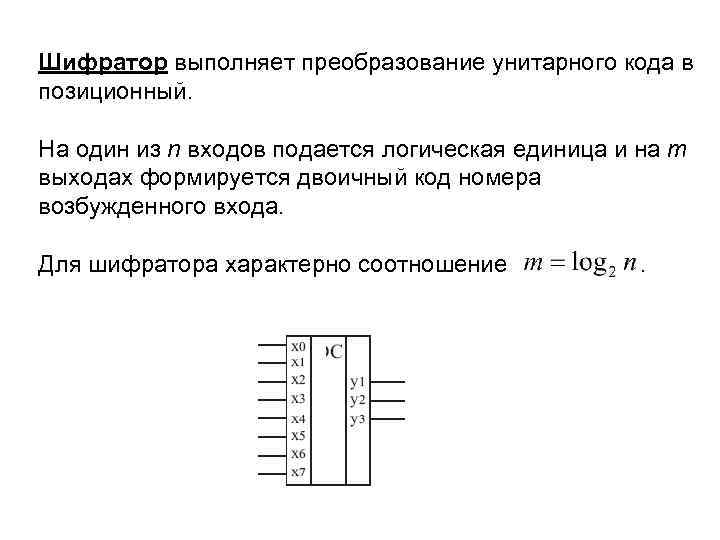

Шифратор выполняет преобразование унитарного кода в позиционный. На один из n входов подается логическая единица и на m выходах формируется двоичный код номера возбужденного входа. Для шифратора характерно соотношение .

Шифратор выполняет преобразование унитарного кода в позиционный. На один из n входов подается логическая единица и на m выходах формируется двоичный код номера возбужденного входа. Для шифратора характерно соотношение .

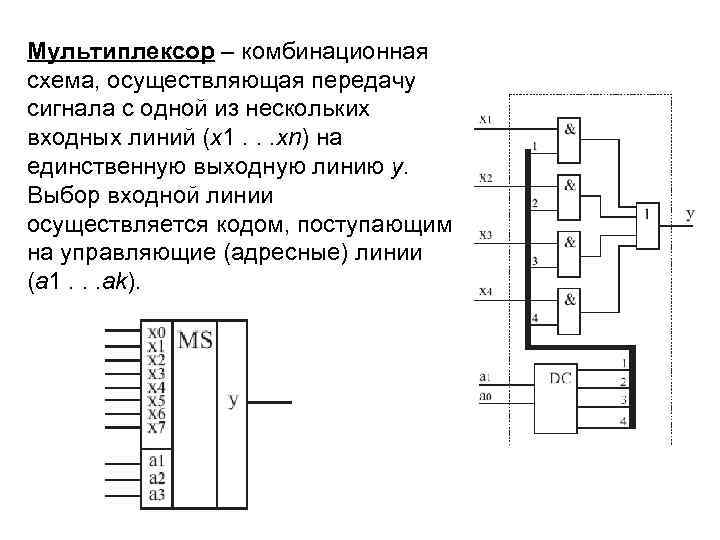

Мультиплексор – комбинационная схема, осуществляющая передачу сигнала с одной из нескольких входных линий (x 1. . . xn) на единственную выходную линию y. Выбор входной линии осуществляется кодом, поступающим на управляющие (адресные) линии (a 1. . . ak).

Мультиплексор – комбинационная схема, осуществляющая передачу сигнала с одной из нескольких входных линий (x 1. . . xn) на единственную выходную линию y. Выбор входной линии осуществляется кодом, поступающим на управляющие (адресные) линии (a 1. . . ak).

Демультиплексор выполняет операцию, обратную мультиплексированию – передает сигнал с единственной входной линии x на одну из нескольких выходных линий (y 1. . . ym), номер которой (адрес) задается на управляющих линиях (a 1. . . ak).

Демультиплексор выполняет операцию, обратную мультиплексированию – передает сигнал с единственной входной линии x на одну из нескольких выходных линий (y 1. . . ym), номер которой (адрес) задается на управляющих линиях (a 1. . . ak).

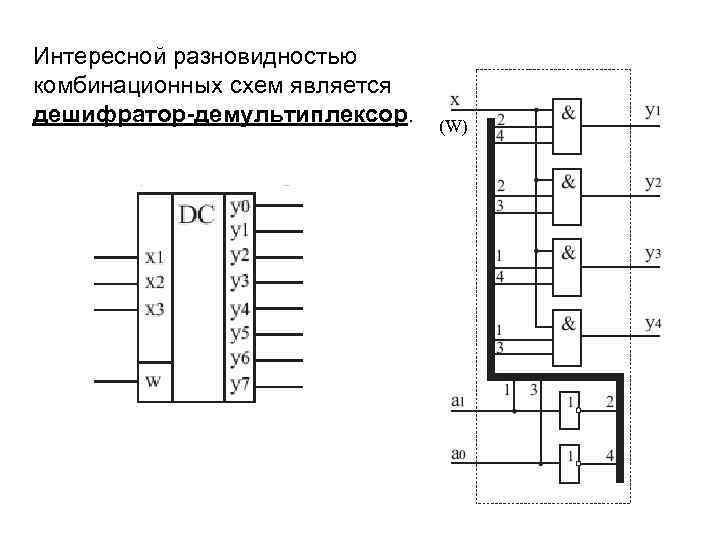

Интересной разновидностью комбинационных схем является дешифратор-демультиплексор. (W)

Интересной разновидностью комбинационных схем является дешифратор-демультиплексор. (W)

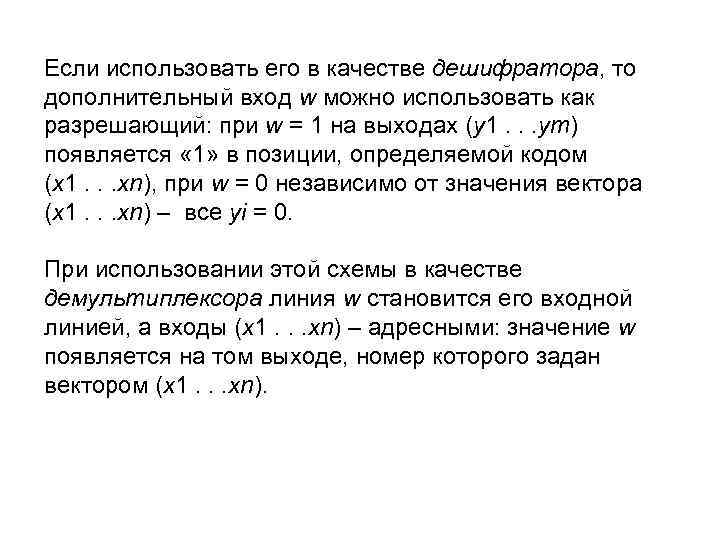

Если использовать его в качестве дешифратора, то дополнительный вход w можно использовать как разрешающий: при w = 1 на выходах (y 1. . . ym) появляется « 1» в позиции, определяемой кодом (x 1. . . xn), при w = 0 независимо от значения вектора (x 1. . . xn) – все yi = 0. При использовании этой схемы в качестве демультиплексора линия w становится его входной линией, а входы (x 1. . . xn) – адресными: значение w появляется на том выходе, номер которого задан вектором (x 1. . . xn).

Если использовать его в качестве дешифратора, то дополнительный вход w можно использовать как разрешающий: при w = 1 на выходах (y 1. . . ym) появляется « 1» в позиции, определяемой кодом (x 1. . . xn), при w = 0 независимо от значения вектора (x 1. . . xn) – все yi = 0. При использовании этой схемы в качестве демультиплексора линия w становится его входной линией, а входы (x 1. . . xn) – адресными: значение w появляется на том выходе, номер которого задан вектором (x 1. . . xn).

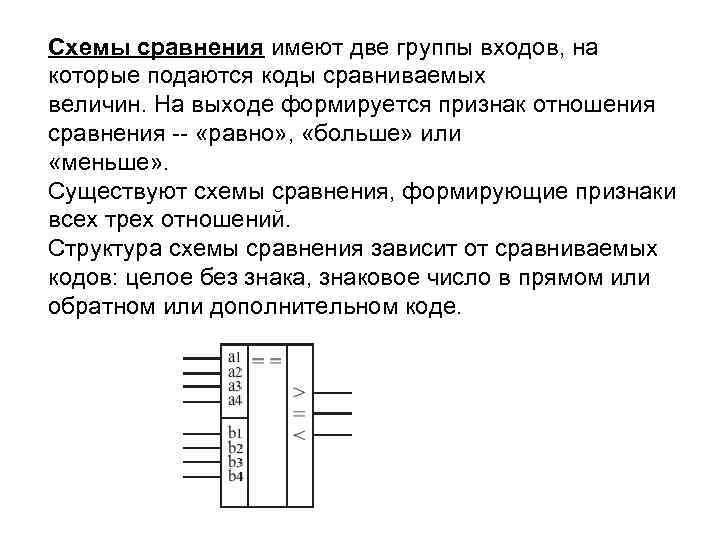

Схемы сравнения имеют две группы входов, на которые подаются коды сравниваемых величин. На выходе формируется признак отношения сравнения -- «равно» , «больше» или «меньше» . Существуют схемы сравнения, формирующие признаки всех трех отношений. Структура схемы сравнения зависит от сравниваемых кодов: целое без знака, знаковое число в прямом или обратном или дополнительном коде.

Схемы сравнения имеют две группы входов, на которые подаются коды сравниваемых величин. На выходе формируется признак отношения сравнения -- «равно» , «больше» или «меньше» . Существуют схемы сравнения, формирующие признаки всех трех отношений. Структура схемы сравнения зависит от сравниваемых кодов: целое без знака, знаковое число в прямом или обратном или дополнительном коде.

Сдвигатели принимают на вход многоразрядный двоичный код и выдают на выходе тот же код, сдвинутый на один разряд. Сдвигатели различают по направлению (вправо – влево) и по типу сдвига – обыкновенный (логический), арифметический, циклический и другие типы сдвигов. В сложных быстродействующих АЛУ встречаются сдвигатели на произвольное количество сдвигаемых за один такт разрядов, например, от 1 до 16.

Сдвигатели принимают на вход многоразрядный двоичный код и выдают на выходе тот же код, сдвинутый на один разряд. Сдвигатели различают по направлению (вправо – влево) и по типу сдвига – обыкновенный (логический), арифметический, циклический и другие типы сдвигов. В сложных быстродействующих АЛУ встречаются сдвигатели на произвольное количество сдвигаемых за один такт разрядов, например, от 1 до 16.

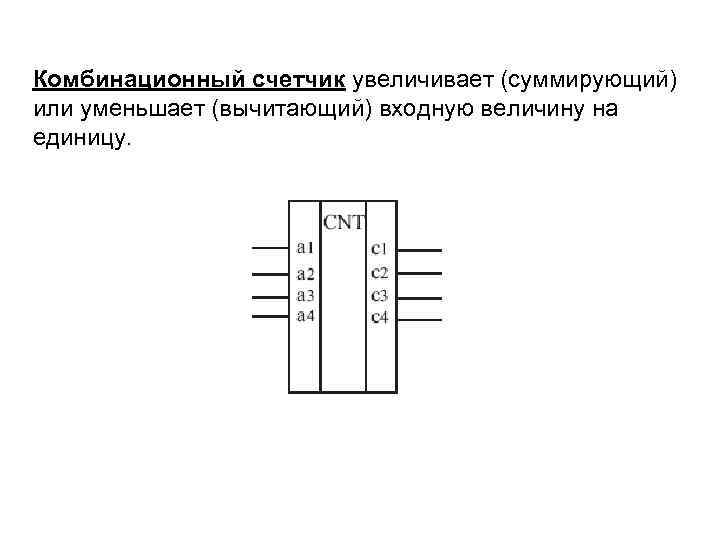

Комбинационный счетчик увеличивает (суммирующий) или уменьшает (вычитающий) входную величину на единицу.

Комбинационный счетчик увеличивает (суммирующий) или уменьшает (вычитающий) входную величину на единицу.

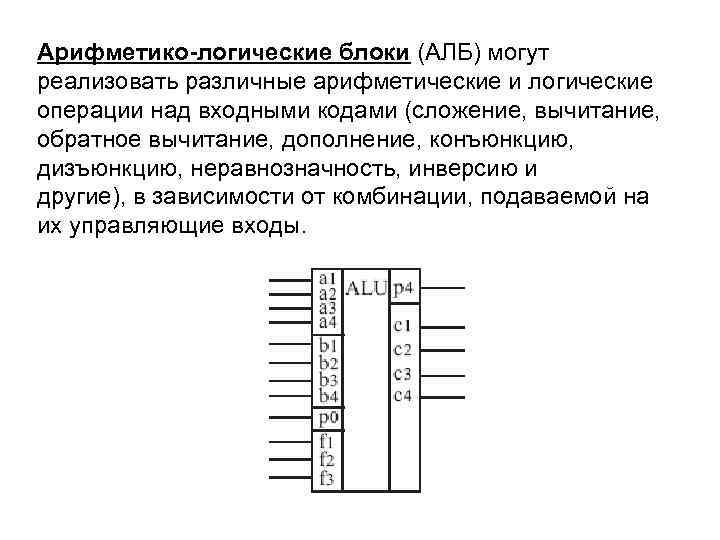

Арифметико-логические блоки (АЛБ) могут реализовать различные арифметические и логические операции над входными кодами (сложение, вычитание, обратное вычитание, дополнение, конъюнкцию, дизъюнкцию, неравнозначность, инверсию и другие), в зависимости от комбинации, подаваемой на их управляющие входы.

Арифметико-логические блоки (АЛБ) могут реализовать различные арифметические и логические операции над входными кодами (сложение, вычитание, обратное вычитание, дополнение, конъюнкцию, дизъюнкцию, неравнозначность, инверсию и другие), в зависимости от комбинации, подаваемой на их управляющие входы.

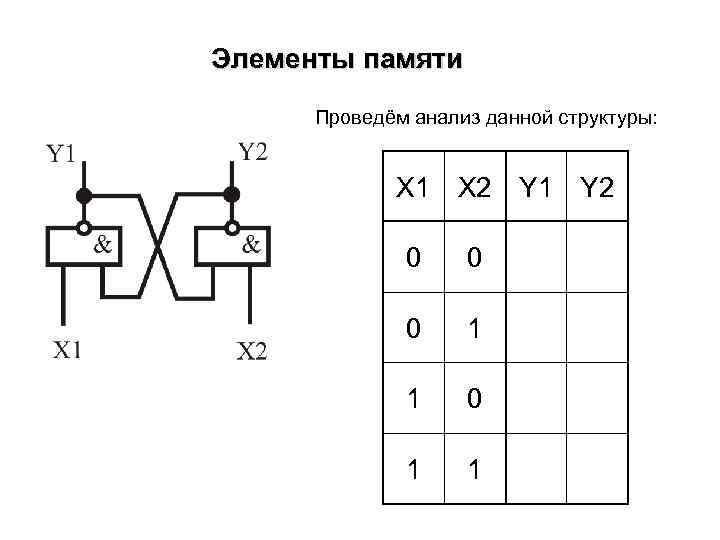

Элементы памяти Проведём анализ данной структуры: X 1 X 2 Y 1 Y 2 0 0 0 1 1

Элементы памяти Проведём анализ данной структуры: X 1 X 2 Y 1 Y 2 0 0 0 1 1

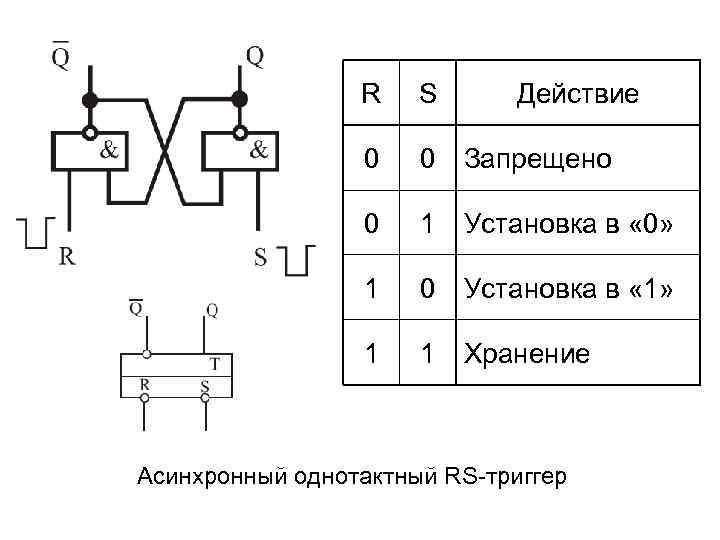

R S Действие 0 0 Запрещено 0 1 Установка в « 0» 1 0 Установка в « 1» 1 1 Хранение Асинхронный однотактный RS-триггер

R S Действие 0 0 Запрещено 0 1 Установка в « 0» 1 0 Установка в « 1» 1 1 Хранение Асинхронный однотактный RS-триггер

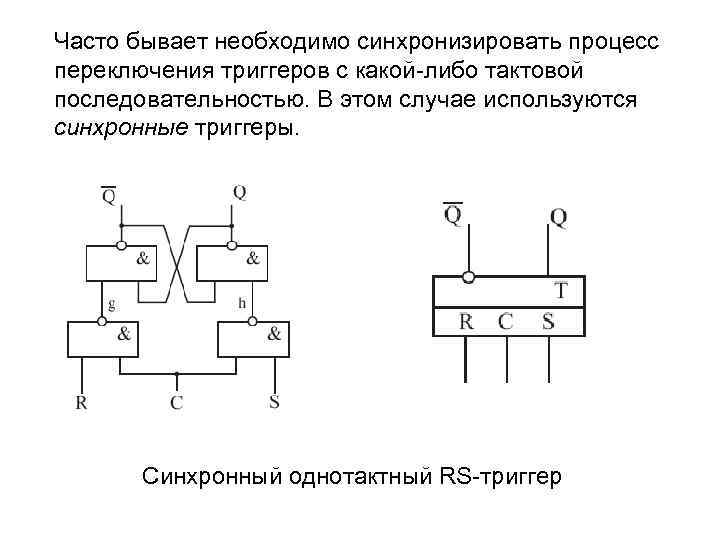

Часто бывает необходимо синхронизировать процесс переключения триггеров с какой-либо тактовой последовательностью. В этом случае используются синхронные триггеры. Синхронный однотактный RS-триггер

Часто бывает необходимо синхронизировать процесс переключения триггеров с какой-либо тактовой последовательностью. В этом случае используются синхронные триггеры. Синхронный однотактный RS-триггер

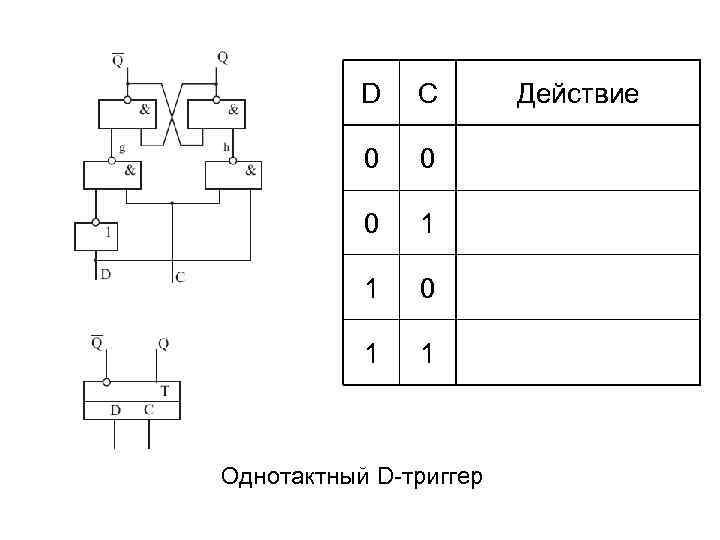

D C 0 0 0 1 1 Однотактный D-триггер Действие

D C 0 0 0 1 1 Однотактный D-триггер Действие

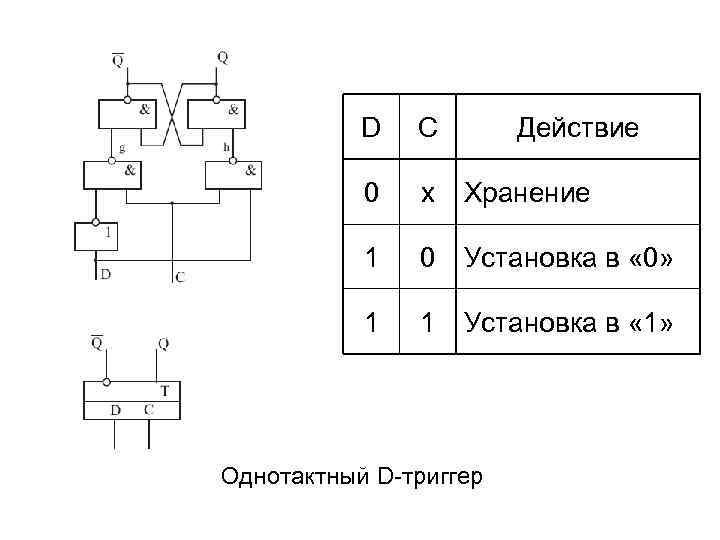

D C Действие 0 x 1 0 Установка в « 0» 1 1 Установка в « 1» Хранение Однотактный D-триггер

D C Действие 0 x 1 0 Установка в « 0» 1 1 Установка в « 1» Хранение Однотактный D-триггер

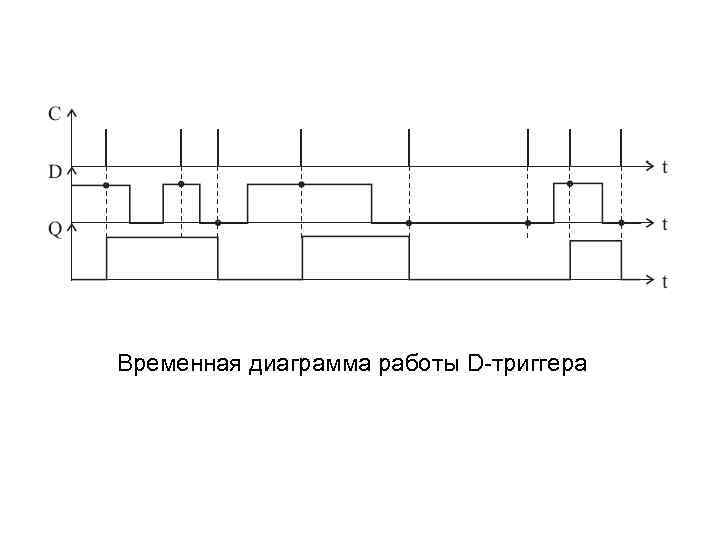

Временная диаграмма работы D-триггера

Временная диаграмма работы D-триггера

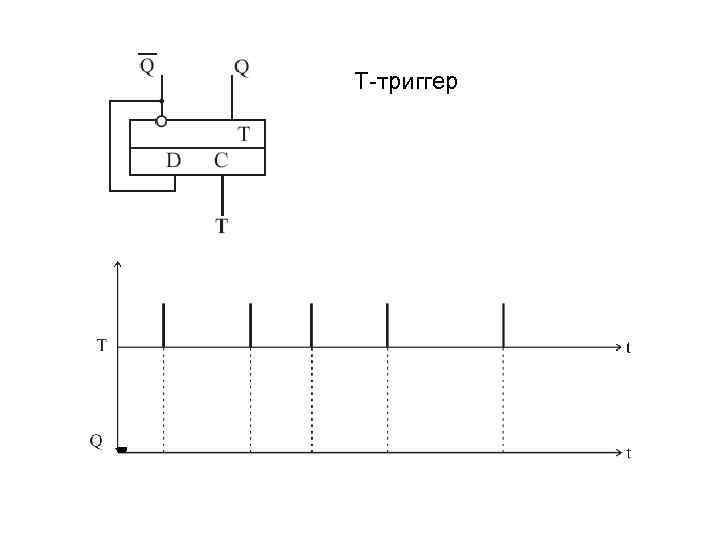

Т-триггер

Т-триггер

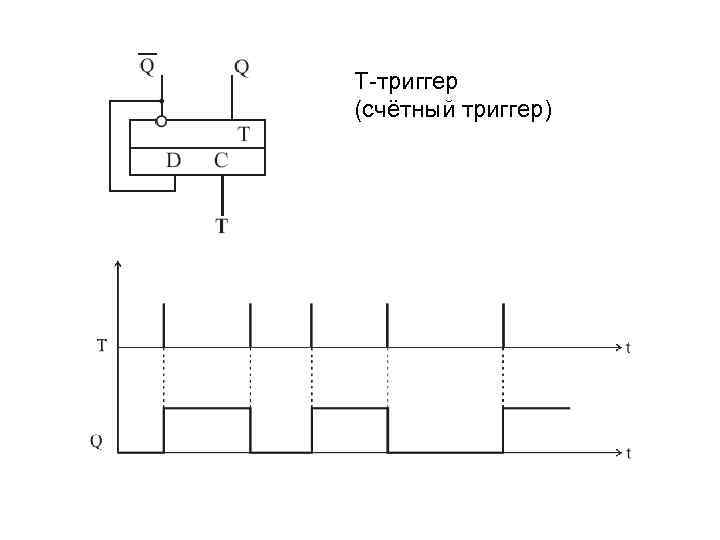

Т-триггер (счётный триггер)

Т-триггер (счётный триггер)

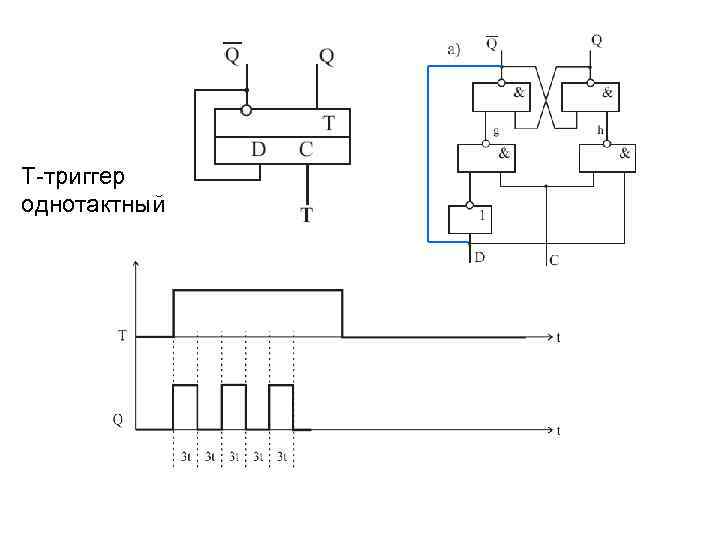

Т-триггер однотактный

Т-триггер однотактный

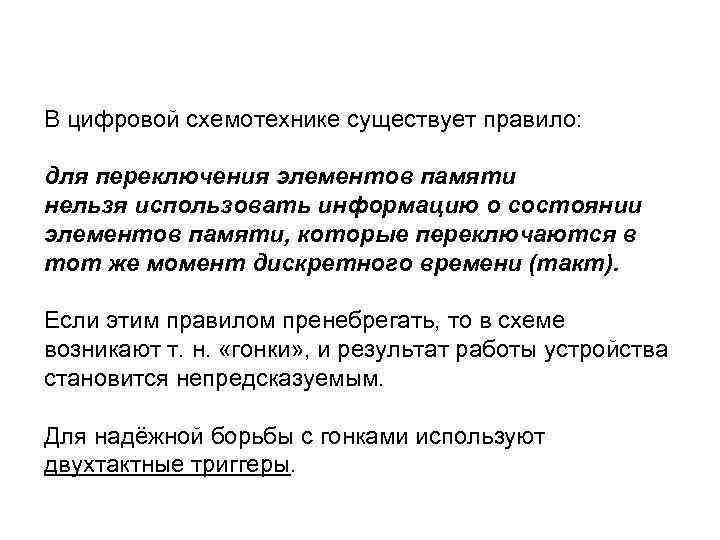

В цифровой схемотехнике существует правило: для переключения элементов памяти нельзя использовать информацию о состоянии элементов памяти, которые переключаются в тот же момент дискретного времени (такт). Если этим правилом пренебрегать, то в схеме возникают т. н. «гонки» , и результат работы устройства становится непредсказуемым. Для надёжной борьбы с гонками используют двухтактные триггеры.

В цифровой схемотехнике существует правило: для переключения элементов памяти нельзя использовать информацию о состоянии элементов памяти, которые переключаются в тот же момент дискретного времени (такт). Если этим правилом пренебрегать, то в схеме возникают т. н. «гонки» , и результат работы устройства становится непредсказуемым. Для надёжной борьбы с гонками используют двухтактные триггеры.

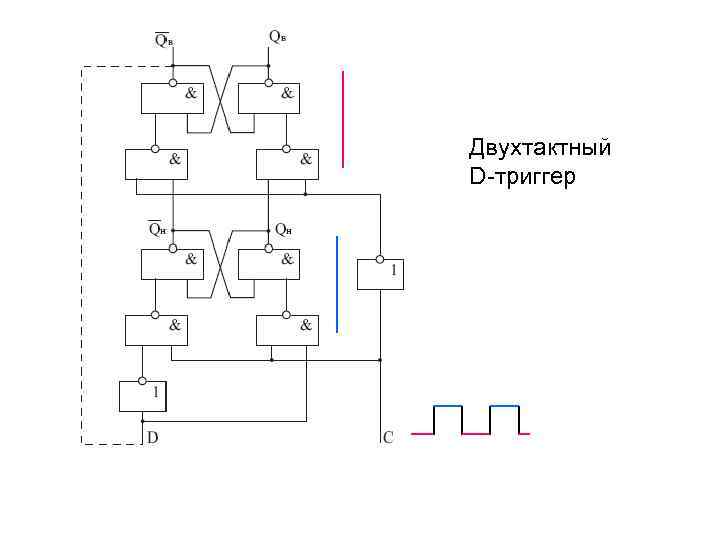

Двухтактный D-триггер

Двухтактный D-триггер

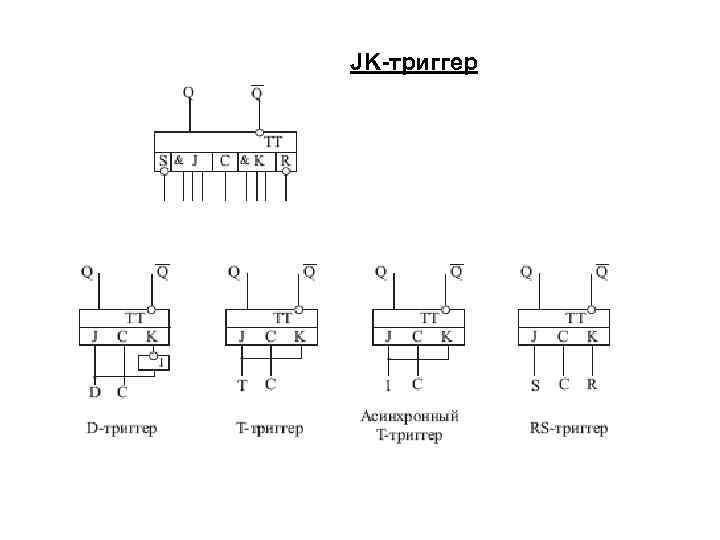

JK-триггер

JK-триггер

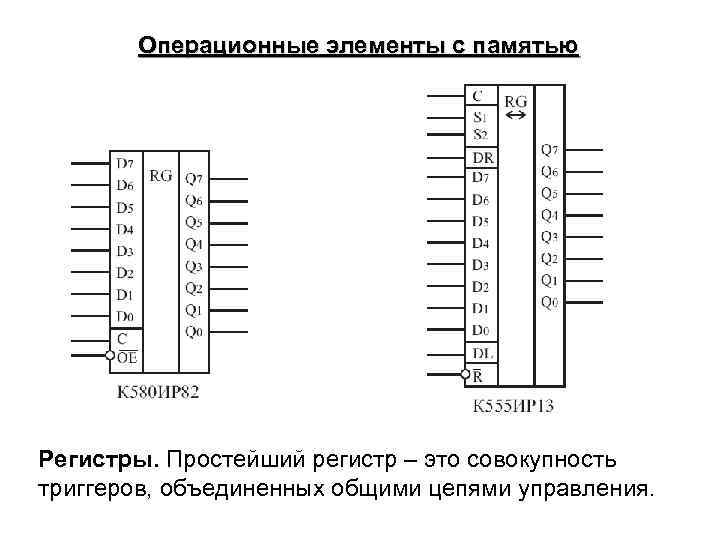

Операционные элементы с памятью Регистры. Простейший регистр – это совокупность триггеров, объединенных общими цепями управления.

Операционные элементы с памятью Регистры. Простейший регистр – это совокупность триггеров, объединенных общими цепями управления.

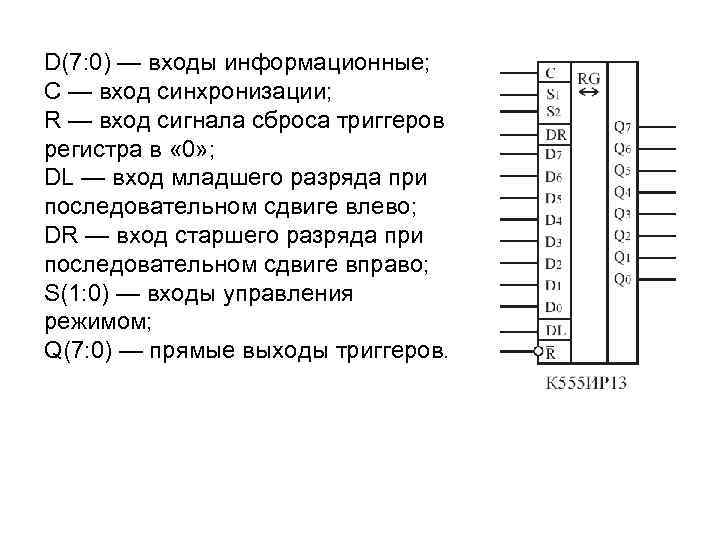

D(7: 0) — входы информационные; C — вход синхронизации; R — вход сигнала сброса триггеров регистра в « 0» ; DL — вход младшего разряда при последовательном сдвиге влево; DR — вход старшего разряда при последовательном сдвиге вправо; S(1: 0) — входы управления режимом; Q(7: 0) — прямые выходы триггеров.

D(7: 0) — входы информационные; C — вход синхронизации; R — вход сигнала сброса триггеров регистра в « 0» ; DL — вход младшего разряда при последовательном сдвиге влево; DR — вход старшего разряда при последовательном сдвиге вправо; S(1: 0) — входы управления режимом; Q(7: 0) — прямые выходы триггеров.

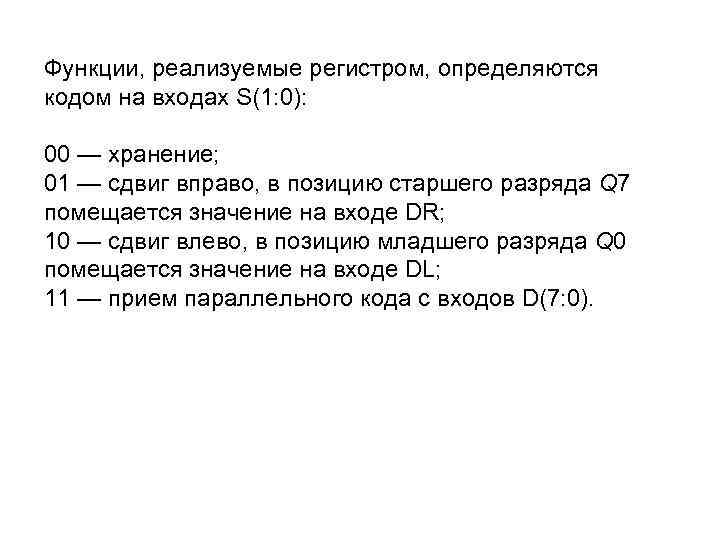

Функции, реализуемые регистром, определяются кодом на входах S(1: 0): 00 — хранение; 01 — сдвиг вправо, в позицию старшего разряда Q 7 помещается значение на входе DR; 10 — сдвиг влево, в позицию младшего разряда Q 0 помещается значение на входе DL; 11 — прием параллельного кода с входов D(7: 0).

Функции, реализуемые регистром, определяются кодом на входах S(1: 0): 00 — хранение; 01 — сдвиг вправо, в позицию старшего разряда Q 7 помещается значение на входе DR; 10 — сдвиг влево, в позицию младшего разряда Q 0 помещается значение на входе DL; 11 — прием параллельного кода с входов D(7: 0).

Фрагмент сдвигающего регистра

Фрагмент сдвигающего регистра

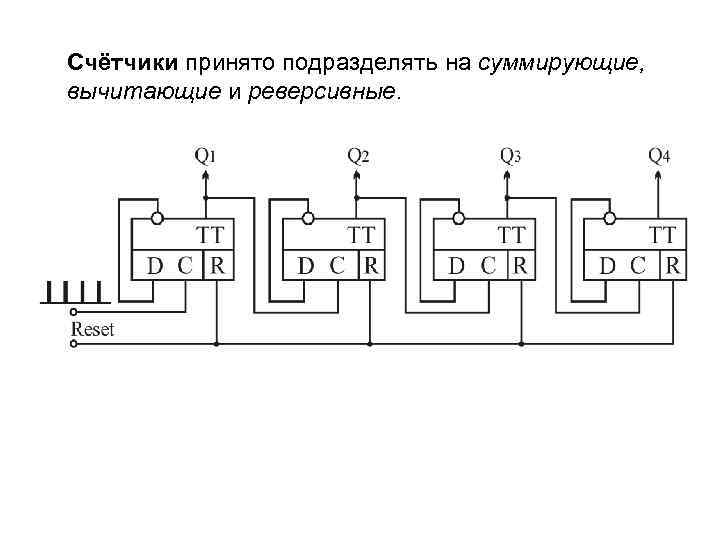

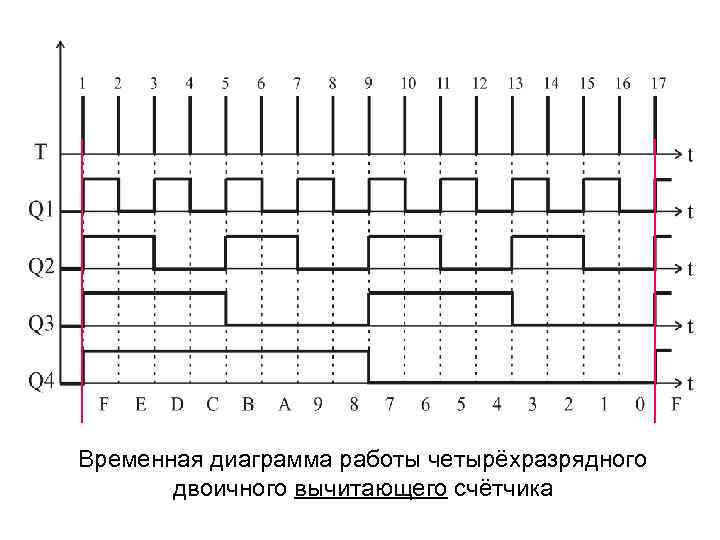

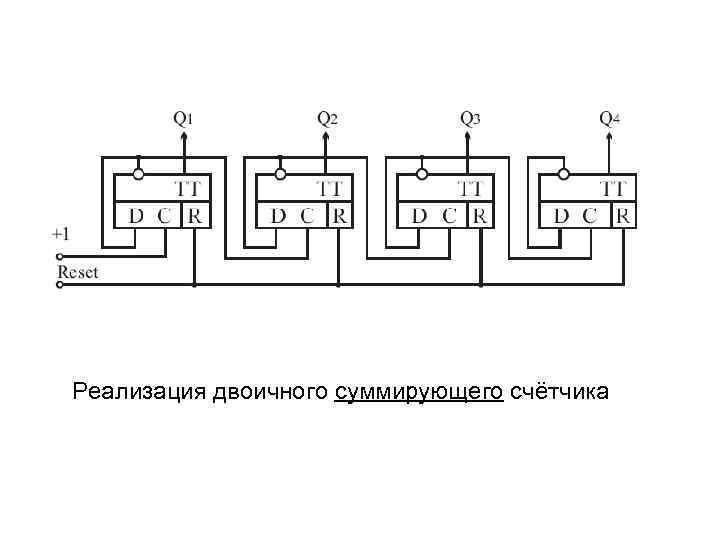

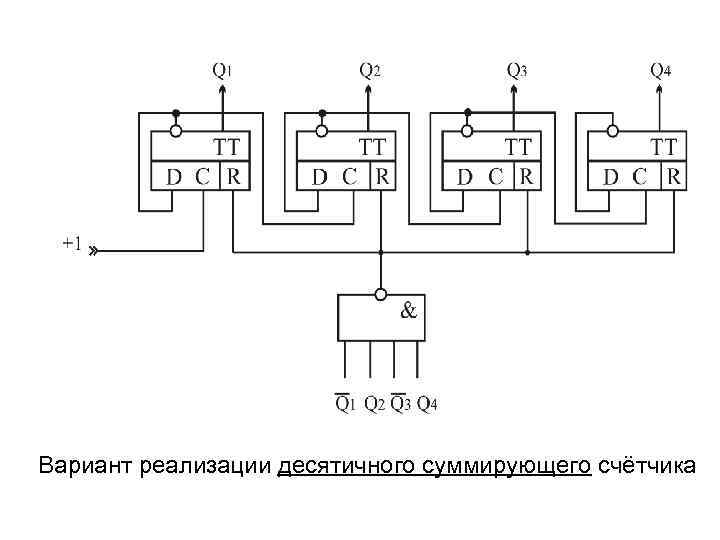

Счётчики принято подразделять на суммирующие, вычитающие и реверсивные.

Счётчики принято подразделять на суммирующие, вычитающие и реверсивные.

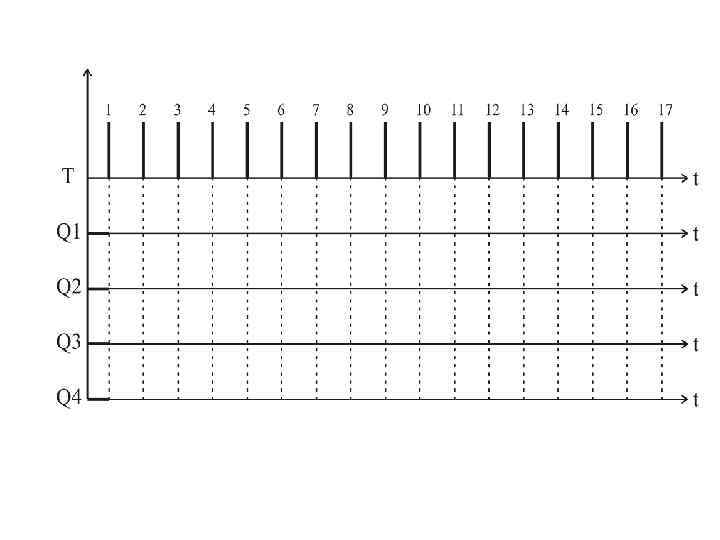

Временная диаграмма работы четырёхразрядного двоичного вычитающего счётчика

Временная диаграмма работы четырёхразрядного двоичного вычитающего счётчика

Реализация двоичного суммирующего счётчика

Реализация двоичного суммирующего счётчика

Вариант реализации десятичного суммирующего счётчика

Вариант реализации десятичного суммирующего счётчика