6dfbe4bd778b88890fb513ee6d9b56fe.ppt

- Количество слайдов: 17

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Proposal for a New Binary Architecture for STAR Microvertex Upgrade Wojciech Dulinski, IPHC, Strasbourg, France Outline · Short history of beginnings: NSS-2004, Roma (W. Dulinski) · Review of existing results: work of M. Szelezniak (10 th ESSD, Wildbad Kreuth, 2005) and A. Dorokhov (FEE-2006, Perugia) · Binary readout scheme, based on FAPS pixel ·Conclusions 1

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Proposal for a New Binary Architecture for STAR Microvertex Upgrade Wojciech Dulinski, IPHC, Strasbourg, France Outline · Short history of beginnings: NSS-2004, Roma (W. Dulinski) · Review of existing results: work of M. Szelezniak (10 th ESSD, Wildbad Kreuth, 2005) and A. Dorokhov (FEE-2006, Perugia) · Binary readout scheme, based on FAPS pixel ·Conclusions 1

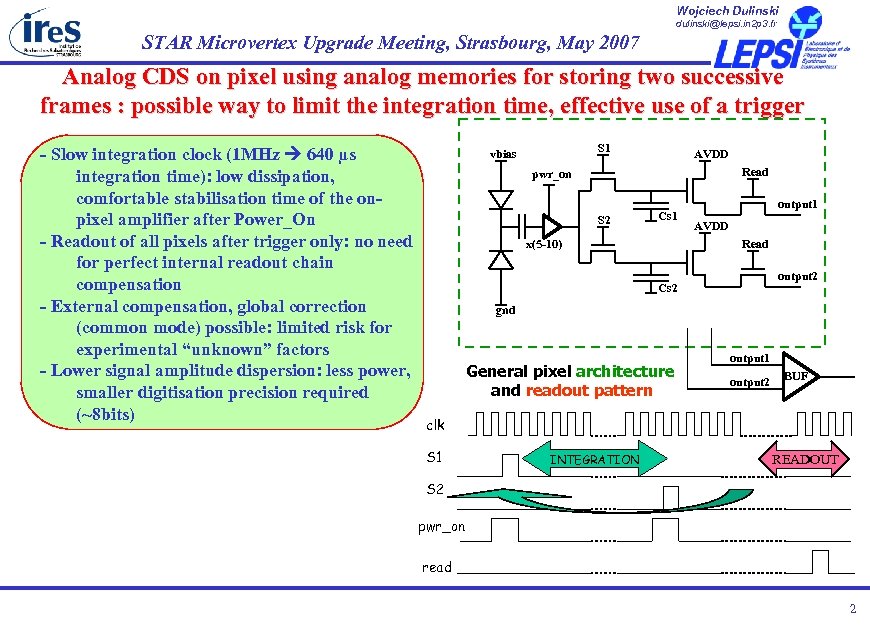

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Analog CDS on pixel using analog memories for storing two successive frames : possible way to limit the integration time, effective use of a trigger - Slow integration clock (1 MHz 640 µs integration time): low dissipation, comfortable stabilisation time of the onpixel amplifier after Power_On - Readout of all pixels after trigger only: no need for perfect internal readout chain compensation - External compensation, global correction (common mode) possible: limited risk for experimental “unknown” factors - Lower signal amplitude dispersion: less power, smaller digitisation precision required (~8 bits) S 1 vbias AVDD Read pwr_on S 2 Cs 1 x(5 -10) output 1 AVDD Read output 2 Cs 2 gnd General pixel architecture and readout pattern output 1 output 2 BUF clk S 1 INTEGRATION READOUT S 2 pwr_on read 2

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Analog CDS on pixel using analog memories for storing two successive frames : possible way to limit the integration time, effective use of a trigger - Slow integration clock (1 MHz 640 µs integration time): low dissipation, comfortable stabilisation time of the onpixel amplifier after Power_On - Readout of all pixels after trigger only: no need for perfect internal readout chain compensation - External compensation, global correction (common mode) possible: limited risk for experimental “unknown” factors - Lower signal amplitude dispersion: less power, smaller digitisation precision required (~8 bits) S 1 vbias AVDD Read pwr_on S 2 Cs 1 x(5 -10) output 1 AVDD Read output 2 Cs 2 gnd General pixel architecture and readout pattern output 1 output 2 BUF clk S 1 INTEGRATION READOUT S 2 pwr_on read 2

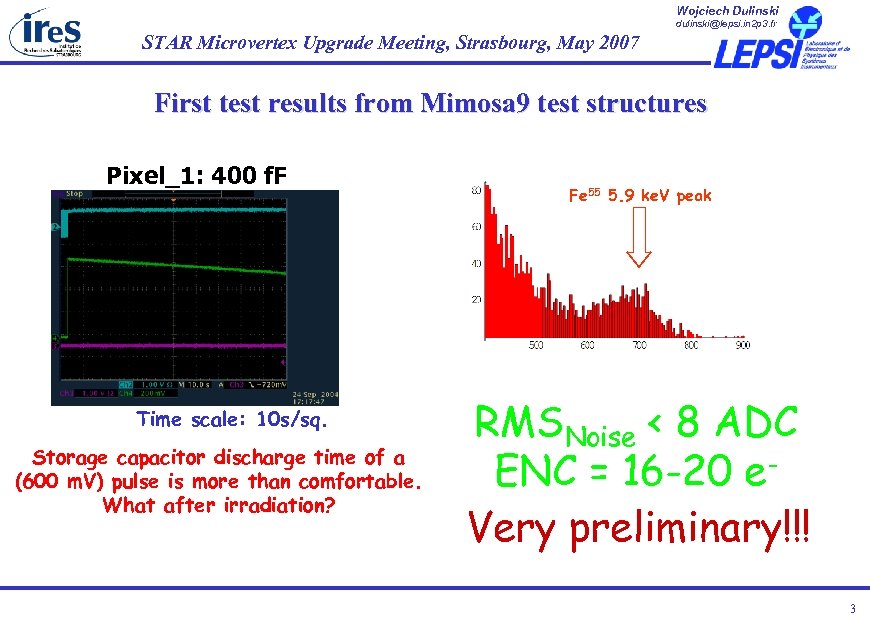

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 First test results from Mimosa 9 test structures Pixel_1: 400 f. F Time scale: 10 s/sq. Storage capacitor discharge time of a (600 m. V) pulse is more than comfortable. What after irradiation? Fe 55 5. 9 ke. V peak RMSNoise < 8 ADC ENC = 16 -20 e. Very preliminary!!! 3

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 First test results from Mimosa 9 test structures Pixel_1: 400 f. F Time scale: 10 s/sq. Storage capacitor discharge time of a (600 m. V) pulse is more than comfortable. What after irradiation? Fe 55 5. 9 ke. V peak RMSNoise < 8 ADC ENC = 16 -20 e. Very preliminary!!! 3

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Conclusions 2: STAR application - Increase of a dark current after irradiation is THE critical factor, in order to run detector at room temperature (not well controlled) AND using several milliseconds integration time - Each process and each layout should be carefully studied for this effect AND compared to STAR radiation environment - Going to shorter integration time (order of magnitude) and systematic research on the more radiation-tollerant layout techniques is strongly recommended, in order to have necessary safety factor for the experiment “unforeseen” - CDS on pixel using analog memory for two frames storing scheme seems promising, but still requires deeper understanding (new small prototypes) 4

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Conclusions 2: STAR application - Increase of a dark current after irradiation is THE critical factor, in order to run detector at room temperature (not well controlled) AND using several milliseconds integration time - Each process and each layout should be carefully studied for this effect AND compared to STAR radiation environment - Going to shorter integration time (order of magnitude) and systematic research on the more radiation-tollerant layout techniques is strongly recommended, in order to have necessary safety factor for the experiment “unforeseen” - CDS on pixel using analog memory for two frames storing scheme seems promising, but still requires deeper understanding (new small prototypes) 4

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 DC coupled and AC coupled on-pixel amplifiers Gain DC coupled AC coupled amp: • Separation from power supply of the sensing node – Increase of the voltage increase of the depleted region no change on the operating point • Separation from influence of the leakage current – Increase of the leakage current after irradiation change of the bias on the sensing node no change on the OP Compact implementation Gain AC coupled 5

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 DC coupled and AC coupled on-pixel amplifiers Gain DC coupled AC coupled amp: • Separation from power supply of the sensing node – Increase of the voltage increase of the depleted region no change on the operating point • Separation from influence of the leakage current – Increase of the leakage current after irradiation change of the bias on the sensing node no change on the OP Compact implementation Gain AC coupled 5

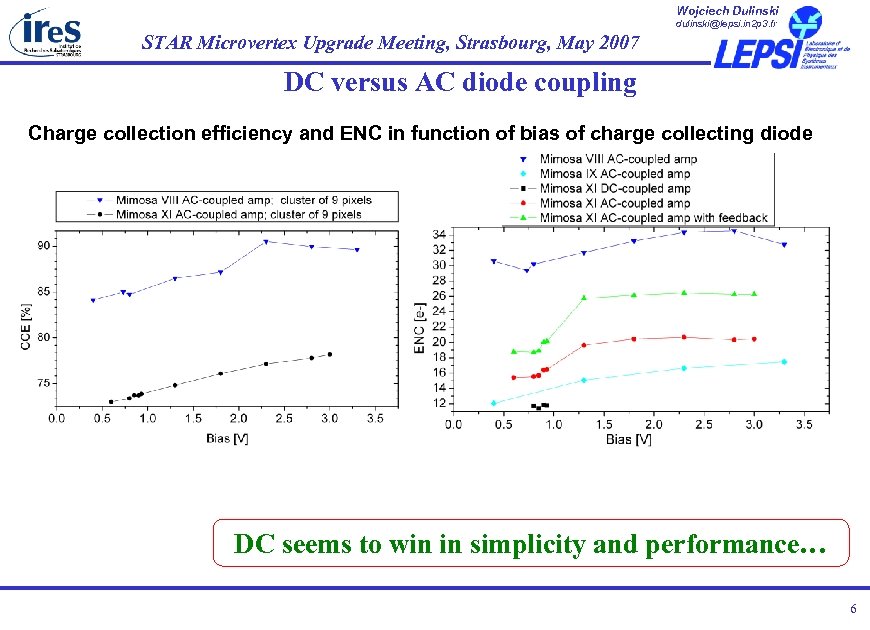

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 DC versus AC diode coupling Charge collection efficiency and ENC in function of bias of charge collecting diode DC seems to win in simplicity and performance… 6

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 DC versus AC diode coupling Charge collection efficiency and ENC in function of bias of charge collecting diode DC seems to win in simplicity and performance… 6

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Amplifiers for MAPS Amplification is needed to decrease noise contribution from switching networks, like clamping or sampling. • PMOS transistors not allowed inside pixel -> signal decrease due to parasitic NWELL • but using PMOS transistor as a load would be the preferred choice to increase in-pixel amplifier gain… load reset bias in gate bias in signal current out vb out cascode in 7

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Amplifiers for MAPS Amplification is needed to decrease noise contribution from switching networks, like clamping or sampling. • PMOS transistors not allowed inside pixel -> signal decrease due to parasitic NWELL • but using PMOS transistor as a load would be the preferred choice to increase in-pixel amplifier gain… load reset bias in gate bias in signal current out vb out cascode in 7

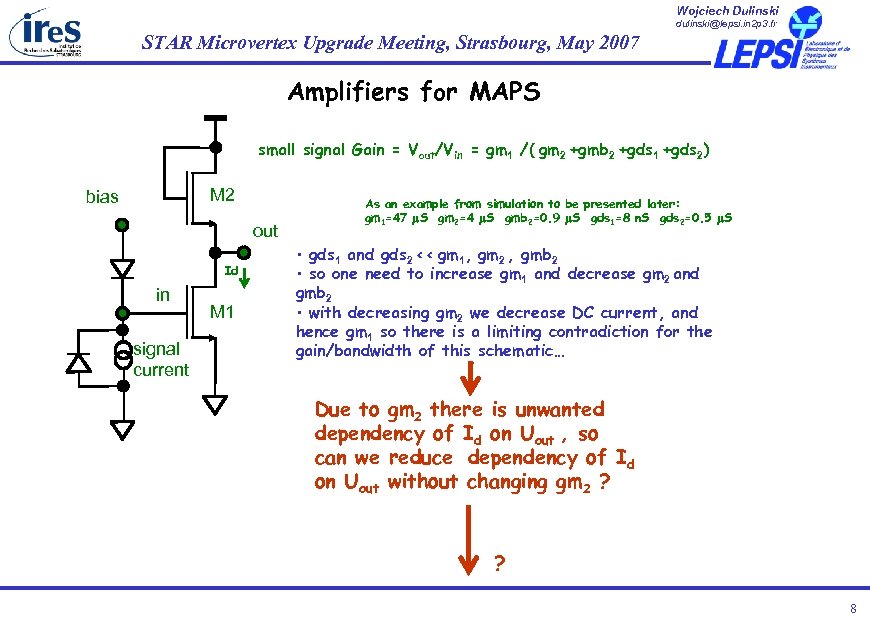

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Amplifiers for MAPS small signal Gain = Vout/Vin = gm 1 /( gm 2 +gmb 2 +gds 1 +gds 2) M 2 bias out Id in signal current M 1 As an example from simulation to be presented later: gm 1=47 m. S gm 2=4 m. S gmb 2=0. 9 m. S gds 1=8 n. S gds 2=0. 5 m. S • gds 1 and gds 2 << gm 1, gm 2 , gmb 2 • so one need to increase gm 1 and decrease gm 2 and gmb 2 • with decreasing gm 2 we decrease DC current, and hence gm 1 so there is a limiting contradiction for the gain/bandwidth of this schematic… Due to gm 2 there is unwanted dependency of Id on Uout , so can we reduce dependency of Id on Uout without changing gm 2 ? ? 8

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Amplifiers for MAPS small signal Gain = Vout/Vin = gm 1 /( gm 2 +gmb 2 +gds 1 +gds 2) M 2 bias out Id in signal current M 1 As an example from simulation to be presented later: gm 1=47 m. S gm 2=4 m. S gmb 2=0. 9 m. S gds 1=8 n. S gds 2=0. 5 m. S • gds 1 and gds 2 << gm 1, gm 2 , gmb 2 • so one need to increase gm 1 and decrease gm 2 and gmb 2 • with decreasing gm 2 we decrease DC current, and hence gm 1 so there is a limiting contradiction for the gain/bandwidth of this schematic… Due to gm 2 there is unwanted dependency of Id on Uout , so can we reduce dependency of Id on Uout without changing gm 2 ? ? 8

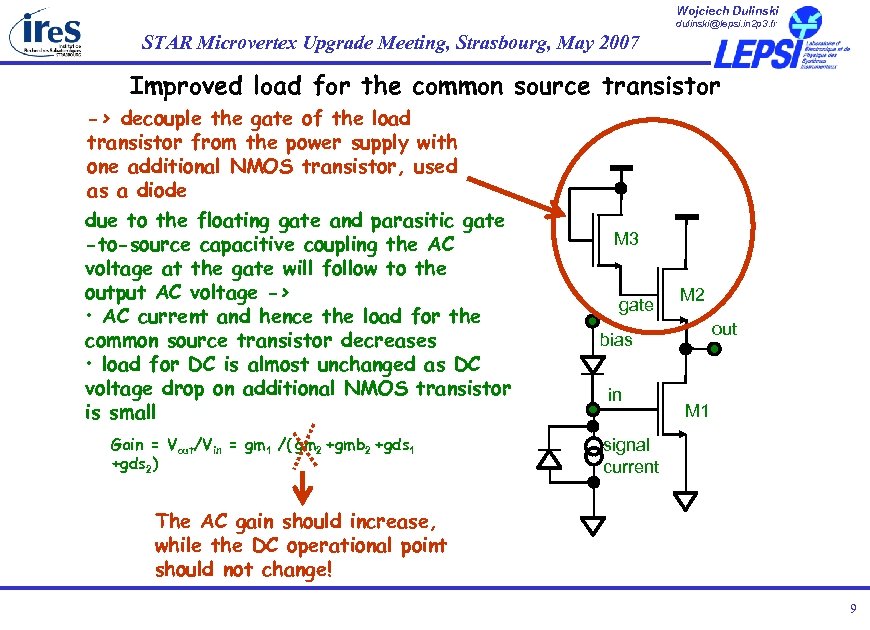

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Improved load for the common source transistor -> decouple the gate of the load transistor from the power supply with one additional NMOS transistor, used as a diode due to the floating gate and parasitic gate -to-source capacitive coupling the AC voltage at the gate will follow to the output AC voltage -> • AC current and hence the load for the common source transistor decreases • load for DC is almost unchanged as DC voltage drop on additional NMOS transistor is small Gain = Vout/Vin = gm 1 /( gm 2 +gmb 2 +gds 1 +gds 2) M 3 gate M 2 out bias in M 1 signal current The AC gain should increase, while the DC operational point should not change! 9

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Improved load for the common source transistor -> decouple the gate of the load transistor from the power supply with one additional NMOS transistor, used as a diode due to the floating gate and parasitic gate -to-source capacitive coupling the AC voltage at the gate will follow to the output AC voltage -> • AC current and hence the load for the common source transistor decreases • load for DC is almost unchanged as DC voltage drop on additional NMOS transistor is small Gain = Vout/Vin = gm 1 /( gm 2 +gmb 2 +gds 1 +gds 2) M 3 gate M 2 out bias in M 1 signal current The AC gain should increase, while the DC operational point should not change! 9

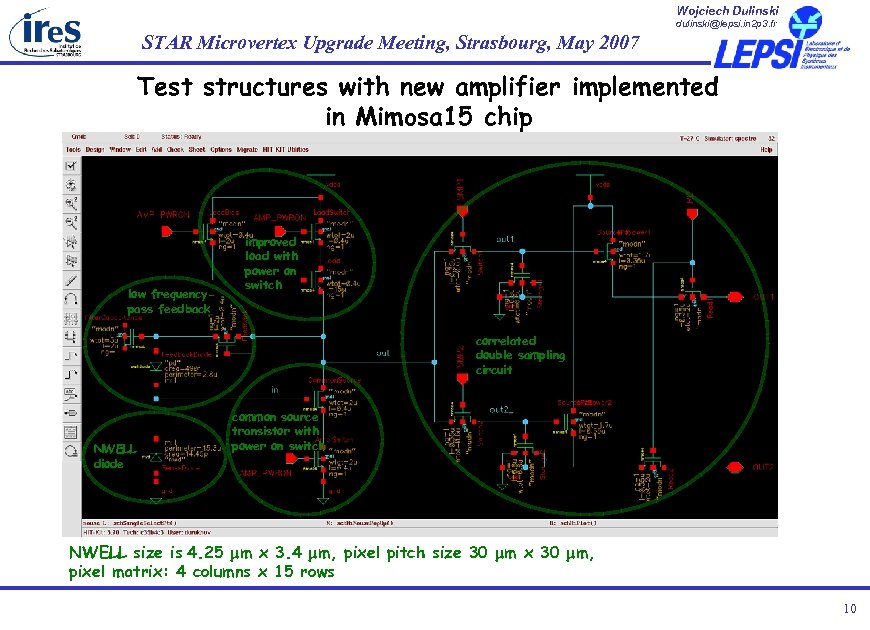

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Test structures with new amplifier implemented in Mimosa 15 chip low frequencypass feedback improved load with power on switch correlated double sampling circuit NWELL diode common source transistor with power on switch NWELL size is 4. 25 mm x 3. 4 mm, pixel pitch size 30 mm x 30 mm, pixel matrix: 4 columns x 15 rows 10

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Test structures with new amplifier implemented in Mimosa 15 chip low frequencypass feedback improved load with power on switch correlated double sampling circuit NWELL diode common source transistor with power on switch NWELL size is 4. 25 mm x 3. 4 mm, pixel pitch size 30 mm x 30 mm, pixel matrix: 4 columns x 15 rows 10

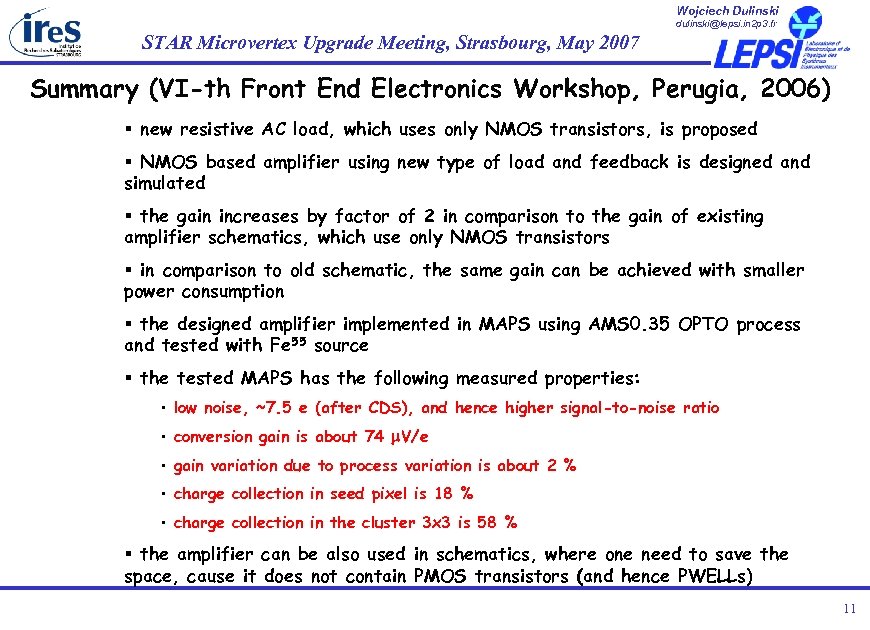

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Summary (VI-th Front End Electronics Workshop, Perugia, 2006) § new resistive AC load, which uses only NMOS transistors, is proposed § NMOS based amplifier using new type of load and feedback is designed and simulated § the gain increases by factor of 2 in comparison to the gain of existing amplifier schematics, which use only NMOS transistors § in comparison to old schematic, the same gain can be achieved with smaller power consumption § the designed amplifier implemented in MAPS using AMS 0. 35 OPTO process and tested with Fe 55 source § the tested MAPS has the following measured properties: • low noise, ~7. 5 e (after CDS), and hence higher signal-to-noise ratio • conversion gain is about 74 m. V/e • gain variation due to process variation is about 2 % • charge collection in seed pixel is 18 % • charge collection in the cluster 3 x 3 is 58 % § the amplifier can be also used in schematics, where one need to save the space, cause it does not contain PMOS transistors (and hence PWELLs) 11

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Summary (VI-th Front End Electronics Workshop, Perugia, 2006) § new resistive AC load, which uses only NMOS transistors, is proposed § NMOS based amplifier using new type of load and feedback is designed and simulated § the gain increases by factor of 2 in comparison to the gain of existing amplifier schematics, which use only NMOS transistors § in comparison to old schematic, the same gain can be achieved with smaller power consumption § the designed amplifier implemented in MAPS using AMS 0. 35 OPTO process and tested with Fe 55 source § the tested MAPS has the following measured properties: • low noise, ~7. 5 e (after CDS), and hence higher signal-to-noise ratio • conversion gain is about 74 m. V/e • gain variation due to process variation is about 2 % • charge collection in seed pixel is 18 % • charge collection in the cluster 3 x 3 is 58 % § the amplifier can be also used in schematics, where one need to save the space, cause it does not contain PMOS transistors (and hence PWELLs) 11

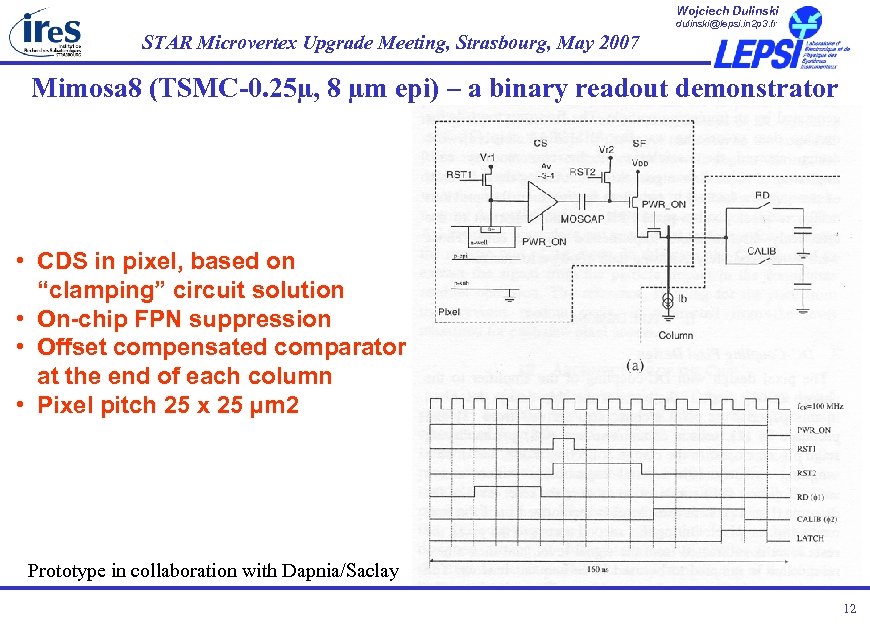

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Mimosa 8 (TSMC-0. 25µ, 8 µm epi) – a binary readout demonstrator • CDS in pixel, based on “clamping” circuit solution • On-chip FPN suppression • Offset compensated comparator at the end of each column • Pixel pitch 25 x 25 µm 2 Prototype in collaboration with Dapnia/Saclay 12

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Mimosa 8 (TSMC-0. 25µ, 8 µm epi) – a binary readout demonstrator • CDS in pixel, based on “clamping” circuit solution • On-chip FPN suppression • Offset compensated comparator at the end of each column • Pixel pitch 25 x 25 µm 2 Prototype in collaboration with Dapnia/Saclay 12

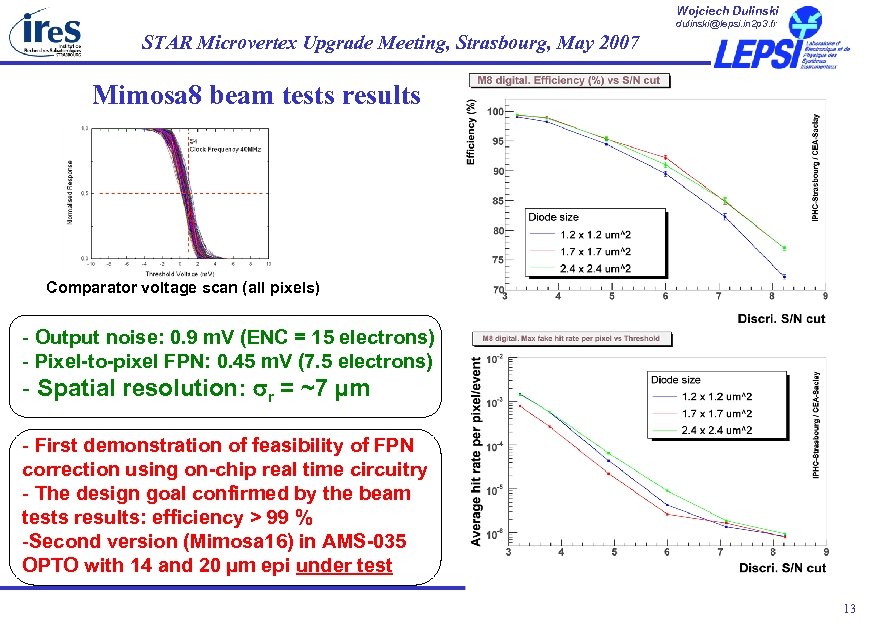

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Mimosa 8 beam tests results Comparator voltage scan (all pixels) - Output noise: 0. 9 m. V (ENC = 15 electrons) - Pixel-to-pixel FPN: 0. 45 m. V (7. 5 electrons) - Spatial resolution: sr = ~7 µm - First demonstration of feasibility of FPN correction using on-chip real time circuitry - The design goal confirmed by the beam tests results: efficiency > 99 % -Second version (Mimosa 16) in AMS-035 OPTO with 14 and 20 µm epi under test 13

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Mimosa 8 beam tests results Comparator voltage scan (all pixels) - Output noise: 0. 9 m. V (ENC = 15 electrons) - Pixel-to-pixel FPN: 0. 45 m. V (7. 5 electrons) - Spatial resolution: sr = ~7 µm - First demonstration of feasibility of FPN correction using on-chip real time circuitry - The design goal confirmed by the beam tests results: efficiency > 99 % -Second version (Mimosa 16) in AMS-035 OPTO with 14 and 20 µm epi under test 13

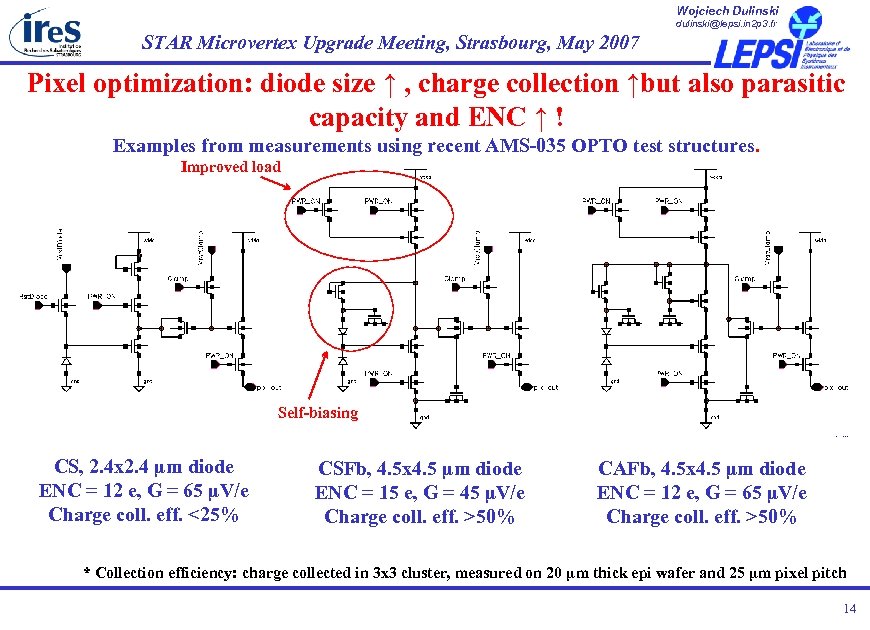

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Pixel optimization: diode size ↑ , charge collection ↑but also parasitic capacity and ENC ↑ ! Examples from measurements using recent AMS-035 OPTO test structures. Improved load Self-biasing CS, 2. 4 x 2. 4 µm diode ENC = 12 e, G = 65 µV/e Charge coll. eff. <25% CSFb, 4. 5 x 4. 5 µm diode ENC = 15 e, G = 45 µV/e Charge coll. eff. >50% CAFb, 4. 5 x 4. 5 µm diode ENC = 12 e, G = 65 µV/e Charge coll. eff. >50% * Collection efficiency: charge collected in 3 x 3 cluster, measured on 20 µm thick epi wafer and 25 µm pixel pitch 14

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Pixel optimization: diode size ↑ , charge collection ↑but also parasitic capacity and ENC ↑ ! Examples from measurements using recent AMS-035 OPTO test structures. Improved load Self-biasing CS, 2. 4 x 2. 4 µm diode ENC = 12 e, G = 65 µV/e Charge coll. eff. <25% CSFb, 4. 5 x 4. 5 µm diode ENC = 15 e, G = 45 µV/e Charge coll. eff. >50% CAFb, 4. 5 x 4. 5 µm diode ENC = 12 e, G = 65 µV/e Charge coll. eff. >50% * Collection efficiency: charge collected in 3 x 3 cluster, measured on 20 µm thick epi wafer and 25 µm pixel pitch 14

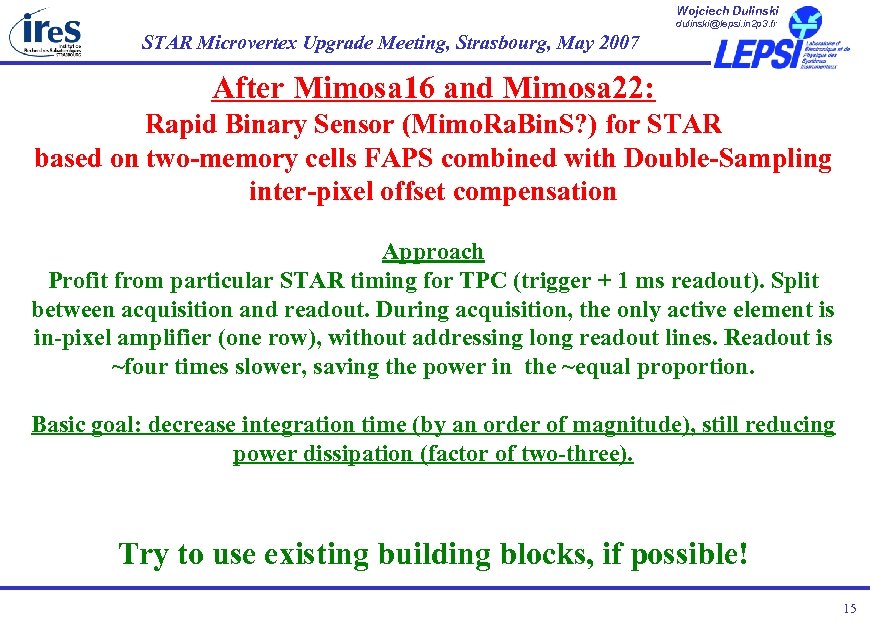

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 After Mimosa 16 and Mimosa 22: Rapid Binary Sensor (Mimo. Ra. Bin. S? ) for STAR based on two-memory cells FAPS combined with Double-Sampling inter-pixel offset compensation Approach Profit from particular STAR timing for TPC (trigger + 1 ms readout). Split between acquisition and readout. During acquisition, the only active element is in-pixel amplifier (one row), without addressing long readout lines. Readout is ~four times slower, saving the power in the ~equal proportion. Basic goal: decrease integration time (by an order of magnitude), still reducing power dissipation (factor of two-three). Try to use existing building blocks, if possible! 15

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 After Mimosa 16 and Mimosa 22: Rapid Binary Sensor (Mimo. Ra. Bin. S? ) for STAR based on two-memory cells FAPS combined with Double-Sampling inter-pixel offset compensation Approach Profit from particular STAR timing for TPC (trigger + 1 ms readout). Split between acquisition and readout. During acquisition, the only active element is in-pixel amplifier (one row), without addressing long readout lines. Readout is ~four times slower, saving the power in the ~equal proportion. Basic goal: decrease integration time (by an order of magnitude), still reducing power dissipation (factor of two-three). Try to use existing building blocks, if possible! 15

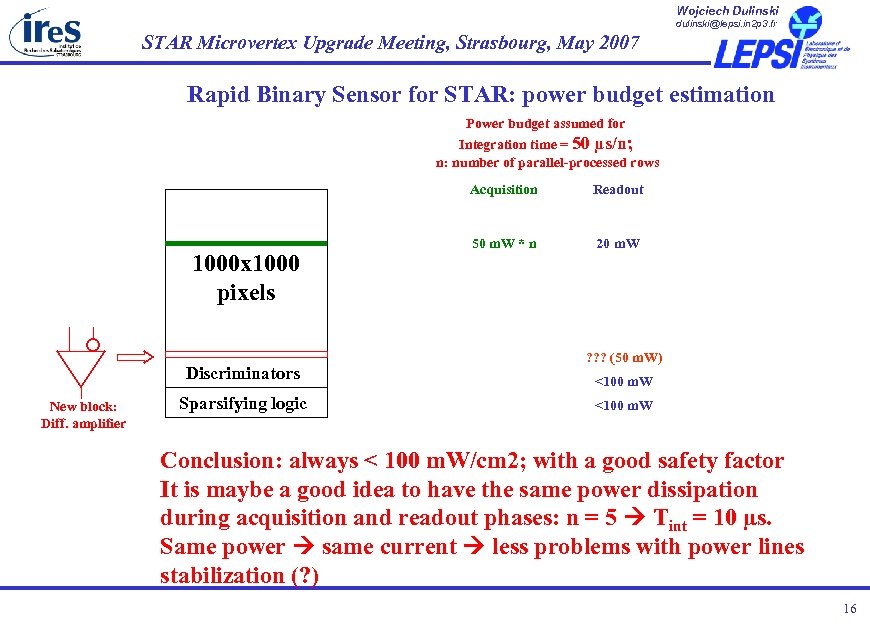

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Rapid Binary Sensor for STAR: power budget estimation Power budget assumed for Integration time = 50 µs/n; n: number of parallel-processed rows Acquisition 1000 x 1000 pixels Discriminators New block: Diff. amplifier Sparsifying logic Readout 50 m. W * n 20 m. W ? ? ? (50 m. W) <100 m. W Conclusion: always < 100 m. W/cm 2; with a good safety factor It is maybe a good idea to have the same power dissipation during acquisition and readout phases: n = 5 Tint = 10 µs. Same power same current less problems with power lines stabilization (? ) 16

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Rapid Binary Sensor for STAR: power budget estimation Power budget assumed for Integration time = 50 µs/n; n: number of parallel-processed rows Acquisition 1000 x 1000 pixels Discriminators New block: Diff. amplifier Sparsifying logic Readout 50 m. W * n 20 m. W ? ? ? (50 m. W) <100 m. W Conclusion: always < 100 m. W/cm 2; with a good safety factor It is maybe a good idea to have the same power dissipation during acquisition and readout phases: n = 5 Tint = 10 µs. Same power same current less problems with power lines stabilization (? ) 16

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Conclusions - A new scheme for a binary MAPS is proposed - Substantial decrease of integration time is possible, with a lower power budget! - Less sensitivity to dark current, lower occupancy, lower data throughput - Do we buy it and continue? ? ? - Answer expected ASAP 17

Wojciech Dulinski dulinski@lepsi. in 2 p 3. fr STAR Microvertex Upgrade Meeting, Strasbourg, May 2007 Conclusions - A new scheme for a binary MAPS is proposed - Substantial decrease of integration time is possible, with a lower power budget! - Less sensitivity to dark current, lower occupancy, lower data throughput - Do we buy it and continue? ? ? - Answer expected ASAP 17