f72689762bc36528408e74796d3d23ed.ppt

- Количество слайдов: 19

Where do we stand? Where do we go? TDAQ Working group meeting Mainz – 8/9/2011

Where do we stand? Where do we go? TDAQ Working group meeting Mainz – 8/9/2011

2 meetings at the price of 1

2 meetings at the price of 1

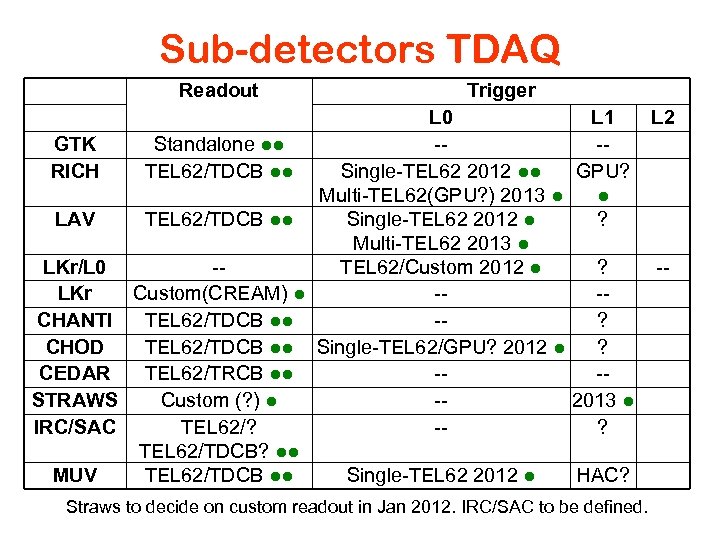

Sub-detectors TDAQ Readout Trigger L 0 L 1 L 2 GTK Standalone ●● --RICH TEL 62/TDCB ●● Single-TEL 62 2012 ●● GPU? Multi-TEL 62(GPU? ) 2013 ● ● LAV TEL 62/TDCB ●● Single-TEL 62 2012 ● ? Multi-TEL 62 2013 ● LKr/L 0 -TEL 62/Custom 2012 ● ? -LKr Custom(CREAM) ● --CHANTI TEL 62/TDCB ●● -? CHOD TEL 62/TDCB ●● Single-TEL 62/GPU? 2012 ● ? CEDAR TEL 62/TRCB ●● --STRAWS Custom (? ) ● -2013 ● IRC/SAC TEL 62/? -? TEL 62/TDCB? ●● MUV TEL 62/TDCB ●● Single-TEL 62 2012 ● HAC? Straws to decide on custom readout in Jan 2012. IRC/SAC to be defined.

Sub-detectors TDAQ Readout Trigger L 0 L 1 L 2 GTK Standalone ●● --RICH TEL 62/TDCB ●● Single-TEL 62 2012 ●● GPU? Multi-TEL 62(GPU? ) 2013 ● ● LAV TEL 62/TDCB ●● Single-TEL 62 2012 ● ? Multi-TEL 62 2013 ● LKr/L 0 -TEL 62/Custom 2012 ● ? -LKr Custom(CREAM) ● --CHANTI TEL 62/TDCB ●● -? CHOD TEL 62/TDCB ●● Single-TEL 62/GPU? 2012 ● ? CEDAR TEL 62/TRCB ●● --STRAWS Custom (? ) ● -2013 ● IRC/SAC TEL 62/? -? TEL 62/TDCB? ●● MUV TEL 62/TDCB ●● Single-TEL 62 2012 ● HAC? Straws to decide on custom readout in Jan 2012. IRC/SAC to be defined.

TDCB - I Status report by B. Angelucci • Pre-production done (total 14 boards exist) • Now: basic tests in Pisa • Ready for distribution in ~1 week (cables too) • Firmware: basic features working, improvements needed. Complete rewrite and simulation would be advisable if manpower were available.

TDCB - I Status report by B. Angelucci • Pre-production done (total 14 boards exist) • Now: basic tests in Pisa • Ready for distribution in ~1 week (cables too) • Firmware: basic features working, improvements needed. Complete rewrite and simulation would be advisable if manpower were available.

TDCB - II • Sub-detector groups should arrange testing (with TELL 1 s): RICH: validation in Perugia (M. Piccini) LAV: validation in Frascati (M. Raggi) CEDAR: validation in Birmingham (A. Romano) STRAWS (fallback): validation in CERN (A. Sergi) MUV: ? CHANTI: ? SAC/IRC (if used? ): ? Expect validation from sub-detectors (sustainable rate, time resolution, noise, etc. ) • After tests and validation from the sub-detectors: ready for full production. • Default: full production in 2013. No more boards to be produced before final production unless decided otherwise (earlier full production is an option) Test setup for large number of boards to be built in Pisa

TDCB - II • Sub-detector groups should arrange testing (with TELL 1 s): RICH: validation in Perugia (M. Piccini) LAV: validation in Frascati (M. Raggi) CEDAR: validation in Birmingham (A. Romano) STRAWS (fallback): validation in CERN (A. Sergi) MUV: ? CHANTI: ? SAC/IRC (if used? ): ? Expect validation from sub-detectors (sustainable rate, time resolution, noise, etc. ) • After tests and validation from the sub-detectors: ready for full production. • Default: full production in 2013. No more boards to be produced before final production unless decided otherwise (earlier full production is an option) Test setup for large number of boards to be built in Pisa

TELL 1 s (either bought or on loan) are now available in: Pisa Perugia Roma Tor Vergata Birmingham CERN Mainz Napoli LNF One still available to loan Lab setup and TDCB tests possible with TELL 1 s

TELL 1 s (either bought or on loan) are now available in: Pisa Perugia Roma Tor Vergata Birmingham CERN Mainz Napoli LNF One still available to loan Lab setup and TDCB tests possible with TELL 1 s

TEL 62 Status report by E. Pedreschi • One more prototype PCB can be mounted on short notice IF somebody is willing to get it and make significant tests before the end of the year • Produce 10 boards at the end of 2011, to be used in the Dry/Test runs • Default: full production in 2013 (Pisa+Roma TV). No more boards to be produced before final production unless decided otherwise • Test procedure: in house/at firm ? Roma TV will produce test vectors • Complete procurement of all components by early 2012 • Recall: fallback solution for straws not included in component procurement

TEL 62 Status report by E. Pedreschi • One more prototype PCB can be mounted on short notice IF somebody is willing to get it and make significant tests before the end of the year • Produce 10 boards at the end of 2011, to be used in the Dry/Test runs • Default: full production in 2013 (Pisa+Roma TV). No more boards to be produced before final production unless decided otherwise • Test procedure: in house/at firm ? Roma TV will produce test vectors • Complete procurement of all components by early 2012 • Recall: fallback solution for straws not included in component procurement

TEL 62 firmware New framework for TEL 62 started. Prioritization of tasks to have basic functionality ready for next year’s runs Manpower issues still present Involvement of 1 person per sub-detector needed: RICH: C. Santoni (Perugia) LAV: M. Raggi (Frascati) CEDAR: M. Krivda (Birmingham) LKr: G. Lamanna (CERN) LKr/L 0: A. Salamon (Roma TV) CHANTI: ? MUV: M. Hita-Hochgesand (Mainz) SAC/IRC: ? Dedicated TEL 62 firmware working meeting later today.

TEL 62 firmware New framework for TEL 62 started. Prioritization of tasks to have basic functionality ready for next year’s runs Manpower issues still present Involvement of 1 person per sub-detector needed: RICH: C. Santoni (Perugia) LAV: M. Raggi (Frascati) CEDAR: M. Krivda (Birmingham) LKr: G. Lamanna (CERN) LKr/L 0: A. Salamon (Roma TV) CHANTI: ? MUV: M. Hita-Hochgesand (Mainz) SAC/IRC: ? Dedicated TEL 62 firmware working meeting later today.

Autumn sale • 1 TEL 62: 3500 € • 1 TDCB: 1000 € • Set of 4 Cables: 500 € Lower prices expected for final production We ship worldwide with very good rates Boards come with working base firmware and nice color manual in electronic format Instruction courses available on subscription Hotline assistance available Pay with TID to NA 62 account T 145400 routing the document to me for information

Autumn sale • 1 TEL 62: 3500 € • 1 TDCB: 1000 € • Set of 4 Cables: 500 € Lower prices expected for final production We ship worldwide with very good rates Boards come with working base firmware and nice color manual in electronic format Instruction courses available on subscription Hotline assistance available Pay with TID to NA 62 account T 145400 routing the document to me for information

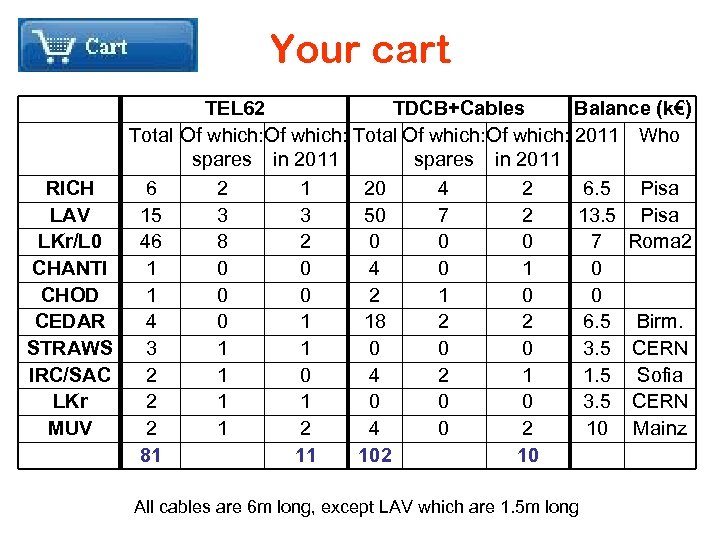

Your cart Total RICH LAV LKr/L 0 CHANTI CHOD CEDAR STRAWS IRC/SAC LKr MUV 6 15 46 1 1 4 3 2 2 2 81 TEL 62 TDCB+Cables Balance (k€) Of which: Total Of which: 2011 Who spares in 2011 2 1 20 4 2 6. 5 Pisa 3 3 50 7 2 13. 5 Pisa 8 2 0 0 0 7 Roma 2 0 0 4 0 1 0 0 0 2 1 0 0 0 1 18 2 2 6. 5 Birm. 1 1 0 0 0 3. 5 CERN 1 0 4 2 1 1. 5 Sofia 1 1 0 0 0 3. 5 CERN 1 2 4 0 2 10 Mainz 11 102 10 All cables are 6 m long, except LAV which are 1. 5 m long

Your cart Total RICH LAV LKr/L 0 CHANTI CHOD CEDAR STRAWS IRC/SAC LKr MUV 6 15 46 1 1 4 3 2 2 2 81 TEL 62 TDCB+Cables Balance (k€) Of which: Total Of which: 2011 Who spares in 2011 2 1 20 4 2 6. 5 Pisa 3 3 50 7 2 13. 5 Pisa 8 2 0 0 0 7 Roma 2 0 0 4 0 1 0 0 0 2 1 0 0 0 1 18 2 2 6. 5 Birm. 1 1 0 0 0 3. 5 CERN 1 0 4 2 1 1. 5 Sofia 1 1 0 0 0 3. 5 CERN 1 2 4 0 2 10 Mainz 11 102 10 All cables are 6 m long, except LAV which are 1. 5 m long

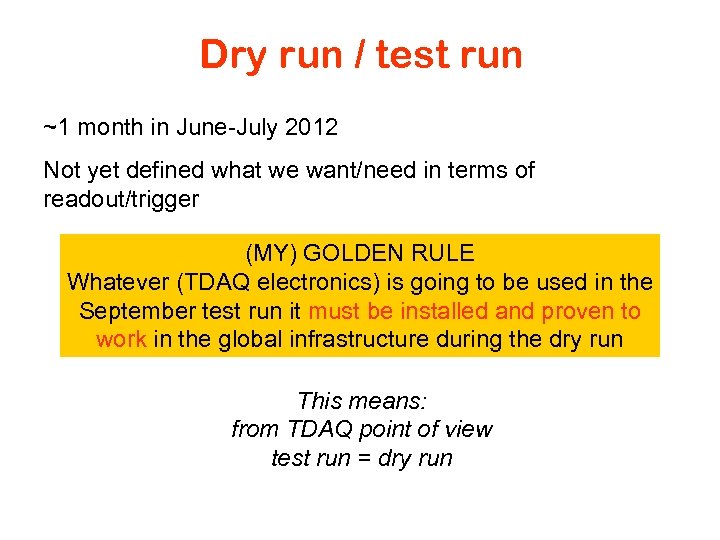

Dry run / test run ~1 month in June-July 2012 Not yet defined what we want/need in terms of readout/trigger (MY) GOLDEN RULE Whatever (TDAQ electronics) is going to be used in the September test run it must be installed and proven to work in the global infrastructure during the dry run This means: from TDAQ point of view test run = dry run

Dry run / test run ~1 month in June-July 2012 Not yet defined what we want/need in terms of readout/trigger (MY) GOLDEN RULE Whatever (TDAQ electronics) is going to be used in the September test run it must be installed and proven to work in the global infrastructure during the dry run This means: from TDAQ point of view test run = dry run

Dry run / test run: minimal goals - O(100) channels/sub-detector readout in coherent events - Full LKr readout - Conventional CHOD L 0 trigger distributed via TTC - Full control of start/end spill (triggers) and special triggers - Parasitic L 0 trigger primitives in data - TEL 62/TDCB: complete readout, no inter-board communication - Data readout to PCs with no software trigger(s) but rough event building - Indipendent sub-detector initialization “by hand” Baseline plan (equipment, goals, priorities) to be drafted by next meeting. Need to start dedicated planning meetings

Dry run / test run: minimal goals - O(100) channels/sub-detector readout in coherent events - Full LKr readout - Conventional CHOD L 0 trigger distributed via TTC - Full control of start/end spill (triggers) and special triggers - Parasitic L 0 trigger primitives in data - TEL 62/TDCB: complete readout, no inter-board communication - Data readout to PCs with no software trigger(s) but rough event building - Indipendent sub-detector initialization “by hand” Baseline plan (equipment, goals, priorities) to be drafted by next meeting. Need to start dedicated planning meetings

Crates • Two (slightly) different versions of Wiener crates, both compatible with TEL 62 (7700 €) • One prototype of each available in NA 62: Roma Tor Vergata and Frascati • Test with TEL 62 in 1 month (fake power-consuming firmware required) • Assessment with FE electronics? • Ordering and schedule? • Full software support from CERN expected

Crates • Two (slightly) different versions of Wiener crates, both compatible with TEL 62 (7700 €) • One prototype of each available in NA 62: Roma Tor Vergata and Frascati • Test with TEL 62 in 1 month (fake power-consuming firmware required) • Assessment with FE electronics? • Ordering and schedule? • Full software support from CERN expected

![Clock – Sub-detector stuff [Update from M. Krivda] LTU (NA 62 version of ALICE Clock – Sub-detector stuff [Update from M. Krivda] LTU (NA 62 version of ALICE](https://present5.com/presentation/f72689762bc36528408e74796d3d23ed/image-14.jpg) Clock – Sub-detector stuff [Update from M. Krivda] LTU (NA 62 version of ALICE board, Birmingham): paid for, ready, available, firmware being developed TTCex (new version, CERN): paid for, built, PLL problem found with new version, solution under investigation, no time estimate

Clock – Sub-detector stuff [Update from M. Krivda] LTU (NA 62 version of ALICE board, Birmingham): paid for, ready, available, firmware being developed TTCex (new version, CERN): paid for, built, PLL problem found with new version, solution under investigation, no time estimate

Clock – Common stuff Master clock generator: NA 48 one available (no spare) Fibres Layout finalized, document being finalized, to be bought (common fund), expect installation at beginning of 2012 Splitters Number defined, collecting offers for common order TTCit monitor board: production starting in September

Clock – Common stuff Master clock generator: NA 48 one available (no spare) Fibres Layout finalized, document being finalized, to be bought (common fund), expect installation at beginning of 2012 Splitters Number defined, collecting offers for common order TTCit monitor board: production starting in September

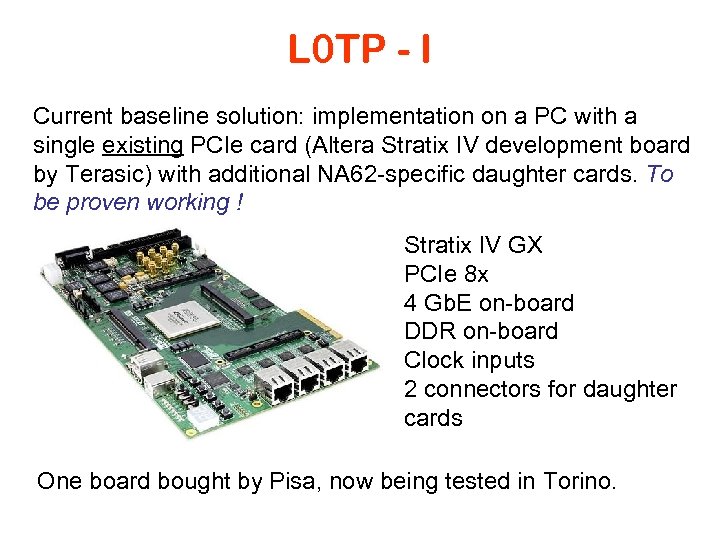

L 0 TP - I Current baseline solution: implementation on a PC with a single existing PCIe card (Altera Stratix IV development board by Terasic) with additional NA 62 -specific daughter cards. To be proven working ! Stratix IV GX PCIe 8 x 4 Gb. E on-board DDR on-board Clock inputs 2 connectors for daughter cards One board bought by Pisa, now being tested in Torino.

L 0 TP - I Current baseline solution: implementation on a PC with a single existing PCIe card (Altera Stratix IV development board by Terasic) with additional NA 62 -specific daughter cards. To be proven working ! Stratix IV GX PCIe 8 x 4 Gb. E on-board DDR on-board Clock inputs 2 connectors for daughter cards One board bought by Pisa, now being tested in Torino.

L 0 TP- II Torino group (E. Menichetti) joined the effort Current status/plan: - Ferrara to provide the board firmware - Torino to provide additional daughter cards - L 0 trigger-matching code (on PC) not yet covered (1) Is this solution viable in terms of L 0 latency? (2) L 0 TP for 2012 run(s): (a) prototype version of PC-based L 0 TP OR (b) “patched” temporary solution (e. g. Talk board) Assessment of (2) (and (1)? ) by fall 2011

L 0 TP- II Torino group (E. Menichetti) joined the effort Current status/plan: - Ferrara to provide the board firmware - Torino to provide additional daughter cards - L 0 trigger-matching code (on PC) not yet covered (1) Is this solution viable in terms of L 0 latency? (2) L 0 TP for 2012 run(s): (a) prototype version of PC-based L 0 TP OR (b) “patched” temporary solution (e. g. Talk board) Assessment of (2) (and (1)? ) by fall 2011

![Higher-level triggers (1) Proposal @ Computing WG [J. Kunze]: merge all PC farms into Higher-level triggers (1) Proposal @ Computing WG [J. Kunze]: merge all PC farms into](https://present5.com/presentation/f72689762bc36528408e74796d3d23ed/image-18.jpg) Higher-level triggers (1) Proposal @ Computing WG [J. Kunze]: merge all PC farms into a single one to be used both for L 1 and L 2 (incl. LKr) - L 1 during the spill - L 2 during the inter-spill (not starting until then) (all event data in memory during the spill) Looks reasonable (no latency issues) more flexible and possibly less expensive Assessment? What about 2012? (2) No L 1 recipe so far to reach 100 k. Hz Downscaled/control triggers might (= will) easily saturate ANY trigger bandwidth in NA 62: bandwidth allocation proposal needed (also true for L 0)

Higher-level triggers (1) Proposal @ Computing WG [J. Kunze]: merge all PC farms into a single one to be used both for L 1 and L 2 (incl. LKr) - L 1 during the spill - L 2 during the inter-spill (not starting until then) (all event data in memory during the spill) Looks reasonable (no latency issues) more flexible and possibly less expensive Assessment? What about 2012? (2) No L 1 recipe so far to reach 100 k. Hz Downscaled/control triggers might (= will) easily saturate ANY trigger bandwidth in NA 62: bandwidth allocation proposal needed (also true for L 0)

Critical/urgent issues 1. L 0 TP: demonstrate we have a viable solution 2. Online software: start, responsibility? 3. TEL 62 firmware: have basics ready for 2012 4. TELL 1 radiation tests: (Birmingham) 5. Crates: validate, buy and get 6. Simulation: L 0 for LKr, L 1 and L 2 7. Data transfer layer SW: common, avoid independent developments 8. Central repository: for documentation, firmware, software 9. Finalize specifications: e. g. fine time (sub 25 -ns) information with each L 0 trigger? [GTK, straws]

Critical/urgent issues 1. L 0 TP: demonstrate we have a viable solution 2. Online software: start, responsibility? 3. TEL 62 firmware: have basics ready for 2012 4. TELL 1 radiation tests: (Birmingham) 5. Crates: validate, buy and get 6. Simulation: L 0 for LKr, L 1 and L 2 7. Data transfer layer SW: common, avoid independent developments 8. Central repository: for documentation, firmware, software 9. Finalize specifications: e. g. fine time (sub 25 -ns) information with each L 0 trigger? [GTK, straws]