6c684f7b966a12844c921f789e4e9401.ppt

- Количество слайдов: 29

WELCOME TO EE 457 COMPUTER SYSTEMS ORGANIZATION

WELCOME TO EE 457 COMPUTER SYSTEMS ORGANIZATION

THREE MAIN TOPICS 1. CPU DESIGN 2. MEMORY SYSTEM 3. COMPUTER ARITHMETIC

THREE MAIN TOPICS 1. CPU DESIGN 2. MEMORY SYSTEM 3. COMPUTER ARITHMETIC

CPU DESIGN MICRO-ARCHITECTURE DESIGN GENERAL DIGITAL SYSTEM DESIGN

CPU DESIGN MICRO-ARCHITECTURE DESIGN GENERAL DIGITAL SYSTEM DESIGN

MEMORY SYSTEM DESIGN CACHE + VIRTUAL MEMORY

MEMORY SYSTEM DESIGN CACHE + VIRTUAL MEMORY

COMPUTER ARITHMETIC 2’s Complement Arithmetic Review FAST ADDERS FAST MULTIPLIERS NON-LINEAR PIPELINES FOR ARTHMETIC OPERATIONS

COMPUTER ARITHMETIC 2’s Complement Arithmetic Review FAST ADDERS FAST MULTIPLIERS NON-LINEAR PIPELINES FOR ARTHMETIC OPERATIONS

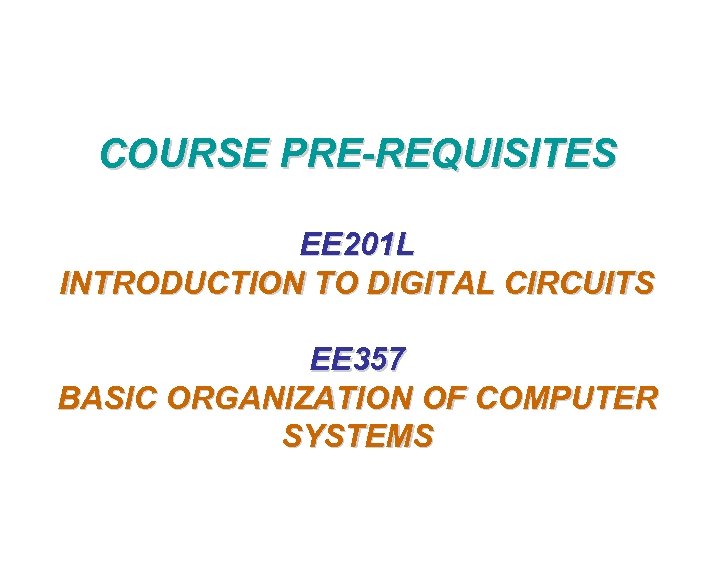

COURSE PRE-REQUISITES EE 201 L INTRODUCTION TO DIGITAL CIRCUITS EE 357 BASIC ORGANIZATION OF COMPUTER SYSTEMS

COURSE PRE-REQUISITES EE 201 L INTRODUCTION TO DIGITAL CIRCUITS EE 357 BASIC ORGANIZATION OF COMPUTER SYSTEMS

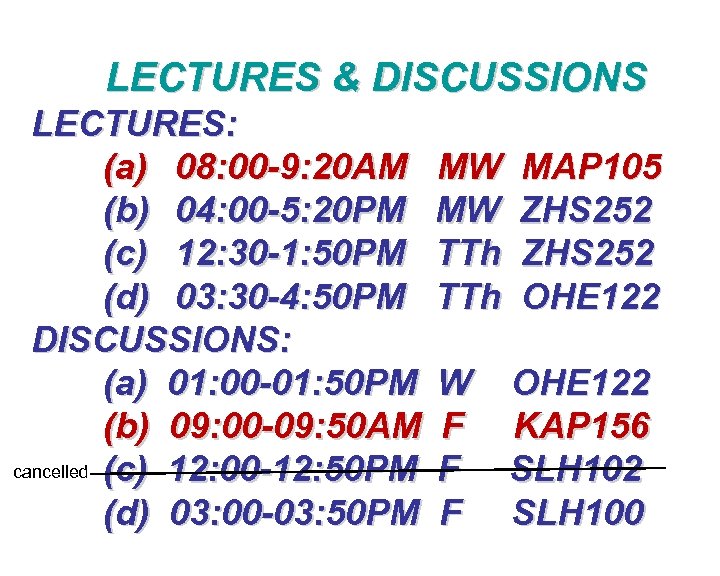

LECTURES & DISCUSSIONS LECTURES: (a) 08: 00 -9: 20 AM (b) 04: 00 -5: 20 PM (c) 12: 30 -1: 50 PM (d) 03: 30 -4: 50 PM DISCUSSIONS: (a) 01: 00 -01: 50 PM (b) 09: 00 -09: 50 AM cancelled (c) 12: 00 -12: 50 PM (d) 03: 00 -03: 50 PM MW MW TTh MAP 105 ZHS 252 OHE 122 W F F F OHE 122 KAP 156 SLH 102 SLH 100

LECTURES & DISCUSSIONS LECTURES: (a) 08: 00 -9: 20 AM (b) 04: 00 -5: 20 PM (c) 12: 30 -1: 50 PM (d) 03: 30 -4: 50 PM DISCUSSIONS: (a) 01: 00 -01: 50 PM (b) 09: 00 -09: 50 AM cancelled (c) 12: 00 -12: 50 PM (d) 03: 00 -03: 50 PM MW MW TTh MAP 105 ZHS 252 OHE 122 W F F F OHE 122 KAP 156 SLH 102 SLH 100

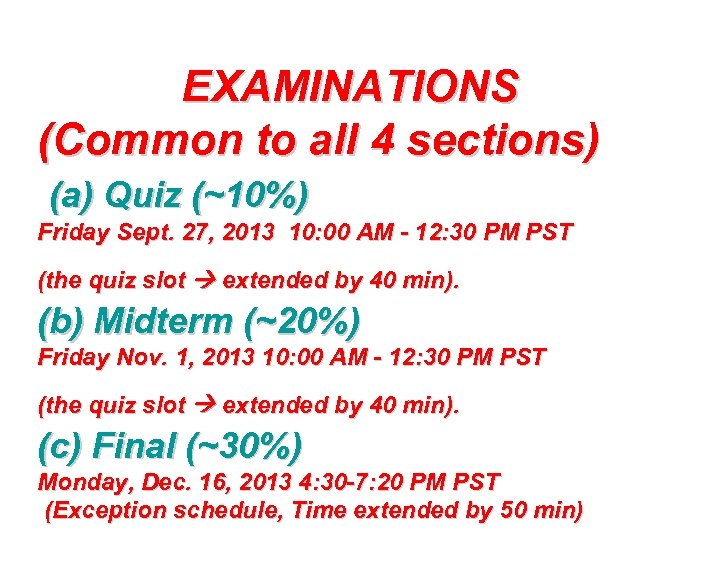

EXAMINATIONS (Common to all 4 sections) (a) Quiz (~10%) Friday Sept. 27, 2013 10: 00 AM - 12: 30 PM PST (the quiz slot extended by 40 min). (b) Midterm (~20%) Friday Nov. 1, 2013 10: 00 AM - 12: 30 PM PST (the quiz slot extended by 40 min). (c) Final (~30%) Monday, Dec. 16, 2013 4: 30 -7: 20 PM PST (Exception schedule, Time extended by 50 min)

EXAMINATIONS (Common to all 4 sections) (a) Quiz (~10%) Friday Sept. 27, 2013 10: 00 AM - 12: 30 PM PST (the quiz slot extended by 40 min). (b) Midterm (~20%) Friday Nov. 1, 2013 10: 00 AM - 12: 30 PM PST (the quiz slot extended by 40 min). (c) Final (~30%) Monday, Dec. 16, 2013 4: 30 -7: 20 PM PST (Exception schedule, Time extended by 50 min)

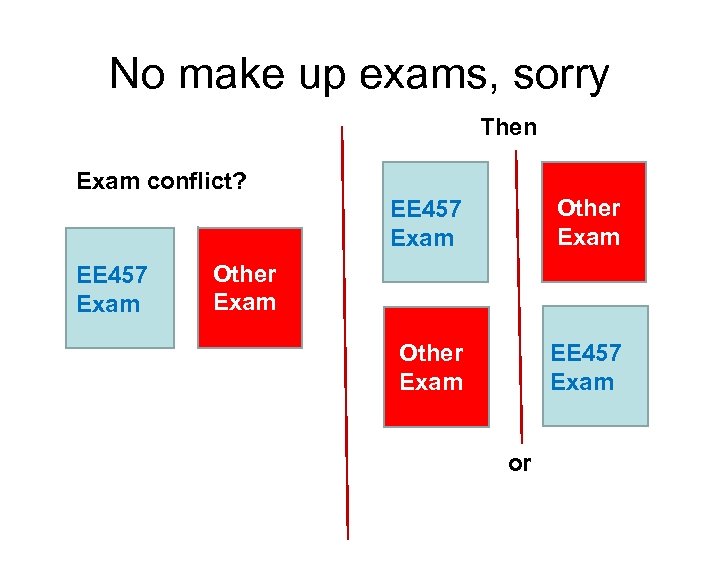

No make up exams, sorry Then Exam conflict? EE 457 Exam Other Exam or

No make up exams, sorry Then Exam conflict? EE 457 Exam Other Exam or

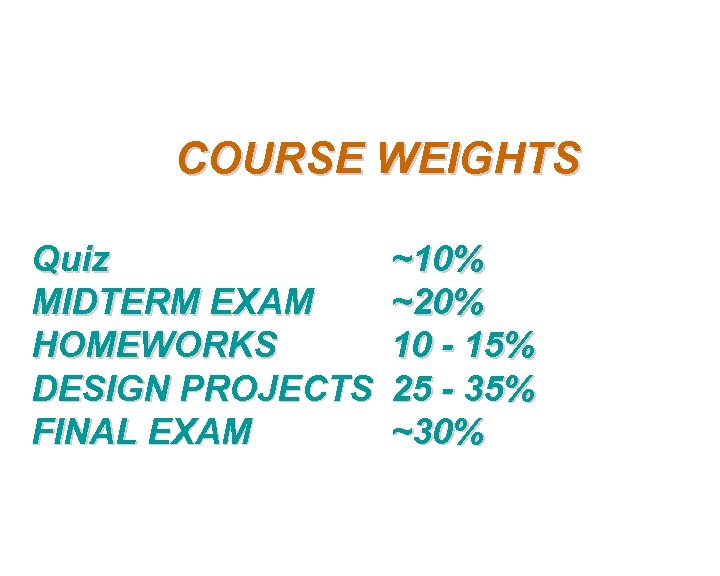

COURSE WEIGHTS Quiz MIDTERM EXAM HOMEWORKS DESIGN PROJECTS FINAL EXAM ~10% ~20% 10 - 15% 25 - 35% ~30%

COURSE WEIGHTS Quiz MIDTERM EXAM HOMEWORKS DESIGN PROJECTS FINAL EXAM ~10% ~20% 10 - 15% 25 - 35% ~30%

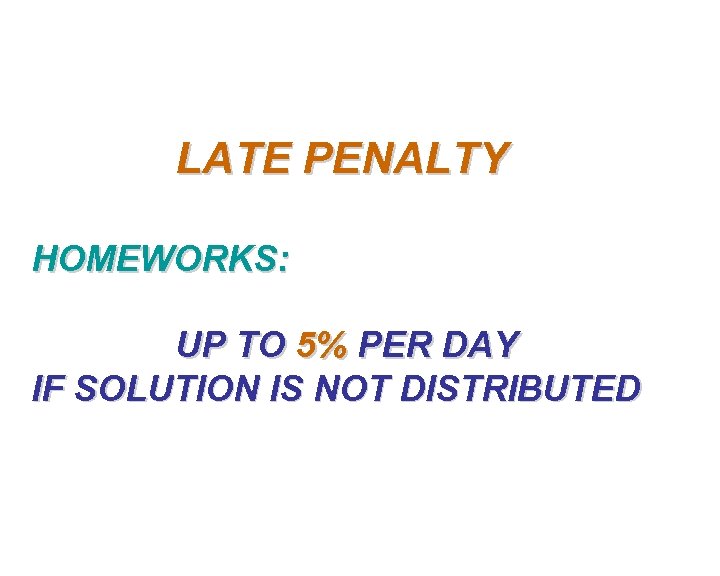

LATE PENALTY HOMEWORKS: UP TO 5% PER DAY IF SOLUTION IS NOT DISTRIBUTED

LATE PENALTY HOMEWORKS: UP TO 5% PER DAY IF SOLUTION IS NOT DISTRIBUTED

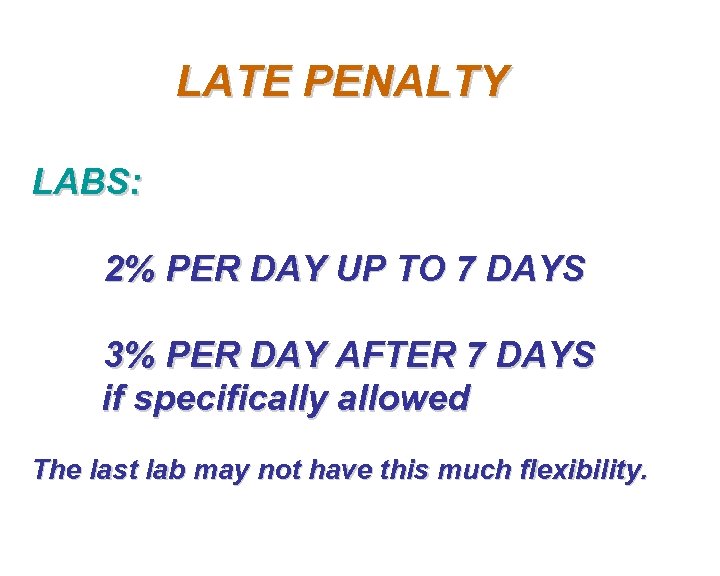

LATE PENALTY LABS: 2% PER DAY UP TO 7 DAYS 3% PER DAY AFTER 7 DAYS if specifically allowed The last lab may not have this much flexibility.

LATE PENALTY LABS: 2% PER DAY UP TO 7 DAYS 3% PER DAY AFTER 7 DAYS if specifically allowed The last lab may not have this much flexibility.

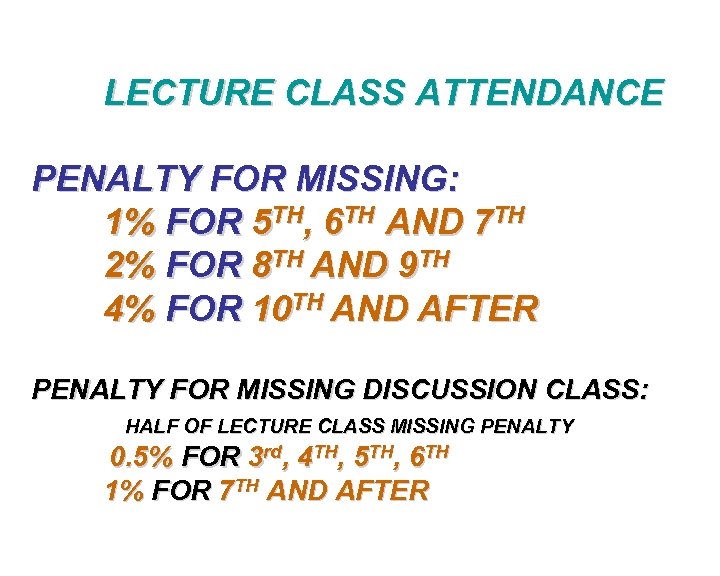

LECTURE CLASS ATTENDANCE PENALTY FOR MISSING: 1% FOR 5 TH, 6 TH AND 7 TH 2% FOR 8 TH AND 9 TH 4% FOR 10 TH AND AFTER PENALTY FOR MISSING DISCUSSION CLASS: HALF OF LECTURE CLASS MISSING PENALTY 0. 5% FOR 3 rd, 4 TH, 5 TH, 6 TH 1% FOR 7 TH AND AFTER

LECTURE CLASS ATTENDANCE PENALTY FOR MISSING: 1% FOR 5 TH, 6 TH AND 7 TH 2% FOR 8 TH AND 9 TH 4% FOR 10 TH AND AFTER PENALTY FOR MISSING DISCUSSION CLASS: HALF OF LECTURE CLASS MISSING PENALTY 0. 5% FOR 3 rd, 4 TH, 5 TH, 6 TH 1% FOR 7 TH AND AFTER

REMOTE STUDENTS gandhi@usc. edu

REMOTE STUDENTS gandhi@usc. edu

Two instructors: 1. Gandhi Puvvada gandhi@usc. edu 2. Waleed Dweik dweik@usc. edu Common TAs (3), Mentors (6), and Graders (6 HW + 6 Lab) Common blackboard (den. usc. edu) Common discussions, assignments, and exams

Two instructors: 1. Gandhi Puvvada gandhi@usc. edu 2. Waleed Dweik dweik@usc. edu Common TAs (3), Mentors (6), and Graders (6 HW + 6 Lab) Common blackboard (den. usc. edu) Common discussions, assignments, and exams

DESIGN PROJECTS PARTIALLY COMPLETE DESIGN FILES Core design Verilog file: ~50% complete Testbench and wave. do files: ~80% to 100% complete TTL DATABOOK NOT NECESSARY

DESIGN PROJECTS PARTIALLY COMPLETE DESIGN FILES Core design Verilog file: ~50% complete Testbench and wave. do files: ~80% to 100% complete TTL DATABOOK NOT NECESSARY

Esperan Verilog Reference Guide Is posted on the BB for personal use of USC faculty and students. -- please do not distribute, do not post it anywhere

Esperan Verilog Reference Guide Is posted on the BB for personal use of USC faculty and students. -- please do not distribute, do not post it anywhere

IEEE Verilog standard ieee 1364 -2001 for USC library members only -- please do not distribute

IEEE Verilog standard ieee 1364 -2001 for USC library members only -- please do not distribute

HOMEWORK: INDIVIDUAL EFFORT LAB: (1) VERILOG CODING, SIMULATION AND DEBUGGING TEAM EFFORT (2) JUSTIFICATION, END-OF-LAB QUESTIONS INDIVIDUAL EFFORT

HOMEWORK: INDIVIDUAL EFFORT LAB: (1) VERILOG CODING, SIMULATION AND DEBUGGING TEAM EFFORT (2) JUSTIFICATION, END-OF-LAB QUESTIONS INDIVIDUAL EFFORT

CLASS WEBPAGE DEN BLACKBOARD den. usc. edu https: //www. uscden. net/webapps/login/ LEC / DIS WEBCASTS ASSIGNMENTS ANNOUNCEMENTS OFFICE HOURS EMAIL

CLASS WEBPAGE DEN BLACKBOARD den. usc. edu https: //www. uscden. net/webapps/login/ LEC / DIS WEBCASTS ASSIGNMENTS ANNOUNCEMENTS OFFICE HOURS EMAIL

Verilog language and Model. Simulator INTRO. LECTUREs are posted

Verilog language and Model. Simulator INTRO. LECTUREs are posted

Buy these two items from the Bookstores (1) TEXTBOOK Computer Organization & Design - The Hardware and Software Interface 4 th edition (Revised Printing) By D. A. Patterson (Berkeley) and J. L. Hennesy (Stanford) (2) CLASS NOTE CHAPTER 1 ON THE BLACK-BOARD ===================== Lab Manual. pdf files will be posted progressively on the BB

Buy these two items from the Bookstores (1) TEXTBOOK Computer Organization & Design - The Hardware and Software Interface 4 th edition (Revised Printing) By D. A. Patterson (Berkeley) and J. L. Hennesy (Stanford) (2) CLASS NOTE CHAPTER 1 ON THE BLACK-BOARD ===================== Lab Manual. pdf files will be posted progressively on the BB

Understand, No need to memorize, Learn to design. Demonstrate your understanding in the exam ~40 to ~50 hours of office hours per week

Understand, No need to memorize, Learn to design. Demonstrate your understanding in the exam ~40 to ~50 hours of office hours per week

Grades

Grades

Grades • Very easy to get an A grade

Grades • Very easy to get an A grade

Grades • Very easy to get an A grade • Equally easy to get a F grade

Grades • Very easy to get an A grade • Equally easy to get a F grade

Grades • Very easy to get an A grade • Equally easy to get a F grade

Grades • Very easy to get an A grade • Equally easy to get a F grade

We appreciate your efforts • ~ 60% of the class gets an A grade No place for the lazy and uninterested • ~20% of the class fails or drops

We appreciate your efforts • ~ 60% of the class gets an A grade No place for the lazy and uninterested • ~20% of the class fails or drops

There is no competition. Everyone can get an A grade. You need to aspire for it, and you need to work for it. You get what you worked for. No grace grade (No minimum grade).

There is no competition. Everyone can get an A grade. You need to aspire for it, and you need to work for it. You get what you worked for. No grace grade (No minimum grade).