Презентация бакалаврской.ppt

- Количество слайдов: 16

Выпускная работа на соискание степени бакалавра техники и технологии на тему: Коммутатор, связывающий один из восьми входов с одним из восьми выходов.

Таблица параметров структуры Техническое задание • Разработать интегральную схему коммутатора, связывающего один из восьми входов с одним из восьми выходов. Используемый базис – ТТЛ. Изоляция – изопланарная. Технологическая норма 2, 5 мкм. Параметры слоёв структуры представлены в таблице. Тип проводи- № Функции слоя 1 Подложка p 400± 40 10± 2 2 Скрытый слой n+ 3± 0. 5 25± 8 3 Эпитаксиальный слой n 3± 0. 5 0. 6± 0. 1 4 Разделительные области p+ 4. 5± 0. 8 15± 5 5 Глубокий коллектор n+ 4. 5± 0. 8 15± 5 6 База активная p 1. 3± 0. 2 200± 50 7 Эмиттер n++ 0. 8± 0. 15 12± 3 мости Толщина, мкм Удельное сопротивление ρs Ом/□ (или ρ Ом см)

План выполнения задания • 1. Разработка логической схемы устройства. • 2. Разработка технологического маршрута изготовления биполярного транзистора. • 3. Расчёт параметров модели интегрального биполярного транзистора. • 4. Разработка электрической схемы и топологии базового ЛЭ.

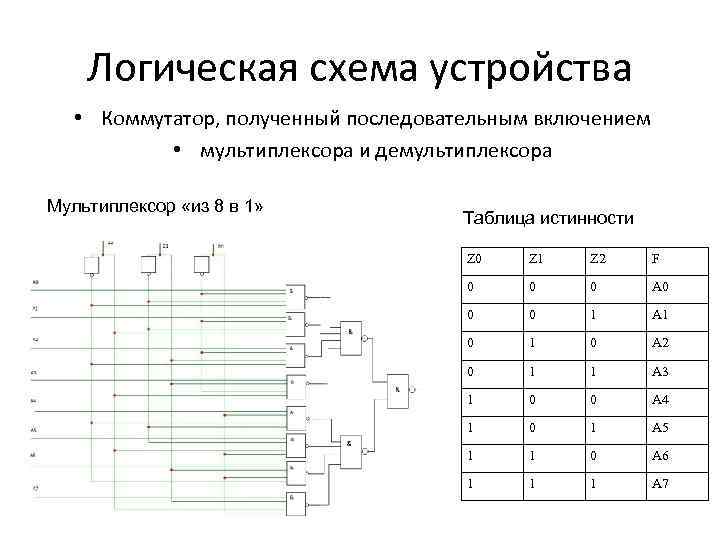

Логическая схема устройства • Коммутатор, полученный последовательным включением • мультиплексора и демультиплексора Мультиплексор «из 8 в 1» Таблица истинности Z 0 Z 1 Z 2 F 0 0 0 A 0 0 0 1 A 1 0 A 2 0 1 1 A 3 1 0 0 A 4 1 0 1 A 5 1 1 0 A 6 1 1 1 A 7

Демультиплексор «из 1 в 8» S 0 S 1 S 2 B 0 B 1 B 2 B 3 B 4 B 5 B 6 B 7 0 0 0 F 0 0 0 0 0 1 0 F 0 0 0 0 1 0 0 0 F 0 0 0 1 1 0 0 0 F 0 0 0 1 0 0 0 F 0 0 1 1 0 0 0 0 F 0 1 1 1 0 0 0 0 F

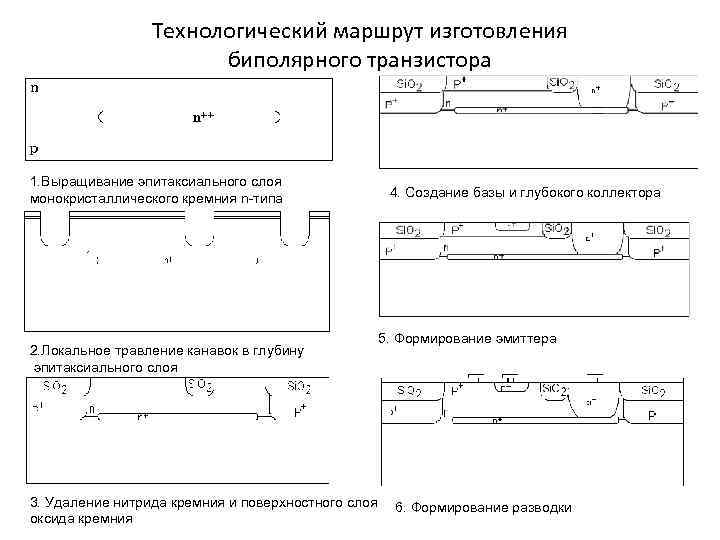

Технологический маршрут изготовления биполярного транзистора 1. Выращивание эпитаксиального слоя монокристаллического кремния n-типа 2. Локальное травление канавок в глубину эпитаксиального слоя 4. Создание базы и глубокого коллектора 5. Формирование эмиттера 3. Удаление нитрида кремния и поверхностного слоя 6. Формирование разводки оксида кремния

Полученный интегральный транзистор Сечение биполярного транзистора, изготовленного по изопланарной технологии. Распределение примеси в сечении эмиттера.

Результаты загонки и разгонки примеси Подложка B Разделительные области Глубокий коллектор Активная база Примесь As В Р В Коэффициент диффузии (D, см 2/c) 4∙ 10 -15 2∙ 10 -13 1∙ 10 -14 Количество примеси (Q, 3, 7∙ 1015 7, 0∙ 1015 8, 6∙ 1015 6, 1∙ 1014 Параметры загонки (Dt, 4, 8∙ 10 -12 6, 1∙ 10 -10 2, 6∙ 10 -11 1, 32∙ 10 -11 9∙ 1015 см 2) 4∙ 10 -14 см -2) Р 2 Эмиттер 1 Скрытый слой Наименование параметра P № Эпитаксиальный слой 4, 23∙ 10 -11 3 4 5 (Dt)Σ , см 2 6∙ 10 -10 7, 5∙ 10 -9 5, 4∙ 10 -9 6∙ 10 -10 3, 1∙ 10 -10 6 ρS, Ом/кв 25 18 14, 9 200, 8 14, 4 7 ρ, Ом см 10, 1 0, 6 8 N, см-3 1, 3∙ 1015 9, 2∙ 1015 9 Глубина слоя (W, мкм) 3, 0 5, 0 4, 4 1, 3 0, 83 400 + 40 3, 0

Моделирование интегрального транзистора Двумерная структура транзистора

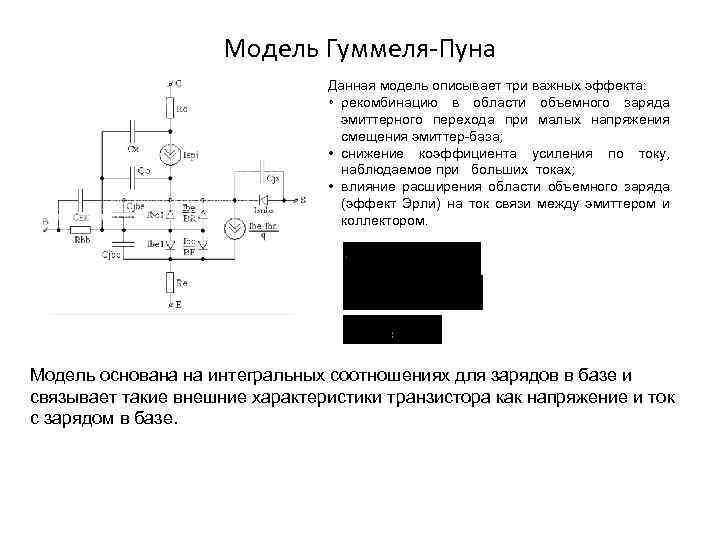

Модель Гуммеля-Пуна Данная модель описывает три важных эффекта: • рекомбинацию в области объемного заряда эмиттерного перехода при малых напряжения смещения эмиттер-база; • снижение коэффициента усиления по току, наблюдаемое при больших токах; • влияние расширения области объемного заряда (эффект Эрли) на ток связи между эмиттером и коллектором. Модель основана на интегральных соотношениях для зарядов в базе и связывает такие внешние характеристики транзистора как напряжение и ток с зарядом в базе.

Статистическая характеристика МЭТ График Гуммеля-Пуна для режима общая база (прямое включение) Выходная характеристика в схеме с общим эмиттером

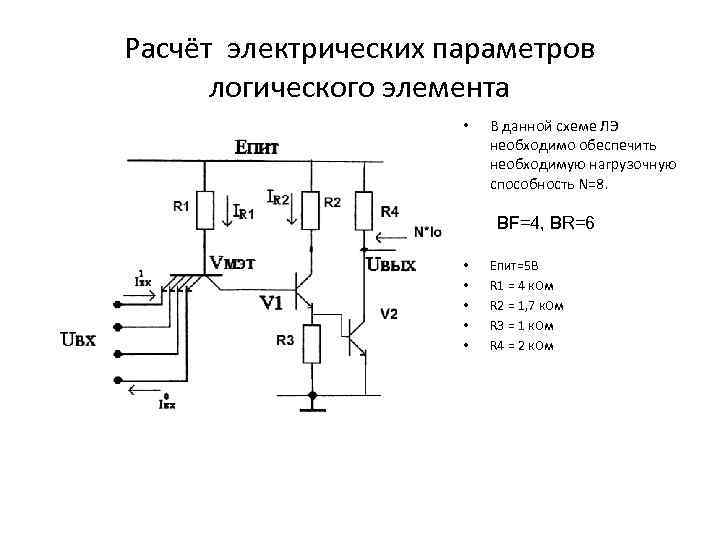

Расчёт электрических параметров логического элемента • В данной схеме ЛЭ необходимо обеспечить необходимую нагрузочную способность N=8. BF=4, BR=6 • • • Eпит=5 В R 1 = 4 к. Ом R 2 = 1, 7 к. Ом R 3 = 1 к. Ом R 4 = 2 к. Ом

Вариант топологии базового логического элемента

Пример топологии всего кристалла

Придание схеме работоспособности • Для того, чтобы схема стала работоспособной, необходимо понизить величину βinv. Этого можно добиться, если: • добавить в конструкцию МЭТ диод Шоттки, • либо изменив толщину ЭС, тем самым увеличив рекомбинацию носителей.

Презентация бакалаврской.ppt