л 1 2016 - понятие ВС.pptx

- Количество слайдов: 37

Вычислительные системы Под вычислительной системой (ВС) понимают совокупность нескольких взаимосвязанных и взаимодействующих компьютеров или узлов, включающих • процессор(ы), • запоминающие устройства (ЗУ), • периферийные устройства (ПУ) • и программное обеспечение (ПО), предназначенных для совместного решения задач пользователя. В отличие от ВС под ЭВМ подразумевали ВС со всеми основными устройствами в единственном экземпляре. По мере развития ВТ понятие ЭВМ устарело. Предпосылки возникновения ВС • предоставления пользователям дополнительных сервисных услуг, • повышения надежности и достоверности вычислений, • повышения производительности/вычислительной мощности.

Вычислительные системы Под вычислительной системой (ВС) понимают совокупность нескольких взаимосвязанных и взаимодействующих компьютеров или узлов, включающих • процессор(ы), • запоминающие устройства (ЗУ), • периферийные устройства (ПУ) • и программное обеспечение (ПО), предназначенных для совместного решения задач пользователя. В отличие от ВС под ЭВМ подразумевали ВС со всеми основными устройствами в единственном экземпляре. По мере развития ВТ понятие ЭВМ устарело. Предпосылки возникновения ВС • предоставления пользователям дополнительных сервисных услуг, • повышения надежности и достоверности вычислений, • повышения производительности/вычислительной мощности.

ПРЕДПОСЫЛКИ ВОЗНИКНОВЕНИЯ ВС 1. предоставления пользователям дополнительных сервисных услуг, подразумевает в первую очередь возможность одновременного выполнения нескольких/многих задач без потерь времени и задержек на переключение между отдельными задачами (программами/потоками). однопроцессорная однозадачная ЭВМ • • • → многозадачный компьютер → многопроцессорная ВС В ВС для каждой группы задач - своё управляюще-обрабатывающее устройство: несколько центральных процессоров (сегодня несколько ядер), сетевой (коммуникационный) процессор, графический процессор, множество периферийных устройств множество запоминающих устройств с собственными контроллерами (которые по сути, также являются упрощёнными специализированными процессорами). Что в итоге приводит к формированию сложной многопроцессорной вычислительной системы.

ПРЕДПОСЫЛКИ ВОЗНИКНОВЕНИЯ ВС 1. предоставления пользователям дополнительных сервисных услуг, подразумевает в первую очередь возможность одновременного выполнения нескольких/многих задач без потерь времени и задержек на переключение между отдельными задачами (программами/потоками). однопроцессорная однозадачная ЭВМ • • • → многозадачный компьютер → многопроцессорная ВС В ВС для каждой группы задач - своё управляюще-обрабатывающее устройство: несколько центральных процессоров (сегодня несколько ядер), сетевой (коммуникационный) процессор, графический процессор, множество периферийных устройств множество запоминающих устройств с собственными контроллерами (которые по сути, также являются упрощёнными специализированными процессорами). Что в итоге приводит к формированию сложной многопроцессорной вычислительной системы.

ПРЕДПОСЫЛКИ ВОЗНИКНОВЕНИЯ ВС 2. повышения надежности и достоверности вычислений, Цель: повысить • надёжность ВС • достоверность вычислений • возможность безотказной работы Средство достижения: дублирование • систем, • устройств, • вычислений. Создание вычислительной системы с несколькими устройствами памяти, вычислителями (процессорами) и проч. дублированными узлами. При отказе одного такого узла всегда продолжить/запустить вычисления на другом. существует возможность

ПРЕДПОСЫЛКИ ВОЗНИКНОВЕНИЯ ВС 2. повышения надежности и достоверности вычислений, Цель: повысить • надёжность ВС • достоверность вычислений • возможность безотказной работы Средство достижения: дублирование • систем, • устройств, • вычислений. Создание вычислительной системы с несколькими устройствами памяти, вычислителями (процессорами) и проч. дублированными узлами. При отказе одного такого узла всегда продолжить/запустить вычисления на другом. существует возможность

ПРЕДПОСЫЛКИ ВОЗНИКНОВЕНИЯ ВС 3. Повышение производительности Производительность определяется временем, затрачиваемым на решение определённых задач или числом выполняемых операций в единицу времени. Цель: повысить скорость выполнения операций или снизить время решения задачи Средства достижения: 1) ускорить коммутацию элементов микросхем за счёт совершенствования элементной базы и повышения тактовой частоты 2) Совершенствование архитектуры и распараллеливание вычислений = создание ВС

ПРЕДПОСЫЛКИ ВОЗНИКНОВЕНИЯ ВС 3. Повышение производительности Производительность определяется временем, затрачиваемым на решение определённых задач или числом выполняемых операций в единицу времени. Цель: повысить скорость выполнения операций или снизить время решения задачи Средства достижения: 1) ускорить коммутацию элементов микросхем за счёт совершенствования элементной базы и повышения тактовой частоты 2) Совершенствование архитектуры и распараллеливание вычислений = создание ВС

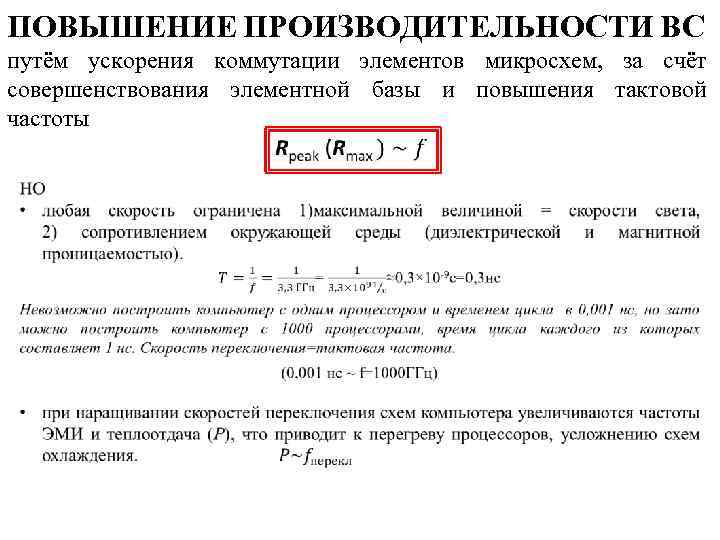

ПОВЫШЕНИЕ ПРОИЗВОДИТЕЛЬНОСТИ ВС путём ускорения коммутации элементов микросхем, за счёт совершенствования элементной базы и повышения тактовой частоты

ПОВЫШЕНИЕ ПРОИЗВОДИТЕЛЬНОСТИ ВС путём ускорения коммутации элементов микросхем, за счёт совершенствования элементной базы и повышения тактовой частоты

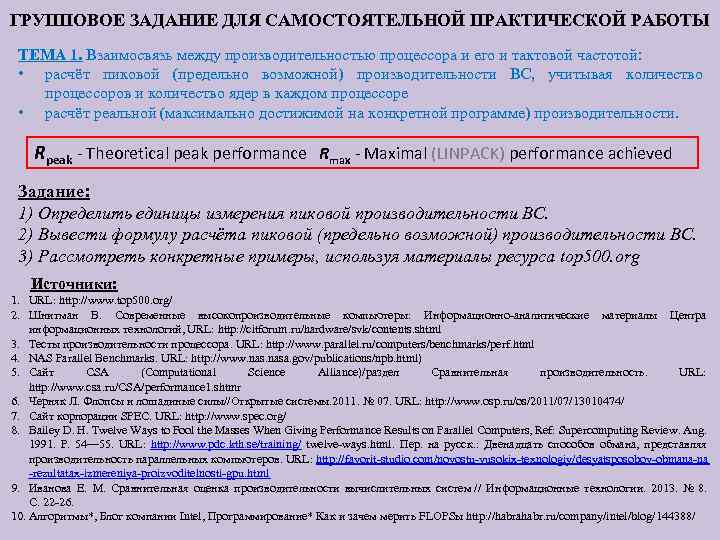

ГРУППОВОЕ ЗАДАНИЕ ДЛЯ САМОСТОЯТЕЛЬНОЙ ПРАКТИЧЕСКОЙ РАБОТЫ ТЕМА 1. Взаимосвязь между производительностью процессора и его и тактовой частотой: • расчёт пиковой (предельно возможной) производительности ВС, учитывая количество процессоров и количество ядер в каждом процессоре • расчёт реальной (максимально достижимой на конкретной программе) производительности. Rpeak - Theoretical peak performance Rmax - Maximal (LINPACK) performance achieved Задание: 1) Определить единицы измерения пиковой производительности ВС. 2) Вывести формулу расчёта пиковой (предельно возможной) производительности ВС. 3) Рассмотреть конкретные примеры, используя материалы ресурса top 500. org Источники: 1. URL: http: //www. top 500. org/ 2. Шнитман В. Современные высокопроизводительные компьютеры: Информационно-аналитические материалы Центра информационных технологий, URL: http: //citforum. ru/hardware/svk/contents. shtml 3. Тесты производительности процессора. URL: http: //www. parallel. ru/computers/benchmarks/perf. html 4. NAS Parallel Benchmarks. URL: http: //www. nasa. gov/publications/npb. html) 5. Сайт CSA (Computational Science Alliance)/раздел Сравнительная производительность. URL: http: //www. csa. ru/CSA/performance 1. shtmr 6. Черняк Л. Флопсы и лошадиные силы//Открытые системы. 2011. № 07. URL: http: //www. osp. ru/os/2011/07/13010474/ 7. Сайт корпорации SPEC. URL: http: //www. spec. org/ 8. Bailey D. H. Twelve Ways to Fool the Masses When Giving Performance Results on Parallel Computers, Ref: Supercomputing Review. Aug. 1991. P. 54— 55. URL: http: //www. pdc. kth. se/training/ twelve-ways. html. Пер. на русск. : Двенадцать способов обмана, представляя производительность параллельных компьютеров. URL: http: //favorit-studio. com/novostu-vusokix-texnologiy/desyatsposobov-obmana-na -rezultatax-izmereniya-proizvoditelnosti-gpu. html 9. Иванова Е. М. Сравнительная оценка производительности вычислительных систем // Информационные технологии. 2013. № 8. С. 22 -26. 10. Алгоритмы*, Блог компании Intel, Программирование* Как и зачем мерить FLOPSы http: //habrahabr. ru/company/intel/blog/144388/

ГРУППОВОЕ ЗАДАНИЕ ДЛЯ САМОСТОЯТЕЛЬНОЙ ПРАКТИЧЕСКОЙ РАБОТЫ ТЕМА 1. Взаимосвязь между производительностью процессора и его и тактовой частотой: • расчёт пиковой (предельно возможной) производительности ВС, учитывая количество процессоров и количество ядер в каждом процессоре • расчёт реальной (максимально достижимой на конкретной программе) производительности. Rpeak - Theoretical peak performance Rmax - Maximal (LINPACK) performance achieved Задание: 1) Определить единицы измерения пиковой производительности ВС. 2) Вывести формулу расчёта пиковой (предельно возможной) производительности ВС. 3) Рассмотреть конкретные примеры, используя материалы ресурса top 500. org Источники: 1. URL: http: //www. top 500. org/ 2. Шнитман В. Современные высокопроизводительные компьютеры: Информационно-аналитические материалы Центра информационных технологий, URL: http: //citforum. ru/hardware/svk/contents. shtml 3. Тесты производительности процессора. URL: http: //www. parallel. ru/computers/benchmarks/perf. html 4. NAS Parallel Benchmarks. URL: http: //www. nasa. gov/publications/npb. html) 5. Сайт CSA (Computational Science Alliance)/раздел Сравнительная производительность. URL: http: //www. csa. ru/CSA/performance 1. shtmr 6. Черняк Л. Флопсы и лошадиные силы//Открытые системы. 2011. № 07. URL: http: //www. osp. ru/os/2011/07/13010474/ 7. Сайт корпорации SPEC. URL: http: //www. spec. org/ 8. Bailey D. H. Twelve Ways to Fool the Masses When Giving Performance Results on Parallel Computers, Ref: Supercomputing Review. Aug. 1991. P. 54— 55. URL: http: //www. pdc. kth. se/training/ twelve-ways. html. Пер. на русск. : Двенадцать способов обмана, представляя производительность параллельных компьютеров. URL: http: //favorit-studio. com/novostu-vusokix-texnologiy/desyatsposobov-obmana-na -rezultatax-izmereniya-proizvoditelnosti-gpu. html 9. Иванова Е. М. Сравнительная оценка производительности вычислительных систем // Информационные технологии. 2013. № 8. С. 22 -26. 10. Алгоритмы*, Блог компании Intel, Программирование* Как и зачем мерить FLOPSы http: //habrahabr. ru/company/intel/blog/144388/

ПОВЫШЕНИЕ ПРОИЗВОДИТЕЛЬНОСТИ ВС путём совершенствование архитектуры и распараллеливание вычислений, т. е. создание ВС Многоуровневая архитектура ВС

ПОВЫШЕНИЕ ПРОИЗВОДИТЕЛЬНОСТИ ВС путём совершенствование архитектуры и распараллеливание вычислений, т. е. создание ВС Многоуровневая архитектура ВС

Совершенствование архитектуры ВС Совершенствовать ВС с целью улучшения технико-эксплуатационных характеристик (быстродействия) можно на каждом уровне архитектуры на физическом уровне: • совершенствование технологии производства кремниевых ИС, • использование новых материалов (новой элементной базы): полимеры, оптика, органические молекулы… • использование новых условий эксплуатации – сверхпроводимость при сверхнизких температурах

Совершенствование архитектуры ВС Совершенствовать ВС с целью улучшения технико-эксплуатационных характеристик (быстродействия) можно на каждом уровне архитектуры на физическом уровне: • совершенствование технологии производства кремниевых ИС, • использование новых материалов (новой элементной базы): полимеры, оптика, органические молекулы… • использование новых условий эксплуатации – сверхпроводимость при сверхнизких температурах

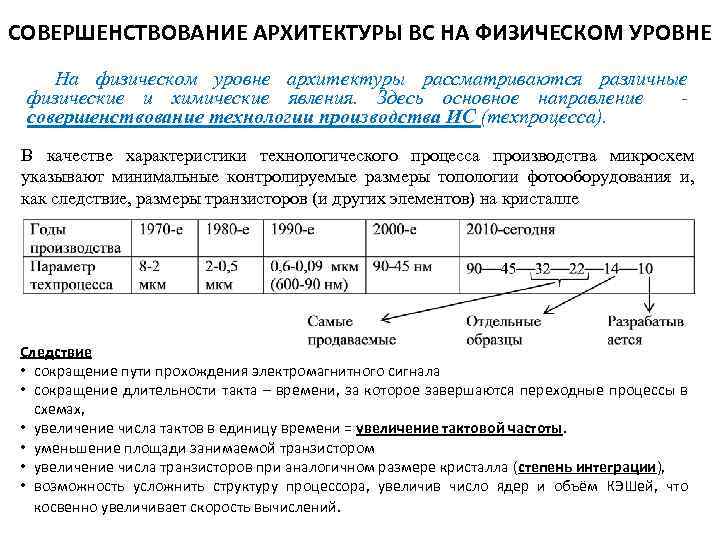

СОВЕРШЕНСТВОВАНИЕ АРХИТЕКТУРЫ ВС НА ФИЗИЧЕСКОМ УРОВНЕ На физическом уровне архитектуры рассматриваются различные физические и химические явления. Здесь основное направление - совершенствование технологии производства ИС (техпроцесса). В качестве характеристики технологического процесса производства микросхем указывают минимальные контролируемые размеры топологии фотооборудования и, как следствие, размеры транзисторов (и других элементов) на кристалле Следствие • сокращение пути прохождения электромагнитного сигнала • сокращение длительности такта – времени, за которое завершаются переходные процессы в схемах, • увеличение числа тактов в единицу времени = увеличение тактовой частоты. • уменьшение площади занимаемой транзистором • увеличение числа транзисторов при аналогичном размере кристалла (степень интеграции), • возможность усложнить структуру процессора, увеличив число ядер и объём КЭШей, что косвенно увеличивает скорость вычислений.

СОВЕРШЕНСТВОВАНИЕ АРХИТЕКТУРЫ ВС НА ФИЗИЧЕСКОМ УРОВНЕ На физическом уровне архитектуры рассматриваются различные физические и химические явления. Здесь основное направление - совершенствование технологии производства ИС (техпроцесса). В качестве характеристики технологического процесса производства микросхем указывают минимальные контролируемые размеры топологии фотооборудования и, как следствие, размеры транзисторов (и других элементов) на кристалле Следствие • сокращение пути прохождения электромагнитного сигнала • сокращение длительности такта – времени, за которое завершаются переходные процессы в схемах, • увеличение числа тактов в единицу времени = увеличение тактовой частоты. • уменьшение площади занимаемой транзистором • увеличение числа транзисторов при аналогичном размере кристалла (степень интеграции), • возможность усложнить структуру процессора, увеличив число ядер и объём КЭШей, что косвенно увеличивает скорость вычислений.

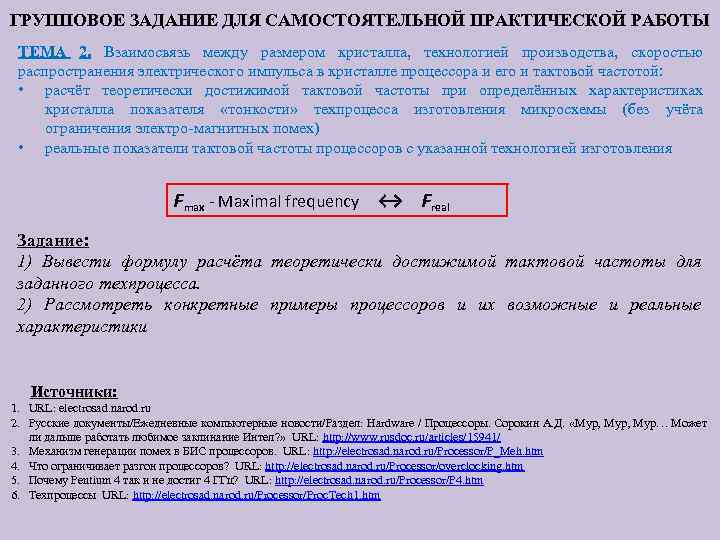

ГРУППОВОЕ ЗАДАНИЕ ДЛЯ САМОСТОЯТЕЛЬНОЙ ПРАКТИЧЕСКОЙ РАБОТЫ ТЕМА 2. Взаимосвязь между размером кристалла, технологией производства, скоростью распространения электрического импульса в кристалле процессора и его и тактовой частотой: • расчёт теоретически достижимой тактовой частоты при определённых характеристиках кристалла показателя «тонкости» техпроцесса изготовления микросхемы (без учёта ограничения электро-магнитных помех) • реальные показатели тактовой частоты процессоров с указанной технологией изготовления Fmax - Maximal frequency ↔ Freal Задание: 1) Вывести формулу расчёта теоретически достижимой тактовой частоты для заданного техпроцесса. 2) Рассмотреть конкретные примеры процессоров и их возможные и реальные характеристики Источники: 1. URL: electrosad. narod. ru 2. Русские документы/Ежедневные компьютерные новости/Раздел: Hardware / Процессоры. Сорокин А. Д. «Мур, Мур… Может ли дальше работать любимое заклинание Интел? » URL: http: //www. rusdoc. ru/articles/15941/ 3. Механизм генерации помех в БИС процессоров. URL: http: //electrosad. narod. ru/Processor/P_Meh. htm 4. Что ограничивает разгон процессоров? URL: http: //electrosad. narod. ru/Processor/overclocking. htm 5. Почему Pentium 4 так и не достиг 4 ГГц? URL: http: //electrosad. narod. ru/Processor/P 4. htm 6. Техпроцессы URL: http: //electrosad. narod. ru/Processor/Proc. Tech 1. htm

ГРУППОВОЕ ЗАДАНИЕ ДЛЯ САМОСТОЯТЕЛЬНОЙ ПРАКТИЧЕСКОЙ РАБОТЫ ТЕМА 2. Взаимосвязь между размером кристалла, технологией производства, скоростью распространения электрического импульса в кристалле процессора и его и тактовой частотой: • расчёт теоретически достижимой тактовой частоты при определённых характеристиках кристалла показателя «тонкости» техпроцесса изготовления микросхемы (без учёта ограничения электро-магнитных помех) • реальные показатели тактовой частоты процессоров с указанной технологией изготовления Fmax - Maximal frequency ↔ Freal Задание: 1) Вывести формулу расчёта теоретически достижимой тактовой частоты для заданного техпроцесса. 2) Рассмотреть конкретные примеры процессоров и их возможные и реальные характеристики Источники: 1. URL: electrosad. narod. ru 2. Русские документы/Ежедневные компьютерные новости/Раздел: Hardware / Процессоры. Сорокин А. Д. «Мур, Мур… Может ли дальше работать любимое заклинание Интел? » URL: http: //www. rusdoc. ru/articles/15941/ 3. Механизм генерации помех в БИС процессоров. URL: http: //electrosad. narod. ru/Processor/P_Meh. htm 4. Что ограничивает разгон процессоров? URL: http: //electrosad. narod. ru/Processor/overclocking. htm 5. Почему Pentium 4 так и не достиг 4 ГГц? URL: http: //electrosad. narod. ru/Processor/P 4. htm 6. Техпроцессы URL: http: //electrosad. narod. ru/Processor/Proc. Tech 1. htm

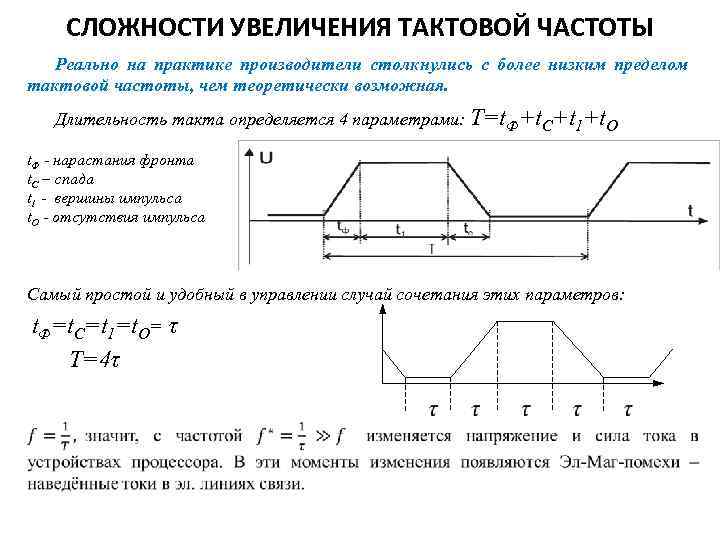

СЛОЖНОСТИ УВЕЛИЧЕНИЯ ТАКТОВОЙ ЧАСТОТЫ Реально на практике производители столкнулись с более низким пределом тактовой частоты, чем теоретически возможная. Длительность такта определяется 4 параметрами: T=t. Ф+t. С+t 1+t. О t. Ф - нарастания фронта t. С – спада t 1 - вершины импульса t. О - отсутствия импульса Самый простой и удобный в управлении случай сочетания этих параметров: t. Ф=t. С=t 1=t. О= τ T=4τ

СЛОЖНОСТИ УВЕЛИЧЕНИЯ ТАКТОВОЙ ЧАСТОТЫ Реально на практике производители столкнулись с более низким пределом тактовой частоты, чем теоретически возможная. Длительность такта определяется 4 параметрами: T=t. Ф+t. С+t 1+t. О t. Ф - нарастания фронта t. С – спада t 1 - вершины импульса t. О - отсутствия импульса Самый простой и удобный в управлении случай сочетания этих параметров: t. Ф=t. С=t 1=t. О= τ T=4τ

СЛОЖНОСТИ УВЕЛИЧЕНИЯ ТАКТОВОЙ ЧАСТОТЫ Частоты помех значительно превосходят тактовую частоту fпомех= f*>>f. Они относительно просто устранялись широкополосными частотными фильтрами на корпусе процессора и в системной плате, гасящими частотные колебания в техпроцессе до 0, 013 мкм (130 нм). При дальнейшем совершенствовании техпроцесса увеличиваются и высокочастотные помехи, которые очень тяжело погасить и большая их часть (ВЧ и СВЧ), остается в процессоре. Реальная мощность генерируемых процессором помех в выделяемой процессором теплоте составляет 25 -50%. На техпроцессах 45 и 32 нм не только растет высокочастотная граница помех, но и доля их мощности остающаяся в процессоре увеличивается с каждым шагом. Что видно из табл. справа. [www. electrosad. ru/] *-характеризует во сколько раз потребляемая процессором мощность меньше выделяемой мощности на максимальной тактовой частоте определяемой теоретически допустимым быстродействием.

СЛОЖНОСТИ УВЕЛИЧЕНИЯ ТАКТОВОЙ ЧАСТОТЫ Частоты помех значительно превосходят тактовую частоту fпомех= f*>>f. Они относительно просто устранялись широкополосными частотными фильтрами на корпусе процессора и в системной плате, гасящими частотные колебания в техпроцессе до 0, 013 мкм (130 нм). При дальнейшем совершенствовании техпроцесса увеличиваются и высокочастотные помехи, которые очень тяжело погасить и большая их часть (ВЧ и СВЧ), остается в процессоре. Реальная мощность генерируемых процессором помех в выделяемой процессором теплоте составляет 25 -50%. На техпроцессах 45 и 32 нм не только растет высокочастотная граница помех, но и доля их мощности остающаяся в процессоре увеличивается с каждым шагом. Что видно из табл. справа. [www. electrosad. ru/] *-характеризует во сколько раз потребляемая процессором мощность меньше выделяемой мощности на максимальной тактовой частоте определяемой теоретически допустимым быстродействием.

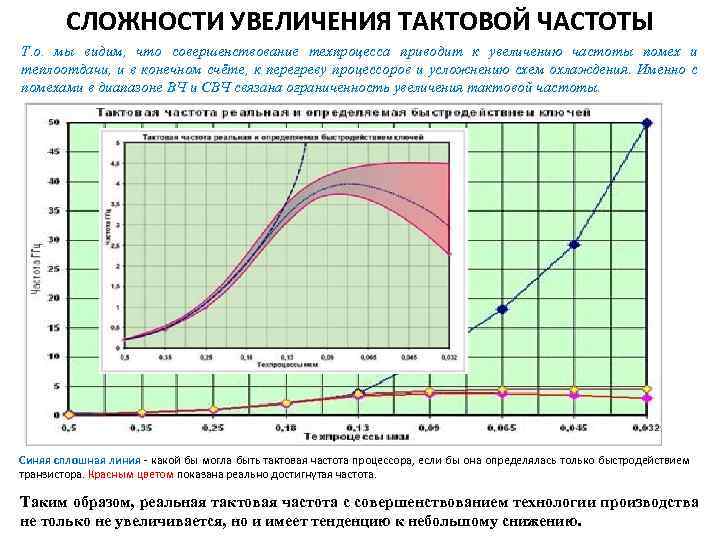

СЛОЖНОСТИ УВЕЛИЧЕНИЯ ТАКТОВОЙ ЧАСТОТЫ Т. о. мы видим, что совершенствование техпроцесса приводит к увеличению частоты помех и теплоотдачи, и в конечном счёте, к перегреву процессоров и усложнению схем охлаждения. Именно с помехами в диапазоне ВЧ и СВЧ связана ограниченность увеличения тактовой частоты. . Cиняя сплошная линия - какой бы могла быть тактовая частота процессора, если бы она определялась только быстродействием транзистора. Красным цветом показана реально достигнутая частота. Таким образом, реальная тактовая частота с совершенствованием технологии производства не только не увеличивается, но и имеет тенденцию к небольшому снижению.

СЛОЖНОСТИ УВЕЛИЧЕНИЯ ТАКТОВОЙ ЧАСТОТЫ Т. о. мы видим, что совершенствование техпроцесса приводит к увеличению частоты помех и теплоотдачи, и в конечном счёте, к перегреву процессоров и усложнению схем охлаждения. Именно с помехами в диапазоне ВЧ и СВЧ связана ограниченность увеличения тактовой частоты. . Cиняя сплошная линия - какой бы могла быть тактовая частота процессора, если бы она определялась только быстродействием транзистора. Красным цветом показана реально достигнутая частота. Таким образом, реальная тактовая частота с совершенствованием технологии производства не только не увеличивается, но и имеет тенденцию к небольшому снижению.

TOP 10 Sites for June 2015 Rank Site 1 2 3 4 5 6 7 System Rmax Rpeak (TFlop/s) National Super Computer Center Tianhe-2 (Milky. Way-2) - TH-IVB-FEP Cluster, Intel Xeon E 5 3, 120, 000 33, 862. 7 54, 902. 4 in Guangzhou China -2692 12 C 2. 200 GHz, TH Express-2, Intel Xeon Phi 31 S 1 P NUDT DOE/SC/Oak Ridge National Titan - Cray XK 7 , Opteron 6274 16 C 2. 200 GHz, Cray 560, 640 17, 590. 0 27, 112. 5 Laboratory United States Gemini interconnect, NVIDIA K 20 x Cray Inc. DOE/NNSA/LLNL United States Sequoia - Blue. Gene/Q, Power BQC 16 C 1. 60 GHz, Custom IBM RIKEN Advanced Institute for K computer, SPARC 64 VIIIfx 2. 0 GHz, Tofu interconnect Computational Science (AICS) Fujitsu Japan DOE/SC/Argonne National Mira - Blue. Gene/Q, Power BQC 16 C 1. 60 GHz, Custom IBM Laboratory United States Swiss National Supercomputing Piz Daint - Cray XC 30, Xeon E 5 -2670 8 C 2. 600 GHz, Aries Centre (CSCS) Switzerland interconnect , NVIDIA K 20 x Cray Inc. King Abdullah University of Science and Technology Saudi Arabia Cores Power (k. W) 17, 808 8, 209 1, 572, 864 17, 173. 2 20, 132. 7 7, 890 705, 024 10, 510. 0 11, 280. 4 12, 660 786, 432 8, 586. 6 10, 066. 3 3, 945 115, 984 6, 271. 0 7, 788. 9 2, 325 Shaheen II - Cray XC 40, Xeon E 5 -2698 v 3 16 C 2. 3 GHz, Aries 196, 608 5, 537. 0 interconnect Cray Inc. 7, 235. 2 2, 834 Реальная тактовая частота с совершенствованием технологии производства не только не увеличивается, но и имеет тенденцию к небольшому снижению

TOP 10 Sites for June 2015 Rank Site 1 2 3 4 5 6 7 System Rmax Rpeak (TFlop/s) National Super Computer Center Tianhe-2 (Milky. Way-2) - TH-IVB-FEP Cluster, Intel Xeon E 5 3, 120, 000 33, 862. 7 54, 902. 4 in Guangzhou China -2692 12 C 2. 200 GHz, TH Express-2, Intel Xeon Phi 31 S 1 P NUDT DOE/SC/Oak Ridge National Titan - Cray XK 7 , Opteron 6274 16 C 2. 200 GHz, Cray 560, 640 17, 590. 0 27, 112. 5 Laboratory United States Gemini interconnect, NVIDIA K 20 x Cray Inc. DOE/NNSA/LLNL United States Sequoia - Blue. Gene/Q, Power BQC 16 C 1. 60 GHz, Custom IBM RIKEN Advanced Institute for K computer, SPARC 64 VIIIfx 2. 0 GHz, Tofu interconnect Computational Science (AICS) Fujitsu Japan DOE/SC/Argonne National Mira - Blue. Gene/Q, Power BQC 16 C 1. 60 GHz, Custom IBM Laboratory United States Swiss National Supercomputing Piz Daint - Cray XC 30, Xeon E 5 -2670 8 C 2. 600 GHz, Aries Centre (CSCS) Switzerland interconnect , NVIDIA K 20 x Cray Inc. King Abdullah University of Science and Technology Saudi Arabia Cores Power (k. W) 17, 808 8, 209 1, 572, 864 17, 173. 2 20, 132. 7 7, 890 705, 024 10, 510. 0 11, 280. 4 12, 660 786, 432 8, 586. 6 10, 066. 3 3, 945 115, 984 6, 271. 0 7, 788. 9 2, 325 Shaheen II - Cray XC 40, Xeon E 5 -2698 v 3 16 C 2. 3 GHz, Aries 196, 608 5, 537. 0 interconnect Cray Inc. 7, 235. 2 2, 834 Реальная тактовая частота с совершенствованием технологии производства не только не увеличивается, но и имеет тенденцию к небольшому снижению

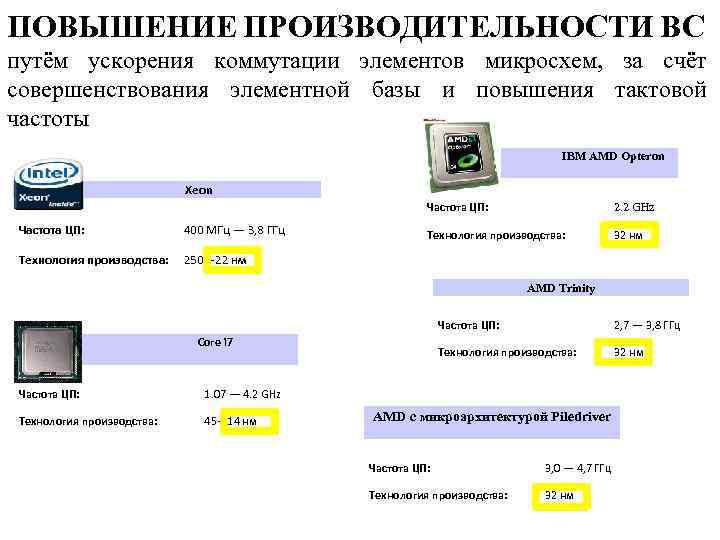

ПОВЫШЕНИЕ ПРОИЗВОДИТЕЛЬНОСТИ ВС путём ускорения коммутации элементов микросхем, за счёт совершенствования элементной базы и повышения тактовой частоты IBM AMD Opteron Xeon Частота ЦП: 400 МГц — 3, 8 ГГц Технология производства: 2. 2 GHz Технология производства: 32 нм 250— 22 нм AMD Trinity Частота ЦП: Технология производства: Core i 7 Частота ЦП: 45— 14 нм 32 нм 1. 07 — 4. 2 GHz Технология производства: 2, 7 — 3, 8 ГГц AMD с микроархитектурой Piledriver Частота ЦП: 3, 0 — 4, 7 ГГц Технология производства: 32 нм

ПОВЫШЕНИЕ ПРОИЗВОДИТЕЛЬНОСТИ ВС путём ускорения коммутации элементов микросхем, за счёт совершенствования элементной базы и повышения тактовой частоты IBM AMD Opteron Xeon Частота ЦП: 400 МГц — 3, 8 ГГц Технология производства: 2. 2 GHz Технология производства: 32 нм 250— 22 нм AMD Trinity Частота ЦП: Технология производства: Core i 7 Частота ЦП: 45— 14 нм 32 нм 1. 07 — 4. 2 GHz Технология производства: 2, 7 — 3, 8 ГГц AMD с микроархитектурой Piledriver Частота ЦП: 3, 0 — 4, 7 ГГц Технология производства: 32 нм

Совершенствание архитектуры ВС Совершенствовать ВС с целью улучшения технико-эксплуатационных характеристик (быстродействия) можно на каждом уровне архитектуры На логическом уровне: • создание новых схемотехнических решений (варианты КМОПтехнологий) • оптимизация временных диаграмм логических сигналов (сокращение переходных процессов)

Совершенствание архитектуры ВС Совершенствовать ВС с целью улучшения технико-эксплуатационных характеристик (быстродействия) можно на каждом уровне архитектуры На логическом уровне: • создание новых схемотехнических решений (варианты КМОПтехнологий) • оптимизация временных диаграмм логических сигналов (сокращение переходных процессов)

ВАРИАНТ ЗАДАНИЯ ДЛЯ ДОМАШНЕЙ РАБОТЫ ТЕМА 1. Современные схемотехнические решения для микросхем процессоров/памяти: Примерное содержание • новые технологии ─ широко распространенные ─ уникальные разработки ─ проекты будущего • сравнение с ранее используемыми • примеры микросхем

ВАРИАНТ ЗАДАНИЯ ДЛЯ ДОМАШНЕЙ РАБОТЫ ТЕМА 1. Современные схемотехнические решения для микросхем процессоров/памяти: Примерное содержание • новые технологии ─ широко распространенные ─ уникальные разработки ─ проекты будущего • сравнение с ранее используемыми • примеры микросхем

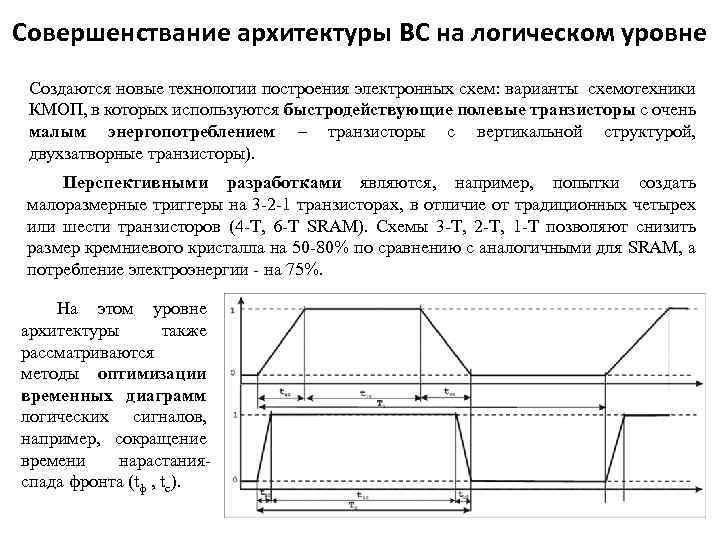

Совершенствание архитектуры ВС на логическом уровне Создаются новые технологии построения электронных схем: варианты схемотехники КМОП, в которых используются быстродействующие полевые транзисторы с очень малым энергопотреблением – транзисторы с вертикальной структурой, двухзатворные транзисторы). Перспективными разработками являются, например, попытки создать малоразмерные триггеры на 3 -2 -1 транзисторах, в отличие от традиционных четырех или шести транзисторов (4 -Т, 6 -Т SRAM). Схемы 3 -Т, 2 -Т, 1 -Т позволяют снизить размер кремниевого кристалла на 50 -80% по сравнению с аналогичными для SRAM, а потребление электроэнергии - на 75%. На этом уровне архитектуры также рассматриваются методы оптимизации временных диаграмм логических сигналов, например, сокращение времени нарастанияспада фронта (tф , tс).

Совершенствание архитектуры ВС на логическом уровне Создаются новые технологии построения электронных схем: варианты схемотехники КМОП, в которых используются быстродействующие полевые транзисторы с очень малым энергопотреблением – транзисторы с вертикальной структурой, двухзатворные транзисторы). Перспективными разработками являются, например, попытки создать малоразмерные триггеры на 3 -2 -1 транзисторах, в отличие от традиционных четырех или шести транзисторов (4 -Т, 6 -Т SRAM). Схемы 3 -Т, 2 -Т, 1 -Т позволяют снизить размер кремниевого кристалла на 50 -80% по сравнению с аналогичными для SRAM, а потребление электроэнергии - на 75%. На этом уровне архитектуры также рассматриваются методы оптимизации временных диаграмм логических сигналов, например, сокращение времени нарастанияспада фронта (tф , tс).

Совершенствание архитектуры ВС Совершенствовать ВС с целью улучшения технико-эксплуатационных характеристик (быстродействия) можно на каждом уровне архитектуры на микроархитектурном уровне: совершенствование микросхем процессоров и памяти, организация взаимодействия ЦП и ОП через многоуровневую КЭШ)

Совершенствание архитектуры ВС Совершенствовать ВС с целью улучшения технико-эксплуатационных характеристик (быстродействия) можно на каждом уровне архитектуры на микроархитектурном уровне: совершенствование микросхем процессоров и памяти, организация взаимодействия ЦП и ОП через многоуровневую КЭШ)

Совершенствание архитектуры ВС Совершенствовать ВС с целью улучшения технико-эксплуатационных характеристик (быстродействия) можно на каждом уровне архитектуры на уровне микропрограмм: совершенствование алгоритмов выполнения машинных команд, увеличение числа микроопераций для одной команды с глубокой конвейеризацией микроопераций

Совершенствание архитектуры ВС Совершенствовать ВС с целью улучшения технико-эксплуатационных характеристик (быстродействия) можно на каждом уровне архитектуры на уровне микропрограмм: совершенствование алгоритмов выполнения машинных команд, увеличение числа микроопераций для одной команды с глубокой конвейеризацией микроопераций

ВАРИАНТ ЗАДАНИЯ ДЛЯ ДОМАШНЕЙ РАБОТЫ ТЕМА 2. Совершенствание архитектуры ВС на уровне микропрограмм Примерное содержание • понятие об уровне микропрограмм • новые технологии ─ широко распространенные ─ уникальные разработки ─ проекты будущего • сравнение с ранее используемыми • примеры реализации

ВАРИАНТ ЗАДАНИЯ ДЛЯ ДОМАШНЕЙ РАБОТЫ ТЕМА 2. Совершенствание архитектуры ВС на уровне микропрограмм Примерное содержание • понятие об уровне микропрограмм • новые технологии ─ широко распространенные ─ уникальные разработки ─ проекты будущего • сравнение с ранее используемыми • примеры реализации

Совершенствание архитектуры ВС Совершенствовать ВС с целью улучшения технико-эксплуатационных характеристик (быстродействия) можно на каждом уровне архитектуры на уровне системы команд: расширение системы команд за счёт добавления новых типов инструкций, аппаратная и программная поддержка быстрых (векторных операций)

Совершенствание архитектуры ВС Совершенствовать ВС с целью улучшения технико-эксплуатационных характеристик (быстродействия) можно на каждом уровне архитектуры на уровне системы команд: расширение системы команд за счёт добавления новых типов инструкций, аппаратная и программная поддержка быстрых (векторных операций)

ВАРИАНТ ЗАДАНИЯ ДЛЯ ДОМАШНЕЙ РАБОТЫ ТЕМА 3. Совершенствание архитектуры ВС на уровне системы команд Примерное содержание • понятие об уровне системы команд • новые технологии ─ широко распространенные ─ уникальные разработки ─ проекты будущего • сравнение с ранее используемыми • примеры реализации

ВАРИАНТ ЗАДАНИЯ ДЛЯ ДОМАШНЕЙ РАБОТЫ ТЕМА 3. Совершенствание архитектуры ВС на уровне системы команд Примерное содержание • понятие об уровне системы команд • новые технологии ─ широко распространенные ─ уникальные разработки ─ проекты будущего • сравнение с ранее используемыми • примеры реализации

Совершенствание архитектуры ВС Совершенствовать ВС с целью улучшения технико-эксплуатационных характеристик (быстродействия) можно на каждом уровне архитектуры на уровне ПО: спец ПО + точная настройка существующего ПО.

Совершенствание архитектуры ВС Совершенствовать ВС с целью улучшения технико-эксплуатационных характеристик (быстродействия) можно на каждом уровне архитектуры на уровне ПО: спец ПО + точная настройка существующего ПО.

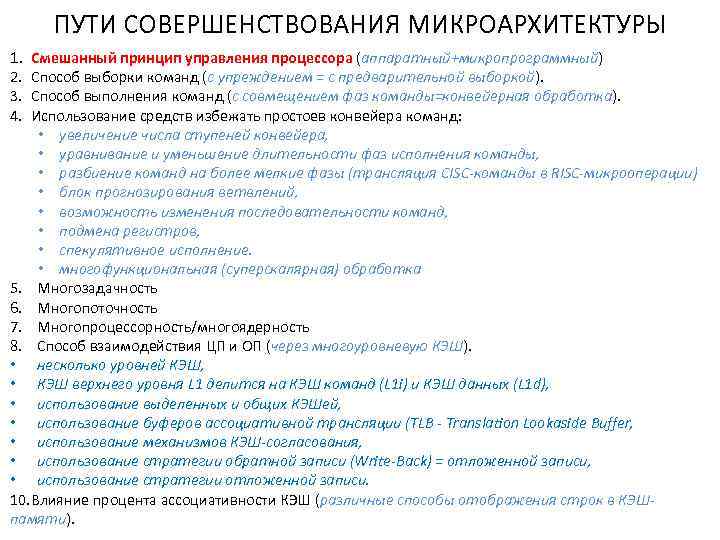

ПУТИ СОВЕРШЕНСТВОВАНИЯ МИКРОАРХИТЕКТУРЫ 1. Смешанный принцип управления процессора (аппаратный+микропрограммный) 2. Способ выборки команд (с упреждением = с предварительной выборкой). 3. Способ выполнения команд (с совмещением фаз команды=конвейерная обработка). 4. Использование средств избежать простоев конвейера команд: • увеличение числа ступеней конвейера, • уравнивание и уменьшение длительности фаз исполнения команды, • разбиение команд на более мелкие фазы (трансляция CISC-команды в RISC-микрооперации) • блок прогнозирования ветвлений, • возможность изменения последовательности команд, • подмена регистров, • спекулятивное исполнение. • многофункциональная (суперскалярная) обработка 5. Многозадачность 6. Многопоточность 7. Многопроцессорность/многоядерность 8. Способ взаимодействия ЦП и ОП (через многоуровневую КЭШ). • несколько уровней КЭШ, • КЭШ верхнего уровня L 1 делится на КЭШ команд (L 1 i) и КЭШ данных (L 1 d), • использование выделенных и общих КЭШей, • использование буферов ассоциативной трансляции (TLB - Translation Lookaside Buffer, • использование механизмов КЭШ-согласования, • использование стратегии обратной записи (Write-Back) = отложенной записи, • использование стратегии отложенной записи. 10. Влияние процента ассоциативности КЭШ (различные способы отображения строк в КЭШпамяти).

ПУТИ СОВЕРШЕНСТВОВАНИЯ МИКРОАРХИТЕКТУРЫ 1. Смешанный принцип управления процессора (аппаратный+микропрограммный) 2. Способ выборки команд (с упреждением = с предварительной выборкой). 3. Способ выполнения команд (с совмещением фаз команды=конвейерная обработка). 4. Использование средств избежать простоев конвейера команд: • увеличение числа ступеней конвейера, • уравнивание и уменьшение длительности фаз исполнения команды, • разбиение команд на более мелкие фазы (трансляция CISC-команды в RISC-микрооперации) • блок прогнозирования ветвлений, • возможность изменения последовательности команд, • подмена регистров, • спекулятивное исполнение. • многофункциональная (суперскалярная) обработка 5. Многозадачность 6. Многопоточность 7. Многопроцессорность/многоядерность 8. Способ взаимодействия ЦП и ОП (через многоуровневую КЭШ). • несколько уровней КЭШ, • КЭШ верхнего уровня L 1 делится на КЭШ команд (L 1 i) и КЭШ данных (L 1 d), • использование выделенных и общих КЭШей, • использование буферов ассоциативной трансляции (TLB - Translation Lookaside Buffer, • использование механизмов КЭШ-согласования, • использование стратегии обратной записи (Write-Back) = отложенной записи, • использование стратегии отложенной записи. 10. Влияние процента ассоциативности КЭШ (различные способы отображения строк в КЭШпамяти).

УУ МИКРООПЕРАЦИИ (операции) первичная командная информация КОП КОМАНДЫ ПРИНЦИП УПРАВЛЕНИЯ РАБОТОЙ ПРОЦЕССОРА вторичная командная информация МОП

УУ МИКРООПЕРАЦИИ (операции) первичная командная информация КОП КОМАНДЫ ПРИНЦИП УПРАВЛЕНИЯ РАБОТОЙ ПРОЦЕССОРА вторичная командная информация МОП

АППАРАТНЫЙ ПРИНЦИП УПРАВЛЕНИЯ ПРОЦЕССОРА (АВТОМАТ С ЖЁСТКОЙ ЛОГИКОЙ) структурная схема автомата

АППАРАТНЫЙ ПРИНЦИП УПРАВЛЕНИЯ ПРОЦЕССОРА (АВТОМАТ С ЖЁСТКОЙ ЛОГИКОЙ) структурная схема автомата

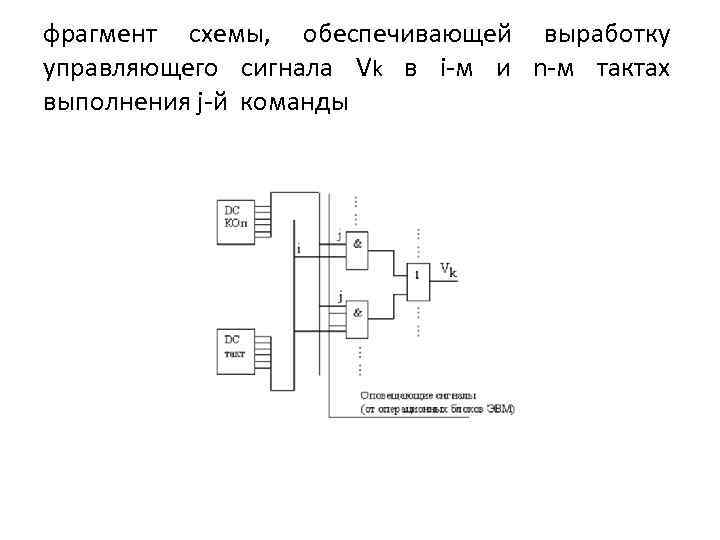

фрагмент схемы, обеспечивающей выработку управляющего сигнала Vk в i-м и n-м тактах выполнения j-й команды

фрагмент схемы, обеспечивающей выработку управляющего сигнала Vk в i-м и n-м тактах выполнения j-й команды

УУ ПРОЦЕССОРА С МИКРОПРОГРАММНОЙ ЛОГИКОЙ

УУ ПРОЦЕССОРА С МИКРОПРОГРАММНОЙ ЛОГИКОЙ

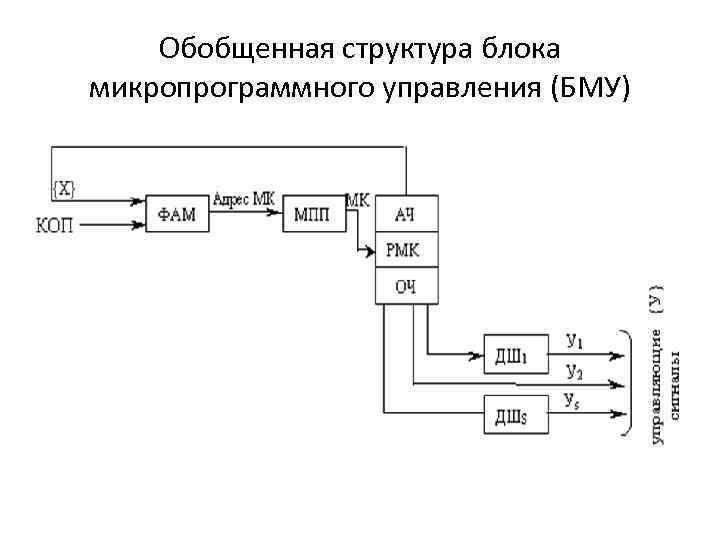

Обобщенная структура блока микропрограммного управления (БМУ)

Обобщенная структура блока микропрограммного управления (БМУ)

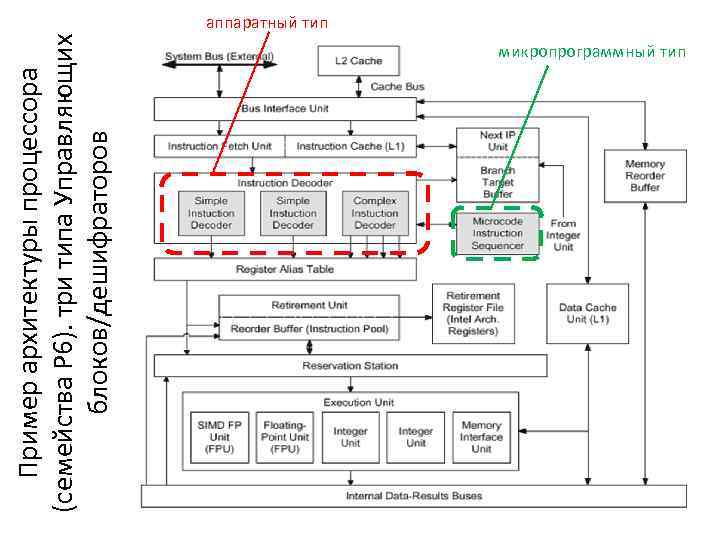

Пример архитектуры процессора (семейства P 6). три типа Управляющих блоков/дешифраторов аппаратный тип микропрограммный тип

Пример архитектуры процессора (семейства P 6). три типа Управляющих блоков/дешифраторов аппаратный тип микропрограммный тип

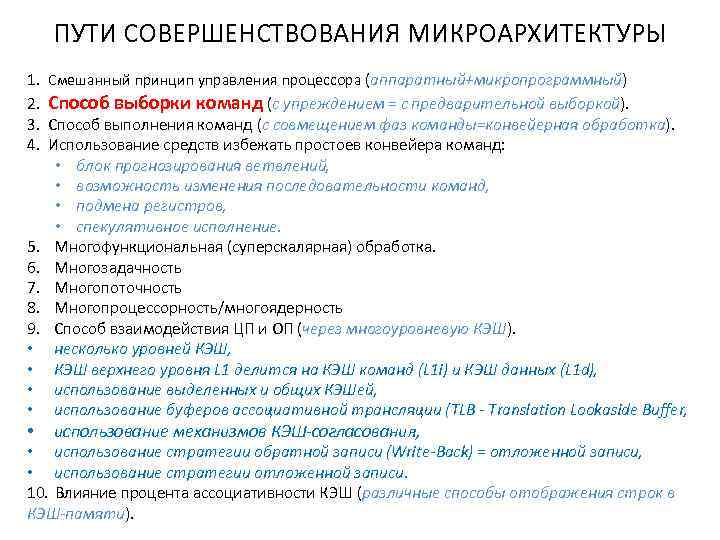

ПУТИ СОВЕРШЕНСТВОВАНИЯ МИКРОАРХИТЕКТУРЫ 1. 2. 3. 4. 5. 6. 7. 8. 9. • • • Смешанный принцип управления процессора (аппаратный+микропрограммный) Способ выборки команд (с упреждением = с предварительной выборкой). Способ выполнения команд (с совмещением фаз команды=конвейерная обработка). Использование средств избежать простоев конвейера команд: • блок прогнозирования ветвлений, • возможность изменения последовательности команд, • подмена регистров, • спекулятивное исполнение. Многофункциональная (суперскалярная) обработка. Многозадачность Многопоточность Многопроцессорность/многоядерность Способ взаимодействия ЦП и ОП (через многоуровневую КЭШ). несколько уровней КЭШ, КЭШ верхнего уровня L 1 делится на КЭШ команд (L 1 i) и КЭШ данных (L 1 d), использование выделенных и общих КЭШей, использование буферов ассоциативной трансляции (TLB - Translation Lookaside Buffer, использование механизмов КЭШ-согласования, • использование стратегии обратной записи (Write-Back) = отложенной записи, • использование стратегии отложенной записи. 10. Влияние процента ассоциативности КЭШ (различные способы отображения строк в КЭШ-памяти).

ПУТИ СОВЕРШЕНСТВОВАНИЯ МИКРОАРХИТЕКТУРЫ 1. 2. 3. 4. 5. 6. 7. 8. 9. • • • Смешанный принцип управления процессора (аппаратный+микропрограммный) Способ выборки команд (с упреждением = с предварительной выборкой). Способ выполнения команд (с совмещением фаз команды=конвейерная обработка). Использование средств избежать простоев конвейера команд: • блок прогнозирования ветвлений, • возможность изменения последовательности команд, • подмена регистров, • спекулятивное исполнение. Многофункциональная (суперскалярная) обработка. Многозадачность Многопоточность Многопроцессорность/многоядерность Способ взаимодействия ЦП и ОП (через многоуровневую КЭШ). несколько уровней КЭШ, КЭШ верхнего уровня L 1 делится на КЭШ команд (L 1 i) и КЭШ данных (L 1 d), использование выделенных и общих КЭШей, использование буферов ассоциативной трансляции (TLB - Translation Lookaside Buffer, использование механизмов КЭШ-согласования, • использование стратегии обратной записи (Write-Back) = отложенной записи, • использование стратегии отложенной записи. 10. Влияние процента ассоциативности КЭШ (различные способы отображения строк в КЭШ-памяти).

ВИДЫ ЦИКЛОВ ВЫПОЛНЕНИЯ КОМАНД Выполнение операции Выборка текущей команды время Прямой цикл выполнения команды Выборка следующей команды Обратный цикл выполнения команды Выборка следующей команды Выполнение текущей операции время Выделение устройств для анализа хода вычислений (BRANCH PREDICT UNIT) и предварительной выборки следующей команды (спекулятивно) (PREFETCH BUFFERS) позволило совместить эти фазы и сократить цикл выполнения команды, а значит, ускорить выполнение программы в целом. Выполнение операции по текущей команде Совмещённый цикл выполнения команды время

ВИДЫ ЦИКЛОВ ВЫПОЛНЕНИЯ КОМАНД Выполнение операции Выборка текущей команды время Прямой цикл выполнения команды Выборка следующей команды Обратный цикл выполнения команды Выборка следующей команды Выполнение текущей операции время Выделение устройств для анализа хода вычислений (BRANCH PREDICT UNIT) и предварительной выборки следующей команды (спекулятивно) (PREFETCH BUFFERS) позволило совместить эти фазы и сократить цикл выполнения команды, а значит, ускорить выполнение программы в целом. Выполнение операции по текущей команде Совмещённый цикл выполнения команды время

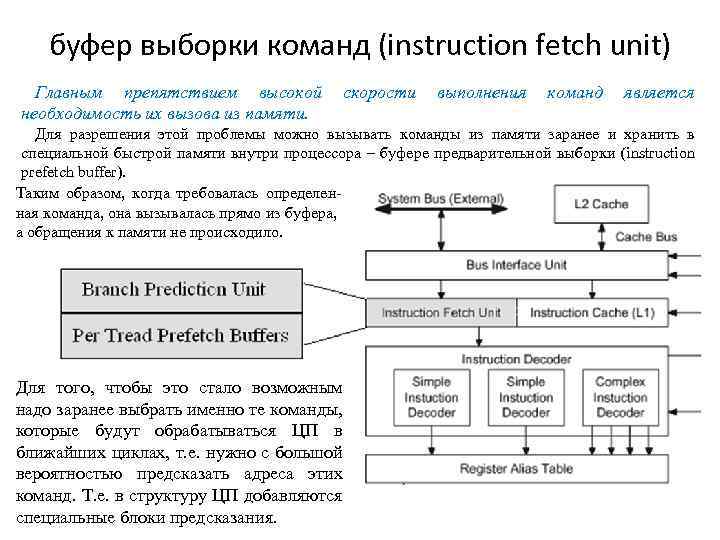

буфер выборки команд (instruction fetch unit) Главным препятствием высокой скорости выполнения команд является необходимость их вызова из памяти. Для разрешения этой проблемы можно вызывать команды из памяти заранее и хранить в специальной быстрой памяти внутри процессора – буфере предварительной выборки (instruction prefetch buffer). Таким образом, когда требовалась определенная команда, она вызывалась прямо из буфера, а обращения к памяти не происходило. Для того, чтобы это стало возможным надо заранее выбрать именно те команды, которые будут обрабатываться ЦП в ближайших циклах, т. е. нужно с большой вероятностью предсказать адреса этих команд. Т. е. в структуру ЦП добавляются специальные блоки предсказания.

буфер выборки команд (instruction fetch unit) Главным препятствием высокой скорости выполнения команд является необходимость их вызова из памяти. Для разрешения этой проблемы можно вызывать команды из памяти заранее и хранить в специальной быстрой памяти внутри процессора – буфере предварительной выборки (instruction prefetch buffer). Таким образом, когда требовалась определенная команда, она вызывалась прямо из буфера, а обращения к памяти не происходило. Для того, чтобы это стало возможным надо заранее выбрать именно те команды, которые будут обрабатываться ЦП в ближайших циклах, т. е. нужно с большой вероятностью предсказать адреса этих команд. Т. е. в структуру ЦП добавляются специальные блоки предсказания.

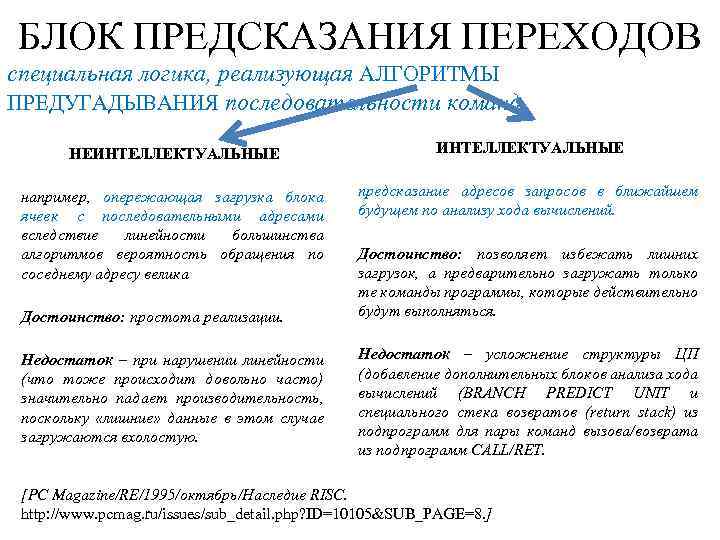

БЛОК ПРЕДСКАЗАНИЯ ПЕРЕХОДОВ специальная логика, реализующая АЛГОРИТМЫ ПРЕДУГАДЫВАНИЯ последовательности команд. НЕИНТЕЛЛЕКТУАЛЬНЫЕ например, опережающая загрузка блока ячеек с последовательными адресами вследствие линейности большинства алгоритмов вероятность обращения по соседнему адресу велика предсказание адресов запросов в ближайшем будущем по анализу хода вычислений. Достоинство: простота реализации. Недостаток – при нарушении линейности (что тоже происходит довольно часто) значительно падает производительность, поскольку «лишние» данные в этом случае загружаются вхолостую. Достоинство: позволяет избежать лишних загрузок, а предварительно загружать только те команды программы, которые действительно будут выполняться. Недостаток – усложнение структуры ЦП (добавление дополнительных блоков анализа хода вычислений (BRANCH PREDICT UNIT и специального стека возвратов (return stack) из подпрограмм для пары команд вызова/возврата из подпрограмм CALL/RET. [PC Magazine/RE/1995/октябрь/Наследие RISC. http: //www. pcmag. ru/issues/sub_detail. php? ID=10105&SUB_PAGE=8. ]

БЛОК ПРЕДСКАЗАНИЯ ПЕРЕХОДОВ специальная логика, реализующая АЛГОРИТМЫ ПРЕДУГАДЫВАНИЯ последовательности команд. НЕИНТЕЛЛЕКТУАЛЬНЫЕ например, опережающая загрузка блока ячеек с последовательными адресами вследствие линейности большинства алгоритмов вероятность обращения по соседнему адресу велика предсказание адресов запросов в ближайшем будущем по анализу хода вычислений. Достоинство: простота реализации. Недостаток – при нарушении линейности (что тоже происходит довольно часто) значительно падает производительность, поскольку «лишние» данные в этом случае загружаются вхолостую. Достоинство: позволяет избежать лишних загрузок, а предварительно загружать только те команды программы, которые действительно будут выполняться. Недостаток – усложнение структуры ЦП (добавление дополнительных блоков анализа хода вычислений (BRANCH PREDICT UNIT и специального стека возвратов (return stack) из подпрограмм для пары команд вызова/возврата из подпрограмм CALL/RET. [PC Magazine/RE/1995/октябрь/Наследие RISC. http: //www. pcmag. ru/issues/sub_detail. php? ID=10105&SUB_PAGE=8. ]

ИНТЕЛЛЕКТУАЛЬНЫЕ МЕТОДЫ ПРЕДСКАЗАНИЯ ПЕРЕХОДОВ На уровне архитектуры машинного языка в каждой точке возможно ветвление не более, чем на 2 потока (команды условной передачи управления Jxxх). простая команда да = 1 ветка 1 программы условие нет = 0 команда ветвления ветка 2 программы Существуют два основных метода предсказания переходов СТАТИЧЕСКИЙ (static) Статические методы предписывают всегда выполнять или не выполнять определенные типы переходов Например, всегда выбирать ветку по выполнению условия (ДА) ДИНАМИЧЕСКИЙ (dynamic) Динамический алгоритм оценивает за предшествующий период времени предысторию переходов, которая сохраняется в специальном буфере адреса перехода (branch target buffer — BTB; Intel Pentium, P 6). Выбирается ветка, по которой было выполнено большее число переходов. Как правило оба подхода комбинируются: для предсказания используются как динамический, так и статический методы. Последний используется в том случае, если динамическое предсказание невозможно (в таблице переходов отсутствует необходимая информация).

ИНТЕЛЛЕКТУАЛЬНЫЕ МЕТОДЫ ПРЕДСКАЗАНИЯ ПЕРЕХОДОВ На уровне архитектуры машинного языка в каждой точке возможно ветвление не более, чем на 2 потока (команды условной передачи управления Jxxх). простая команда да = 1 ветка 1 программы условие нет = 0 команда ветвления ветка 2 программы Существуют два основных метода предсказания переходов СТАТИЧЕСКИЙ (static) Статические методы предписывают всегда выполнять или не выполнять определенные типы переходов Например, всегда выбирать ветку по выполнению условия (ДА) ДИНАМИЧЕСКИЙ (dynamic) Динамический алгоритм оценивает за предшествующий период времени предысторию переходов, которая сохраняется в специальном буфере адреса перехода (branch target buffer — BTB; Intel Pentium, P 6). Выбирается ветка, по которой было выполнено большее число переходов. Как правило оба подхода комбинируются: для предсказания используются как динамический, так и статический методы. Последний используется в том случае, если динамическое предсказание невозможно (в таблице переходов отсутствует необходимая информация).

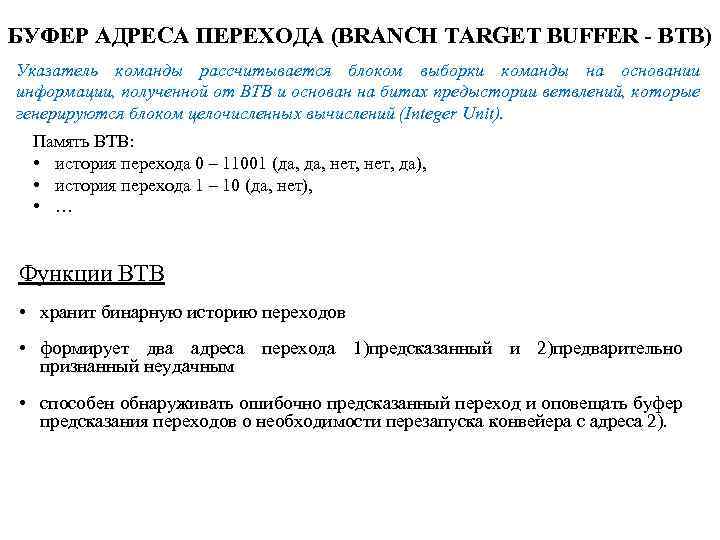

БУФЕР АДРЕСА ПЕРЕХОДА (BRANCH TARGET BUFFER - BTB) Указатель команды рассчитывается блоком выборки команды на основании информации, полученной от BTB и основан на битах предыстории ветвлений, которые генерируются блоком целочисленных вычислений (Integer Unit). Память ВТВ: • история перехода 0 – 11001 (да, нет, да), • история перехода 1 – 10 (да, нет), • … Функции ВТВ • хранит бинарную историю переходов • формирует два адреса перехода 1)предсказанный и 2)предварительно признанный неудачным • способен обнаруживать ошибочно предсказанный переход и оповещать буфер предсказания переходов о необходимости перезапуска конвейера с адреса 2).

БУФЕР АДРЕСА ПЕРЕХОДА (BRANCH TARGET BUFFER - BTB) Указатель команды рассчитывается блоком выборки команды на основании информации, полученной от BTB и основан на битах предыстории ветвлений, которые генерируются блоком целочисленных вычислений (Integer Unit). Память ВТВ: • история перехода 0 – 11001 (да, нет, да), • история перехода 1 – 10 (да, нет), • … Функции ВТВ • хранит бинарную историю переходов • формирует два адреса перехода 1)предсказанный и 2)предварительно признанный неудачным • способен обнаруживать ошибочно предсказанный переход и оповещать буфер предсказания переходов о необходимости перезапуска конвейера с адреса 2).