3-3 Оперативная память.ppt

- Количество слайдов: 63

Вычислительные системы и телекоммуникации Тема 3. Аппаратная платформа ПК оперативная память

Вычислительные системы и телекоммуникации Тема 3. Аппаратная платформа ПК оперативная память

Оперативная память n n n Общеизвестно, что производительность компьютера зависит от объема установленной оперативной памяти. «Память лишней не бывает» — этот базовый принцип, высказанный еще в конце 40 -х фон Нейманом, остается актуальным и сегодня. Поэтому на вопрос, сколько памяти нужно ставить, ответ прост — чем больше, тем лучше. Пять лет назад для рабочих ПК вполне хватало 64 -128 Мбайт оперативной памяти, теперь же нужно иметь уже как минимум 2048 Мбайт. Связано это, прежде всего, с наметившейся тенденцией смещения приложений в сторону их мультимедийности™.

Оперативная память n n n Общеизвестно, что производительность компьютера зависит от объема установленной оперативной памяти. «Память лишней не бывает» — этот базовый принцип, высказанный еще в конце 40 -х фон Нейманом, остается актуальным и сегодня. Поэтому на вопрос, сколько памяти нужно ставить, ответ прост — чем больше, тем лучше. Пять лет назад для рабочих ПК вполне хватало 64 -128 Мбайт оперативной памяти, теперь же нужно иметь уже как минимум 2048 Мбайт. Связано это, прежде всего, с наметившейся тенденцией смещения приложений в сторону их мультимедийности™.

Оперативная память n Впрочем, объем устанавливаемой оперативной памяти — это еще не все. Если несколько лет назад доминирующее положение на рынке занимала память PC 100, а позднее РС 133 SDRAM, то сейчас существует несколько различных типов памяти: DDR 333/400/533 SDRAM, DDR 2400/533/800 и уже используется память DDR 3. -1066/1333 n Поэтому актуальным становится вопрос о выборе типа устанавливаемой памяти.

Оперативная память n Впрочем, объем устанавливаемой оперативной памяти — это еще не все. Если несколько лет назад доминирующее положение на рынке занимала память PC 100, а позднее РС 133 SDRAM, то сейчас существует несколько различных типов памяти: DDR 333/400/533 SDRAM, DDR 2400/533/800 и уже используется память DDR 3. -1066/1333 n Поэтому актуальным становится вопрос о выборе типа устанавливаемой памяти.

Принципы функционирования памяти n n n Оперативная память, которая также именуется RAM-память (Random Access Memory), то есть память с произвольным доступом, используется центральным процессором для совместного хранения данных и исполняемого программного кода. Отличительной особенностью RAM-памяти является ее быстродействие, которое очень важно для современных процессоров. По принципам действия RAM-память можно разделить на динамическую и статическую. Различие между этими типами памяти заключается в принципе хранения информации. Поскольку элементарной единицей информации является бит, то оперативную память можно рассматривать как некий набор ячеек, каждая из которых может хранить один информационный бит. Различие между динамической и статической памятью заключается в конструктивных особенностях элементарных ячеек для хранения отдельных битов.

Принципы функционирования памяти n n n Оперативная память, которая также именуется RAM-память (Random Access Memory), то есть память с произвольным доступом, используется центральным процессором для совместного хранения данных и исполняемого программного кода. Отличительной особенностью RAM-памяти является ее быстродействие, которое очень важно для современных процессоров. По принципам действия RAM-память можно разделить на динамическую и статическую. Различие между этими типами памяти заключается в принципе хранения информации. Поскольку элементарной единицей информации является бит, то оперативную память можно рассматривать как некий набор ячеек, каждая из которых может хранить один информационный бит. Различие между динамической и статической памятью заключается в конструктивных особенностях элементарных ячеек для хранения отдельных битов.

Статическая память SRAM n n n В статической памяти ячейки построены на различных вариантах триггеров — транзисторных схем с двумя устойчивыми состояниями. После записи бита в такую ячейку она может пребывать в одном из этих состояний и сохранять записанный бит сколь угодно долго — необходимо только наличие питания. Отсюда и название памяти — статическая, то есть пребывающая в неизменном состоянии. Достоинством статической памяти является ее быстродействие, а недостатками — высокое энергопотребление и низкая удельная плотность данных, поскольку одна триггерная ячейка состоит из нескольких транзисторов и, следовательно, занимает немало места на кристалле. К примеру, микросхема емкостью 4 Мбит состояла бы более чем из 24 млн транзисторов, потребляя соответствующую мощность.

Статическая память SRAM n n n В статической памяти ячейки построены на различных вариантах триггеров — транзисторных схем с двумя устойчивыми состояниями. После записи бита в такую ячейку она может пребывать в одном из этих состояний и сохранять записанный бит сколь угодно долго — необходимо только наличие питания. Отсюда и название памяти — статическая, то есть пребывающая в неизменном состоянии. Достоинством статической памяти является ее быстродействие, а недостатками — высокое энергопотребление и низкая удельная плотность данных, поскольку одна триггерная ячейка состоит из нескольких транзисторов и, следовательно, занимает немало места на кристалле. К примеру, микросхема емкостью 4 Мбит состояла бы более чем из 24 млн транзисторов, потребляя соответствующую мощность.

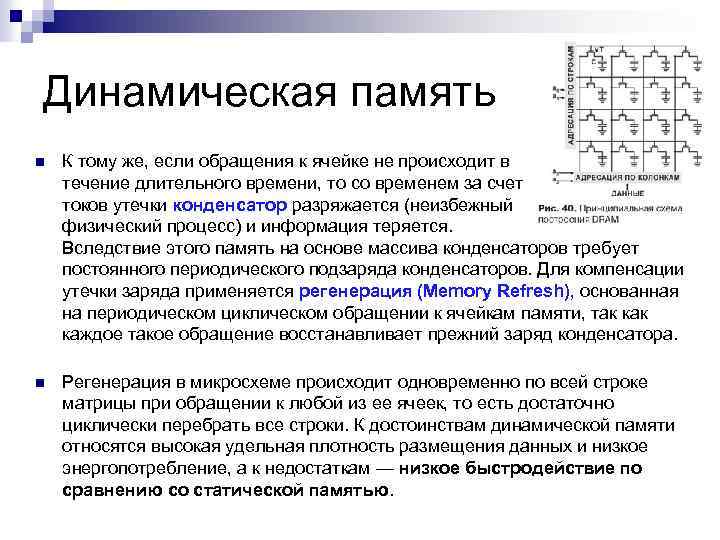

Динамическая память n К тому же, если обращения к ячейке не происходит в течение длительного времени, то со временем за счет токов утечки конденсатор разряжается (неизбежный физический процесс) и информация теряется. Вследствие этого память на основе массива конденсаторов требует постоянного периодического подзаряда конденсаторов. Для компенсации утечки заряда применяется регенерация (Memory Refresh), основанная на периодическом циклическом обращении к ячейкам памяти, так каждое такое обращение восстанавливает прежний заряд конденсатора. n Регенерация в микросхеме происходит одновременно по всей строке матрицы при обращении к любой из ее ячеек, то есть достаточно циклически перебрать все строки. К достоинствам динамической памяти относятся высокая удельная плотность размещения данных и низкое энергопотребление, а к недостаткам — низкое быстродействие по сравнению со статической памятью.

Динамическая память n К тому же, если обращения к ячейке не происходит в течение длительного времени, то со временем за счет токов утечки конденсатор разряжается (неизбежный физический процесс) и информация теряется. Вследствие этого память на основе массива конденсаторов требует постоянного периодического подзаряда конденсаторов. Для компенсации утечки заряда применяется регенерация (Memory Refresh), основанная на периодическом циклическом обращении к ячейкам памяти, так каждое такое обращение восстанавливает прежний заряд конденсатора. n Регенерация в микросхеме происходит одновременно по всей строке матрицы при обращении к любой из ее ячеек, то есть достаточно циклически перебрать все строки. К достоинствам динамической памяти относятся высокая удельная плотность размещения данных и низкое энергопотребление, а к недостаткам — низкое быстродействие по сравнению со статической памятью.

Динамическая память DRAM n n В настоящее время динамическая память DRAM (Dynamic Random Access Memory) используется в качестве оперативной памяти компьютера, а статическая память SRAM (Static Random Access Memory) — для создания высокоскоростной кэш-памяти процессора. Микросхемы динамической памяти организованы в виде квадратной матрицы , причем пересечение столбца и строки матрицы задает одну из элементарных ячеек. При обращении к той или иной ячейке памяти нужно задать адрес нужной строки и столбца.

Динамическая память DRAM n n В настоящее время динамическая память DRAM (Dynamic Random Access Memory) используется в качестве оперативной памяти компьютера, а статическая память SRAM (Static Random Access Memory) — для создания высокоскоростной кэш-памяти процессора. Микросхемы динамической памяти организованы в виде квадратной матрицы , причем пересечение столбца и строки матрицы задает одну из элементарных ячеек. При обращении к той или иной ячейке памяти нужно задать адрес нужной строки и столбца.

Динамическая память n n Задание адреса строки происходит, когда на входы матрицы памяти подается специальный стробирующий импульс RAS (Row Address Strobe), а задание адреса столбца — при подаче стробирующего импульса CAS (Column Address Strobe). При этом сигналами для выбора содержимого строки и столбца служат положительные фронты стробирующих импульсов. Импульсы RAS и CAS подаются последовательно друг за другом, причем импульс CAS всегда подается после импульса RAS, то есть сначала происходит выбор строки, а затем выбор столбца. Сам адрес строки и столбца передается по специальной мультиплексированной шине адреса MA (Multiplexed Address).

Динамическая память n n Задание адреса строки происходит, когда на входы матрицы памяти подается специальный стробирующий импульс RAS (Row Address Strobe), а задание адреса столбца — при подаче стробирующего импульса CAS (Column Address Strobe). При этом сигналами для выбора содержимого строки и столбца служат положительные фронты стробирующих импульсов. Импульсы RAS и CAS подаются последовательно друг за другом, причем импульс CAS всегда подается после импульса RAS, то есть сначала происходит выбор строки, а затем выбор столбца. Сам адрес строки и столбца передается по специальной мультиплексированной шине адреса MA (Multiplexed Address).

Динамическая память n По логике организации DRAM-памяти может быть асинхронной и синхронной. n При асинхронной организации памяти установка адреса, подача управляющих сигналов и чтение/запись данных могут выполняться в произвольные моменты времени — необходимо только соблюдение временных соотношений между этими сигналами. n Синхронная организация памяти подразумевает, что имеется внешний синхросигнал, к импульсам которого жестко привязаны моменты подачи адресов и обмена данными.

Динамическая память n По логике организации DRAM-памяти может быть асинхронной и синхронной. n При асинхронной организации памяти установка адреса, подача управляющих сигналов и чтение/запись данных могут выполняться в произвольные моменты времени — необходимо только соблюдение временных соотношений между этими сигналами. n Синхронная организация памяти подразумевает, что имеется внешний синхросигнал, к импульсам которого жестко привязаны моменты подачи адресов и обмена данными.

Асинхронная память FPM DRAM n n Существует довольно много различных вариантов динамической памяти, незначительно отличающихся друг от друга принципами доступа к данным. Обычная динамическая память DRAM уже давно не встречается — в середине 90 -х ей на смену пришла модификация динамической памяти FPM DRAM (Fast Page Mode — динамическая память с быстрым страничным доступом).

Асинхронная память FPM DRAM n n Существует довольно много различных вариантов динамической памяти, незначительно отличающихся друг от друга принципами доступа к данным. Обычная динамическая память DRAM уже давно не встречается — в середине 90 -х ей на смену пришла модификация динамической памяти FPM DRAM (Fast Page Mode — динамическая память с быстрым страничным доступом).

Асинхронная память FPM DRAM Принцип действия n Принцип действия FPM-памяти основан на предположении о последовательном доступе к данным: предполагается, что данные, к которым происходит обращение, расположены последовательно в пределах одной строки матрицы памяти. n Страницей в данном случае называется сама строка матрицы. Смысл страничного режима доступа заключается в том, что после выбора строки матрицы и удержания RAS допускается многократная установка адреса столбца, стробируемого CAS. n Такой подход позволяет выбирать последовательные данные в пределах одной строки без изменения ее адреса, то есть с одним и тем же сигналом RAS. Это позволяет ускорить блочные передачи, но только в том случае, когда весь блок данных или его часть находится внутри одной строки матрицы.

Асинхронная память FPM DRAM Принцип действия n Принцип действия FPM-памяти основан на предположении о последовательном доступе к данным: предполагается, что данные, к которым происходит обращение, расположены последовательно в пределах одной строки матрицы памяти. n Страницей в данном случае называется сама строка матрицы. Смысл страничного режима доступа заключается в том, что после выбора строки матрицы и удержания RAS допускается многократная установка адреса столбца, стробируемого CAS. n Такой подход позволяет выбирать последовательные данные в пределах одной строки без изменения ее адреса, то есть с одним и тем же сигналом RAS. Это позволяет ускорить блочные передачи, но только в том случае, когда весь блок данных или его часть находится внутри одной строки матрицы.

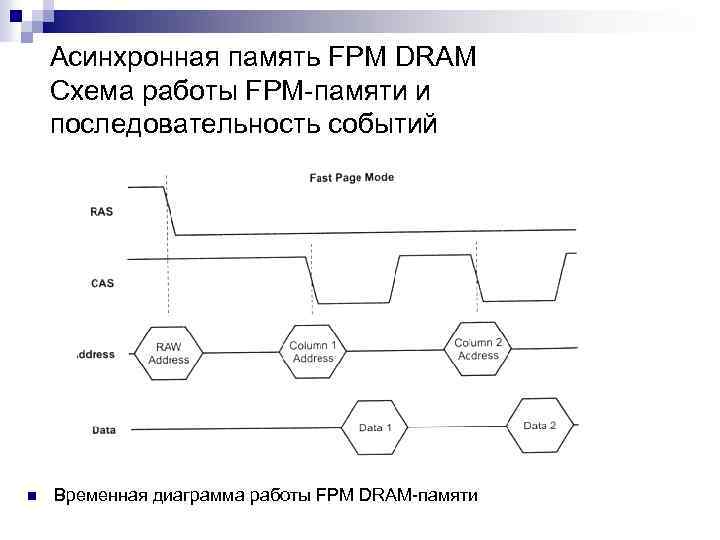

Асинхронная память FPM DRAM Схема работы FPM-памяти и последовательность событий n Временная диаграмма работы FPM DRAM-памяти

Асинхронная память FPM DRAM Схема работы FPM-памяти и последовательность событий n Временная диаграмма работы FPM DRAM-памяти

Асинхронная память EDO DRAM n Вторым типом динамической памяти (она также уже не встречается) является EDO DRAM (Extended Data Out), по сути представляющая собой несколько «продвинутый» вариант FPM-памяти. В этой памяти тоже реализована страничная схема доступа, но на выходе микросхемы памяти устанавливаются регистры-защелки данных. n При страничном режиме доступа такой тип памяти работает по принципу конвейера: содержимое выбранной ячейки удерживается в выходных регистрах-защелках, в то время как на входы матрицы уже подается адрес следующей выбираемой ячейки.

Асинхронная память EDO DRAM n Вторым типом динамической памяти (она также уже не встречается) является EDO DRAM (Extended Data Out), по сути представляющая собой несколько «продвинутый» вариант FPM-памяти. В этой памяти тоже реализована страничная схема доступа, но на выходе микросхемы памяти устанавливаются регистры-защелки данных. n При страничном режиме доступа такой тип памяти работает по принципу конвейера: содержимое выбранной ячейки удерживается в выходных регистрах-защелках, в то время как на входы матрицы уже подается адрес следующей выбираемой ячейки.

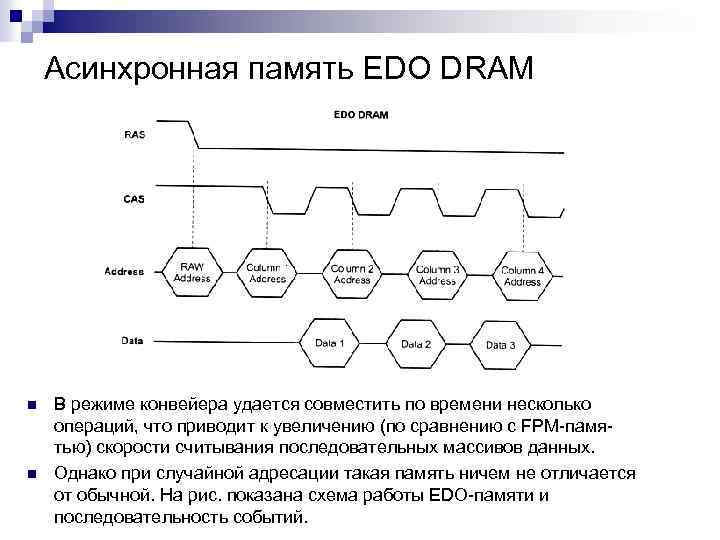

Асинхронная память EDO DRAM n n В режиме конвейера удается совместить по времени несколько операций, что приводит к увеличению (по сравнению с FPM-памятью) скорости считывания последовательных массивов данных. Однако при случайной адресации такая память ничем не отличается от обычной. На рис. показана схема работы EDO-памяти и последовательность событий.

Асинхронная память EDO DRAM n n В режиме конвейера удается совместить по времени несколько операций, что приводит к увеличению (по сравнению с FPM-памятью) скорости считывания последовательных массивов данных. Однако при случайной адресации такая память ничем не отличается от обычной. На рис. показана схема работы EDO-памяти и последовательность событий.

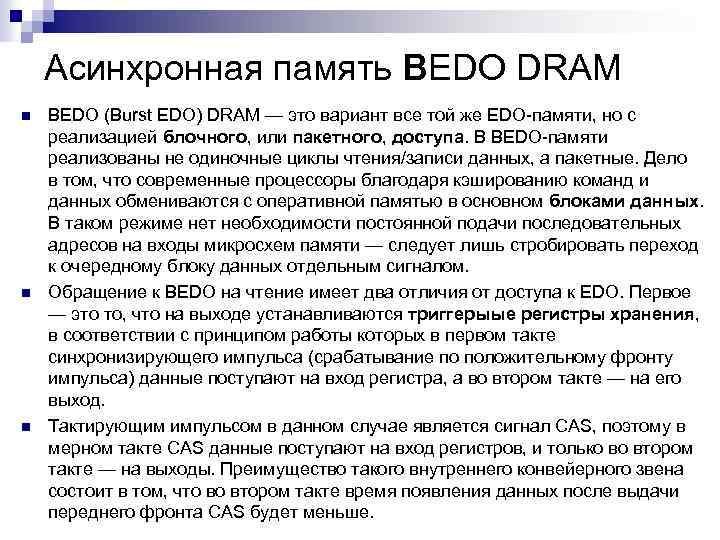

Асинхронная память BEDO DRAM n n n BEDO (Burst EDO) DRAM — это вариант все той же EDO-памяти, но с реализацией блочного, или пакетного, доступа. В BEDO-памяти реализованы не одиночные циклы чтения/записи данных, а пакетные. Дело в том, что современные процессоры благодаря кэшированию команд и данных обмениваются с оперативной памятью в основном блоками данных. В таком режиме нет необходимости постоянной подачи последовательных адресов на входы микросхем памяти — следует лишь стробировать переход к очередному блоку данных отдельным сигналом. Обращение к BEDO на чтение имеет два отличия от доступа к EDO. Первое — это то, что на выходе устанавливаются триггерыые регистры хранения, в соответствии с принципом работы которых в первом такте синхронизирующего импульса (срабатывание по положительному фронту импульса) данные поступают на вход регистра, а во втором такте — на его выход. Тактирующим импульсом в данном случае является сигнал CAS, поэтому в мерном такте CAS данные поступают на вход регистров, и только во втором такте — на выходы. Преимущество такого внутреннего конвейерного звена состоит в том, что во втором такте время появления данных после выдачи переднего фронта CAS будет меньше.

Асинхронная память BEDO DRAM n n n BEDO (Burst EDO) DRAM — это вариант все той же EDO-памяти, но с реализацией блочного, или пакетного, доступа. В BEDO-памяти реализованы не одиночные циклы чтения/записи данных, а пакетные. Дело в том, что современные процессоры благодаря кэшированию команд и данных обмениваются с оперативной памятью в основном блоками данных. В таком режиме нет необходимости постоянной подачи последовательных адресов на входы микросхем памяти — следует лишь стробировать переход к очередному блоку данных отдельным сигналом. Обращение к BEDO на чтение имеет два отличия от доступа к EDO. Первое — это то, что на выходе устанавливаются триггерыые регистры хранения, в соответствии с принципом работы которых в первом такте синхронизирующего импульса (срабатывание по положительному фронту импульса) данные поступают на вход регистра, а во втором такте — на его выход. Тактирующим импульсом в данном случае является сигнал CAS, поэтому в мерном такте CAS данные поступают на вход регистров, и только во втором такте — на выходы. Преимущество такого внутреннего конвейерного звена состоит в том, что во втором такте время появления данных после выдачи переднего фронта CAS будет меньше.

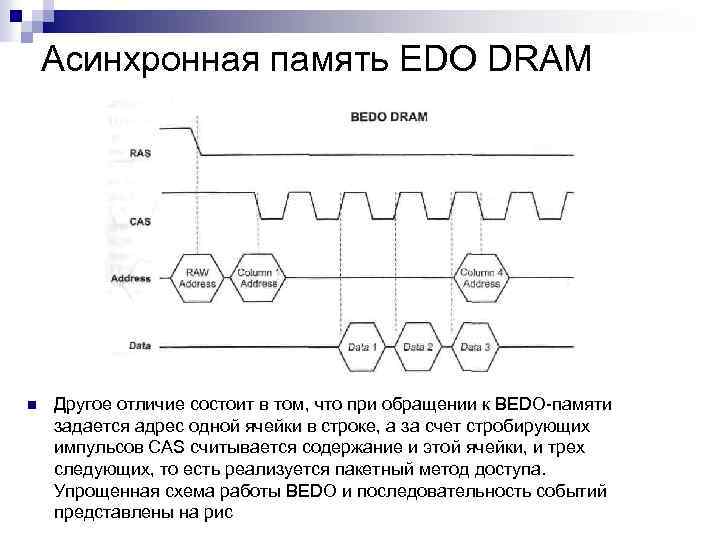

Асинхронная память EDO DRAM n Другое отличие состоит в том, что при обращении к BEDO-памяти задается адрес одной ячейки в строке, а за счет стробирующих импульсов CAS считывается содержание и этой ячейки, и трех следующих, то есть реализуется пакетный метод доступа. Упрощенная схема работы BEDO и последовательность событий представлены на рис

Асинхронная память EDO DRAM n Другое отличие состоит в том, что при обращении к BEDO-памяти задается адрес одной ячейки в строке, а за счет стробирующих импульсов CAS считывается содержание и этой ячейки, и трех следующих, то есть реализуется пакетный метод доступа. Упрощенная схема работы BEDO и последовательность событий представлены на рис

Синхронная память SDRAM n n Все рассмотренные выше типы памяти (FPM/EDO/BEDO) являются асинхронными. При асинхронной передаче данных гарантируется, что определенная операция будет закончена за фиксированный промежуток времени, например за 60 нс. Работа асинхронной памяти не синхронизована с тактовой частотой системной шины, то есть данные появляются на этой шине в произвольные моменты времени. С системной шины данные считываются контроллером, который синхронизирован тактовой частотой. Следовательно, если данные появляются в ближайший момент за фронтом тактового импульса, то они будут считаны только с началом следующего тактового импульса. Так происходит потому, что сигналом к считыванию данных является не уровень тактового импульса (высокий или низкий), а его фронт. Поэтому при использовании асинхронной памяти часто возникает задержка с обработкой данных, что, в свою очередь, приводит к жестким ограничениям на частоту системной шины FSB.

Синхронная память SDRAM n n Все рассмотренные выше типы памяти (FPM/EDO/BEDO) являются асинхронными. При асинхронной передаче данных гарантируется, что определенная операция будет закончена за фиксированный промежуток времени, например за 60 нс. Работа асинхронной памяти не синхронизована с тактовой частотой системной шины, то есть данные появляются на этой шине в произвольные моменты времени. С системной шины данные считываются контроллером, который синхронизирован тактовой частотой. Следовательно, если данные появляются в ближайший момент за фронтом тактового импульса, то они будут считаны только с началом следующего тактового импульса. Так происходит потому, что сигналом к считыванию данных является не уровень тактового импульса (высокий или низкий), а его фронт. Поэтому при использовании асинхронной памяти часто возникает задержка с обработкой данных, что, в свою очередь, приводит к жестким ограничениям на частоту системной шины FSB.

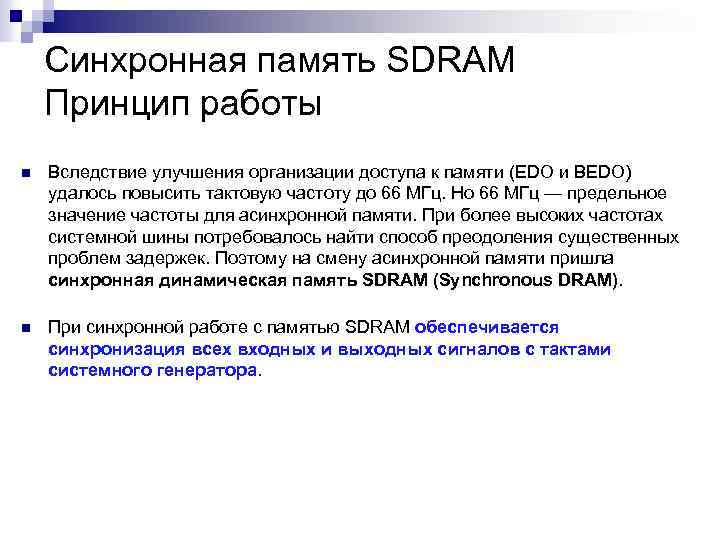

Синхронная память SDRAM Принцип работы n Вследствие улучшения организации доступа к памяти (EDO и BEDO) удалось повысить тактовую частоту до 66 МГц. Но 66 МГц — предельное значение частоты для асинхронной памяти. При более высоких частотах системной шины потребовалось найти способ преодоления существенных проблем задержек. Поэтому на смену асинхронной памяти пришла синхронная динамическая память SDRAM (Synchronous DRAM). n При синхронной работе с памятью SDRAM обеспечивается синхронизация всех входных и выходных сигналов с тактами системного генератора.

Синхронная память SDRAM Принцип работы n Вследствие улучшения организации доступа к памяти (EDO и BEDO) удалось повысить тактовую частоту до 66 МГц. Но 66 МГц — предельное значение частоты для асинхронной памяти. При более высоких частотах системной шины потребовалось найти способ преодоления существенных проблем задержек. Поэтому на смену асинхронной памяти пришла синхронная динамическая память SDRAM (Synchronous DRAM). n При синхронной работе с памятью SDRAM обеспечивается синхронизация всех входных и выходных сигналов с тактами системного генератора.

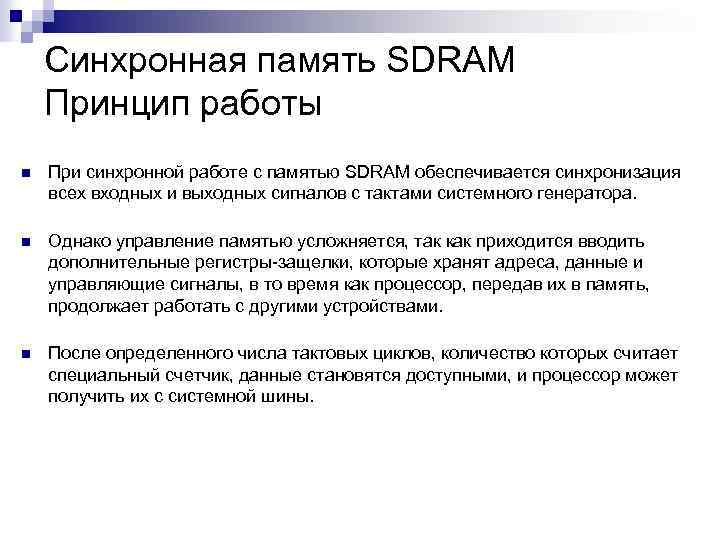

Синхронная память SDRAM Принцип работы n При синхронной работе с памятью SDRAM обеспечивается синхронизация всех входных и выходных сигналов с тактами системного генератора. n Однако управление памятью усложняется, так как приходится вводить дополнительные регистры-защелки, которые хранят адреса, данные и управляющие сигналы, в то время как процессор, передав их в память, продолжает работать с другими устройствами. n После определенного числа тактовых циклов, количество которых считает специальный счетчик, данные становятся доступными, и процессор может получить их с системной шины.

Синхронная память SDRAM Принцип работы n При синхронной работе с памятью SDRAM обеспечивается синхронизация всех входных и выходных сигналов с тактами системного генератора. n Однако управление памятью усложняется, так как приходится вводить дополнительные регистры-защелки, которые хранят адреса, данные и управляющие сигналы, в то время как процессор, передав их в память, продолжает работать с другими устройствами. n После определенного числа тактовых циклов, количество которых считает специальный счетчик, данные становятся доступными, и процессор может получить их с системной шины.

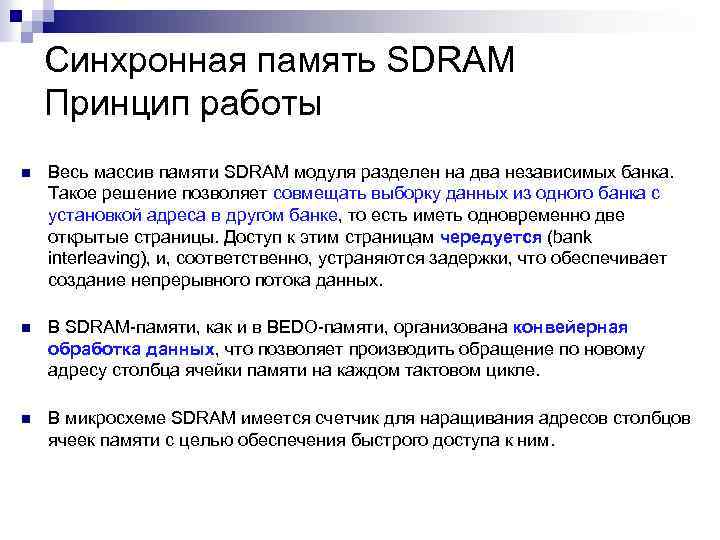

Синхронная память SDRAM Принцип работы n Весь массив памяти SDRAM модуля разделен на два независимых банка. Такое решение позволяет совмещать выборку данных из одного банка с установкой адреса в другом банке, то есть иметь одновременно две открытые страницы. Доступ к этим страницам чередуется (bank interleaving), и, соответственно, устраняются задержки, что обеспечивает создание непрерывного потока данных. n В SDRAM-памяти, как и в BEDO-памяти, организована конвейерная обработка данных, что позволяет производить обращение по новому адресу столбца ячейки памяти на каждом тактовом цикле. n В микросхеме SDRAM имеется счетчик для наращивания адресов столбцов ячеек памяти с целью обеспечения быстрого доступа к ним.

Синхронная память SDRAM Принцип работы n Весь массив памяти SDRAM модуля разделен на два независимых банка. Такое решение позволяет совмещать выборку данных из одного банка с установкой адреса в другом банке, то есть иметь одновременно две открытые страницы. Доступ к этим страницам чередуется (bank interleaving), и, соответственно, устраняются задержки, что обеспечивает создание непрерывного потока данных. n В SDRAM-памяти, как и в BEDO-памяти, организована конвейерная обработка данных, что позволяет производить обращение по новому адресу столбца ячейки памяти на каждом тактовом цикле. n В микросхеме SDRAM имеется счетчик для наращивания адресов столбцов ячеек памяти с целью обеспечения быстрого доступа к ним.

Синхронная память SDRAM Типы n n Существовало два типа синхронной динамической SDRAM-памяти: РС 100 и PC 133. Цифры 100 и 133 определяют частоту системной шины, которую поддерживает эта память. Соответственно, память PC 100 поддерживает максимальную частоту 100 МГц, а память PC 133 — 133 МГц. По своей внутренней архитектуре, способам управления и внешнему дизайну модули памяти РС 100 и РС 133 были полностью идентичны. Можно сказать, что память РС 133 — это «разогнанный» вариант памяти PC 100. Память принято характеризовать различными параметрами, среди которых основным (точнее, первым из называемых) является пропускная способность канала данных — максимальное количество байт, передаваемых по каналу данных за единицу времени (за одну секунду).

Синхронная память SDRAM Типы n n Существовало два типа синхронной динамической SDRAM-памяти: РС 100 и PC 133. Цифры 100 и 133 определяют частоту системной шины, которую поддерживает эта память. Соответственно, память PC 100 поддерживает максимальную частоту 100 МГц, а память PC 133 — 133 МГц. По своей внутренней архитектуре, способам управления и внешнему дизайну модули памяти РС 100 и РС 133 были полностью идентичны. Можно сказать, что память РС 133 — это «разогнанный» вариант памяти PC 100. Память принято характеризовать различными параметрами, среди которых основным (точнее, первым из называемых) является пропускная способность канала данных — максимальное количество байт, передаваемых по каналу данных за единицу времени (за одну секунду).

Синхронная память SDRAM Типы n n Память PC 100 и PC 133 имеет 64 -битную (8 -байтную) шину данных, то есть за каждый такт можно передать 8 байт данных. Следовательно, для того чтобы определить пропускную способность памяти, нужно количество тактов передачи за одну секунду умножить на количество байт, передаваемых за один такт. Количество тактов обращений к памяти за одну секунду — это частота работы памяти. Таким образом, пропускная способность канала памяти определяется по формуле: Пропускная способность (Мбайт/с) = (Частота системной шины (МГц)) х 8 байт. n Для памяти PC 100 пропускная способность составит 100 МГц * 8 байт = 800 Мбайт/с, а для памяти PC 133 — 1064 Мбайт/с, или приблизительно 1 Гбайт/с.

Синхронная память SDRAM Типы n n Память PC 100 и PC 133 имеет 64 -битную (8 -байтную) шину данных, то есть за каждый такт можно передать 8 байт данных. Следовательно, для того чтобы определить пропускную способность памяти, нужно количество тактов передачи за одну секунду умножить на количество байт, передаваемых за один такт. Количество тактов обращений к памяти за одну секунду — это частота работы памяти. Таким образом, пропускная способность канала памяти определяется по формуле: Пропускная способность (Мбайт/с) = (Частота системной шины (МГц)) х 8 байт. n Для памяти PC 100 пропускная способность составит 100 МГц * 8 байт = 800 Мбайт/с, а для памяти PC 133 — 1064 Мбайт/с, или приблизительно 1 Гбайт/с.

Синхронная память SDRAM Типы n Следует иметь в виду, что здесь речь идет о максимально возможной пропускной способности, которая реализуется только в случае последовательной передачи данных (в режиме страничного доступа), когда данные передаются с каждым тактом обращения. n В то же время при этом не учитывается количество тактов, необходимых для получения доступа к самой строке, а также для настроек (пробуждения) модуля памяти. n Поэтому другими важными характеристиками памяти являются время доступа и время цикла.

Синхронная память SDRAM Типы n Следует иметь в виду, что здесь речь идет о максимально возможной пропускной способности, которая реализуется только в случае последовательной передачи данных (в режиме страничного доступа), когда данные передаются с каждым тактом обращения. n В то же время при этом не учитывается количество тактов, необходимых для получения доступа к самой строке, а также для настроек (пробуждения) модуля памяти. n Поэтому другими важными характеристиками памяти являются время доступа и время цикла.

Синхронная память SDRAM Время доступа (RAS to active time, Tras) n n Время доступа (RAS to active time, Tras) — это время, проходящее с момента обращения к памяти до момента считывания данных. Эта величина приблизительно одинакова для всех типов динамической памяти и составляет примерно 50 нс. Время доступа актуально при случайном доступе к памяти, то есть когда последовательные считываемые ячейки памяти принадлежат различным строкам. Если же говорить о блочной передаче, то более показательной характеристикой является время цикла, то есть время между двумя последовательными обращениями к ячейкам памяти. Первый цикл обращения всегда равен времени доступа, то есть около 50 нс. Но при последующих циклах обращения в пределах одной страницы время существенно меньше и составляет 10 нс для памяти PC 100 и 7, 5 нс для памяти PC 133 (7, 5 нс — длительность одного такта при частоте шины 133 МГц).

Синхронная память SDRAM Время доступа (RAS to active time, Tras) n n Время доступа (RAS to active time, Tras) — это время, проходящее с момента обращения к памяти до момента считывания данных. Эта величина приблизительно одинакова для всех типов динамической памяти и составляет примерно 50 нс. Время доступа актуально при случайном доступе к памяти, то есть когда последовательные считываемые ячейки памяти принадлежат различным строкам. Если же говорить о блочной передаче, то более показательной характеристикой является время цикла, то есть время между двумя последовательными обращениями к ячейкам памяти. Первый цикл обращения всегда равен времени доступа, то есть около 50 нс. Но при последующих циклах обращения в пределах одной страницы время существенно меньше и составляет 10 нс для памяти PC 100 и 7, 5 нс для памяти PC 133 (7, 5 нс — длительность одного такта при частоте шины 133 МГц).

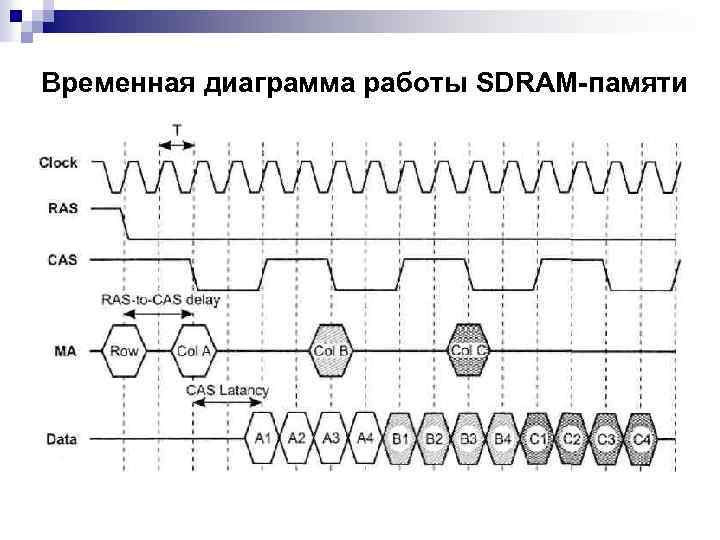

Временная диаграмма работы SDRAM-памяти

Временная диаграмма работы SDRAM-памяти

Синхронная память SDRAM Циклы доступа n n Любая динамическая память характеризуется также циклами доступа, записываемыми в виде цепочек типа 5 -1 -1 -1 или 5 -2 -2 -2 и т. д. Такая цепочка определяет количество тактов, необходимых для чтения первых четырех элементов (байт, слово, двойное слово) данных в страничном режиме доступа. Первая цифра в таком обозначении определяет время доступа, то есть количество тактов, проходимых от начала обращения к банку памяти до появления данных на шине. Соответственно, при работе в страничном режиме следующие данные появятся на шине уже через меньшее количество тактов. Например, при цепочке 5 -1 -1 -1 данные появляются без задержек, то есть с каждым тактовым импульсом. Сумма всех цифр цепочки показывает количество тактов, необходимых для получения четырех элементов. Так, для памяти PC 133 реализуется схема 5 -1 -1 -1, которая означает, что для доступа к данным требуется 8 тактов. Для рассмотренной ранее памяти EDO реализуется схема 5 -2 -2 -2 и для доступа требуется 11 тактов, а для памяти FPM схема 5 -3 -3 -3 дает 14 тактов.

Синхронная память SDRAM Циклы доступа n n Любая динамическая память характеризуется также циклами доступа, записываемыми в виде цепочек типа 5 -1 -1 -1 или 5 -2 -2 -2 и т. д. Такая цепочка определяет количество тактов, необходимых для чтения первых четырех элементов (байт, слово, двойное слово) данных в страничном режиме доступа. Первая цифра в таком обозначении определяет время доступа, то есть количество тактов, проходимых от начала обращения к банку памяти до появления данных на шине. Соответственно, при работе в страничном режиме следующие данные появятся на шине уже через меньшее количество тактов. Например, при цепочке 5 -1 -1 -1 данные появляются без задержек, то есть с каждым тактовым импульсом. Сумма всех цифр цепочки показывает количество тактов, необходимых для получения четырех элементов. Так, для памяти PC 133 реализуется схема 5 -1 -1 -1, которая означает, что для доступа к данным требуется 8 тактов. Для рассмотренной ранее памяти EDO реализуется схема 5 -2 -2 -2 и для доступа требуется 11 тактов, а для памяти FPM схема 5 -3 -3 -3 дает 14 тактов.

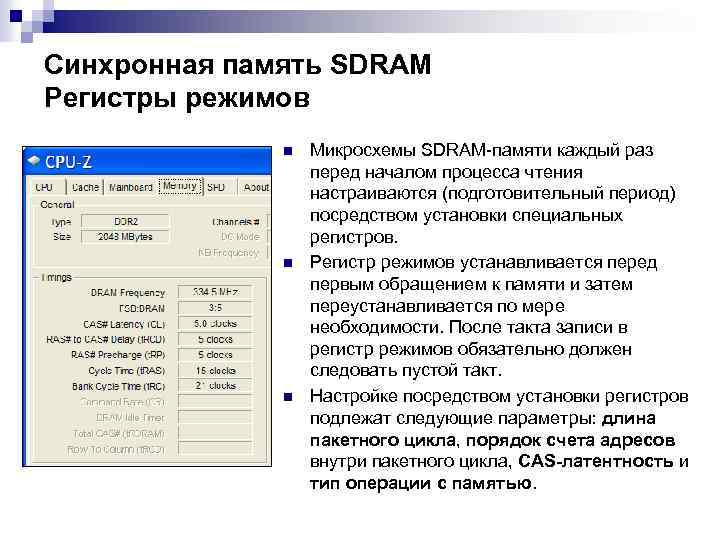

Синхронная память SDRAM Регистры режимов n n n Микросхемы SDRAM-памяти каждый раз перед началом процесса чтения настраиваются (подготовительный период) посредством установки специальных регистров. Регистр режимов устанавливается перед первым обращением к памяти и затем переустанавливается по мере необходимости. После такта записи в регистр режимов обязательно должен следовать пустой такт. Настройке посредством установки регистров подлежат следующие параметры: длина пакетного цикла, порядок счета адресов внутри пакетного цикла, CAS-латентность и тип операции с памятью.

Синхронная память SDRAM Регистры режимов n n n Микросхемы SDRAM-памяти каждый раз перед началом процесса чтения настраиваются (подготовительный период) посредством установки специальных регистров. Регистр режимов устанавливается перед первым обращением к памяти и затем переустанавливается по мере необходимости. После такта записи в регистр режимов обязательно должен следовать пустой такт. Настройке посредством установки регистров подлежат следующие параметры: длина пакетного цикла, порядок счета адресов внутри пакетного цикла, CAS-латентность и тип операции с памятью.

Синхронная память SDRAM CAS-латентность (CAS latency) n n CAS-латентность (CAS latency) определяет задержку по времени в тактах, которая происходит с момента подачи сигнала CAS (с момента получения адреса столбца) до выдачи первого слова данных на шину. (Для SDRAM-памяти эта задержка может составлять два или три такта. ) Тип операции с памятью (Operation Mode) может быть либо нормальным, когда используется пакетный режим для чтения и записи, либо специальным, когда используется режим пакетного чтения и одиночных операций записи. Порядок обращения к памяти начинается, как уже отмечалось, с установки регистров управления. На это уходит два такта, после чего начинается активизация нужного банка памяти, то есть ввод адреса строки и подача стробирующего сигнала RAS. С приходом положительного фронта тактового импульса открывается доступ к нужной строке, а адрес строки помещается в адресный буфер строки, где он может удерживаться столько времени, сколько нужно.

Синхронная память SDRAM CAS-латентность (CAS latency) n n CAS-латентность (CAS latency) определяет задержку по времени в тактах, которая происходит с момента подачи сигнала CAS (с момента получения адреса столбца) до выдачи первого слова данных на шину. (Для SDRAM-памяти эта задержка может составлять два или три такта. ) Тип операции с памятью (Operation Mode) может быть либо нормальным, когда используется пакетный режим для чтения и записи, либо специальным, когда используется режим пакетного чтения и одиночных операций записи. Порядок обращения к памяти начинается, как уже отмечалось, с установки регистров управления. На это уходит два такта, после чего начинается активизация нужного банка памяти, то есть ввод адреса строки и подача стробирующего сигнала RAS. С приходом положительного фронта тактового импульса открывается доступ к нужной строке, а адрес строки помещается в адресный буфер строки, где он может удерживаться столько времени, сколько нужно.

Синхронная память SDRAM RAS to CAS delay (t. RCD) , CAS latency (t. CL) n n n Промежуток времени, называемый RAS to CAS delay (t. RCD) — то есть задержка в тактах подачи сигнала CAS относительно сигнала RAS, подается стробирующий импульс CAS. При установке CAS в низкий уровень после прихода положительного фронта тактирующего импульса происходит выборка адреса столбца, который присутствует в данный момент на шине адреса, и открывается ДОСТУП к нужному столбцу матрицы памяти. Затем, через время CAS latency (t. CL), на шине данных появляется первое слово, которое может быть считано процессором. Каждое последующее слово (их количество определяется длиной пакетного цикла) появляется на шине данных в очередном такте. Завершение цикла обращения к банку памяти осуществляется подачей команды деактивации RAS Precharge (t. RP). Эта команда подается за один (при CAS latency = 2) или за два (при CAS latency = 3) такта перед выдачей последнего слова данных. Время деактивации также измеряется в тактах и может быть равно двум или трем.

Синхронная память SDRAM RAS to CAS delay (t. RCD) , CAS latency (t. CL) n n n Промежуток времени, называемый RAS to CAS delay (t. RCD) — то есть задержка в тактах подачи сигнала CAS относительно сигнала RAS, подается стробирующий импульс CAS. При установке CAS в низкий уровень после прихода положительного фронта тактирующего импульса происходит выборка адреса столбца, который присутствует в данный момент на шине адреса, и открывается ДОСТУП к нужному столбцу матрицы памяти. Затем, через время CAS latency (t. CL), на шине данных появляется первое слово, которое может быть считано процессором. Каждое последующее слово (их количество определяется длиной пакетного цикла) появляется на шине данных в очередном такте. Завершение цикла обращения к банку памяти осуществляется подачей команды деактивации RAS Precharge (t. RP). Эта команда подается за один (при CAS latency = 2) или за два (при CAS latency = 3) такта перед выдачей последнего слова данных. Время деактивации также измеряется в тактах и может быть равно двум или трем.

Синхронная память SDRAM. Тайминги памяти n Описанные промежутки времени RAS to CAS delay (t. RCD), CAS latency (t. CL) и время деактивации RAS Precharge (t. RP) определяют тайминг памяти, записываемый в виде последовательности t. CL —> t. RCD —> t. RP. n Понятно, что чем меньше тайминг, тем более быстродействующей является память. n Самый простой способ увеличения максимальной пропускной способности памяти заключается в увеличении частоты работы памяти. Однако на практике реализовать это совсем не просто. n Вспомним, что элементарной ячейкой динамической памяти является конденсатор — инерционное по своей природе устройство. Для того чтобы произвести считывание информации с конденсатора, необходимо его разрядить, для чего требуется определенное время, пропорциональное емкости конденсатора, — сделать это мгновенно невозможно. Следовательно, нельзя повышать частоту ядра памяти до бесконечности.

Синхронная память SDRAM. Тайминги памяти n Описанные промежутки времени RAS to CAS delay (t. RCD), CAS latency (t. CL) и время деактивации RAS Precharge (t. RP) определяют тайминг памяти, записываемый в виде последовательности t. CL —> t. RCD —> t. RP. n Понятно, что чем меньше тайминг, тем более быстродействующей является память. n Самый простой способ увеличения максимальной пропускной способности памяти заключается в увеличении частоты работы памяти. Однако на практике реализовать это совсем не просто. n Вспомним, что элементарной ячейкой динамической памяти является конденсатор — инерционное по своей природе устройство. Для того чтобы произвести считывание информации с конденсатора, необходимо его разрядить, для чего требуется определенное время, пропорциональное емкости конденсатора, — сделать это мгновенно невозможно. Следовательно, нельзя повышать частоту ядра памяти до бесконечности.

Синхронная память SDRAM Тайминги памяти n n Кроме того, динамическая память требует периодической регенерации, чтобы восстанавливать заряды конденсаторов, а для зарядки конденсаторов тоже необходим определенный временной интервал. В результате повышение частоты ядра памяти сопряжено с непреодолимыми трудностями. Конечно, применение более миниатюрных конденсаторов повышает их быстродействие, однако для этого нужно использовать иную проектную норму при производстве чипов памяти. К тому же переход на новый технологический процесс производства не может кардинально увеличить скорость работы памяти. Поэтому, кроме банального увеличения частоты работы памяти, для увеличения ее пропускной способности часто используют иные приемы. О некоторых приемах, таких как пакетный режим передачи и организация чередующихся банков, мы уже упоминали. Однако более кардинальным способом увеличения пропускной способности памяти стал переход к стандарту DDR

Синхронная память SDRAM Тайминги памяти n n Кроме того, динамическая память требует периодической регенерации, чтобы восстанавливать заряды конденсаторов, а для зарядки конденсаторов тоже необходим определенный временной интервал. В результате повышение частоты ядра памяти сопряжено с непреодолимыми трудностями. Конечно, применение более миниатюрных конденсаторов повышает их быстродействие, однако для этого нужно использовать иную проектную норму при производстве чипов памяти. К тому же переход на новый технологический процесс производства не может кардинально увеличить скорость работы памяти. Поэтому, кроме банального увеличения частоты работы памяти, для увеличения ее пропускной способности часто используют иные приемы. О некоторых приемах, таких как пакетный режим передачи и организация чередующихся банков, мы уже упоминали. Однако более кардинальным способом увеличения пропускной способности памяти стал переход к стандарту DDR

Синхронная память SDRAM Память DDR SDRAM n Синхронная динамическая память DDR SDRAM пришла на смену памяти SDRAM и обеспечивает в два раза большую пропускную способность. Аббревиатура DDR (Double Data Rate) в названии памяти означает удвоенную скорость передачи данных. Аналогично, обычную SDRAMпамять называют SDR (Single Data Rate) памятью, то есть памятью с одинарной скоростью передачи.

Синхронная память SDRAM Память DDR SDRAM n Синхронная динамическая память DDR SDRAM пришла на смену памяти SDRAM и обеспечивает в два раза большую пропускную способность. Аббревиатура DDR (Double Data Rate) в названии памяти означает удвоенную скорость передачи данных. Аналогично, обычную SDRAMпамять называют SDR (Single Data Rate) памятью, то есть памятью с одинарной скоростью передачи.

Синхронная динамическая память DDR SDRAM n n n Синхронная динамическая память DDR SDRAM пришла на смену памяти SDRAM и обеспечивает в два раза большую пропускную способность. Основным сдерживающим элементом увеличения тактовой частоты работы памяти является само ядро памяти (массив элементов хранения). Однако кроме ядра памяти в модуле присутствуют и буферы промежуточного хранения (I/O Logic), через которые ядро памяти обменивается данными с шиной памяти. Эти буферы имеют значительно более высокое быстродействие, нежели само ядро, поэтому тактовую частоту работы самой шины памяти и буферов обмена можно легко увеличить. Именно такой способ и используется в DDR-памяти.

Синхронная динамическая память DDR SDRAM n n n Синхронная динамическая память DDR SDRAM пришла на смену памяти SDRAM и обеспечивает в два раза большую пропускную способность. Основным сдерживающим элементом увеличения тактовой частоты работы памяти является само ядро памяти (массив элементов хранения). Однако кроме ядра памяти в модуле присутствуют и буферы промежуточного хранения (I/O Logic), через которые ядро памяти обменивается данными с шиной памяти. Эти буферы имеют значительно более высокое быстродействие, нежели само ядро, поэтому тактовую частоту работы самой шины памяти и буферов обмена можно легко увеличить. Именно такой способ и используется в DDR-памяти.

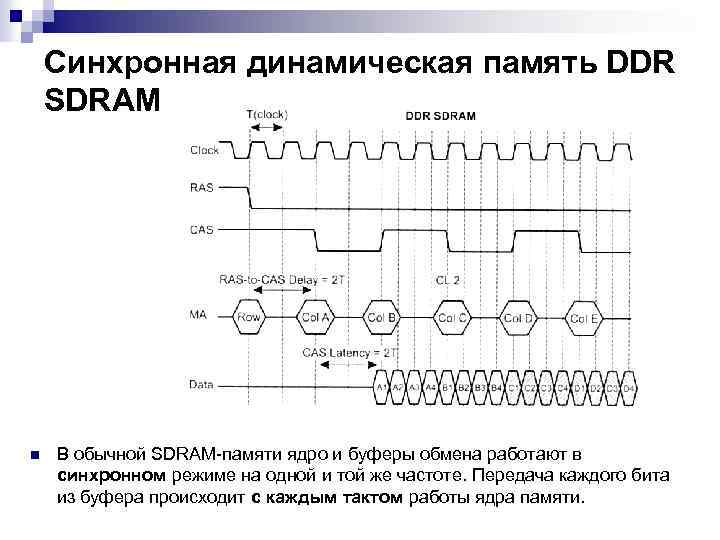

Синхронная динамическая память DDR SDRAM n В обычной SDRAM-памяти ядро и буферы обмена работают в синхронном режиме на одной и той же частоте. Передача каждого бита из буфера происходит с каждым тактом работы ядра памяти.

Синхронная динамическая память DDR SDRAM n В обычной SDRAM-памяти ядро и буферы обмена работают в синхронном режиме на одной и той же частоте. Передача каждого бита из буфера происходит с каждым тактом работы ядра памяти.

Синхронная динамическая память DDR SDRAM n n n Для того чтобы синхронизировать работу ядра памяти и буферов вводавывода, используется одна и та же тактовая частота (одни и те же тактирующие импульсы). Только если в самом ядре памяти синхронизация осуществляется по положительному фронту тактирующего импульса, то в буфере ввода-вывода для синхронизации используется как положительный, так и отрицательный фронт тактирующего импульса. Таким образом, передача двух бит в буфер ввода-вывода по двум раздельным линиям осуществляется по положительному фронту тактирующего импульса, а их выдача на шину данных происходит как по положительному, так и по отрицательному фронтам тактирующего импульса. Это обеспечивает в два раза более высокую скорость работы буфера и, соответственно, вдвое большую пропускную способность памяти. Все же остальные принципиальные моменты DDR-памяти не изменились: структура нескольких независимых банков позволяет совмещать выборку данных из одного банка с установкой адреса в другом банке, то есть можно одновременно иметь две открытые страницы. Доступ к этим страницам чередуется (bank interleaving), что приводит к устранению задержек и обеспечивает создание непрерывного потока данных.

Синхронная динамическая память DDR SDRAM n n n Для того чтобы синхронизировать работу ядра памяти и буферов вводавывода, используется одна и та же тактовая частота (одни и те же тактирующие импульсы). Только если в самом ядре памяти синхронизация осуществляется по положительному фронту тактирующего импульса, то в буфере ввода-вывода для синхронизации используется как положительный, так и отрицательный фронт тактирующего импульса. Таким образом, передача двух бит в буфер ввода-вывода по двум раздельным линиям осуществляется по положительному фронту тактирующего импульса, а их выдача на шину данных происходит как по положительному, так и по отрицательному фронтам тактирующего импульса. Это обеспечивает в два раза более высокую скорость работы буфера и, соответственно, вдвое большую пропускную способность памяти. Все же остальные принципиальные моменты DDR-памяти не изменились: структура нескольких независимых банков позволяет совмещать выборку данных из одного банка с установкой адреса в другом банке, то есть можно одновременно иметь две открытые страницы. Доступ к этим страницам чередуется (bank interleaving), что приводит к устранению задержек и обеспечивает создание непрерывного потока данных.

Синхронная динамическая память DDR SDRAM n n DDR-память настраивается в процессе работы путем установки соответствующих регистров, как и SDRAM-память. Кроме того, DDRпамять, как и SDRAM, предназначена для работы с системными частотами 100 и 133, 166 и 200, 216, 250 и 266 МГц. DDR-память, работающую на частоте 100 МГц, иногда обозначают как DDR 200, подразумевая при этом, что «эффективная» частота памяти составляет 200 МГц (данные передаются два раза за такт). Аналогично, при работе памяти на частоте 133 МГц используют обозначение DDR 266, при частоте 166 МГц — DDR 333, при частоте 200 МГц — DDR 400 и т. д. Нетрудно рассчитать и пропускную способность DDR-памяти. Учитывая, что ширина шины данных составляет 8 байт, ¨ ¨ ¨ ¨ для памяти DDR 200 получим 200 МГц х 8 байт = 1, 6 Гбайт/с; для памяти DDR 266 — 2, 1 Гбайт/с; для памяти DDR 333 — 2, 7 Гбайт/с, для памяти DDR 400 - 3, 2 Гбайт/с, для памяти DDR 433 - 3, 5 Гбайт/с, для памяти DDR 500 -4, 0 Гбайт/с и для памяти DDR 533 - 4, 3 Гбайт/с.

Синхронная динамическая память DDR SDRAM n n DDR-память настраивается в процессе работы путем установки соответствующих регистров, как и SDRAM-память. Кроме того, DDRпамять, как и SDRAM, предназначена для работы с системными частотами 100 и 133, 166 и 200, 216, 250 и 266 МГц. DDR-память, работающую на частоте 100 МГц, иногда обозначают как DDR 200, подразумевая при этом, что «эффективная» частота памяти составляет 200 МГц (данные передаются два раза за такт). Аналогично, при работе памяти на частоте 133 МГц используют обозначение DDR 266, при частоте 166 МГц — DDR 333, при частоте 200 МГц — DDR 400 и т. д. Нетрудно рассчитать и пропускную способность DDR-памяти. Учитывая, что ширина шины данных составляет 8 байт, ¨ ¨ ¨ ¨ для памяти DDR 200 получим 200 МГц х 8 байт = 1, 6 Гбайт/с; для памяти DDR 266 — 2, 1 Гбайт/с; для памяти DDR 333 — 2, 7 Гбайт/с, для памяти DDR 400 - 3, 2 Гбайт/с, для памяти DDR 433 - 3, 5 Гбайт/с, для памяти DDR 500 -4, 0 Гбайт/с и для памяти DDR 533 - 4, 3 Гбайт/с.

Синхронная динамическая память DDR SDRAM n n n Хотя обозначение типа DDR 200, DDR 266, DDR 333 и т. д. кажется вполне логичным и понятным, официально принято другое обозначение этой памяти. В названии используется не «эффективная» частота, а пиковая пропускная способность, то есть память DDR 200 обозначается как DDR PC 1600, DDR 266 - как DDR PC 2100, DDR 333 - как РС 2700, a DDR 400 - как РС 3200. Кроме частоты, память, как уже отмечалось, характеризуется схемой тайминга (t. CL —> t. RCD —> t. RP). Для памяти DDR 200 тайминг всегда 2 -22, а вот для остальных типов памяти тайминг может быть различным. К примеру, встречаются тайминги 3 -3 -3, 2, 5 -3 -3, 2 -3 -3 и 2, 5 -2 -2. Дело в том, что памяти типа DDR 433, DDR 500 и DDR 533 отличаются от остальных типов памяти только способностью работать на более высоких частотах ядра памяти. Это, во-первых, не препятствует ее использованию и на более высоких частотах, а во-вторых, позволяет использовать при разгоне системы. Кроме того, при использовании этих типов памяти на частоте 400 МГц возможно уменьшение таймингов памяти (идеальный случай соответствует таймингу 2 -2 -2), что можно рассматривать как своеобразный разгон памяти.

Синхронная динамическая память DDR SDRAM n n n Хотя обозначение типа DDR 200, DDR 266, DDR 333 и т. д. кажется вполне логичным и понятным, официально принято другое обозначение этой памяти. В названии используется не «эффективная» частота, а пиковая пропускная способность, то есть память DDR 200 обозначается как DDR PC 1600, DDR 266 - как DDR PC 2100, DDR 333 - как РС 2700, a DDR 400 - как РС 3200. Кроме частоты, память, как уже отмечалось, характеризуется схемой тайминга (t. CL —> t. RCD —> t. RP). Для памяти DDR 200 тайминг всегда 2 -22, а вот для остальных типов памяти тайминг может быть различным. К примеру, встречаются тайминги 3 -3 -3, 2, 5 -3 -3, 2 -3 -3 и 2, 5 -2 -2. Дело в том, что памяти типа DDR 433, DDR 500 и DDR 533 отличаются от остальных типов памяти только способностью работать на более высоких частотах ядра памяти. Это, во-первых, не препятствует ее использованию и на более высоких частотах, а во-вторых, позволяет использовать при разгоне системы. Кроме того, при использовании этих типов памяти на частоте 400 МГц возможно уменьшение таймингов памяти (идеальный случай соответствует таймингу 2 -2 -2), что можно рассматривать как своеобразный разгон памяти.

Память DDR 2 SDRAM n Если следовать терминологии SDR (Single Data Rate), DDR (Doub. Je Data Rate), то память DDR 2 было бы логично назвать QDR (Quadra Data Rate), так как этот стандарт подразумевает в четыре раза большую скорость передачи. То есть в стандарте DDR 2 при пакетном режиме доступа данные передаются четыре раза за один такт.

Память DDR 2 SDRAM n Если следовать терминологии SDR (Single Data Rate), DDR (Doub. Je Data Rate), то память DDR 2 было бы логично назвать QDR (Quadra Data Rate), так как этот стандарт подразумевает в четыре раза большую скорость передачи. То есть в стандарте DDR 2 при пакетном режиме доступа данные передаются четыре раза за один такт.

Синхронная динамическая память DDR 2 SDRAM n n Для организации данного режима работы памяти необходимо, чтобы буфер ввода-вывода работал бы на учетверенной частоте по сравнению с частотой ядра памяти. Достигается это следующим образом: ядро памяти, как и прежде, синхронизируется по положительному фронту тактирующих импульсов и с приходом каждого такого положительного фронта по четырем независимым линиям передают в буфер ввода-вывода четыре бита информации (выборка четырех битов за такт). Сам буфер ввода-вывода тактируется на удвоенной частоте ядра памяти и синхронизируется как по положительному, так и по отрицательному фронту этой частоты. То есть с приходом положительного и отрицательного фронта происходит передача бит в мультиплексном режиме на шину данных. Это позволяет за каждый такт работы ядра памяти передавать четыре бита на шину данных, то есть вчетверо повысить пропускную способность памяти.

Синхронная динамическая память DDR 2 SDRAM n n Для организации данного режима работы памяти необходимо, чтобы буфер ввода-вывода работал бы на учетверенной частоте по сравнению с частотой ядра памяти. Достигается это следующим образом: ядро памяти, как и прежде, синхронизируется по положительному фронту тактирующих импульсов и с приходом каждого такого положительного фронта по четырем независимым линиям передают в буфер ввода-вывода четыре бита информации (выборка четырех битов за такт). Сам буфер ввода-вывода тактируется на удвоенной частоте ядра памяти и синхронизируется как по положительному, так и по отрицательному фронту этой частоты. То есть с приходом положительного и отрицательного фронта происходит передача бит в мультиплексном режиме на шину данных. Это позволяет за каждый такт работы ядра памяти передавать четыре бита на шину данных, то есть вчетверо повысить пропускную способность памяти.

Синхронная динамическая память DDR 2 SDRAM n По Сравнению с памятью DDR, память DDR 2 позволяет обеспечить ту же пропускную способность, по при вдвое меньшей частоте ядра. К примеру, в памяти DDR 400 ядро функционирует на частоте 200 МГц, а в памяти DDR 2 -400 — на частоте 100 МГц. В этом смысле память DDR 2 имеет значительно большие потенциальные возможности для увеличения пропускной способности по сравнению с памятью DDR.

Синхронная динамическая память DDR 2 SDRAM n По Сравнению с памятью DDR, память DDR 2 позволяет обеспечить ту же пропускную способность, по при вдвое меньшей частоте ядра. К примеру, в памяти DDR 400 ядро функционирует на частоте 200 МГц, а в памяти DDR 2 -400 — на частоте 100 МГц. В этом смысле память DDR 2 имеет значительно большие потенциальные возможности для увеличения пропускной способности по сравнению с памятью DDR.

Синхронная динамическая память DDR 3 SDRAM n Память DDR 3 является логическим развитием стандарта DDR 2. Стандарт DDR 3 был принят летом 2007 года, однако многие производители еще до официального утверждения спецификации успели представить новые модули. n Эффективная частота работы DDR 3 -памяти составляет от 800 до 1600 МГц. n Кроме увеличенной пропускной способности, память DDR 3 будет также выгодно отличаться и уменьшенным энергопотреблением. Так, если модули DDR-памяти работают при напряжении питания 2, 5 В, а модули DDR 2 — при 1, 8 В, то модули DDR 3 функционируют при напряжении питания 1, 5 В (на 16, 5 % меньше, чем для памяти DDR 2). n Снижение напряжения питания достигается за счет использования 90 нанометрового техпроцесса производства микросхем памяти и применения транзисторов с двойным затвором (Dual-gate), что способствует снижению токов утечки.

Синхронная динамическая память DDR 3 SDRAM n Память DDR 3 является логическим развитием стандарта DDR 2. Стандарт DDR 3 был принят летом 2007 года, однако многие производители еще до официального утверждения спецификации успели представить новые модули. n Эффективная частота работы DDR 3 -памяти составляет от 800 до 1600 МГц. n Кроме увеличенной пропускной способности, память DDR 3 будет также выгодно отличаться и уменьшенным энергопотреблением. Так, если модули DDR-памяти работают при напряжении питания 2, 5 В, а модули DDR 2 — при 1, 8 В, то модули DDR 3 функционируют при напряжении питания 1, 5 В (на 16, 5 % меньше, чем для памяти DDR 2). n Снижение напряжения питания достигается за счет использования 90 нанометрового техпроцесса производства микросхем памяти и применения транзисторов с двойным затвором (Dual-gate), что способствует снижению токов утечки.

Синхронная динамическая память DDR 3 SDRAM n Модули памяти DDR 3 DIMM для настольных ПК обладают 240 -контактной структурой, привычной нам по модулям DDR 2; однако физической совместимости не будет благодаря различному расположению ключей DIMM. Такая "защита от дурака", предотвращающая установку модулей DDR 3 в платы под DDR 2 и наоборот предусмотрена не только по причине поконтактной несовместимости модулей, но и в связи с разными напряжения питания и сигнальными уровнями разных поколений оперативной памяти.

Синхронная динамическая память DDR 3 SDRAM n Модули памяти DDR 3 DIMM для настольных ПК обладают 240 -контактной структурой, привычной нам по модулям DDR 2; однако физической совместимости не будет благодаря различному расположению ключей DIMM. Такая "защита от дурака", предотвращающая установку модулей DDR 3 в платы под DDR 2 и наоборот предусмотрена не только по причине поконтактной несовместимости модулей, но и в связи с разными напряжения питания и сигнальными уровнями разных поколений оперативной памяти.

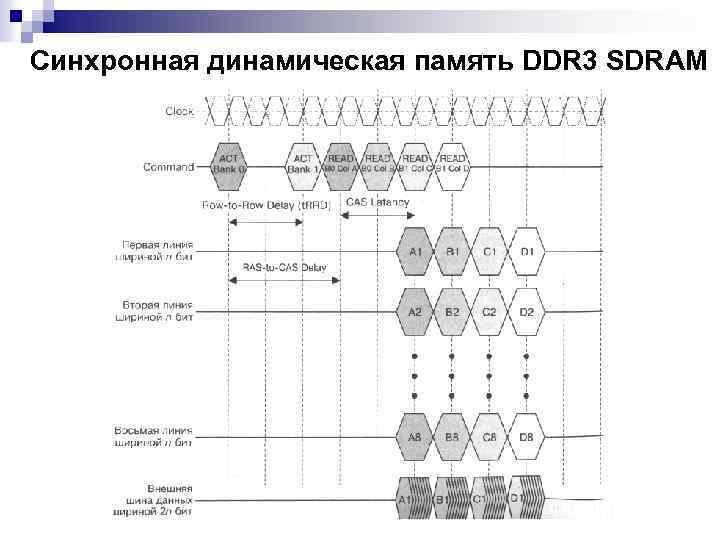

Синхронная динамическая память DDR 3 SDRAM n n n Для памяти DDR 3 будет реализована восьмибанковая логическая структура, а размер страницы составит 1 Кбайт для чипов с шиной х4 и х8 и 2 Кбайт — для чипов с шиной х16. Принципиальное отличие памяти DDR 3 от DDR 2 заключается в реализации механизма 8 n-Prefetch вместо 4 n-Prefetch. Для организации данного режима работы памяти необходимо, чтобы буфер ввода-вывода (мультиплексор) работал на частоте, в восемь раз большей по сравнению с частотой ядра памяти. Достигается это следующим образом: ядро памяти, как и прежде, синхронизируется по положительному фронту тактирующих импульсов, а с приходом каждого положительного фронта по восьми независимым линиям в буфер вводавывода (мультиплексор) передаются 8 n бит информации (выборка 8 -и бит за такт). Сам буфер ввода-вывода тактируется на учетверенной частоте ядра памяти и синхронизируется как по положительному, так и по отрицательному фронту данной частоты. Это позволяет за каждый такт работы ядра памяти передавать восемь слов на шину данных, то есть в восемь раз повысить пропускную способность памяти.

Синхронная динамическая память DDR 3 SDRAM n n n Для памяти DDR 3 будет реализована восьмибанковая логическая структура, а размер страницы составит 1 Кбайт для чипов с шиной х4 и х8 и 2 Кбайт — для чипов с шиной х16. Принципиальное отличие памяти DDR 3 от DDR 2 заключается в реализации механизма 8 n-Prefetch вместо 4 n-Prefetch. Для организации данного режима работы памяти необходимо, чтобы буфер ввода-вывода (мультиплексор) работал на частоте, в восемь раз большей по сравнению с частотой ядра памяти. Достигается это следующим образом: ядро памяти, как и прежде, синхронизируется по положительному фронту тактирующих импульсов, а с приходом каждого положительного фронта по восьми независимым линиям в буфер вводавывода (мультиплексор) передаются 8 n бит информации (выборка 8 -и бит за такт). Сам буфер ввода-вывода тактируется на учетверенной частоте ядра памяти и синхронизируется как по положительному, так и по отрицательному фронту данной частоты. Это позволяет за каждый такт работы ядра памяти передавать восемь слов на шину данных, то есть в восемь раз повысить пропускную способность памяти.

Синхронная динамическая память DDR 3 SDRAM n По сравнению с DDR 2, память DDR 3 позволяет обеспечить ту же пропускную способность при вдвое меньшей частоте ядра. К примеру, в памяти DDR 2 -800 ядро функционирует на частоте 200 МГц, а в памяти DDR 3 -800 — на частоте 100 МГц

Синхронная динамическая память DDR 3 SDRAM n По сравнению с DDR 2, память DDR 3 позволяет обеспечить ту же пропускную способность при вдвое меньшей частоте ядра. К примеру, в памяти DDR 2 -800 ядро функционирует на частоте 200 МГц, а в памяти DDR 3 -800 — на частоте 100 МГц

Синхронная динамическая память DDR 3 SDRAM

Синхронная динамическая память DDR 3 SDRAM

Синхронная динамическая память DDR 3 SDRAM n n Конечно, реализация механизма 8 n- Prefetch вместо 4 n-Prefetch — это не единственное различие между памятью DDR 3 и DDR 2. Другими нововведениями, реализованными в памяти DDR 3, являются технология динамического терминирования сигналов (dynamic On-Die Termination, ODT) и новая технология калибровки сигналов. Технология динамического терминирования сигналов позволяет гибко оптимизировать значения терминальных сопротивлений в зависимости от условий загрузки памяти.

Синхронная динамическая память DDR 3 SDRAM n n Конечно, реализация механизма 8 n- Prefetch вместо 4 n-Prefetch — это не единственное различие между памятью DDR 3 и DDR 2. Другими нововведениями, реализованными в памяти DDR 3, являются технология динамического терминирования сигналов (dynamic On-Die Termination, ODT) и новая технология калибровки сигналов. Технология динамического терминирования сигналов позволяет гибко оптимизировать значения терминальных сопротивлений в зависимости от условий загрузки памяти.

Проблема терминирования сигналов n n Распространение любого сигнала вдоль шины неизбежно приводит к его частичному отражению от любых неоднородпостен вдоль пути распространения. Для того чтобы такого отражения сигнала не происходило, необходимо, чтобы, во-первых, на пути распространения сигнала не было неоднородностей и, во-вторых, чтобы сам путь был бесконечным. Понятно, что на практике такие условия нереализуемы и отражение сигнала всегда присутствует. Отраженный сигнал интерферирует с основным сигналом, что приводит к искажению последнего. Поэтому одной из основных задач является уменьшение отраженного сигнала.

Проблема терминирования сигналов n n Распространение любого сигнала вдоль шины неизбежно приводит к его частичному отражению от любых неоднородпостен вдоль пути распространения. Для того чтобы такого отражения сигнала не происходило, необходимо, чтобы, во-первых, на пути распространения сигнала не было неоднородностей и, во-вторых, чтобы сам путь был бесконечным. Понятно, что на практике такие условия нереализуемы и отражение сигнала всегда присутствует. Отраженный сигнал интерферирует с основным сигналом, что приводит к искажению последнего. Поэтому одной из основных задач является уменьшение отраженного сигнала.

Проблема терминирования сигналов n n n Одно из решений, используемых для предотвращения отражения сигнала, заключается во введении шунтирующих сопротивлений, образующих заглушку или терминатор. Шунтирующее сопротивление устанавливается на конце шины, по которой распространяется сигнал и заземляется. Такая «заглушка» полностью поглощает сигнал и предотвращает его отражение. В случае DDR-памяти терминальные сопротивления устанавливаются на самой материнской плате. Такой подход позволяет устранить отражения, которые могли бы возникнуть на конце самой шины, однако не решает проблемы возникновения отражений от неоднородностей, связанных с наличием нескольких слотов для установки модулей памяти. В случае памяти DDR 2 используется принципиально иной метод терминирования сигналов, получивший название ODT (On-Die-Termination). В данном случае терминальные сопротивления устанавливаются непосредственно на самих модулях памяти, а для того чтобы предотвратить поглощение сигнала в активном модуле памяти, используется технология отключения терминальных сопротивлений от активных модулей.

Проблема терминирования сигналов n n n Одно из решений, используемых для предотвращения отражения сигнала, заключается во введении шунтирующих сопротивлений, образующих заглушку или терминатор. Шунтирующее сопротивление устанавливается на конце шины, по которой распространяется сигнал и заземляется. Такая «заглушка» полностью поглощает сигнал и предотвращает его отражение. В случае DDR-памяти терминальные сопротивления устанавливаются на самой материнской плате. Такой подход позволяет устранить отражения, которые могли бы возникнуть на конце самой шины, однако не решает проблемы возникновения отражений от неоднородностей, связанных с наличием нескольких слотов для установки модулей памяти. В случае памяти DDR 2 используется принципиально иной метод терминирования сигналов, получивший название ODT (On-Die-Termination). В данном случае терминальные сопротивления устанавливаются непосредственно на самих модулях памяти, а для того чтобы предотвратить поглощение сигнала в активном модуле памяти, используется технология отключения терминальных сопротивлений от активных модулей.

Отложенная операция CAS n n Другая проблема, связанная с функционированием памяти и приводящая к снижению пропускной способности, — возникновение конфликтов команд. Дело в том, что на шине в один момент времени может присутствовать только одна команда. Для простоты предположим, что существует четыре командные линии, уровни напряжений на которых задают команды RAS, CS (Chip Select) и WE (Write Enable). Если предположить, что на шине одновременно появляются две команды, задаваемые, к примеру, комбинациями 101 и 001, то возникает конфликт. Рассмотрим в качестве примера ситуацию с тремя банками памяти. Активация каждого следующего банка может происходить только после определенного промежутка времени, называемого Row to Row Delay (t. RRD).

Отложенная операция CAS n n Другая проблема, связанная с функционированием памяти и приводящая к снижению пропускной способности, — возникновение конфликтов команд. Дело в том, что на шине в один момент времени может присутствовать только одна команда. Для простоты предположим, что существует четыре командные линии, уровни напряжений на которых задают команды RAS, CS (Chip Select) и WE (Write Enable). Если предположить, что на шине одновременно появляются две команды, задаваемые, к примеру, комбинациями 101 и 001, то возникает конфликт. Рассмотрим в качестве примера ситуацию с тремя банками памяти. Активация каждого следующего банка может происходить только после определенного промежутка времени, называемого Row to Row Delay (t. RRD).

Отложенная операция CAS n n n Для того чтобы избежать пропусков данных, в DDR 2 -памяти используются отложенные операции CAS. Суть заключается в том, что операции активации банка и команда на выбор столбца (СAS) следуют непосредственно друг за другом с разницей в один цикл. Это позволяет избежать конфликта команд, поскольку команда CAS уже не совпадает с командой активации банка. Команда CAS поступает в буфер команд и хранится там требуемое количество циклов в зависимости от значения t. RCD. После этого она считывается, но тина команд остается не занятой и может быть использована для команды активации очередного банка. В результате достигается непрерывный поток данных на шине и увеличивается пропускная способность памяти. Хранение команды CAS в буфере эквивалентно введению дополнительной задержки (Additive Latency, AL), поэтому данный способ известен также как Additive Latency или как способ отложенного чтения (Posted CAS). В DDR-памяти при операциях записи контроллер может осуществлять запись в любую ячейку в пределах открытой строки, причем задержка записи (Write Latency, WL) данных относительно сигнала CAS (выбора столбца) составляет один такт. В памяти DDR 2 задержка записи определяется несколько иначе, она на один такт меньше задержки на чтение (Read Latency, RL): WL = RL - IT. Если, к примеру, RL 7, то WL = 6.

Отложенная операция CAS n n n Для того чтобы избежать пропусков данных, в DDR 2 -памяти используются отложенные операции CAS. Суть заключается в том, что операции активации банка и команда на выбор столбца (СAS) следуют непосредственно друг за другом с разницей в один цикл. Это позволяет избежать конфликта команд, поскольку команда CAS уже не совпадает с командой активации банка. Команда CAS поступает в буфер команд и хранится там требуемое количество циклов в зависимости от значения t. RCD. После этого она считывается, но тина команд остается не занятой и может быть использована для команды активации очередного банка. В результате достигается непрерывный поток данных на шине и увеличивается пропускная способность памяти. Хранение команды CAS в буфере эквивалентно введению дополнительной задержки (Additive Latency, AL), поэтому данный способ известен также как Additive Latency или как способ отложенного чтения (Posted CAS). В DDR-памяти при операциях записи контроллер может осуществлять запись в любую ячейку в пределах открытой строки, причем задержка записи (Write Latency, WL) данных относительно сигнала CAS (выбора столбца) составляет один такт. В памяти DDR 2 задержка записи определяется несколько иначе, она на один такт меньше задержки на чтение (Read Latency, RL): WL = RL - IT. Если, к примеру, RL 7, то WL = 6.

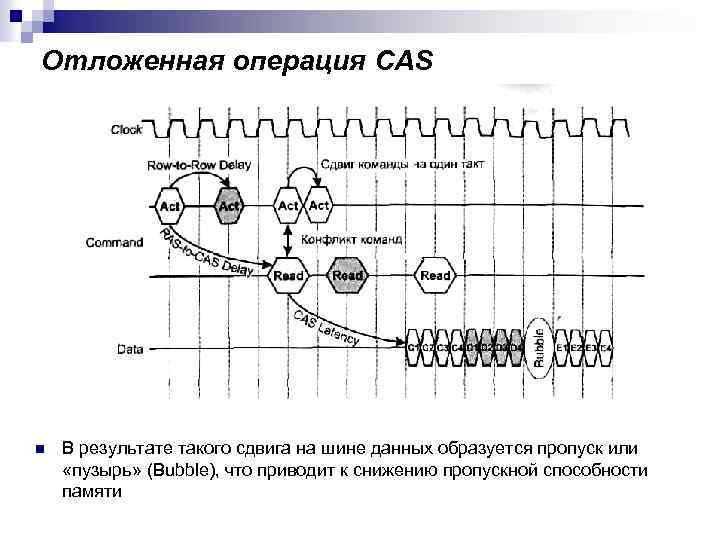

Отложенная операция CAS n В результате такого сдвига на шине данных образуется пропуск или «пузырь» (Bubble), что приводит к снижению пропускной способности памяти

Отложенная операция CAS n В результате такого сдвига на шине данных образуется пропуск или «пузырь» (Bubble), что приводит к снижению пропускной способности памяти

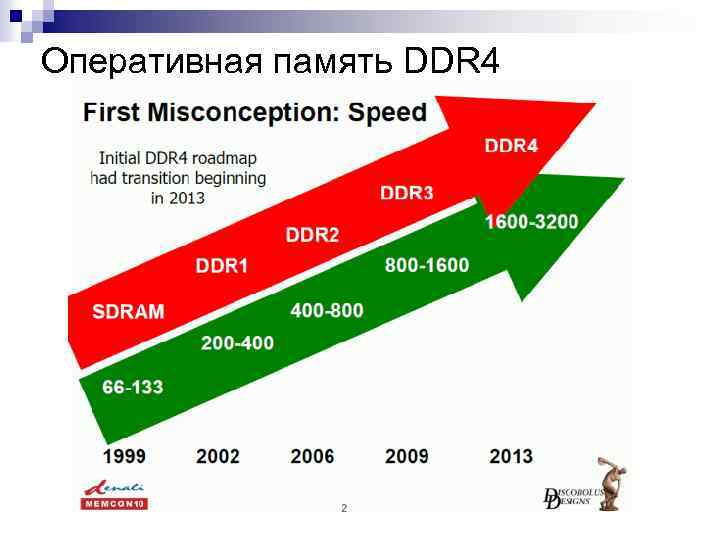

Оперативная память DDR 4 n n Появление нового стандарта оперативной памяти DDR 4 уже не за горами. По прогнозам экспертов JEDEC Solid State Technology Association (ранее Joint Electron Devices Engineering Council), независимой индустриальной организации по разработке и принятию стандартов в полупроводниковой промышленности, первые прототипы модулей DDR 4 SDRAM появятся уже в следующем году, когда будут оформлены окончательные спецификации стандарта. Начало массового коммерческого производства DDR 4 сейчас планируется на 2012 год, а полномасштабный переход с DDR 3 на DDR 4 ожидается ближе к 2015 году. До недавнего времени о стандарте DDR 4, впервые представленном на форуме Intel для разработчиков в Сан-Франциско в 2008 году, было известно относительно немного. В целом, обсуждались грядущие тактовые частоты, напряжение питания да предполагаемые нормы техпроцесса. Никакой особой конкретики по архитектуре чипов, топологии интерфейсов или сигнальным параметрам не было. По большому счёту, полной ясности в этих вопросах нет и сейчас, однако конференции Denali Mem. Con 10 и Mem. Con Tokyo 2010, прошедшие в конце июля в Санта Клара и Токио, добавили некоторой определённости будущему стандарту.

Оперативная память DDR 4 n n Появление нового стандарта оперативной памяти DDR 4 уже не за горами. По прогнозам экспертов JEDEC Solid State Technology Association (ранее Joint Electron Devices Engineering Council), независимой индустриальной организации по разработке и принятию стандартов в полупроводниковой промышленности, первые прототипы модулей DDR 4 SDRAM появятся уже в следующем году, когда будут оформлены окончательные спецификации стандарта. Начало массового коммерческого производства DDR 4 сейчас планируется на 2012 год, а полномасштабный переход с DDR 3 на DDR 4 ожидается ближе к 2015 году. До недавнего времени о стандарте DDR 4, впервые представленном на форуме Intel для разработчиков в Сан-Франциско в 2008 году, было известно относительно немного. В целом, обсуждались грядущие тактовые частоты, напряжение питания да предполагаемые нормы техпроцесса. Никакой особой конкретики по архитектуре чипов, топологии интерфейсов или сигнальным параметрам не было. По большому счёту, полной ясности в этих вопросах нет и сейчас, однако конференции Denali Mem. Con 10 и Mem. Con Tokyo 2010, прошедшие в конце июля в Санта Клара и Токио, добавили некоторой определённости будущему стандарту.

Оперативная память DDR 4

Оперативная память DDR 4

Оперативная память DDR 4

Оперативная память DDR 4

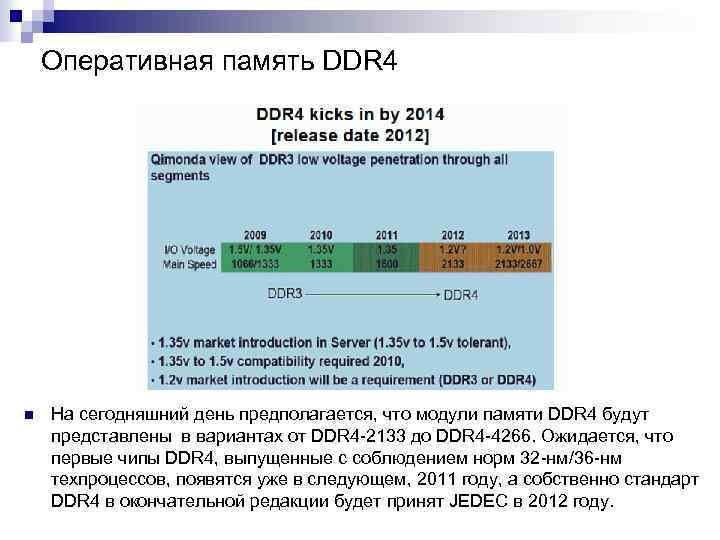

Оперативная память DDR 4 n Таким образом, при наличии сертифицированных стандартных модулей DDR 3 -2133 появление памяти стандарта DDR 4 -1600 попросту теряет всякий смысл. Современный, более реалистичный роадмэп, озвученный на конференции Mem. Con 10, предполагает, что в рамках стандарта DDR 4 скорость модулей составит от DDR 4 -2133 до DDR 4 -4266. n Однако растущая производительность – не единственный "козырь", продлевающий жизнь стандарта DDR 3 и отдаляющий появление DDR 4. Ещё один важный момент – энергопотребление, напрямую связанное с напряжением питания чипов памяти. Первоначально предполагалось, что напряжение питания новой памяти DDR 4 составит 1, 2 В, и затем появятся новые поколения чипов с питающим напряжением 1, 1 В и 1, 05 В. В то же время, для DDR 3, впервые представленной в 1, 5 В варианте, экспансия должна была закончиться на нынешних 1, 35 В чипах. Однако выпуск низковольтной памяти DDR 3 с напряжением питания всего 1, 25 В делает появление 1, 2 В памяти DDR 4 преждевременным, так как более высокие частоты работы памяти значительно увеличивают энергопотребление.

Оперативная память DDR 4 n Таким образом, при наличии сертифицированных стандартных модулей DDR 3 -2133 появление памяти стандарта DDR 4 -1600 попросту теряет всякий смысл. Современный, более реалистичный роадмэп, озвученный на конференции Mem. Con 10, предполагает, что в рамках стандарта DDR 4 скорость модулей составит от DDR 4 -2133 до DDR 4 -4266. n Однако растущая производительность – не единственный "козырь", продлевающий жизнь стандарта DDR 3 и отдаляющий появление DDR 4. Ещё один важный момент – энергопотребление, напрямую связанное с напряжением питания чипов памяти. Первоначально предполагалось, что напряжение питания новой памяти DDR 4 составит 1, 2 В, и затем появятся новые поколения чипов с питающим напряжением 1, 1 В и 1, 05 В. В то же время, для DDR 3, впервые представленной в 1, 5 В варианте, экспансия должна была закончиться на нынешних 1, 35 В чипах. Однако выпуск низковольтной памяти DDR 3 с напряжением питания всего 1, 25 В делает появление 1, 2 В памяти DDR 4 преждевременным, так как более высокие частоты работы памяти значительно увеличивают энергопотребление.

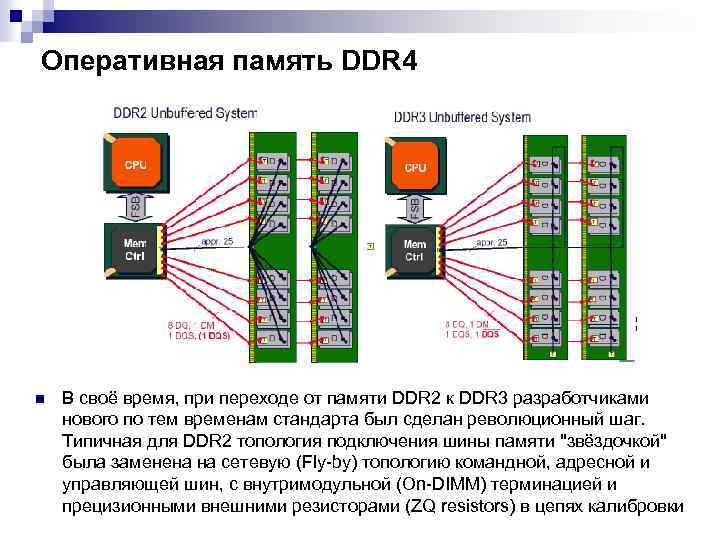

Оперативная память DDR 4 n В своё время, при переходе от памяти DDR 2 к DDR 3 разработчиками нового по тем временам стандарта был сделан революционный шаг. Типичная для DDR 2 топология подключения шины памяти "звёздочкой" была заменена на сетевую (Fly-by) топологию командной, адресной и управляющей шин, с внутримодульной (On-DIMM) терминацией и прецизионными внешними резисторами (ZQ resistors) в цепях калибровки

Оперативная память DDR 4 n В своё время, при переходе от памяти DDR 2 к DDR 3 разработчиками нового по тем временам стандарта был сделан революционный шаг. Типичная для DDR 2 топология подключения шины памяти "звёздочкой" была заменена на сетевую (Fly-by) топологию командной, адресной и управляющей шин, с внутримодульной (On-DIMM) терминацией и прецизионными внешними резисторами (ZQ resistors) в цепях калибровки

Оперативная память DDR 4 n n Однако сколько верёвочке не виться, а шине с многоточечной топологией линий передач данных всё же приходит конец, как он давным-давно пришёл для графической памяти GDDR. Не те нынче скорости, не те потребности в объёмах передаваемых данных. Применительно к стандарту DDR 4 это означает, что место многоточечной топологии займут соединения типа "точка-точка", иначе не добиться значительного прироста производительности.

Оперативная память DDR 4 n n Однако сколько верёвочке не виться, а шине с многоточечной топологией линий передач данных всё же приходит конец, как он давным-давно пришёл для графической памяти GDDR. Не те нынче скорости, не те потребности в объёмах передаваемых данных. Применительно к стандарту DDR 4 это означает, что место многоточечной топологии займут соединения типа "точка-точка", иначе не добиться значительного прироста производительности.

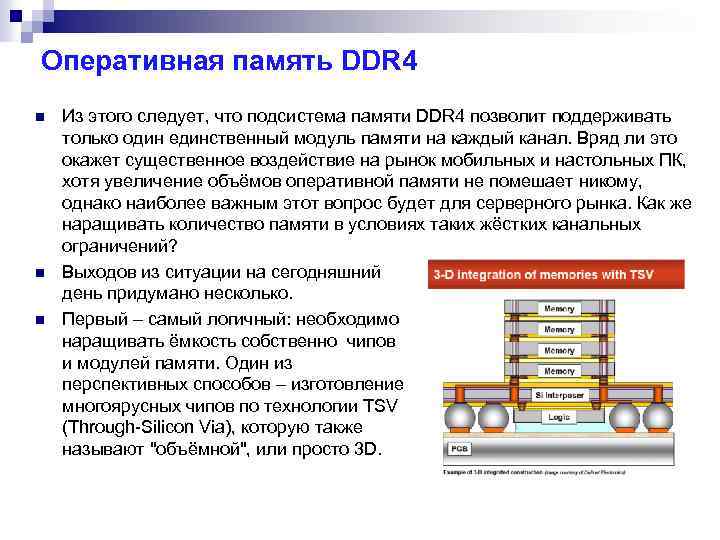

Оперативная память DDR 4 n n n Из этого следует, что подсистема памяти DDR 4 позволит поддерживать только один единственный модуль памяти на каждый канал. Вряд ли это окажет существенное воздействие на рынок мобильных и настольных ПК, хотя увеличение объёмов оперативной памяти не помешает никому, однако наиболее важным этот вопрос будет для серверного рынка. Как же наращивать количество памяти в условиях таких жёстких канальных ограничений? Выходов из ситуации на сегодняшний день придумано несколько. Первый – самый логичный: необходимо наращивать ёмкость собственно чипов и модулей памяти. Один из перспективных способов – изготовление многоярусных чипов по технологии TSV (Through-Silicon Via), которую также называют "объёмной", или просто 3 D.

Оперативная память DDR 4 n n n Из этого следует, что подсистема памяти DDR 4 позволит поддерживать только один единственный модуль памяти на каждый канал. Вряд ли это окажет существенное воздействие на рынок мобильных и настольных ПК, хотя увеличение объёмов оперативной памяти не помешает никому, однако наиболее важным этот вопрос будет для серверного рынка. Как же наращивать количество памяти в условиях таких жёстких канальных ограничений? Выходов из ситуации на сегодняшний день придумано несколько. Первый – самый логичный: необходимо наращивать ёмкость собственно чипов и модулей памяти. Один из перспективных способов – изготовление многоярусных чипов по технологии TSV (Through-Silicon Via), которую также называют "объёмной", или просто 3 D.

Оперативная память DDR 4 n Ещё один хорошо известный и уже зарекомендовавший себя способ использование техники так называемой "разгружающей памяти" - LRDIMM (Load-Reduce DIMM). Суть идеи состоит в том, что в состав модуля памяти LR-DIMM входит специальный чип (или несколько чипов), буферизирующих все сигналы шины и позволяющих увеличить количество поддерживаемой системой памяти.

Оперативная память DDR 4 n Ещё один хорошо известный и уже зарекомендовавший себя способ использование техники так называемой "разгружающей памяти" - LRDIMM (Load-Reduce DIMM). Суть идеи состоит в том, что в состав модуля памяти LR-DIMM входит специальный чип (или несколько чипов), буферизирующих все сигналы шины и позволяющих увеличить количество поддерживаемой системой памяти.

Оперативная память DDR 4 n n n Уже сейчас, задолго до появления первых модулей памяти DDR 4 SDRAM на прилавках наших магазинов, можно уверенно сказать: процесс перехода с DDR 3 на DDR 4 будет более сложным и более продолжительным, нежели в своё время переход с DDR 2 на DDR 3, который, как мы все помним, тоже был не сахар и закончился совсем недавно. Тяжелее придётся всем – и производителям чипов, и производителям модулей памяти. За счёт изменения топологии и архитектуры памяти сложнее придётся и производителям системных плат, и системным интеграторам. Разумеется, достанется и нам, конечным пользователям, которые в итоге оплатят весь этот "праздник" перехода на новые стандарты из своего кошелька. Отчасти переход на новый тип памяти тормозится технической неготовностью индустрии к выпуску DDR 4. Например, чтобы выпускать чипы памяти DDR 4 с напряжением питания хотя бы 1, 2 В, необходимо сначала толком осилить 30 нм техпроцесс, а ведь в результате получится не самый экономичный чип даже по сравнению с нынешними 1, 25 В вариантами DDR 3 из-за более высокого энергопотребления на более высоких рабочих частотах. Меньшее напряжение питания транзисторных ядер, и, соответственно, меньшее энергопотребление чипов будут реальны только с освоением примерно 20 -нм норм техпроцесса, что произойдёт не ранее 2012 -2013 годов.

Оперативная память DDR 4 n n n Уже сейчас, задолго до появления первых модулей памяти DDR 4 SDRAM на прилавках наших магазинов, можно уверенно сказать: процесс перехода с DDR 3 на DDR 4 будет более сложным и более продолжительным, нежели в своё время переход с DDR 2 на DDR 3, который, как мы все помним, тоже был не сахар и закончился совсем недавно. Тяжелее придётся всем – и производителям чипов, и производителям модулей памяти. За счёт изменения топологии и архитектуры памяти сложнее придётся и производителям системных плат, и системным интеграторам. Разумеется, достанется и нам, конечным пользователям, которые в итоге оплатят весь этот "праздник" перехода на новые стандарты из своего кошелька. Отчасти переход на новый тип памяти тормозится технической неготовностью индустрии к выпуску DDR 4. Например, чтобы выпускать чипы памяти DDR 4 с напряжением питания хотя бы 1, 2 В, необходимо сначала толком осилить 30 нм техпроцесс, а ведь в результате получится не самый экономичный чип даже по сравнению с нынешними 1, 25 В вариантами DDR 3 из-за более высокого энергопотребления на более высоких рабочих частотах. Меньшее напряжение питания транзисторных ядер, и, соответственно, меньшее энергопотребление чипов будут реальны только с освоением примерно 20 -нм норм техпроцесса, что произойдёт не ранее 2012 -2013 годов.