Вычислительные машины, системы и сети.ppt

- Количество слайдов: 27

Вычислительные машины, системы и сети Кафедра Вычислительной техники Вл. ГУ Туляков Валерий Станиславович LOGO Edit your company slogan

Вычислительные машины, системы и сети Кафедра Вычислительной техники Вл. ГУ Туляков Валерий Станиславович LOGO Edit your company slogan

Литература для подготовки - В. Л. Бройдо, О. П. Ильина Вычислительные системы, сети и телекоммуникации: Учебник для вузов. 4 -е изд. - СПб. : Питер, 2011. - 560 с. - Максимов Н. В. , Партыка Т. Л. , Попов И. И. Архитектура ЭВМ и вычислительных систем: Учебник. - 3 -е изд. , перераб. и доп. - М. : Форум, 2010. -512. : ил. - Таненбаум Э. Архитектура компьютера. 4 -изд. - СПб. : Питер, 2005. - 699 с. : ил. - Орлов С. А. , Цилькер Б. Я. Организация ЭВМ и систем: Учебник для вузов. 2 -е изд. -СПб: Питер, 2011. - 688 с. - Асманов С. , Пахомов С. Железо 2011. Компьютер Пресс рекомендует. - СПб. : Питер, 2011. - 512 с. LOGO www. themegallery. com

Литература для подготовки - В. Л. Бройдо, О. П. Ильина Вычислительные системы, сети и телекоммуникации: Учебник для вузов. 4 -е изд. - СПб. : Питер, 2011. - 560 с. - Максимов Н. В. , Партыка Т. Л. , Попов И. И. Архитектура ЭВМ и вычислительных систем: Учебник. - 3 -е изд. , перераб. и доп. - М. : Форум, 2010. -512. : ил. - Таненбаум Э. Архитектура компьютера. 4 -изд. - СПб. : Питер, 2005. - 699 с. : ил. - Орлов С. А. , Цилькер Б. Я. Организация ЭВМ и систем: Учебник для вузов. 2 -е изд. -СПб: Питер, 2011. - 688 с. - Асманов С. , Пахомов С. Железо 2011. Компьютер Пресс рекомендует. - СПб. : Питер, 2011. - 512 с. LOGO www. themegallery. com

Лекция № 1. Введение в курс § Термины согласно ISOIEC 23821 -93 и ГОСТ 15971 -90 Вычислительная машина – совокупность технических и программных средств, создающая возможность проведения обработки информации и получения результата в необходимой форме. Вычислительная система – одна или несколько ВМ, периферийное оборудование и программной обеспечение. LOGO www. themegallery. com

Лекция № 1. Введение в курс § Термины согласно ISOIEC 23821 -93 и ГОСТ 15971 -90 Вычислительная машина – совокупность технических и программных средств, создающая возможность проведения обработки информации и получения результата в необходимой форме. Вычислительная система – одна или несколько ВМ, периферийное оборудование и программной обеспечение. LOGO www. themegallery. com

Четыре принципа построения ВМ § Двоичное кодирование Вся информация (данные и команды) кодируются 0 и 1 в определенном формате. § Программное управление Алгоритм решения задачи записывается в виде программы – списка инструкций. § Однородность памяти Данные и команды для памяти одинаковы. § Адресуемость памяти Память представляет из себя список нумерованных ячеек. LOGO www. themegallery. com

Четыре принципа построения ВМ § Двоичное кодирование Вся информация (данные и команды) кодируются 0 и 1 в определенном формате. § Программное управление Алгоритм решения задачи записывается в виде программы – списка инструкций. § Однородность памяти Данные и команды для памяти одинаковы. § Адресуемость памяти Память представляет из себя список нумерованных ячеек. LOGO www. themegallery. com

Пристонская архитектура ВМ фон Неймана Память Ввод УУ АЛУ Вывод Акком. LOGO www. themegallery. com

Пристонская архитектура ВМ фон Неймана Память Ввод УУ АЛУ Вывод Акком. LOGO www. themegallery. com

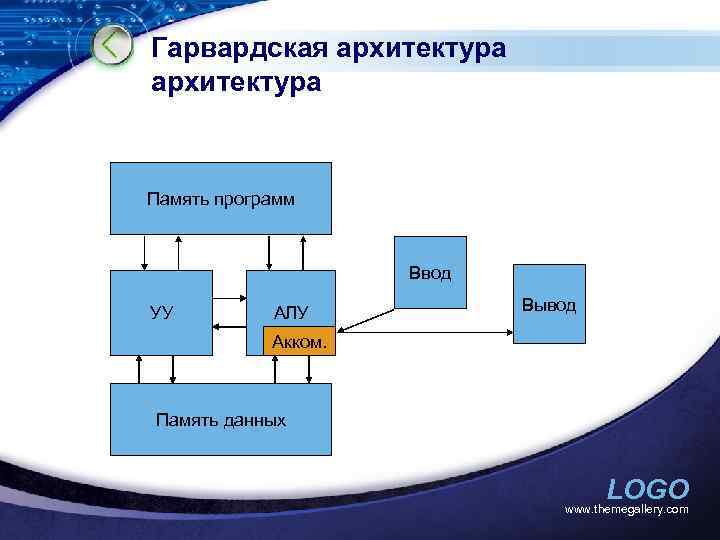

Гарвардская архитектура Память программ Ввод УУ АЛУ Вывод Акком. Память данных LOGO www. themegallery. com

Гарвардская архитектура Память программ Ввод УУ АЛУ Вывод Акком. Память данных LOGO www. themegallery. com

Понятия процесса и формата команды Формат команд 32 р ПРОЦЕСС Цикл процессора Чтение и запись Выборка из памяти очередной команды Код операции rs 1 rd операнд 6 Декодирование команды: определение преобразования, регистров операндов и регистра результата 0 16 Преобразование в АЛУ Код операции rs 1 rs 2 rd Функция 6 5 5 5 11 Переход Исполнение команды Запись в регистр результата 5 5 Код операции 6 Смещение 26 32 LOGO www. themegallery. com

Понятия процесса и формата команды Формат команд 32 р ПРОЦЕСС Цикл процессора Чтение и запись Выборка из памяти очередной команды Код операции rs 1 rd операнд 6 Декодирование команды: определение преобразования, регистров операндов и регистра результата 0 16 Преобразование в АЛУ Код операции rs 1 rs 2 rd Функция 6 5 5 5 11 Переход Исполнение команды Запись в регистр результата 5 5 Код операции 6 Смещение 26 32 LOGO www. themegallery. com

Аппаратная и микропрограммная реализация вычислений § Аппаратная X Ч Вычислитель Требует построения уникальной схемы, объединяющей функциональные устройства для вычисления каждой функции. F(x, y) Y память Xn Yn Вычислитель УУ Fn(Xn, Yn) Fn - Микропрограммная Использует универсальную схему функциональных устройств, а вычисление функций задается набором микрокоманд. LOGO www. themegallery. com

Аппаратная и микропрограммная реализация вычислений § Аппаратная X Ч Вычислитель Требует построения уникальной схемы, объединяющей функциональные устройства для вычисления каждой функции. F(x, y) Y память Xn Yn Вычислитель УУ Fn(Xn, Yn) Fn - Микропрограммная Использует универсальную схему функциональных устройств, а вычисление функций задается набором микрокоманд. LOGO www. themegallery. com

Элементная база § § Транзистор (Уильям Шокли, 1956 г. ) Интегральная схема (Роберт Нойс, 1958 г. ) СБИС микропроцессор (Intel 4004, 1971 г. ) С 1971 г. по 2011 г. развитие микропроцессоров. § Что нас ждет в ближайшее время ? LOGO www. themegallery. com

Элементная база § § Транзистор (Уильям Шокли, 1956 г. ) Интегральная схема (Роберт Нойс, 1958 г. ) СБИС микропроцессор (Intel 4004, 1971 г. ) С 1971 г. по 2011 г. развитие микропроцессоров. § Что нас ждет в ближайшее время ? LOGO www. themegallery. com

Направления совершенствования микропроцессоров 1. Технология – уменьшение размера транзистора до 25 нм. При уменьшении длины затвора транзистора В N раз ----Плотность размещения увеличивается в N 2. Скорость переключения транзистора увеличивается в N раз. Рассеиваемая мощность уменьшается в N 2. LOGO www. themegallery. com

Направления совершенствования микропроцессоров 1. Технология – уменьшение размера транзистора до 25 нм. При уменьшении длины затвора транзистора В N раз ----Плотность размещения увеличивается в N 2. Скорость переключения транзистора увеличивается в N раз. Рассеиваемая мощность уменьшается в N 2. LOGO www. themegallery. com

Направления совершенствования микропроцессоров § Увеличение частоты работы процессора. § Увеличение пропускной способности внешней шины (Quch. Path Interconnect – QPI 25. 6 Гбайт в сек. § Разрядность 64 р. § Уменьшение потребляемой мощности. § Увеличение количества процессоров на кристалле. § Совершенствование интерфейсов. § Специализация. LOGO www. themegallery. com

Направления совершенствования микропроцессоров § Увеличение частоты работы процессора. § Увеличение пропускной способности внешней шины (Quch. Path Interconnect – QPI 25. 6 Гбайт в сек. § Разрядность 64 р. § Уменьшение потребляемой мощности. § Увеличение количества процессоров на кристалле. § Совершенствование интерфейсов. § Специализация. LOGO www. themegallery. com

Многоуровневая организация ВМ с точки зрения взаимодействия человека и компьютера Что удобно для вычислительной машины, не удобно для человека Уровень n Виртуальная машина Мn Машинный язык Яn Уровень 2 Виртуальная машина М 2 Программа на Я 2 транслируется в Я 1 или Я 0 Машинный язык Я 2 Виртуальная машина М 1 Программа на Я 1 либо интерпрети. Уровень 1 руется либо транслируется на Я 0 Машинный язык Я 1 Уровень 0 Виртуальная машина М 0 Программа на Я 0 выполняются Машинный язык Я 0 электронными схемами Пользователь, пишущий программы для виртуальной машины уровня N, не обязан знать трансляторы или интерпретаторы более низких уровней LOGO www. themegallery. com

Многоуровневая организация ВМ с точки зрения взаимодействия человека и компьютера Что удобно для вычислительной машины, не удобно для человека Уровень n Виртуальная машина Мn Машинный язык Яn Уровень 2 Виртуальная машина М 2 Программа на Я 2 транслируется в Я 1 или Я 0 Машинный язык Я 2 Виртуальная машина М 1 Программа на Я 1 либо интерпрети. Уровень 1 руется либо транслируется на Я 0 Машинный язык Я 1 Уровень 0 Виртуальная машина М 0 Программа на Я 0 выполняются Машинный язык Я 0 электронными схемами Пользователь, пишущий программы для виртуальной машины уровня N, не обязан знать трансляторы или интерпретаторы более низких уровней LOGO www. themegallery. com

Современная многоуровневая вычислительная машина Уровень 5 Пользователь Уровень 4 Системный программист Уровень 3 Уровень 2 Система Команд и форматы д. Уровень 1 Функциональные узлы Уровень 0 базовые ЛЭИ , И-НЕ Язык высокого уровня Трансляция (компилятор) Уровень языка Ассемблер Уровень операционной системы Трансляция (Ассемблер) Уровень архитектуры команд Интерпретация или непосредственное исполнение Уровень Микро архитектуры Аппаратное обеспечение Цифровой логический уровень LOGO www. themegallery. com

Современная многоуровневая вычислительная машина Уровень 5 Пользователь Уровень 4 Системный программист Уровень 3 Уровень 2 Система Команд и форматы д. Уровень 1 Функциональные узлы Уровень 0 базовые ЛЭИ , И-НЕ Язык высокого уровня Трансляция (компилятор) Уровень языка Ассемблер Уровень операционной системы Трансляция (Ассемблер) Уровень архитектуры команд Интерпретация или непосредственное исполнение Уровень Микро архитектуры Аппаратное обеспечение Цифровой логический уровень LOGO www. themegallery. com

ВАЖНО ПОМНИТЬ!! § Аппаратное и программное обеспечение логически эквивалентны LOGO www. themegallery. com

ВАЖНО ПОМНИТЬ!! § Аппаратное и программное обеспечение логически эквивалентны LOGO www. themegallery. com

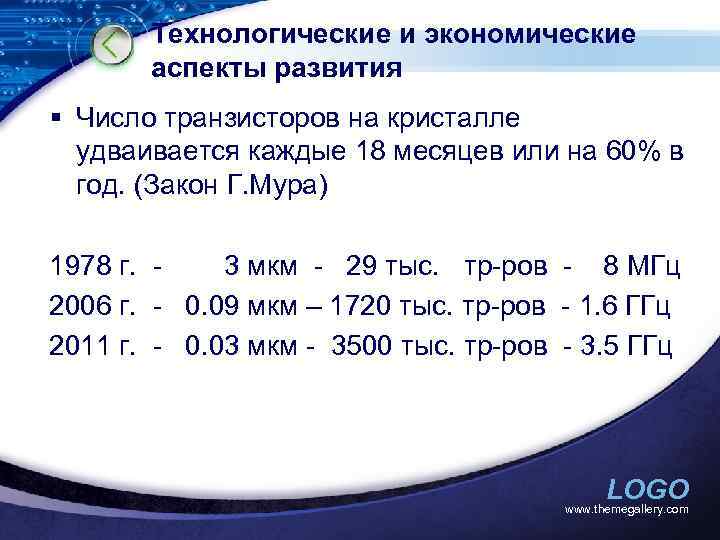

Технологические и экономические аспекты развития § Число транзисторов на кристалле удваивается каждые 18 месяцев или на 60% в год. (Закон Г. Мура) 1978 г. 3 мкм - 29 тыс. тр-ров - 8 МГц 2006 г. - 0. 09 мкм – 1720 тыс. тр-ров - 1. 6 ГГц 2011 г. - 0. 03 мкм - 3500 тыс. тр-ров - 3. 5 ГГц LOGO www. themegallery. com

Технологические и экономические аспекты развития § Число транзисторов на кристалле удваивается каждые 18 месяцев или на 60% в год. (Закон Г. Мура) 1978 г. 3 мкм - 29 тыс. тр-ров - 8 МГц 2006 г. - 0. 09 мкм – 1720 тыс. тр-ров - 1. 6 ГГц 2011 г. - 0. 03 мкм - 3500 тыс. тр-ров - 3. 5 ГГц LOGO www. themegallery. com

Типы компьютеров, стоимость и рынок Тип $ Сфера Одноразовые 1 Открытки Встроенные 10 Приборы Игровые 100 Игровые приставки Персональные 1000 Настольные и портативные Серверы 10 000 Сетевые серверы Рабочие станции 100 000 Мини-суперкомпьютер Большие ЭВМ 1 000 Банковские Супер ЭВМ 10 000 Аналитические LOGO www. themegallery. com

Типы компьютеров, стоимость и рынок Тип $ Сфера Одноразовые 1 Открытки Встроенные 10 Приборы Игровые 100 Игровые приставки Персональные 1000 Настольные и портативные Серверы 10 000 Сетевые серверы Рабочие станции 100 000 Мини-суперкомпьютер Большие ЭВМ 1 000 Банковские Супер ЭВМ 10 000 Аналитические LOGO www. themegallery. com

Быстродействие и производительность Номинальное быстродействие - время выполнения стандартной операции Среднее быстродействие Количество операций в алгоритме Время выполнения эталонного алгоритма LOGO www. themegallery. com

Быстродействие и производительность Номинальное быстродействие - время выполнения стандартной операции Среднее быстродействие Количество операций в алгоритме Время выполнения эталонного алгоритма LOGO www. themegallery. com

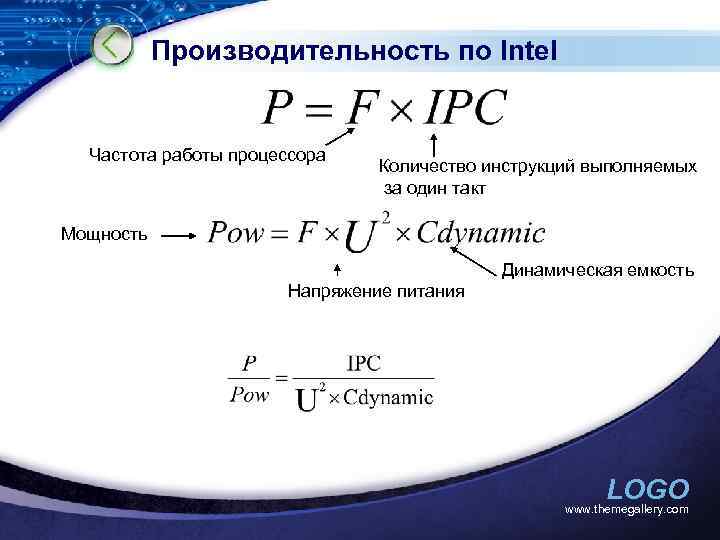

Производительность по Intel Частота работы процессора Количество инструкций выполняемых за один такт Мощность Динамическая емкость Напряжение питания LOGO www. themegallery. com

Производительность по Intel Частота работы процессора Количество инструкций выполняемых за один такт Мощность Динамическая емкость Напряжение питания LOGO www. themegallery. com

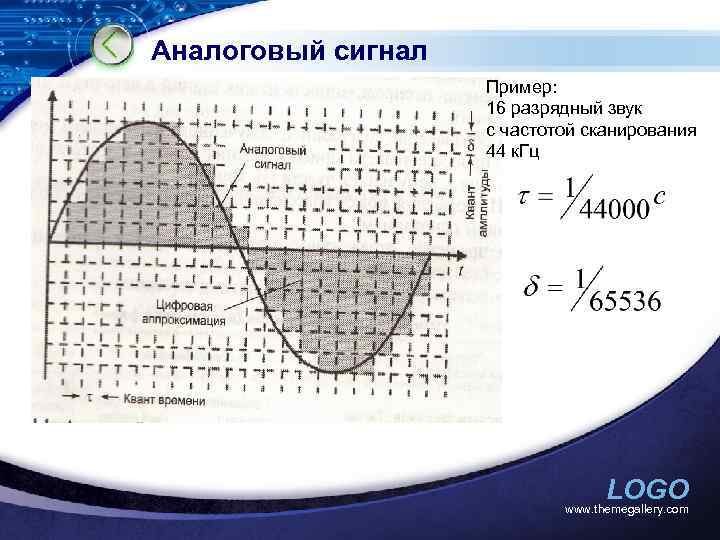

Аналоговый сигнал Пример: 16 разрядный звук с частотой сканирования 44 к. Гц LOGO www. themegallery. com

Аналоговый сигнал Пример: 16 разрядный звук с частотой сканирования 44 к. Гц LOGO www. themegallery. com

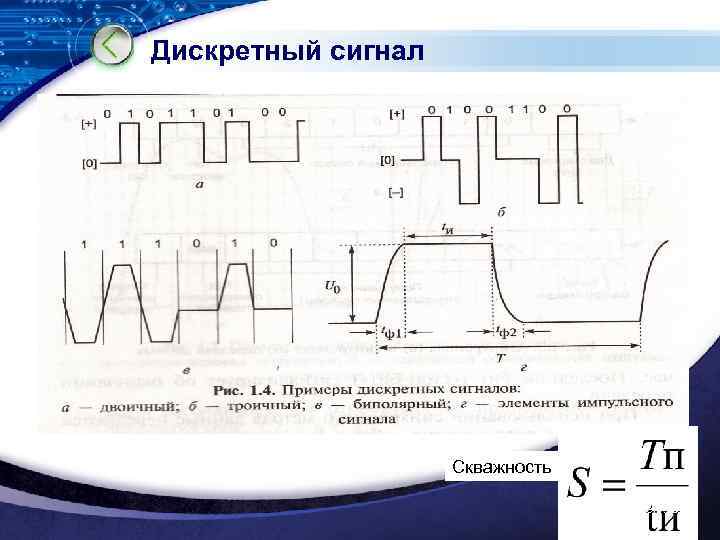

Дискретный сигнал Скважность LOGO www. themegallery. com

Дискретный сигнал Скважность LOGO www. themegallery. com

Передача данных § Канал передачи – комплекс технических средств и среда распространения, обеспечивающие передачу данных с определенной скоростью в заданном формате от передатчика к приемнику. Симплексная Синхронная Последовательная Дуплексная Асинхронная Параллельная Полудуплексная LOGO www. themegallery. com

Передача данных § Канал передачи – комплекс технических средств и среда распространения, обеспечивающие передачу данных с определенной скоростью в заданном формате от передатчика к приемнику. Симплексная Синхронная Последовательная Дуплексная Асинхронная Параллельная Полудуплексная LOGO www. themegallery. com

Измерение количества информации Бит ввел в обращение Клод Шеннон LOGO www. themegallery. com

Измерение количества информации Бит ввел в обращение Клод Шеннон LOGO www. themegallery. com

Архитектуры вычислительных машин - централизованная ОП ЦП ВУ ВУ ВУ LOGO www. themegallery. com

Архитектуры вычислительных машин - централизованная ОП ЦП ВУ ВУ ВУ LOGO www. themegallery. com

Архитектуры вычислительных машин - иерархическая ОП ЦП Канальный процессор ВУ ВУ LOGO www. themegallery. com

Архитектуры вычислительных машин - иерархическая ОП ЦП Канальный процессор ВУ ВУ LOGO www. themegallery. com

Архитектуры вычислительных машин - магистральная ЦП ОЗУ ISA Порт Контр. RS-232 Контр. видео ПДП 33 Мбайтс Контр. МД Контр. ГМД LOGO www. themegallery. com

Архитектуры вычислительных машин - магистральная ЦП ОЗУ ISA Порт Контр. RS-232 Контр. видео ПДП 33 Мбайтс Контр. МД Контр. ГМД LOGO www. themegallery. com

Архитектуры вычислительных машин магистральная мостовая Шина КЭШ памяти Кэш память второго уровня Шина памяти Мост PCI ЦП Шина PCI SCSI USB Мышь Модем Графический адаптер Монитор Кл. Звук Мост ISA ОЗУ Принтер Шина ISA LOGO www. themegallery. com

Архитектуры вычислительных машин магистральная мостовая Шина КЭШ памяти Кэш память второго уровня Шина памяти Мост PCI ЦП Шина PCI SCSI USB Мышь Модем Графический адаптер Монитор Кл. Звук Мост ISA ОЗУ Принтер Шина ISA LOGO www. themegallery. com

Компоненты вычислительной системы Центральный процессор Память АЛУ ОЗУ УУ Регистры Интерфейсы Внешние устройства Внут. Внеш. Ув-в DRAM ISA RS 232 ЗУ SRAM IDE LPT PCI USB PCIE Blu HT FW ПЗУ LOGO www. themegallery. com

Компоненты вычислительной системы Центральный процессор Память АЛУ ОЗУ УУ Регистры Интерфейсы Внешние устройства Внут. Внеш. Ув-в DRAM ISA RS 232 ЗУ SRAM IDE LPT PCI USB PCIE Blu HT FW ПЗУ LOGO www. themegallery. com