ВТ_2 часть.ppt

- Количество слайдов: 61

Вторая часть рассматривает вопросы структуры и архитектуры микропроцессоров Рекомендуемая литература: В основе построения микропроцессорных систем (МПС) обработки информации лежит модульный принцип. Модулем микропроцессорной системы является её функциональный блок, выполненный в виде конструктивно законченного устройства – обычно в виде одной или нескольких БИС либо в виде плат. Модули соединяются между собой посредством специальных устройств, называемых интерфейсами. Основными модулями МПС являются однокристальный микропроцессор (МП), постоянная и оперативная (основная) памяти, устройства ввода-вывода информации и блоки управления (контроллеры).

Вторая часть рассматривает вопросы структуры и архитектуры микропроцессоров Рекомендуемая литература: В основе построения микропроцессорных систем (МПС) обработки информации лежит модульный принцип. Модулем микропроцессорной системы является её функциональный блок, выполненный в виде конструктивно законченного устройства – обычно в виде одной или нескольких БИС либо в виде плат. Модули соединяются между собой посредством специальных устройств, называемых интерфейсами. Основными модулями МПС являются однокристальный микропроцессор (МП), постоянная и оперативная (основная) памяти, устройства ввода-вывода информации и блоки управления (контроллеры).

• • • Суть проектирования микропроцессорных систем на основе выбранного однокристального микропроцессора состоит в следующем: выбор внешних устройств, предназначенных для связи МП с устройствами ввода-вывода информации; организация связи этих устройств с микропроцессором; выбор ёмкости памяти для размещения программы и промежуточных данных, а также способа её организации; программирование МП на выполнение требуемых функций при известной конфигурации МПС с использованием системы команд МП. Эти вопросы мы и рассмотрим в данной части курса ЦУ и МП. 7. ПРИНЦИПЫ УПРАВЛЕНИЯ МИКРОПРОЦЕССОРА. 7. 1. Классификация микропроцессоров. • • • Микропроцессором называется функционально законченное программно-управляемое устройство обработки цифровой информации. Числовая информация, заданная для обработки, называется данными. Физически микропроцессоры (МП) выпускаются в виде одной или нескольких больших или сверхбольших интегральных схем (БИС или СБИС), содержащих на одном кристалле сотни тысяч элементарных транзисторов.

• • • Суть проектирования микропроцессорных систем на основе выбранного однокристального микропроцессора состоит в следующем: выбор внешних устройств, предназначенных для связи МП с устройствами ввода-вывода информации; организация связи этих устройств с микропроцессором; выбор ёмкости памяти для размещения программы и промежуточных данных, а также способа её организации; программирование МП на выполнение требуемых функций при известной конфигурации МПС с использованием системы команд МП. Эти вопросы мы и рассмотрим в данной части курса ЦУ и МП. 7. ПРИНЦИПЫ УПРАВЛЕНИЯ МИКРОПРОЦЕССОРА. 7. 1. Классификация микропроцессоров. • • • Микропроцессором называется функционально законченное программно-управляемое устройство обработки цифровой информации. Числовая информация, заданная для обработки, называется данными. Физически микропроцессоры (МП) выпускаются в виде одной или нескольких больших или сверхбольших интегральных схем (БИС или СБИС), содержащих на одном кристалле сотни тысяч элементарных транзисторов.

МП дополняются БИС для хранения, ввода-вывода данных, управления и синхронизации, сопряжения интерфейсов и т. п. Эти БИС совместимы с МП по архитектуре, конструктивному исполнению и параметрам. Такие наборы БИС называются микропроцессорными комплектами (МПК). МП можно классифицировать по весьма большому числу характеристик. Мы воспользуемся одним из возможных вариантов классификации. По назначению различают универсальные и специализированные микропроцессоры. Универсальные МП могут осуществить преобразование информации в соответствии с любым заданным алгоритмом. Специализированные МП предназначены для решения определённого класса задач и даже, может быть, для решения одной конкретной задачи. Их особенностью являются низкая стоимость, малая потребляемая мощность, компактность, простота управления. Среди специализированных МП выделяют микроконтроллеры, используемые в управлении технологическими процессами, измерениях, научных исследованиях. Их отличительной чертой является работа в реальном масштабе времени. По числу БИС различают секционные (разрядно-модульные) и однокристальные МП. Микропроцессорная секция (модуль) представляет собой БИС для обработки небольшого числа разрядов данных (4 или 8). Такие МП обладают возможностью наращивания разрядности, что позволяет на их основе строить МП произвольной разрядности. Кроме того, секционные МП не имеют фиксированного набора команд, а программируются на микрокомандном уровне. Это позволяет реализовать оптимальный для данной задачи набор команд и отдельных процедур.

МП дополняются БИС для хранения, ввода-вывода данных, управления и синхронизации, сопряжения интерфейсов и т. п. Эти БИС совместимы с МП по архитектуре, конструктивному исполнению и параметрам. Такие наборы БИС называются микропроцессорными комплектами (МПК). МП можно классифицировать по весьма большому числу характеристик. Мы воспользуемся одним из возможных вариантов классификации. По назначению различают универсальные и специализированные микропроцессоры. Универсальные МП могут осуществить преобразование информации в соответствии с любым заданным алгоритмом. Специализированные МП предназначены для решения определённого класса задач и даже, может быть, для решения одной конкретной задачи. Их особенностью являются низкая стоимость, малая потребляемая мощность, компактность, простота управления. Среди специализированных МП выделяют микроконтроллеры, используемые в управлении технологическими процессами, измерениях, научных исследованиях. Их отличительной чертой является работа в реальном масштабе времени. По числу БИС различают секционные (разрядно-модульные) и однокристальные МП. Микропроцессорная секция (модуль) представляет собой БИС для обработки небольшого числа разрядов данных (4 или 8). Такие МП обладают возможностью наращивания разрядности, что позволяет на их основе строить МП произвольной разрядности. Кроме того, секционные МП не имеют фиксированного набора команд, а программируются на микрокомандном уровне. Это позволяет реализовать оптимальный для данной задачи набор команд и отдельных процедур.

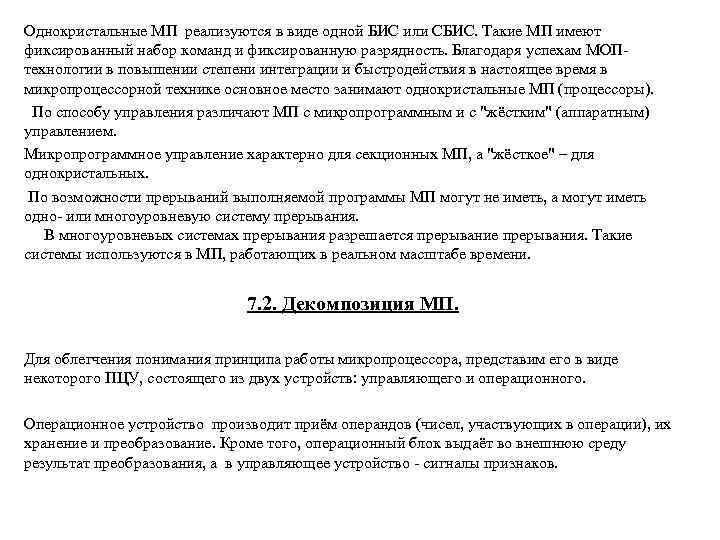

Однокристальные МП реализуются в виде одной БИС или СБИС. Такие МП имеют фиксированный набор команд и фиксированную разрядность. Благодаря успехам МОПтехнологии в повышении степени интеграции и быстродействия в настоящее время в микропроцессорной технике основное место занимают однокристальные МП (процессоры). По способу управления различают МП с микропрограммным и с "жёстким" (аппаратным) управлением. Микропрограммное управление характерно для секционных МП, а "жёсткое" – для однокристальных. По возможности прерываний выполняемой программы МП могут не иметь, а могут иметь одно- или многоуровневую систему прерывания. В многоуровневых системах прерывания разрешается прерывание прерывания. Такие системы используются в МП, работающих в реальном масштабе времени. 7. 2. Декомпозиция МП. Для облегчения понимания принципа работы микропроцессора, представим его в виде некоторого ПЦУ, состоящего из двух устройств: управляющего и операционного. Операционное устройство производит приём операндов (чисел, участвующих в операции), их хранение и преобразование. Кроме того, операционный блок выдаёт во внешнюю среду результат преобразования, а в управляющее устройство - сигналы признаков.

Однокристальные МП реализуются в виде одной БИС или СБИС. Такие МП имеют фиксированный набор команд и фиксированную разрядность. Благодаря успехам МОПтехнологии в повышении степени интеграции и быстродействия в настоящее время в микропроцессорной технике основное место занимают однокристальные МП (процессоры). По способу управления различают МП с микропрограммным и с "жёстким" (аппаратным) управлением. Микропрограммное управление характерно для секционных МП, а "жёсткое" – для однокристальных. По возможности прерываний выполняемой программы МП могут не иметь, а могут иметь одно- или многоуровневую систему прерывания. В многоуровневых системах прерывания разрешается прерывание прерывания. Такие системы используются в МП, работающих в реальном масштабе времени. 7. 2. Декомпозиция МП. Для облегчения понимания принципа работы микропроцессора, представим его в виде некоторого ПЦУ, состоящего из двух устройств: управляющего и операционного. Операционное устройство производит приём операндов (чисел, участвующих в операции), их хранение и преобразование. Кроме того, операционный блок выдаёт во внешнюю среду результат преобразования, а в управляющее устройство - сигналы признаков.

Сигналы признаков (флаги) несут информацию об особенностях операндов и их отдельных разрядов, а также особенностях промежуточных и конечных результатов обработки (например, равенство нулю, чётность результата, переполнение разрядной сетки и др. ). Управляющее устройство, в зависимости от кода операции и сигналов признаков вырабатывает сигналы управления, обеспечивающие выполнение заданной операции. Процесс функционирования МП во времени состоит из последовательности элементарных операций. Например, передача кодового слова от одного узла МП к другому, поразрядное инвертирование слова, сдвиг и др. Элементарная операция выполняется за один такт синхросигнала и называется микрооперацией. В течение такта может быть выполнено несколько микроопераций, но только если результат выполнения каждой из них не зависит от результатов выполнения остальных. Элементарные преобразования информации производятся операционным блоком под воздействием управляющих сигналов. Совокупность управляющих сигналов, обеспечивающих выполнение микроопераций в течение одного тактового интервала, называется микрокомандой.

Сигналы признаков (флаги) несут информацию об особенностях операндов и их отдельных разрядов, а также особенностях промежуточных и конечных результатов обработки (например, равенство нулю, чётность результата, переполнение разрядной сетки и др. ). Управляющее устройство, в зависимости от кода операции и сигналов признаков вырабатывает сигналы управления, обеспечивающие выполнение заданной операции. Процесс функционирования МП во времени состоит из последовательности элементарных операций. Например, передача кодового слова от одного узла МП к другому, поразрядное инвертирование слова, сдвиг и др. Элементарная операция выполняется за один такт синхросигнала и называется микрооперацией. В течение такта может быть выполнено несколько микроопераций, но только если результат выполнения каждой из них не зависит от результатов выполнения остальных. Элементарные преобразования информации производятся операционным блоком под воздействием управляющих сигналов. Совокупность управляющих сигналов, обеспечивающих выполнение микроопераций в течение одного тактового интервала, называется микрокомандой.

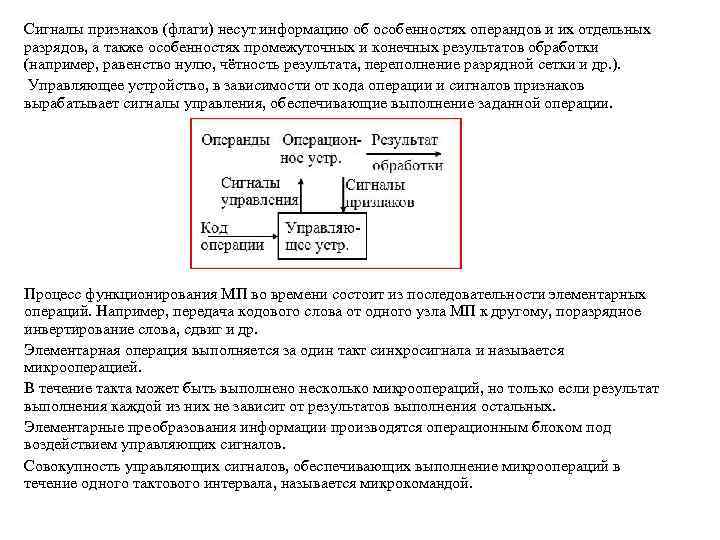

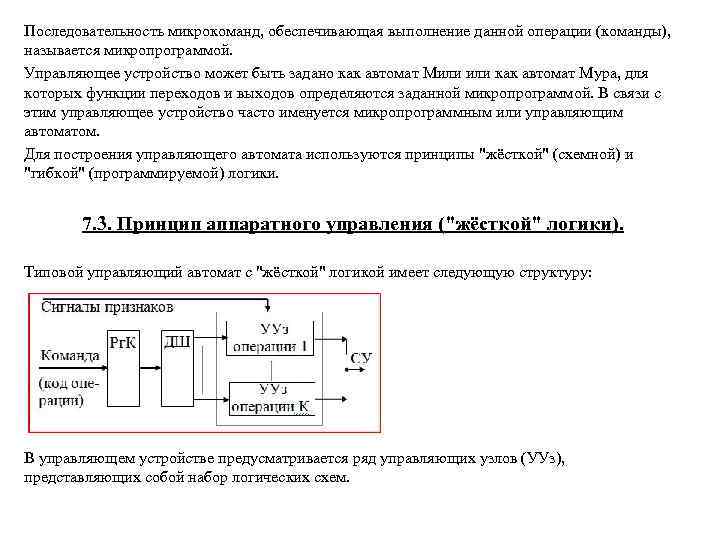

Последовательность микрокоманд, обеспечивающая выполнение данной операции (команды), называется микропрограммой. Управляющее устройство может быть задано как автомат Мили как автомат Мура, для которых функции переходов и выходов определяются заданной микропрограммой. В связи с этим управляющее устройство часто именуется микропрограммным или управляющим автоматом. Для построения управляющего автомата используются принципы "жёсткой" (схемной) и "гибкой" (программируемой) логики. 7. 3. Принцип аппаратного управления ("жёсткой" логики). Типовой управляющий автомат с "жёсткой" логикой имеет следующую структуру: В управляющем устройстве предусматривается ряд управляющих узлов (УУз), представляющих собой набор логических схем.

Последовательность микрокоманд, обеспечивающая выполнение данной операции (команды), называется микропрограммой. Управляющее устройство может быть задано как автомат Мили как автомат Мура, для которых функции переходов и выходов определяются заданной микропрограммой. В связи с этим управляющее устройство часто именуется микропрограммным или управляющим автоматом. Для построения управляющего автомата используются принципы "жёсткой" (схемной) и "гибкой" (программируемой) логики. 7. 3. Принцип аппаратного управления ("жёсткой" логики). Типовой управляющий автомат с "жёсткой" логикой имеет следующую структуру: В управляющем устройстве предусматривается ряд управляющих узлов (УУз), представляющих собой набор логических схем.

Команда, поступающая из внешнего ОЗУ, фиксируется в регистре команд (Рг. К) и с помощью дешифратора команд (ДШ) включает соответствующий управляющий узел. Управляющий узел вырабатывает определённую последовательность сигналов управления (СУ), обеспечивая выполнение данной операции операционным блоком. В общем случае значения сигналов управления зависят от сигналов признаков, отражающих ход вычислительного процесса. При таком способе построения управляющего автомата микропрограммы операций заложены в однажды выполненные соединения между логическими схемами управляющих узлов. Это означает, что набор команд или, иначе говоря, система команд фиксируется и соответствует числу выполняемых операций. Поэтому такие микропроцессоры называются с "жёсткой" логикой управления. Невозможность изменения системы команд после изготовления МП приводит к его узкой специализации. Вместе с тем МП с "жёсткой" логикой управления обеспечивает наивысшее быстродействие при заданной технологии изготовления. 7. 4. Принцип микропрограммного управления (гибкой логики). В управляющем автомате с "гибкой" логикой предусматриваются управляющая память (УП) и блок микропрограммного управления (БМУ): В УП для каждой операции содержится своя МКП. УП может быть постоянной или с произвольным обращением, т. е. допускающая как считывание, так и запись.

Команда, поступающая из внешнего ОЗУ, фиксируется в регистре команд (Рг. К) и с помощью дешифратора команд (ДШ) включает соответствующий управляющий узел. Управляющий узел вырабатывает определённую последовательность сигналов управления (СУ), обеспечивая выполнение данной операции операционным блоком. В общем случае значения сигналов управления зависят от сигналов признаков, отражающих ход вычислительного процесса. При таком способе построения управляющего автомата микропрограммы операций заложены в однажды выполненные соединения между логическими схемами управляющих узлов. Это означает, что набор команд или, иначе говоря, система команд фиксируется и соответствует числу выполняемых операций. Поэтому такие микропроцессоры называются с "жёсткой" логикой управления. Невозможность изменения системы команд после изготовления МП приводит к его узкой специализации. Вместе с тем МП с "жёсткой" логикой управления обеспечивает наивысшее быстродействие при заданной технологии изготовления. 7. 4. Принцип микропрограммного управления (гибкой логики). В управляющем автомате с "гибкой" логикой предусматриваются управляющая память (УП) и блок микропрограммного управления (БМУ): В УП для каждой операции содержится своя МКП. УП может быть постоянной или с произвольным обращением, т. е. допускающая как считывание, так и запись.

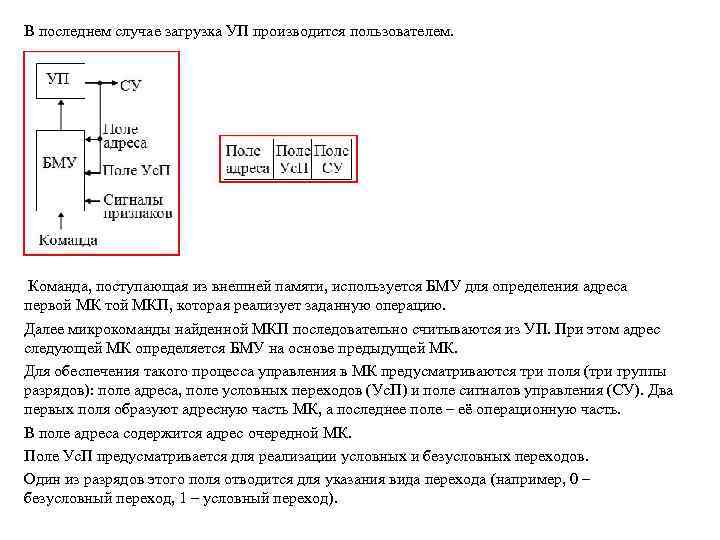

В последнем случае загрузка УП производится пользователем. Команда, поступающая из внешней памяти, используется БМУ для определения адреса первой МК той МКП, которая реализует заданную операцию. Далее микрокоманды найденной МКП последовательно считываются из УП. При этом адрес следующей МК определяется БМУ на основе предыдущей МК. Для обеспечения такого процесса управления в МК предусматриваются три поля (три группы разрядов): поле адреса, поле условных переходов (Ус. П) и поле сигналов управления (СУ). Два первых поля образуют адресную часть МК, а последнее поле – её операционную часть. В поле адреса содержится адрес очередной МК. Поле Ус. П предусматривается для реализации условных и безусловных переходов. Один из разрядов этого поля отводится для указания вида перехода (например, 0 – безусловный переход, 1 – условный переход).

В последнем случае загрузка УП производится пользователем. Команда, поступающая из внешней памяти, используется БМУ для определения адреса первой МК той МКП, которая реализует заданную операцию. Далее микрокоманды найденной МКП последовательно считываются из УП. При этом адрес следующей МК определяется БМУ на основе предыдущей МК. Для обеспечения такого процесса управления в МК предусматриваются три поля (три группы разрядов): поле адреса, поле условных переходов (Ус. П) и поле сигналов управления (СУ). Два первых поля образуют адресную часть МК, а последнее поле – её операционную часть. В поле адреса содержится адрес очередной МК. Поле Ус. П предусматривается для реализации условных и безусловных переходов. Один из разрядов этого поля отводится для указания вида перехода (например, 0 – безусловный переход, 1 – условный переход).

Ещё один разряд определяет участие данного вида перехода в определении адреса (например, 1 – участвует, 0 – не участвует). Остальные разряды используются для указания условий, на которые следует ориентироваться при определении адреса очередной МК. В результате в зависимости от условия образуются два различных адреса и очередная МК считывается из одной либо из другой ячейки УП. Рассмотренный способ управления получил название микропрограммного, а МП с управляющим автоматом на этом принципе называются МП с программируемой логикой. Достоинством такой организации управления является возможность гибкого изменения системы команд МП с помощью изменения совокупности МКП, реализующих эти команды. Отсюда второе название принципа – принцип "гибкой" логики. Вместе с тем использование принципа "гибкой" логики может привести к снижению быстродействия из-за увеличения числа тактов реализации микропрограммы. Микропрограммное управление используется не только в секционных МП, но и в устройствах управления периферийным оборудованием МПС, а также как средство для аппаратной реализации фрагментов операционных систем, трансляторов и т. д. Управляющие автоматы с "гибкой" логикой различаются по способу формирования сигналов управления.

Ещё один разряд определяет участие данного вида перехода в определении адреса (например, 1 – участвует, 0 – не участвует). Остальные разряды используются для указания условий, на которые следует ориентироваться при определении адреса очередной МК. В результате в зависимости от условия образуются два различных адреса и очередная МК считывается из одной либо из другой ячейки УП. Рассмотренный способ управления получил название микропрограммного, а МП с управляющим автоматом на этом принципе называются МП с программируемой логикой. Достоинством такой организации управления является возможность гибкого изменения системы команд МП с помощью изменения совокупности МКП, реализующих эти команды. Отсюда второе название принципа – принцип "гибкой" логики. Вместе с тем использование принципа "гибкой" логики может привести к снижению быстродействия из-за увеличения числа тактов реализации микропрограммы. Микропрограммное управление используется не только в секционных МП, но и в устройствах управления периферийным оборудованием МПС, а также как средство для аппаратной реализации фрагментов операционных систем, трансляторов и т. д. Управляющие автоматы с "гибкой" логикой различаются по способу формирования сигналов управления.

7. 5. Способы формирования сигналов управления в управляющих автоматах с "гибкой" логикой. Возможно горизонтальное, вертикальное и смешанное микропрограммирование. При горизонтальном микропрограммировании каждому разряду операционной части МК ставится в соответствие определённый управляющий сигнал, т. е. определённая микрооперация. Так, если в i-ом разряде стоит 1, то соответствующая микрооперация выполняется независимо от значения других разрядов. При таком способе операционная часть МК содержит m разрядов, где m – общее число микроопераций. Достоинствами горизонтального микропрограммирования являются возможность одновременного выполнения в одном такте любого набора микроопераций и простота формирования сигналов управления. Однако при этом требуется большая длина МК, поскольку число управляющих сигналов может достигать нескольких сотен. Поэтому большее распространение получили другие методы. При вертикальном микропрограммировании микрооперация определяется двоичным кодом, содержащимся в операционной части МК. При этом отдельный код задаёт отсутствие МКП.

7. 5. Способы формирования сигналов управления в управляющих автоматах с "гибкой" логикой. Возможно горизонтальное, вертикальное и смешанное микропрограммирование. При горизонтальном микропрограммировании каждому разряду операционной части МК ставится в соответствие определённый управляющий сигнал, т. е. определённая микрооперация. Так, если в i-ом разряде стоит 1, то соответствующая микрооперация выполняется независимо от значения других разрядов. При таком способе операционная часть МК содержит m разрядов, где m – общее число микроопераций. Достоинствами горизонтального микропрограммирования являются возможность одновременного выполнения в одном такте любого набора микроопераций и простота формирования сигналов управления. Однако при этом требуется большая длина МК, поскольку число управляющих сигналов может достигать нескольких сотен. Поэтому большее распространение получили другие методы. При вертикальном микропрограммировании микрооперация определяется двоичным кодом, содержащимся в операционной части МК. При этом отдельный код задаёт отсутствие МКП.

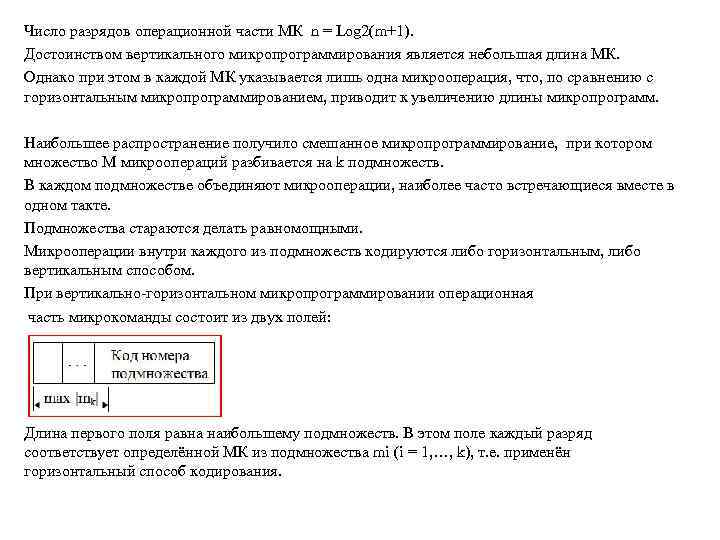

Число разрядов операционной части МК n = Log 2(m+1). Достоинством вертикального микропрограммирования является небольшая длина МК. Однако при этом в каждой МК указывается лишь одна микрооперация, что, по сравнению с горизонтальным микропрограммированием, приводит к увеличению длины микропрограмм. Наибольшее распространение получило смешанное микропрограммирование, при котором множество М микроопераций разбивается на k подмножеств. В каждом подмножестве объединяют микрооперации, наиболее часто встречающиеся вместе в одном такте. Подмножества стараются делать равномощными. Микрооперации внутри каждого из подмножеств кодируются либо горизонтальным, либо вертикальным способом. При вертикально-горизонтальном микропрограммировании операционная часть микрокоманды состоит из двух полей: Длина первого поля равна наибольшему подмножеств. В этом поле каждый разряд соответствует определённой МК из подмножества mi (i = 1, …, k), т. е. применён горизонтальный способ кодирования.

Число разрядов операционной части МК n = Log 2(m+1). Достоинством вертикального микропрограммирования является небольшая длина МК. Однако при этом в каждой МК указывается лишь одна микрооперация, что, по сравнению с горизонтальным микропрограммированием, приводит к увеличению длины микропрограмм. Наибольшее распространение получило смешанное микропрограммирование, при котором множество М микроопераций разбивается на k подмножеств. В каждом подмножестве объединяют микрооперации, наиболее часто встречающиеся вместе в одном такте. Подмножества стараются делать равномощными. Микрооперации внутри каждого из подмножеств кодируются либо горизонтальным, либо вертикальным способом. При вертикально-горизонтальном микропрограммировании операционная часть микрокоманды состоит из двух полей: Длина первого поля равна наибольшему подмножеств. В этом поле каждый разряд соответствует определённой МК из подмножества mi (i = 1, …, k), т. е. применён горизонтальный способ кодирования.

Второе поле, длинной Log 2 k , указывает, к какому из k подмножеств принадлежат микрооперации в первом поле. Более гибким и часто используемым является горизонтально-вертикаль-ное микропрограммирование. Подмножества кодируются горизонтальным, а микрооперации внутри каждого из подмножеств – вертикальным способом. В этом случае каждому подмножеству выделяется отдельное поле в операционной части микрокоманды. Длина операционной части микрокоманды определяется суммой: где mi – число микроопераций, представляемых в поле i. 7. 6. Операционное устройство МП. Функционально операционное устройство представляет собой АЛУ, выполняющее арифметические и логические операции над операндами, находящимися в регистрах МП. Результат операции засылается также в некоторый регистр МП. В процессе выполнения операций АЛУ взаимодействует с регистрами МП. При этом нередко один и тот же регистр бывает как источником, так и приёмником информации. Для реализации такой возможности необходимо осуществлять временное запоминание информации в отдельных регистрах. Здесь возможны два варианта:

Второе поле, длинной Log 2 k , указывает, к какому из k подмножеств принадлежат микрооперации в первом поле. Более гибким и часто используемым является горизонтально-вертикаль-ное микропрограммирование. Подмножества кодируются горизонтальным, а микрооперации внутри каждого из подмножеств – вертикальным способом. В этом случае каждому подмножеству выделяется отдельное поле в операционной части микрокоманды. Длина операционной части микрокоманды определяется суммой: где mi – число микроопераций, представляемых в поле i. 7. 6. Операционное устройство МП. Функционально операционное устройство представляет собой АЛУ, выполняющее арифметические и логические операции над операндами, находящимися в регистрах МП. Результат операции засылается также в некоторый регистр МП. В процессе выполнения операций АЛУ взаимодействует с регистрами МП. При этом нередко один и тот же регистр бывает как источником, так и приёмником информации. Для реализации такой возможности необходимо осуществлять временное запоминание информации в отдельных регистрах. Здесь возможны два варианта:

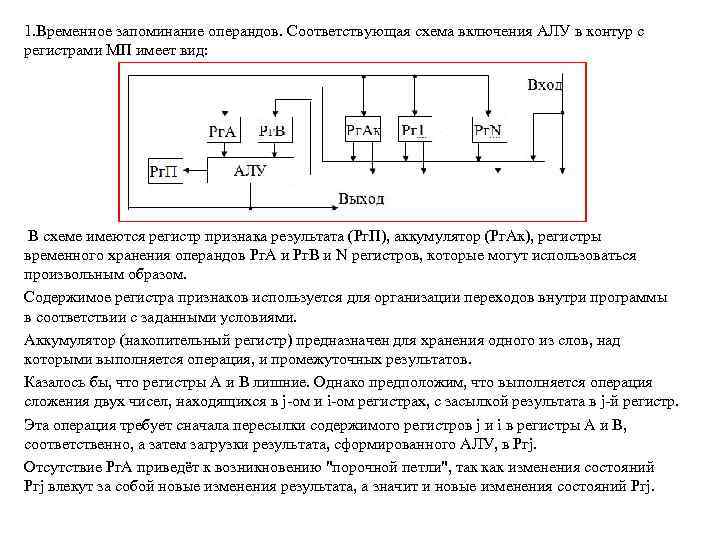

1. Временное запоминание операндов. Соответствующая схема включения АЛУ в контур с регистрами МП имеет вид: В схеме имеются регистр признака результата (Рг. П), аккумулятор (Рг. Ак), регистры временного хранения операндов Рг. А и Рг. В и N регистров, которые могут использоваться произвольным образом. Содержимое регистра признаков используется для организации переходов внутри программы в соответствии с заданными условиями. Аккумулятор (накопительный регистр) предназначен для хранения одного из слов, над которыми выполняется операция, и промежуточных результатов. Казалось бы, что регистры А и В лишние. Однако предположим, что выполняется операция сложения двух чисел, находящихся в j-ом и i-ом регистрах, с засылкой результата в j-й регистр. Эта операция требует сначала пересылки содержимого регистров j и i в регистры А и В, соответственно, а затем загрузки результата, сформированного АЛУ, в Ргj. Отсутствие Рг. А приведёт к возникновению "порочной петли", так как изменения состояний Ргj влекут за собой новые изменения результата, а значит и новые изменения состояний Ргj.

1. Временное запоминание операндов. Соответствующая схема включения АЛУ в контур с регистрами МП имеет вид: В схеме имеются регистр признака результата (Рг. П), аккумулятор (Рг. Ак), регистры временного хранения операндов Рг. А и Рг. В и N регистров, которые могут использоваться произвольным образом. Содержимое регистра признаков используется для организации переходов внутри программы в соответствии с заданными условиями. Аккумулятор (накопительный регистр) предназначен для хранения одного из слов, над которыми выполняется операция, и промежуточных результатов. Казалось бы, что регистры А и В лишние. Однако предположим, что выполняется операция сложения двух чисел, находящихся в j-ом и i-ом регистрах, с засылкой результата в j-й регистр. Эта операция требует сначала пересылки содержимого регистров j и i в регистры А и В, соответственно, а затем загрузки результата, сформированного АЛУ, в Ргj. Отсутствие Рг. А приведёт к возникновению "порочной петли", так как изменения состояний Ргj влекут за собой новые изменения результата, а значит и новые изменения состояний Ргj.

2. Временное хранение результата. Схема включения АЛУ отличается от только что рассмотренной лишь тем, что регистр временного хранения включается на выходе АЛУ: 7. 7. Обобщённая структурная схема МП. Структурные схемы МП конкретных типов и серий могут существенно различаться, но все они содержат 6 основных функциональных блоков:

2. Временное хранение результата. Схема включения АЛУ отличается от только что рассмотренной лишь тем, что регистр временного хранения включается на выходе АЛУ: 7. 7. Обобщённая структурная схема МП. Структурные схемы МП конкретных типов и серий могут существенно различаться, но все они содержат 6 основных функциональных блоков:

Система связи между блоками, как правило, централизованная (магистральная), что даёт возможность разнообразных межрегистровых пересылок информации. Магистраль представляет собой систему шин. Шиной называется часть линий (электрических цепей), сгруппированных по функциональному назначению. Выделяют следующие магистральные шины: шины адреса, данных и управления. Операционный блок производит приём из внешней среды операндов, их хранение и преобразование, а также выдачу результата во внешнюю среду. В простейшем случае операционный блок содержит АЛУ и ряд специальных регистров: аккумулятор, регистры временного хранения операндов и регистр признаков (флагов). В более сложных МП операционный блок может включать аппаратный умножитель, сдвигатель и прочие схемы для аппаратной поддержки команд деления, операций с плавающей запятой и т. д. Основной функцией блока управления является приём команд, их декодирование и формирование сигналов управления другими блоками МП. Управление операционным блоком может осуществляться на уровне микрокоманд, а остальными блоками – посредством сигналов тактирования и синхронизации. Важнейшей функцией блока управления является обработка прерываний. Блок управления содержит регистры и счётчики, предназначенные для временного хранения управляющей информации: регистры, хранящие информацию о состоянии МП, регистрсчётчик адреса команды -–счётчик команд, счётчики тактов, регистр запросов прерывания и др.

Система связи между блоками, как правило, централизованная (магистральная), что даёт возможность разнообразных межрегистровых пересылок информации. Магистраль представляет собой систему шин. Шиной называется часть линий (электрических цепей), сгруппированных по функциональному назначению. Выделяют следующие магистральные шины: шины адреса, данных и управления. Операционный блок производит приём из внешней среды операндов, их хранение и преобразование, а также выдачу результата во внешнюю среду. В простейшем случае операционный блок содержит АЛУ и ряд специальных регистров: аккумулятор, регистры временного хранения операндов и регистр признаков (флагов). В более сложных МП операционный блок может включать аппаратный умножитель, сдвигатель и прочие схемы для аппаратной поддержки команд деления, операций с плавающей запятой и т. д. Основной функцией блока управления является приём команд, их декодирование и формирование сигналов управления другими блоками МП. Управление операционным блоком может осуществляться на уровне микрокоманд, а остальными блоками – посредством сигналов тактирования и синхронизации. Важнейшей функцией блока управления является обработка прерываний. Блок управления содержит регистры и счётчики, предназначенные для временного хранения управляющей информации: регистры, хранящие информацию о состоянии МП, регистрсчётчик адреса команды -–счётчик команд, счётчики тактов, регистр запросов прерывания и др.

Адресный блок определяет способы адресации и объём адресуемой памяти. Многообразие способов адресации обусловлено невозможностью прямого указания адресов операндов при достаточно большом объёме памяти (1 Мбайт и более). Так, для задания каждого адреса в коде команды потребовалось бы более 20 разрядов. Кроме того, различные методы формирования адресов обеспечивают удобство при работе с процедурами последовательной выборки данных из таблиц и массивов, а также с алгоритмами, требующими вычисления адресов. Для реализации различных методов адресации в адресном блоке используется ряд регистров: индексные, базы, смещения, сегментные и др. Над содержимым этих регистров могут выполняться операции инкремента (увеличение на 1), декремента (уменьшение на 1), сложения, сравнения и некоторые другие. Шина адреса блока используется для адресации внешней памяти и внешних устройств. Блок регистров является внутренней памятью МП небольшой ёмкости, но, по сравнению с внешней оперативной памятью, более высокого быстродействия. Регистры этого блока являются многофункциональными и могут использоваться в качестве накопительных, индексных, указателей стека, как буферные для хранения обрабатываемой информации, для автоинкрементной и автодекрементной адресации. Поэтому блок регистров называется регистрами общего назначения (РОН). РОН программно доступны, т. е. их адреса явно указываются в кодах команд.

Адресный блок определяет способы адресации и объём адресуемой памяти. Многообразие способов адресации обусловлено невозможностью прямого указания адресов операндов при достаточно большом объёме памяти (1 Мбайт и более). Так, для задания каждого адреса в коде команды потребовалось бы более 20 разрядов. Кроме того, различные методы формирования адресов обеспечивают удобство при работе с процедурами последовательной выборки данных из таблиц и массивов, а также с алгоритмами, требующими вычисления адресов. Для реализации различных методов адресации в адресном блоке используется ряд регистров: индексные, базы, смещения, сегментные и др. Над содержимым этих регистров могут выполняться операции инкремента (увеличение на 1), декремента (уменьшение на 1), сложения, сравнения и некоторые другие. Шина адреса блока используется для адресации внешней памяти и внешних устройств. Блок регистров является внутренней памятью МП небольшой ёмкости, но, по сравнению с внешней оперативной памятью, более высокого быстродействия. Регистры этого блока являются многофункциональными и могут использоваться в качестве накопительных, индексных, указателей стека, как буферные для хранения обрабатываемой информации, для автоинкрементной и автодекрементной адресации. Поэтому блок регистров называется регистрами общего назначения (РОН). РОН программно доступны, т. е. их адреса явно указываются в кодах команд.

Блок системной магистрали связывает внутреннюю магистраль с внешней шиной данных, управляет буферами данных или усилителями приёма и выдачи информации на совмещённые выводы адресов и данных. По шине данных передаются числа и команды, с которыми работает МП. Интерфейсный блок объединяет управляющие сигналы и осуществляет управление обменом информацией между МП и устройствами, расположенными на системной магистрали. Кроме того, этот блок осуществляет арбитраж при операциях прямого доступа в память, а также приём и предварительную обработку запросов на прерывание. Рассмотренная совокупность блоков может размещаться на одном кристалле СБИС – тогда говорят об однокристальных МП. Эти приборы в наибольшей мере воплощают достоинства МП, используют самые современные технологии и архитектуру, обеспечивают чрезвычайно широкие функциональные возможности и высокое быстродействие. Однако если требования задачи хотя бы незначительно превосходят их возможности, эффективность применения однокристальных МП резко снижается. Отдельные блоки МП могут быть размещены на разных БИС, что соответствует секционным МП, на основе которых строятся специализированные вычислители.

Блок системной магистрали связывает внутреннюю магистраль с внешней шиной данных, управляет буферами данных или усилителями приёма и выдачи информации на совмещённые выводы адресов и данных. По шине данных передаются числа и команды, с которыми работает МП. Интерфейсный блок объединяет управляющие сигналы и осуществляет управление обменом информацией между МП и устройствами, расположенными на системной магистрали. Кроме того, этот блок осуществляет арбитраж при операциях прямого доступа в память, а также приём и предварительную обработку запросов на прерывание. Рассмотренная совокупность блоков может размещаться на одном кристалле СБИС – тогда говорят об однокристальных МП. Эти приборы в наибольшей мере воплощают достоинства МП, используют самые современные технологии и архитектуру, обеспечивают чрезвычайно широкие функциональные возможности и высокое быстродействие. Однако если требования задачи хотя бы незначительно превосходят их возможности, эффективность применения однокристальных МП резко снижается. Отдельные блоки МП могут быть размещены на разных БИС, что соответствует секционным МП, на основе которых строятся специализированные вычислители.

8. ЭЛЕМЕНТЫ АРХИТЕКТУРЫ МП. Однокристальные микропроцессоры по быстродействию и возможностям системы команд приближаются к процессорам ЭВМ. Поэтому дальнейший материал применим как к тем, так и к другим приборам. Под архитектурой МП принято понимать совокупность представлений о составе его компонентов, организации обмена информацией внутри МП и с внешней средой, а также о функциональных возможностях, реализуемых посредством системы команд. Выделим следующие элементы архитектуры МП: типы обрабатываемых данных (целое двоичное число, число с плавающей точкой, десятичное число и т. д. ) и способы их представления в МП (изложены в первой части курса); структуры команд; способы адресации информации; системы прерывания; рабочий цикл процессора; конвейеризация обработки команд и данных.

8. ЭЛЕМЕНТЫ АРХИТЕКТУРЫ МП. Однокристальные микропроцессоры по быстродействию и возможностям системы команд приближаются к процессорам ЭВМ. Поэтому дальнейший материал применим как к тем, так и к другим приборам. Под архитектурой МП принято понимать совокупность представлений о составе его компонентов, организации обмена информацией внутри МП и с внешней средой, а также о функциональных возможностях, реализуемых посредством системы команд. Выделим следующие элементы архитектуры МП: типы обрабатываемых данных (целое двоичное число, число с плавающей точкой, десятичное число и т. д. ) и способы их представления в МП (изложены в первой части курса); структуры команд; способы адресации информации; системы прерывания; рабочий цикл процессора; конвейеризация обработки команд и данных.

8. 1. Структура команд. Обработка информации и функционирование МП обеспечиваются с помощью программного управления. Программа записывается во внешнем ОЗУ в виде последовательности команд. Команда представляет собой код, определяющий вид операции, адреса операндов, адрес размещения результата операции и адрес расположения следующей команды. По функциональному назначению различаются команды передачи данных, обработки данных, передачи управления и дополнительные команды. Команды передачи данных включают в себя команды передачи кодов между регистрами МП, между МП и внешней памятью, между МП и внешними устройствами. Команды обработки данных подразделяются на арифметические, логические и команды сдвига. Команды передачи управления используются для изменения естественного порядка следования команд (условные и безусловные переходы) и организации циклических участков в программах. Дополнительные команды предназначены для задания останова программы, начальной установки аппаратных средств, реализации ожидания. В общем случае команда состоит из операционной и адресной частей:

8. 1. Структура команд. Обработка информации и функционирование МП обеспечиваются с помощью программного управления. Программа записывается во внешнем ОЗУ в виде последовательности команд. Команда представляет собой код, определяющий вид операции, адреса операндов, адрес размещения результата операции и адрес расположения следующей команды. По функциональному назначению различаются команды передачи данных, обработки данных, передачи управления и дополнительные команды. Команды передачи данных включают в себя команды передачи кодов между регистрами МП, между МП и внешней памятью, между МП и внешними устройствами. Команды обработки данных подразделяются на арифметические, логические и команды сдвига. Команды передачи управления используются для изменения естественного порядка следования команд (условные и безусловные переходы) и организации циклических участков в программах. Дополнительные команды предназначены для задания останова программы, начальной установки аппаратных средств, реализации ожидания. В общем случае команда состоит из операционной и адресной частей:

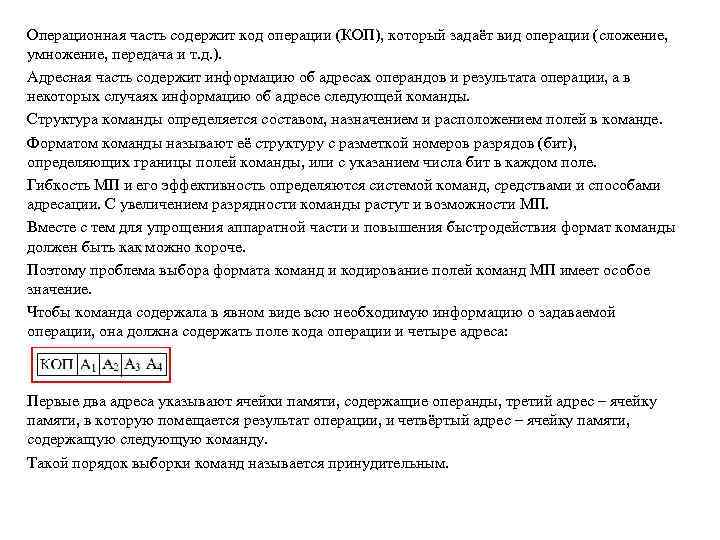

Операционная часть содержит код операции (КОП), который задаёт вид операции (сложение, умножение, передача и т. д. ). Адресная часть содержит информацию об адресах операндов и результата операции, а в некоторых случаях информацию об адресе следующей команды. Структура команды определяется составом, назначением и расположением полей в команде. Форматом команды называют её структуру с разметкой номеров разрядов (бит), определяющих границы полей команды, или с указанием числа бит в каждом поле. Гибкость МП и его эффективность определяются системой команд, средствами и способами адресации. С увеличением разрядности команды растут и возможности МП. Вместе с тем для упрощения аппаратной части и повышения быстродействия формат команды должен быть как можно короче. Поэтому проблема выбора формата команд и кодирование полей команд МП имеет особое значение. Чтобы команда содержала в явном виде всю необходимую информацию о задаваемой операции, она должна содержать поле кода операции и четыре адреса: Первые два адреса указывают ячейки памяти, содержащие операнды, третий адрес – ячейку памяти, в которую помещается результат операции, и четвёртый адрес – ячейку памяти, содержащую следующую команду. Такой порядок выборки команд называется принудительным.

Операционная часть содержит код операции (КОП), который задаёт вид операции (сложение, умножение, передача и т. д. ). Адресная часть содержит информацию об адресах операндов и результата операции, а в некоторых случаях информацию об адресе следующей команды. Структура команды определяется составом, назначением и расположением полей в команде. Форматом команды называют её структуру с разметкой номеров разрядов (бит), определяющих границы полей команды, или с указанием числа бит в каждом поле. Гибкость МП и его эффективность определяются системой команд, средствами и способами адресации. С увеличением разрядности команды растут и возможности МП. Вместе с тем для упрощения аппаратной части и повышения быстродействия формат команды должен быть как можно короче. Поэтому проблема выбора формата команд и кодирование полей команд МП имеет особое значение. Чтобы команда содержала в явном виде всю необходимую информацию о задаваемой операции, она должна содержать поле кода операции и четыре адреса: Первые два адреса указывают ячейки памяти, содержащие операнды, третий адрес – ячейку памяти, в которую помещается результат операции, и четвёртый адрес – ячейку памяти, содержащую следующую команду. Такой порядок выборки команд называется принудительным.

Четырёхадресный формат команды неэффективен и в настоящее время не применяется. Можно установить, что после выполнения данной команды, расположенной по адресу К и занимающей L ячеек памяти, выполняется команда из (К+L)-й ячейки. Такой порядок выборки команд называется естественным. Он нарушается только специальными командами. В этом случае отпадает необходимость указывать в явной форме адрес сле-дующей команды. В результате приходим к трёхадресной команде. Можно условиться, что результат операции всегда помещается на месте одного из операндов, например, первого. В итоге получаем двухадресную команду: Операция, описываемая двухадресной командой, символически может быть представлена в виде: ОП[A 1] : = ОП[A 1]*ОП[A 2], где знак * обозначает символ операции (+, - и т. п. ). Запись читается так: в ячейку оперативной памяти с номером А 1 помещается результат операции над числами, размещёнными в оперативной памяти по адресам А 1 и А 2. Таким образом, в этом случае для результата операции используется подразумеваемый адрес. В одноадресной команде подразумеваемые адреса имеют и результат операции и один из операндов. Предполагается, что явно не адресуемый операнд всегда находится в аккумуляторе. Туда же записывается и результат операции.

Четырёхадресный формат команды неэффективен и в настоящее время не применяется. Можно установить, что после выполнения данной команды, расположенной по адресу К и занимающей L ячеек памяти, выполняется команда из (К+L)-й ячейки. Такой порядок выборки команд называется естественным. Он нарушается только специальными командами. В этом случае отпадает необходимость указывать в явной форме адрес сле-дующей команды. В результате приходим к трёхадресной команде. Можно условиться, что результат операции всегда помещается на месте одного из операндов, например, первого. В итоге получаем двухадресную команду: Операция, описываемая двухадресной командой, символически может быть представлена в виде: ОП[A 1] : = ОП[A 1]*ОП[A 2], где знак * обозначает символ операции (+, - и т. п. ). Запись читается так: в ячейку оперативной памяти с номером А 1 помещается результат операции над числами, размещёнными в оперативной памяти по адресам А 1 и А 2. Таким образом, в этом случае для результата операции используется подразумеваемый адрес. В одноадресной команде подразумеваемые адреса имеют и результат операции и один из операндов. Предполагается, что явно не адресуемый операнд всегда находится в аккумуляторе. Туда же записывается и результат операции.

![Символическая запись соответствующей операции имеет вид: Ак : = Ак*ОП[A]. Наконец, в некоторых случаях Символическая запись соответствующей операции имеет вид: Ак : = Ак*ОП[A]. Наконец, в некоторых случаях](https://present5.com/presentation/3/51183084_92453024.pdf-img/51183084_92453024.pdf-22.jpg) Символическая запись соответствующей операции имеет вид: Ак : = Ак*ОП[A]. Наконец, в некоторых случаях (например, при работе со стековой памятью) возможно использование безадресных команд. В таких случаях подразумеваются адреса обоих операндов и результата операции. В современных МП применяют, как правило, двух- и одноадресные команды. Обусловлено это следующими причинами: 1) необходимость иметь большее число разрядов для представления адресов и кода операции приводит к недопустимо большой длине трёхадресной команды; 2) часто в качестве операндов используются результаты предыдущих операций, хранимых в регистрах МП. В этом случае трёхадресный формат используется неэффективно. При ограниченной разрядности команд практически невозможно кодировать большое число различных операций и одновременно иметь гибкую форму адресации операндов. Это противоречие преодолевается расширением кодов операций в команде. Так, для задания небольшой группы основных операций (арифметических и т. п. ) используется короткий код операции, а получаемая при этом сравнительно большая адресная часть команды позволяет реализовать гибкую адресацию (например, двухадресную с многими модификациями). Для задания других операций используются более длинные (расширяемые) коды операций, при этом сокращаемая адресная часть оставляет возможность лишь для более простой адресации операндов (например, одноадресной). В пределе расширяемый код операций занимает весь формат команды (безадресная команда).

Символическая запись соответствующей операции имеет вид: Ак : = Ак*ОП[A]. Наконец, в некоторых случаях (например, при работе со стековой памятью) возможно использование безадресных команд. В таких случаях подразумеваются адреса обоих операндов и результата операции. В современных МП применяют, как правило, двух- и одноадресные команды. Обусловлено это следующими причинами: 1) необходимость иметь большее число разрядов для представления адресов и кода операции приводит к недопустимо большой длине трёхадресной команды; 2) часто в качестве операндов используются результаты предыдущих операций, хранимых в регистрах МП. В этом случае трёхадресный формат используется неэффективно. При ограниченной разрядности команд практически невозможно кодировать большое число различных операций и одновременно иметь гибкую форму адресации операндов. Это противоречие преодолевается расширением кодов операций в команде. Так, для задания небольшой группы основных операций (арифметических и т. п. ) используется короткий код операции, а получаемая при этом сравнительно большая адресная часть команды позволяет реализовать гибкую адресацию (например, двухадресную с многими модификациями). Для задания других операций используются более длинные (расширяемые) коды операций, при этом сокращаемая адресная часть оставляет возможность лишь для более простой адресации операндов (например, одноадресной). В пределе расширяемый код операций занимает весь формат команды (безадресная команда).

Приведённые структуры команд достаточно схематичны. В действительности адресные поля команд большей частью содержат не сами адреса, а только информацию, позволяющую определить действительные (исполнительные) адреса операндов в соответствии с используемыми в командах способами адресации. 8. 2. Способы адресации, основанные на прямом использовании кода команды. Следует различать понятия адресный код и исполнительный адрес. Адресный код АК – это информация об адресе операнда, содержащаяся в команде. Исполнительный адрес АИ – это номер ячейки памяти, к которой производится фактическое обращение. Адресный код, как правило, не совпадает с исполнительным адресом. Способы, в которых исполнительный адрес определяется значением адресного кода команды, включают непосредственную, прямую, укороченную, регистровую, косвенную, автоинкрементную и автодекрементную адресации. При непосредственной адресации в команде содержится не адрес операнда, а непосредственно сам операнд. В этом случае не требуется ячейки памяти для хранения операнда, а значит не требуется и обращения к памяти для его выборки. В результате уменьшается время выполнения программы и занимаемого ею объёма памяти. Непосредственная адресация удобна при работе с различного рода константами.

Приведённые структуры команд достаточно схематичны. В действительности адресные поля команд большей частью содержат не сами адреса, а только информацию, позволяющую определить действительные (исполнительные) адреса операндов в соответствии с используемыми в командах способами адресации. 8. 2. Способы адресации, основанные на прямом использовании кода команды. Следует различать понятия адресный код и исполнительный адрес. Адресный код АК – это информация об адресе операнда, содержащаяся в команде. Исполнительный адрес АИ – это номер ячейки памяти, к которой производится фактическое обращение. Адресный код, как правило, не совпадает с исполнительным адресом. Способы, в которых исполнительный адрес определяется значением адресного кода команды, включают непосредственную, прямую, укороченную, регистровую, косвенную, автоинкрементную и автодекрементную адресации. При непосредственной адресации в команде содержится не адрес операнда, а непосредственно сам операнд. В этом случае не требуется ячейки памяти для хранения операнда, а значит не требуется и обращения к памяти для его выборки. В результате уменьшается время выполнения программы и занимаемого ею объёма памяти. Непосредственная адресация удобна при работе с различного рода константами.

При прямой адресации исполнительный адрес совпадает с кодом адреса команды. Укороченная адресация используется для уменьшения длины кода команды. Суть способа сводится к тому, что в команде задаются только младшие разряды адресов, а старшие подразумеваются нулевыми. Такая адресация позволяет использовать только небольшую группу фиксированных ячеек с короткими адресами и поэтому может применяться лишь совместно с другими способами адресации. Косвенная адресация используется для преодоления ограничений короткого формата команды. Адресный код команды указывает адрес ячейки памяти, в которой находится адрес операнда или команды. Таким образом, косвенная адресация может быть иначе определена как "адресация адреса". Данный вид адресации указывается либо кодом операции команды, либо её специальным разрядом – указателем адресации (УА). В УА цифра 0 означает, что адресная часть команды является прямым адресом, а цифра 1 – косвенным адресом. Иногда используется многоступенчатая косвенная адресация. В этом случае УА содержится и в ячейках памяти. Адреса последовательно выбираются из памяти до тех пор, пока не будет найдена ячейка, в которой УА определит прямую адресацию. Адрес из этой последней ячейки и является искомым исполнительным адресом. В МП широко применяется совместное использование регистровой и косвенной адресаций.

При прямой адресации исполнительный адрес совпадает с кодом адреса команды. Укороченная адресация используется для уменьшения длины кода команды. Суть способа сводится к тому, что в команде задаются только младшие разряды адресов, а старшие подразумеваются нулевыми. Такая адресация позволяет использовать только небольшую группу фиксированных ячеек с короткими адресами и поэтому может применяться лишь совместно с другими способами адресации. Косвенная адресация используется для преодоления ограничений короткого формата команды. Адресный код команды указывает адрес ячейки памяти, в которой находится адрес операнда или команды. Таким образом, косвенная адресация может быть иначе определена как "адресация адреса". Данный вид адресации указывается либо кодом операции команды, либо её специальным разрядом – указателем адресации (УА). В УА цифра 0 означает, что адресная часть команды является прямым адресом, а цифра 1 – косвенным адресом. Иногда используется многоступенчатая косвенная адресация. В этом случае УА содержится и в ячейках памяти. Адреса последовательно выбираются из памяти до тех пор, пока не будет найдена ячейка, в которой УА определит прямую адресацию. Адрес из этой последней ячейки и является искомым исполнительным адресом. В МП широко применяется совместное использование регистровой и косвенной адресаций.

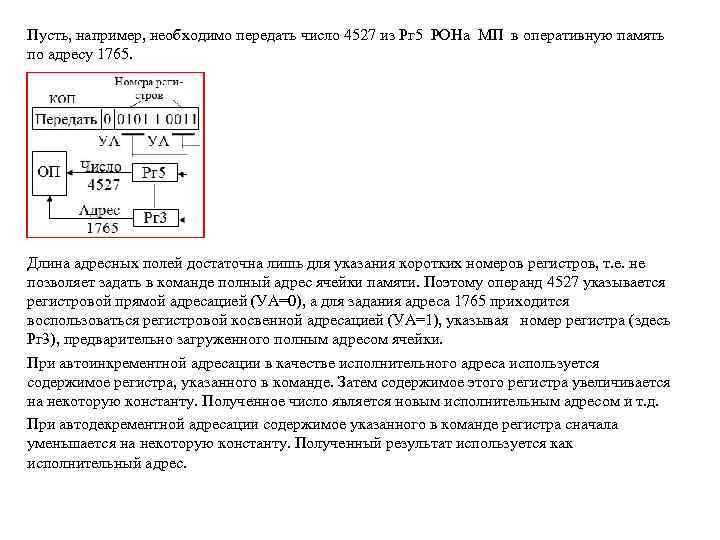

Пусть, например, необходимо передать число 4527 из Рг 5 РОНа МП в оперативную память по адресу 1765. Длина адресных полей достаточна лишь для указания коротких номеров регистров, т. е. не позволяет задать в команде полный адрес ячейки памяти. Поэтому операнд 4527 указывается регистровой прямой адресацией (УА=0), а для задания адреса 1765 приходится воспользоваться регистровой косвенной адресацией (УА=1), указывая номер регистра (здесь Рг 3), предварительно загруженного полным адресом ячейки. При автоинкрементной адресации в качестве исполнительного адреса используется содержимое регистра, указанного в команде. Затем содержимое этого регистра увеличивается на некоторую константу. Полученное число является новым исполнительным адресом и т. д. При автодекрементной адресации содержимое указанного в команде регистра сначала уменьшается на некоторую константу. Полученный результат используется как исполнительный адрес.

Пусть, например, необходимо передать число 4527 из Рг 5 РОНа МП в оперативную память по адресу 1765. Длина адресных полей достаточна лишь для указания коротких номеров регистров, т. е. не позволяет задать в команде полный адрес ячейки памяти. Поэтому операнд 4527 указывается регистровой прямой адресацией (УА=0), а для задания адреса 1765 приходится воспользоваться регистровой косвенной адресацией (УА=1), указывая номер регистра (здесь Рг 3), предварительно загруженного полным адресом ячейки. При автоинкрементной адресации в качестве исполнительного адреса используется содержимое регистра, указанного в команде. Затем содержимое этого регистра увеличивается на некоторую константу. Полученное число является новым исполнительным адресом и т. д. При автодекрементной адресации содержимое указанного в команде регистра сначала уменьшается на некоторую константу. Полученный результат используется как исполнительный адрес.

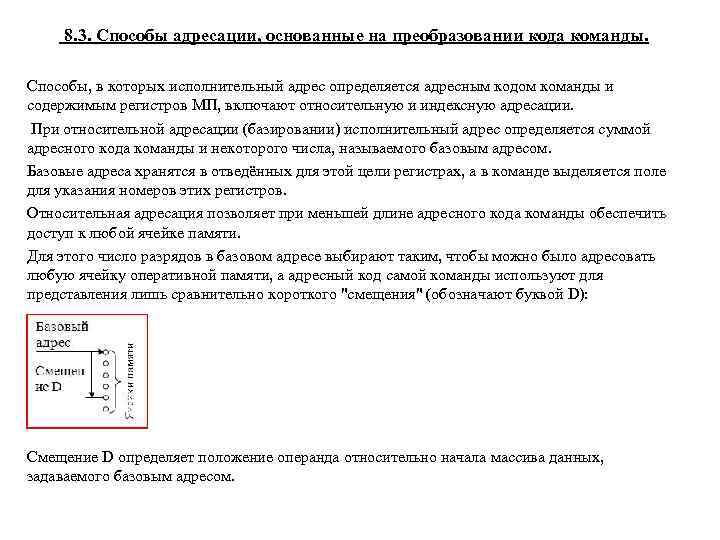

8. 3. Способы адресации, основанные на преобразовании кода команды. Способы, в которых исполнительный адрес определяется адресным кодом команды и содержимым регистров МП, включают относительную и индексную адресации. При относительной адресации (базировании) исполнительный адрес определяется суммой адресного кода команды и некоторого числа, называемого базовым адресом. Базовые адреса хранятся в отведённых для этой цели регистрах, а в команде выделяется поле для указания номеров этих регистров. Относительная адресация позволяет при меньшей длине адресного кода команды обеспечить доступ к любой ячейке памяти. Для этого число разрядов в базовом адресе выбирают таким, чтобы можно было адресовать любую ячейку оперативной памяти, а адресный код самой команды используют для представления лишь сравнительно короткого "смещения" (обозначают буквой D): Смещение D определяет положение операнда относительно начала массива данных, задаваемого базовым адресом.

8. 3. Способы адресации, основанные на преобразовании кода команды. Способы, в которых исполнительный адрес определяется адресным кодом команды и содержимым регистров МП, включают относительную и индексную адресации. При относительной адресации (базировании) исполнительный адрес определяется суммой адресного кода команды и некоторого числа, называемого базовым адресом. Базовые адреса хранятся в отведённых для этой цели регистрах, а в команде выделяется поле для указания номеров этих регистров. Относительная адресация позволяет при меньшей длине адресного кода команды обеспечить доступ к любой ячейке памяти. Для этого число разрядов в базовом адресе выбирают таким, чтобы можно было адресовать любую ячейку оперативной памяти, а адресный код самой команды используют для представления лишь сравнительно короткого "смещения" (обозначают буквой D): Смещение D определяет положение операнда относительно начала массива данных, задаваемого базовым адресом.

Поскольку суммирование связано с потерей времени, то для формирования исполнительного адреса используют также метод совмещения. В этом случае базовый адрес содержит старшие, а смещение – младшие разряды исполнительного адреса, которые объединяются в регистре адреса. Однако при совмещении базовый адрес может задавать не любую ячейку, а только те, адреса которых содержат нули в младших разрядах, соответствующих смещению. Относительная адресация обеспечивает так называемую перемещаемость программ, т. е. возможность передвижения программ в памяти без изменений внутри самой программы. Развитием метода базирования является индексация. Механизм индексации обеспечивает автоматическую модификацию адресных частей команд и используется для управления циклическими вычислительными процессами. В данном случае модификация заключается в изменении адресных частей соответствующих команд согласно расположению в оперативной памяти обрабатываемых операндов. Для выполнения индексации используются так называемые индексные регистры, а в формате команды выделяется поле для указания номера индексного регистра. Наименование индексных регистров связано с тем, что первоначально они предназначались для хранения индекса текущего элемента массива ai. Хотя назначение индексных регистров значительно расширилось, термин сохранился. Исполнительный адрес формируется путём сложения адресного кода команды (смещения) с содержимым индексного регистра (индексом), а при наличии базирования – и с базовым адресом. Отличительной чертой индексации является то, что код команды, хранящейся в оперативной памяти, остаётся неизменным.

Поскольку суммирование связано с потерей времени, то для формирования исполнительного адреса используют также метод совмещения. В этом случае базовый адрес содержит старшие, а смещение – младшие разряды исполнительного адреса, которые объединяются в регистре адреса. Однако при совмещении базовый адрес может задавать не любую ячейку, а только те, адреса которых содержат нули в младших разрядах, соответствующих смещению. Относительная адресация обеспечивает так называемую перемещаемость программ, т. е. возможность передвижения программ в памяти без изменений внутри самой программы. Развитием метода базирования является индексация. Механизм индексации обеспечивает автоматическую модификацию адресных частей команд и используется для управления циклическими вычислительными процессами. В данном случае модификация заключается в изменении адресных частей соответствующих команд согласно расположению в оперативной памяти обрабатываемых операндов. Для выполнения индексации используются так называемые индексные регистры, а в формате команды выделяется поле для указания номера индексного регистра. Наименование индексных регистров связано с тем, что первоначально они предназначались для хранения индекса текущего элемента массива ai. Хотя назначение индексных регистров значительно расширилось, термин сохранился. Исполнительный адрес формируется путём сложения адресного кода команды (смещения) с содержимым индексного регистра (индексом), а при наличии базирования – и с базовым адресом. Отличительной чертой индексации является то, что код команды, хранящейся в оперативной памяти, остаётся неизменным.

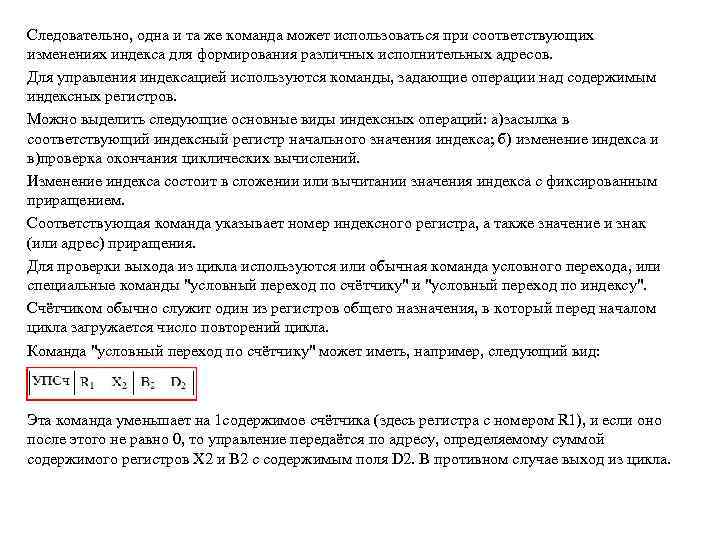

Следовательно, одна и та же команда может использоваться при соответствующих изменениях индекса для формирования различных исполнительных адресов. Для управления индексацией используются команды, задающие операции над содержимым индексных регистров. Можно выделить следующие основные виды индексных операций: а)засылка в соответствующий индексный регистр начального значения индекса; б) изменение индекса и в)проверка окончания циклических вычислений. Изменение индекса состоит в сложении или вычитании значения индекса с фиксированным приращением. Соответствующая команда указывает номер индексного регистра, а также значение и знак (или адрес) приращения. Для проверки выхода из цикла используются или обычная команда условного перехода, или специальные команды "условный переход по счётчику" и "условный переход по индексу". Счётчиком обычно служит один из регистров общего назначения, в который перед началом цикла загружается число повторений цикла. Команда "условный переход по счётчику" может иметь, например, следующий вид: Эта команда уменьшает на 1 содержимое счётчика (здесь регистра с номером R 1), и если оно после этого не равно 0, то управление передаётся по адресу, определяемому суммой содержимого регистров Х 2 и В 2 с содержимым поля D 2. В противном случае выход из цикла.

Следовательно, одна и та же команда может использоваться при соответствующих изменениях индекса для формирования различных исполнительных адресов. Для управления индексацией используются команды, задающие операции над содержимым индексных регистров. Можно выделить следующие основные виды индексных операций: а)засылка в соответствующий индексный регистр начального значения индекса; б) изменение индекса и в)проверка окончания циклических вычислений. Изменение индекса состоит в сложении или вычитании значения индекса с фиксированным приращением. Соответствующая команда указывает номер индексного регистра, а также значение и знак (или адрес) приращения. Для проверки выхода из цикла используются или обычная команда условного перехода, или специальные команды "условный переход по счётчику" и "условный переход по индексу". Счётчиком обычно служит один из регистров общего назначения, в который перед началом цикла загружается число повторений цикла. Команда "условный переход по счётчику" может иметь, например, следующий вид: Эта команда уменьшает на 1 содержимое счётчика (здесь регистра с номером R 1), и если оно после этого не равно 0, то управление передаётся по адресу, определяемому суммой содержимого регистров Х 2 и В 2 с содержимым поля D 2. В противном случае выход из цикла.

Команда "условный переход по индексу" имеет, например, вид: Здесь R 1 – номер индексного регистра; R 3 – номер регистра, хранящего приращение; сумма содержимого регистра В 2 с содержимым поля D 2 определяет адрес начала цикла; в регистре с номером R 3+1 хранится предельное значение индекса. Команда производит суммирование содержимого регистров R 1 и R 3. Если новое значение индекса меньше или равно предельному, то это новое значение помещается в регистр R 1 и происходит переход к началу цикла (повторение цикла). В противном случае выход из цикла. Аналогично выполняется проверка окончания цикла в случае обратного условия. 8. 4. Понятие вектора состояния МП. При выполнении микропроцессором программы после завершения каждой МК, а тем более команды, изменяется содержимое регистров, счётчиков, состояния отдельных управляющих триггеров. Можно говорить, что изменяется состояние МП или, употребляя другую терминологию, состояние программы. Информация о состоянии МП лежит в основе многих процедур управления вычислительным процессом, например при анализе ситуаций в случаях отказов и сбоев, при возобновлении выполнения программы после перерывов, для фиксации состояния процессора в момент перехода от обработки данной программы к другой и т. п.

Команда "условный переход по индексу" имеет, например, вид: Здесь R 1 – номер индексного регистра; R 3 – номер регистра, хранящего приращение; сумма содержимого регистра В 2 с содержимым поля D 2 определяет адрес начала цикла; в регистре с номером R 3+1 хранится предельное значение индекса. Команда производит суммирование содержимого регистров R 1 и R 3. Если новое значение индекса меньше или равно предельному, то это новое значение помещается в регистр R 1 и происходит переход к началу цикла (повторение цикла). В противном случае выход из цикла. Аналогично выполняется проверка окончания цикла в случае обратного условия. 8. 4. Понятие вектора состояния МП. При выполнении микропроцессором программы после завершения каждой МК, а тем более команды, изменяется содержимое регистров, счётчиков, состояния отдельных управляющих триггеров. Можно говорить, что изменяется состояние МП или, употребляя другую терминологию, состояние программы. Информация о состоянии МП лежит в основе многих процедур управления вычислительным процессом, например при анализе ситуаций в случаях отказов и сбоев, при возобновлении выполнения программы после перерывов, для фиксации состояния процессора в момент перехода от обработки данной программы к другой и т. п.

Состоянием микропроцессора после данного такта или после выполнения данной команды следует считать совокупность состояний в соответствующий момент времени всех его запоминающих элементов. Однако не вся эта информация исчезает или искажается при переходе к очередной команде либо другой программе. Поэтому из всего многообразия информации о состоянии МП отбираются наиболее существенные её элементы. Совокупность значений элементов информации о состоянии МП, как правило, подверженные изменениям при переходе к другой команде или программе, называется вектором состояния микропроцессора. Вектор состояния в каждый момент времени должен содержать информацию, достаточную для продолжения выполнения программы или её повторного пуска. При этом предполагается, что остальная информация, характеризующая состояние МП, или сохраняется, или может быть восстановлена программным путём по копии, сохранённой в памяти. Вектор состояния формируется в соответствующем регистре или регистрах микропроцессора. В наиболее простом виде вектор состояния включает в себя содержимое счётчика команд (адрес очередной команды), содержимое регистров признаков и содержимое аккумулятора АЛУ.

Состоянием микропроцессора после данного такта или после выполнения данной команды следует считать совокупность состояний в соответствующий момент времени всех его запоминающих элементов. Однако не вся эта информация исчезает или искажается при переходе к очередной команде либо другой программе. Поэтому из всего многообразия информации о состоянии МП отбираются наиболее существенные её элементы. Совокупность значений элементов информации о состоянии МП, как правило, подверженные изменениям при переходе к другой команде или программе, называется вектором состояния микропроцессора. Вектор состояния в каждый момент времени должен содержать информацию, достаточную для продолжения выполнения программы или её повторного пуска. При этом предполагается, что остальная информация, характеризующая состояние МП, или сохраняется, или может быть восстановлена программным путём по копии, сохранённой в памяти. Вектор состояния формируется в соответствующем регистре или регистрах микропроцессора. В наиболее простом виде вектор состояния включает в себя содержимое счётчика команд (адрес очередной команды), содержимое регистров признаков и содержимое аккумулятора АЛУ.

8. 5. Понятие системы прерывания программ. Процесс прерывания программы заключается в прерывании обработки текущей программы и переходе к выполнению некоторой другой программы. По завершении этой программы МП возвращается к выполнению прерванной программы. Возможность прерывания программ – важное архитектурное свойство. Оно позволяет организовать обслуживание одним микропроцессором нескольких процессов, протекающих во времени параллельно (одновременно). Сигналы, сопровождающие события, требующие прерывания текущей программы, называются запросами прерывания. Программа, затребованная запросом прерывания, называется прерывающей программой. Совокупность аппаратурных и программных средств, обеспечивающих реализацию прерывания программ, называется системой прерывания программ или контроллером прерывания. Процесс прерывания реализуется в следующем порядке. По запросу прерывания, поступающего от периферийного (внешнего) устройства, МП заканчивает выполнение текущей МК или команды. После этого система прерывания загружает текущий вектор состояния МП во внешнюю память (в частности, в стек). Затем в регистры МП загружается вектор прерывания, соответствующий периферийному устройству, которое требует прерывания.

8. 5. Понятие системы прерывания программ. Процесс прерывания программы заключается в прерывании обработки текущей программы и переходе к выполнению некоторой другой программы. По завершении этой программы МП возвращается к выполнению прерванной программы. Возможность прерывания программ – важное архитектурное свойство. Оно позволяет организовать обслуживание одним микропроцессором нескольких процессов, протекающих во времени параллельно (одновременно). Сигналы, сопровождающие события, требующие прерывания текущей программы, называются запросами прерывания. Программа, затребованная запросом прерывания, называется прерывающей программой. Совокупность аппаратурных и программных средств, обеспечивающих реализацию прерывания программ, называется системой прерывания программ или контроллером прерывания. Процесс прерывания реализуется в следующем порядке. По запросу прерывания, поступающего от периферийного (внешнего) устройства, МП заканчивает выполнение текущей МК или команды. После этого система прерывания загружает текущий вектор состояния МП во внешнюю память (в частности, в стек). Затем в регистры МП загружается вектор прерывания, соответствующий периферийному устройству, которое требует прерывания.

Вектором прерывания называется вектор начального состояния прерывающей программы. Он содержит всю необходимую информацию для перехода к прерывающей программе, в том числе её начальный адрес. Структура вектора прерывания аналогична структуре вектора состояния процессора. Векторы прерывания обычно находятся в специально выделенных фиксированных ячейках внешней памяти. После обработки прерывания система прерывания возвращает в соответствующие регистры МП сохранённый вектор состояния и процесс обработки прерванной программы возобновляется. Таким образом, основными функциями системы прерывания являются: - запоминание состояния прерываемой программы и осуществление перехода к прерывающей программе; - восстановление состояния прерванной программы и возврат к ней. Помимо основных функций система прерывания выполняет ещё одну – выделение из выставленных запросов такого, который имеет наибольший приоритет. Различают абсолютный и относительный приоритеты. Запрос, имеющий абсолютный приоритет, прерывает выполняемую программу и инициирует выполнение соответствующей прерывающей программы. Запрос с относительным приоритетом является первым кандидатом на обслуживание после завершения выполнения текущей программы. Следует отметить, что если наиболее приоритетный из выставленных запросов не превосходит по уровню приоритета выполняемой программы, то запрос прерывания игнорируется или его обслуживание откладывается до завершения выполнения текущей программы.

Вектором прерывания называется вектор начального состояния прерывающей программы. Он содержит всю необходимую информацию для перехода к прерывающей программе, в том числе её начальный адрес. Структура вектора прерывания аналогична структуре вектора состояния процессора. Векторы прерывания обычно находятся в специально выделенных фиксированных ячейках внешней памяти. После обработки прерывания система прерывания возвращает в соответствующие регистры МП сохранённый вектор состояния и процесс обработки прерванной программы возобновляется. Таким образом, основными функциями системы прерывания являются: - запоминание состояния прерываемой программы и осуществление перехода к прерывающей программе; - восстановление состояния прерванной программы и возврат к ней. Помимо основных функций система прерывания выполняет ещё одну – выделение из выставленных запросов такого, который имеет наибольший приоритет. Различают абсолютный и относительный приоритеты. Запрос, имеющий абсолютный приоритет, прерывает выполняемую программу и инициирует выполнение соответствующей прерывающей программы. Запрос с относительным приоритетом является первым кандидатом на обслуживание после завершения выполнения текущей программы. Следует отметить, что если наиболее приоритетный из выставленных запросов не превосходит по уровню приоритета выполняемой программы, то запрос прерывания игнорируется или его обслуживание откладывается до завершения выполнения текущей программы.

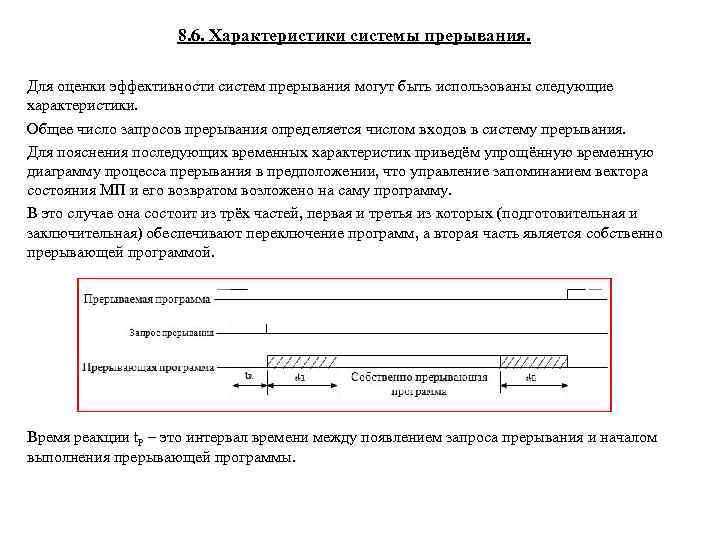

8. 6. Характеристики системы прерывания. Для оценки эффективности систем прерывания могут быть использованы следующие характеристики. Общее число запросов прерывания определяется числом входов в систему прерывания. Для пояснения последующих временных характеристик приведём упрощённую временную диаграмму процесса прерывания в предположении, что управление запоминанием вектора состояния МП и его возвратом возложено на саму программу. В это случае она состоит из трёх частей, первая и третья из которых (подготовительная и заключительная) обеспечивают переключение программ, а вторая часть является собственно прерывающей программой. Время реакции t. Р – это интервал времени между появлением запроса прерывания и началом выполнения прерывающей программы.

8. 6. Характеристики системы прерывания. Для оценки эффективности систем прерывания могут быть использованы следующие характеристики. Общее число запросов прерывания определяется числом входов в систему прерывания. Для пояснения последующих временных характеристик приведём упрощённую временную диаграмму процесса прерывания в предположении, что управление запоминанием вектора состояния МП и его возвратом возложено на саму программу. В это случае она состоит из трёх частей, первая и третья из которых (подготовительная и заключительная) обеспечивают переключение программ, а вторая часть является собственно прерывающей программой. Время реакции t. Р – это интервал времени между появлением запроса прерывания и началом выполнения прерывающей программы.

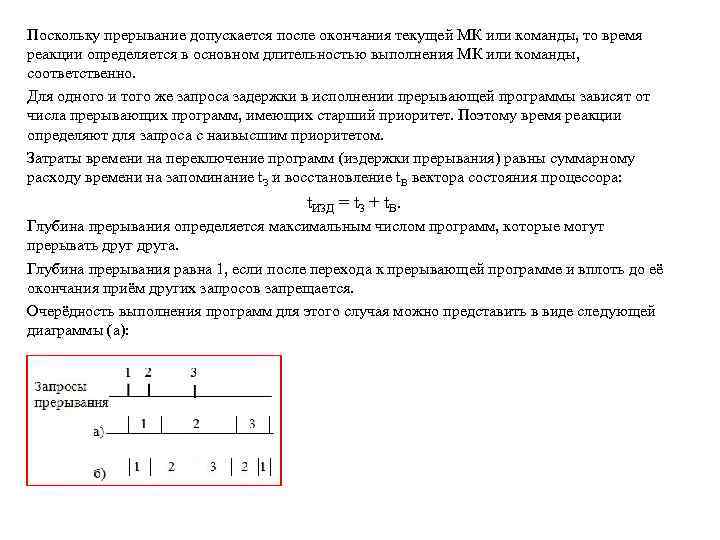

Поскольку прерывание допускается после окончания текущей МК или команды, то время реакции определяется в основном длительностью выполнения МК или команды, соответственно. Для одного и того же запроса задержки в исполнении прерывающей программы зависят от числа прерывающих программ, имеющих старший приоритет. Поэтому время реакции определяют для запроса с наивысшим приоритетом. Затраты времени на переключение программ (издержки прерывания) равны суммарному расходу времени на запоминание t. З и восстановление t. В вектора состояния процессора: t. ИЗД = t. З + t. В. Глубина прерывания определяется максимальным числом программ, которые могут прерывать друга. Глубина прерывания равна 1, если после перехода к прерывающей программе и вплоть до её окончания приём других запросов запрещается. Очерёдность выполнения программ для этого случая можно представить в виде следующей диаграммы (а):

Поскольку прерывание допускается после окончания текущей МК или команды, то время реакции определяется в основном длительностью выполнения МК или команды, соответственно. Для одного и того же запроса задержки в исполнении прерывающей программы зависят от числа прерывающих программ, имеющих старший приоритет. Поэтому время реакции определяют для запроса с наивысшим приоритетом. Затраты времени на переключение программ (издержки прерывания) равны суммарному расходу времени на запоминание t. З и восстановление t. В вектора состояния процессора: t. ИЗД = t. З + t. В. Глубина прерывания определяется максимальным числом программ, которые могут прерывать друга. Глубина прерывания равна 1, если после перехода к прерывающей программе и вплоть до её окончания приём других запросов запрещается. Очерёдность выполнения программ для этого случая можно представить в виде следующей диаграммы (а):

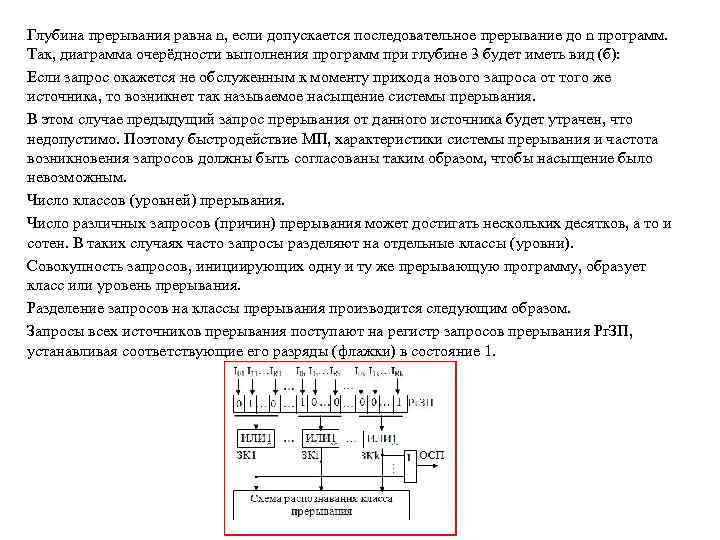

Глубина прерывания равна n, если допускается последовательное прерывание до n программ. Так, диаграмма очерёдности выполнения программ при глубине 3 будет иметь вид (б): Если запрос окажется не обслуженным к моменту прихода нового запроса от того же источника, то возникнет так называемое насыщение системы прерывания. В этом случае предыдущий запрос прерывания от данного источника будет утрачен, что недопустимо. Поэтому быстродействие МП, характеристики системы прерывания и частота возникновения запросов должны быть согласованы таким образом, чтобы насыщение было невозможным. Число классов (уровней) прерывания. Число различных запросов (причин) прерывания может достигать нескольких десятков, а то и сотен. В таких случаях часто запросы разделяют на отдельные классы (уровни). Совокупность запросов, инициирующих одну и ту же прерывающую программу, образует класс или уровень прерывания. Разделение запросов на классы прерывания производится следующим образом. Запросы всех источников прерывания поступают на регистр запросов прерывания Рг. ЗП, устанавливая соответствующие его разряды (флажки) в состояние 1.

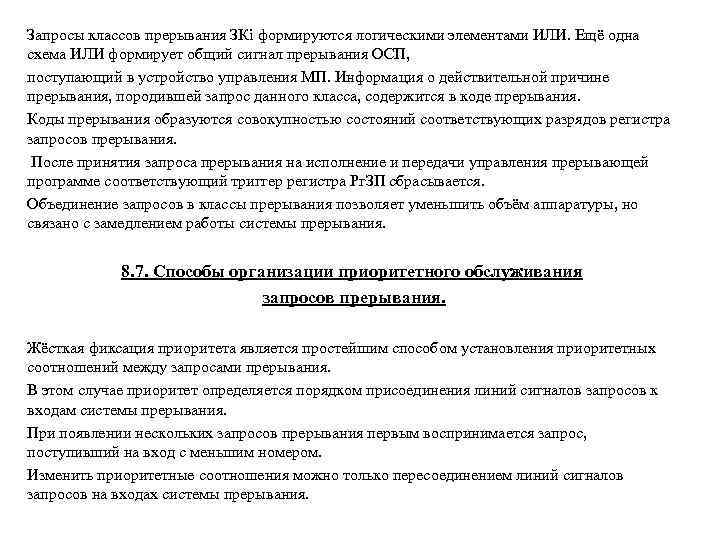

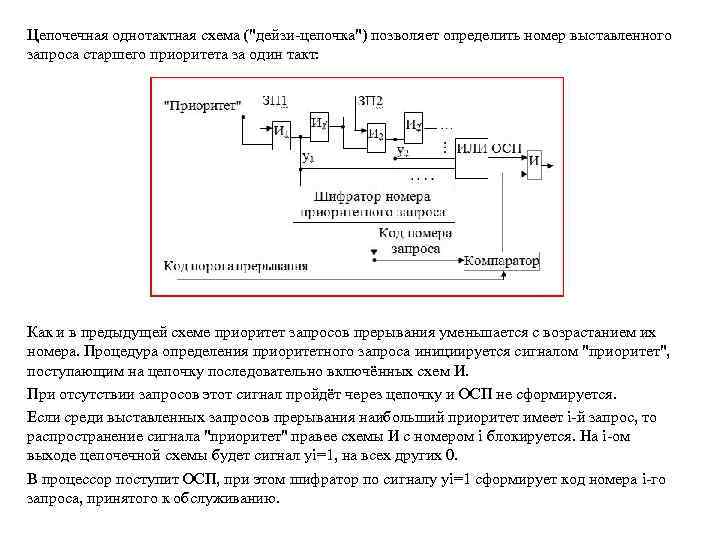

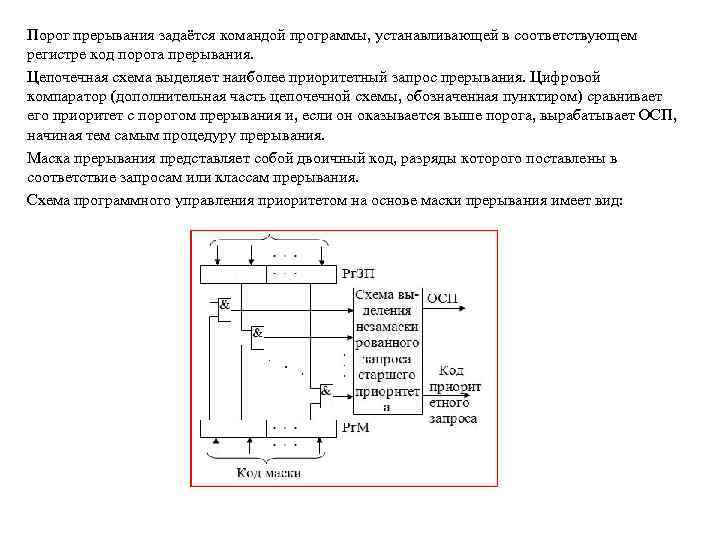

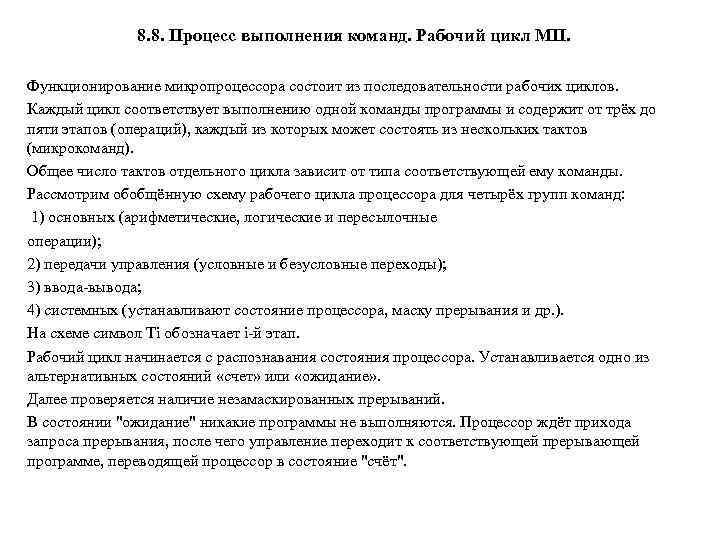

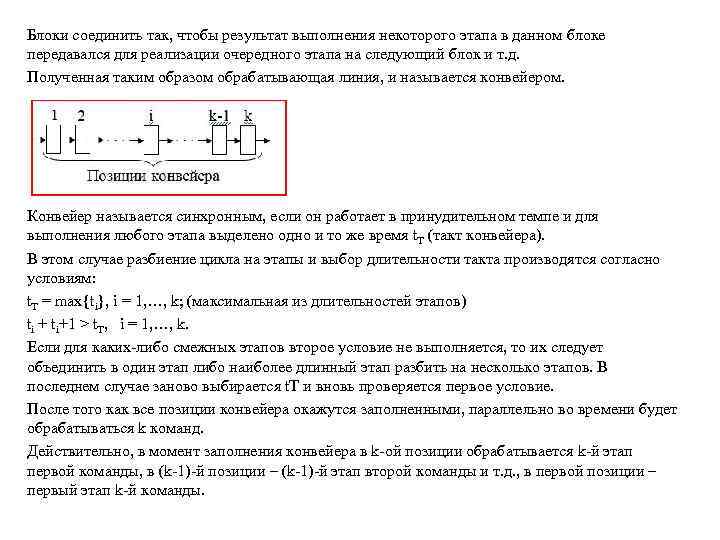

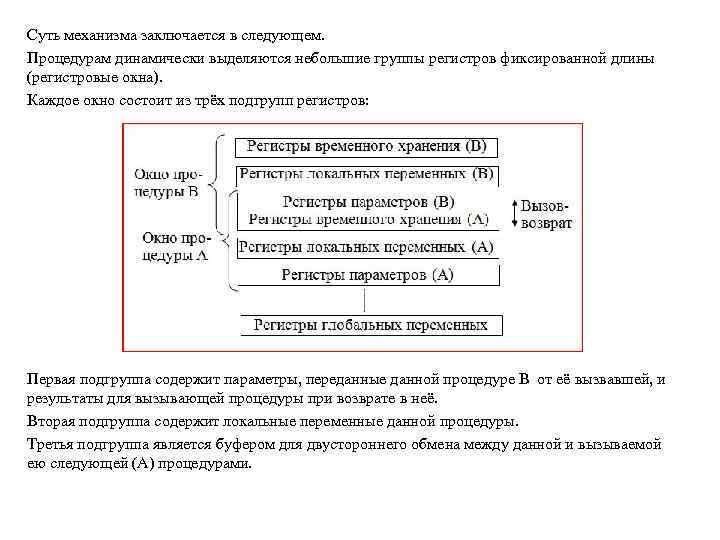

Глубина прерывания равна n, если допускается последовательное прерывание до n программ. Так, диаграмма очерёдности выполнения программ при глубине 3 будет иметь вид (б): Если запрос окажется не обслуженным к моменту прихода нового запроса от того же источника, то возникнет так называемое насыщение системы прерывания. В этом случае предыдущий запрос прерывания от данного источника будет утрачен, что недопустимо. Поэтому быстродействие МП, характеристики системы прерывания и частота возникновения запросов должны быть согласованы таким образом, чтобы насыщение было невозможным. Число классов (уровней) прерывания. Число различных запросов (причин) прерывания может достигать нескольких десятков, а то и сотен. В таких случаях часто запросы разделяют на отдельные классы (уровни). Совокупность запросов, инициирующих одну и ту же прерывающую программу, образует класс или уровень прерывания. Разделение запросов на классы прерывания производится следующим образом. Запросы всех источников прерывания поступают на регистр запросов прерывания Рг. ЗП, устанавливая соответствующие его разряды (флажки) в состояние 1.