d87681af2980cab76f918fdeaf84bd88.ppt

- Количество слайдов: 12

VILAB Meeting, Linkoeping, Sweden, 13 -14 August 1999 VILAB: Microelectronics Virtual Laboratory for Cooperation in Research and Knowledge Transfer Partner Progress Report 980901 - 990901 Tallinn Technical University Raimund Ubar TALLINN TECHNICAL UNIVERSITY, ESTONIA

VILAB Meeting, Linkoeping, Sweden, 13 -14 August 1999 VILAB: Partner Progress Report (980901 - 990901) Tallinn Technical University List of subprojects: SP 1: Improving FPGA Design Flow by Introducing Test Activities Partners: The goal: IIS/EAS, TTU Integrate the ATPG developed in TTU into the FPGA Design Flow used at the IIS/EAS SP 2: Testability Driven System Design Flow Partners: The goal: LIU, TTU, TUD Developing behavioral level ATPG and Testability Analyser for preanalysing SW/HW codesigns SP 3: IDDQ ATPG and Testing Partners: The goal: ICS, SUT, TTU Developing an ATPG for combined voltage and current testing and interfacing it to commercial design tools (Mentor Graphics) TALLINN TECHNICAL UNIVERSITY, ESTONIA

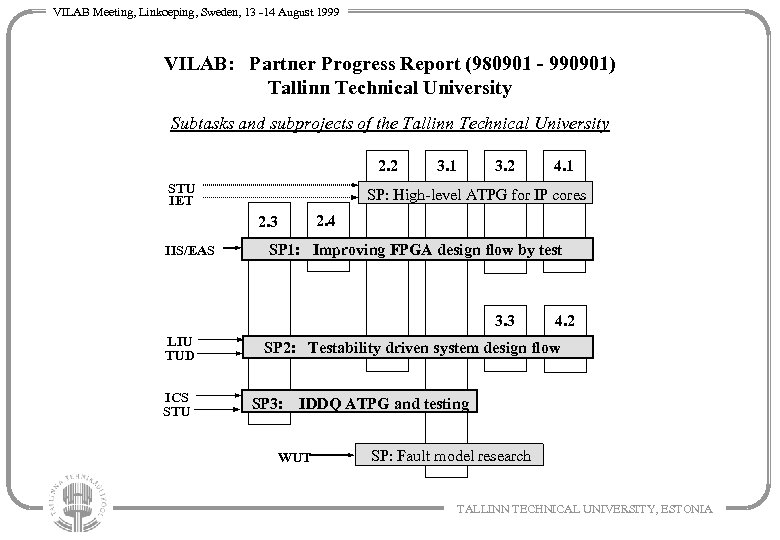

VILAB Meeting, Linkoeping, Sweden, 13 -14 August 1999 VILAB: Partner Progress Report (980901 - 990901) Tallinn Technical University Subtasks and subprojects of the Tallinn Technical University 2. 2 STU IET 2. 4 SP 1: Improving FPGA design flow by test 3. 3 LIU TUD ICS STU 4. 1 SP: High-level ATPG for IP cores 2. 3 IIS/EAS 3. 2 3. 1 4. 2 SP 2: Testability driven system design flow SP 3: IDDQ ATPG and testing WUT SP: Fault model research TALLINN TECHNICAL UNIVERSITY, ESTONIA

VILAB Meeting, Linkoeping, Sweden, 13 -14 August 1999 VILAB: Partner Progress Report (980901 - 990901) Tallinn Technical University Subtask 2. 2 (Links to: IIS/EAS, LIU – Subprojects SP 1, SP 2 ) Results: • Fault simulator and ATPG for digital systems • WWW Distribution of test generation and fault simulation tools (Turbo-Tester) via URL http: //www. pld. ttu. ee/tt/ Tools can be installed: Solaris 2. x, Windows 95/98/NT Current distribution contains utilities for gate-level circuits: à three test generators · deterministic · genetic algorithms · random à multi-valued simulator for dynamic signal analysis à fault simulator à EDIF design interface with a library compiler TALLINN TECHNICAL UNIVERSITY, ESTONIA

VILAB Meeting, Linkoeping, Sweden, 13 -14 August 1999 VILAB: Partner Progress Report (980901 - 990901) Tallinn Technical University Subtask 2. 3 (Link to: ICS - Subproject SP 3 ) Creation of interfaces between tools Results: Interfaces between design and test generation tools · · EDIF interface created at TTU was modified to support translation into ISCAS 85 format used by test tools of ICS Interface between high-level VHDL description and Hierarchical Test Pattern Generator Subtask 2. 4 (Local use – Subproject SP 1) Creation of the set of benchmark circuits for evaluating the quality of test tools Results: The following benchmarks are currently available at TTU: · · · Greatest Common Divisor (GCD) Differential Equation (DIFFEQ) 8 -bit multiplier (MULT 8 x 8) Data files are available for: behavioral, RTL (in VHDL) and gate-level (in EDIF) descriptions TALLINN TECHNICAL UNIVERSITY, ESTONIA

VILAB Meeting, Linkoeping, Sweden, 13 -14 August 1999 VILAB: Partner Progress Report (980901 - 990901) Tallinn Technical University Subtask 3. 1 (Links to IIS/EAS, LIU, ICS – SP 1, SP 2, SP 3) Cooperative research in the field of design for testability and test generation (TTU) Results: • ATPG developed at TTU has been improved to reach very high speed of test generation (SP 1 with IIS/EAS) Publications: DATE`99, ETW`99, Semicon`99 (Singapore) • • IDDQ ATPG development, linking to commercial design tool (SP 3 with IES) DD-based diagnostic model generation from VHDL (SP 2 with LIU) Publications: Kluwer Acad. Publishers Under development: • • ATPG based testability analysis (SP 2 with LIU) Testability driven ATPG (SP 2 with LIU) Under discussion (Links to WUT, Uni Stuttgart, TIMA): • • • Investigations on the fault model quality (WUT) ATPG for functional BIST (Uni Stuttgart) Design error diagnosis in digital circuits (TIMA) TALLINN TECHNICAL UNIVERSITY, ESTONIA

VILAB Meeting, Linkoeping, Sweden, 13 -14 August 1999 VILAB: Partner Progress Report (980901 - 990901) Tallinn Technical University Subtask 3. 2 (Links to IIS/EAS, LIU – SP 1, SP 2) Cooperative research in VLSI design for applications in digital data processing (IET) Results: • Concept of integrating an ATPG into the FPGA design flow (with IIS/EAS) Publications: Joint VILAB publication (IIS/EAS & TTU) • Hierarchical diagnostic model for VLSI designs Converters and model generators developed: · from RT level VHDL into high-level DD-based diagnostic model · from gate-level EDIF into low-level BDD-based diagnostic model Under development: • ATPG for testing SW/HW codesigns (with LIU) Under discussion (Link to IET): • High level test generation for IP cores TALLINN TECHNICAL UNIVERSITY, ESTONIA

VILAB Meeting, Linkoeping, Sweden, 13 -14 August 1999 VILAB: Partner Progress Report (980901 - 990901) Tallinn Technical University Subtask 3. 3 (Links to LIU, TUD – SP 2) Cooperative research in the field of hardware-software codesign (TUD) Results: • A fast cycle-based simulator for verification hardware components of HW/SW codesigns was developed Publication: Date`99 Under development: • New DD-model for diagnostic describing of behavioral descriptions of specifications for SW/HW codesign is being developed The diagnostic model will be used for developing a behavioral level ATPG and Testability Analyser for preanalysing SW/HW codesigns Publication: Kluwer Academic Publishers TALLINN TECHNICAL UNIVERSITY, ESTONIA

VILAB Meeting, Linkoeping, Sweden, 13 -14 August 1999 VILAB: Partner Progress Report (980901 - 990901) Tallinn Technical University Subtask 4. 1 (Links to IIS/EAS, LIU, TUD – SP 1, SP 2) Cooperative research in the field of ASIC development using cores (IET) Results: Improving FPGA design flow by introduced test activities · A novel FPGA design flow combined with ATPG was developed and experimented on a real FPGA circuit for telecommunication · Preliminary experimental results have shown the advantages of using structural tests generated by ATPG compared to using functional test sequences created by designer Publications: Joint VILAB publication (IIS/EAS & TTU) Under development: Design error diagnosis in digital circuits (Link to: TIMA Laboratory) Under discussion: ATPG for functional BIST (Links to: Uni Stuttgart, IIS/EAS) TALLINN TECHNICAL UNIVERSITY, ESTONIA

VILAB Meeting, Linkoeping, Sweden, 13 -14 August 1999 VILAB: Partner Progress Report (980901 - 990901) Tallinn Technical University Subtask 4. 2 (Links to IIS/EAS, LIU, TUD – SP 1, SP 2) Cooperative research in the field of HW/SW codesign developments (TUD) SP 2 - Testability Driven System Design Flow Partners: TTU, LIU, TUD The main goal of the subproject is to investigate a complete SW/HW codesign flow with emphasis on testability analysis and test generation Results: For such investigations, the interface between High Level Synthesis System (its output VHDL description) and the high-level ATPG (its input Decision Diagrams) was created during the 1 st project year Under development: Experimental work is to be carried out in cooperation between LIU and TTU TALLINN TECHNICAL UNIVERSITY, ESTONIA

VILAB Meeting, Linkoeping, Sweden, 13 -14 August 1999 VILAB: Partner Progress Report (980901 - 990901) Tallinn Technical University Subtask 5. 3 (Link to TU Ilmenau) Cooperative research in multimedial knowledge transfer course on “Advanced methods on Test“ (TTU) Results: • Course on Design and Test has been developed The course was carried out (in cooperation with LIU) at Ericsson Telecom AB • Concept for Computer Based Interactive Training in the field of "Digital Design and Test" · The concept was developed in cooperation with TU Ilmenau · It consists on Java applets, user's Web browser and a server, performing all computations · Using the interactive teaching software, user can experiment with different methods of test pattern generation, fault simulation, design for testability, built-in self-test, and fault diagnosis Under development: Teaching software for teaching Design and Test TALLINN TECHNICAL UNIVERSITY, ESTONIA

VILAB Meeting, Linkoeping, Sweden, 13 -14 August 1999 VILAB: Partner Progress Report (980901 - 990901) Tallinn Technical University Publications: • VILAB joint publication: – • G. Elst, K-H. Diener, E. Ivask, J. Raik, R. Ubar. FPGA Design Flow with Automated Test Generation German 11 th Workshop on Test Technology and Reliability of Circuits and Systems. Potsdam, 1999, pp. 120 -123. Other publications: – – – R. Ubar, J. Raik. Hierarchical Test Generation for Complex Digital Systems with Control and Data Processing Parts. SEMICON Techn. Symp. , Singapur May 3 -6, 1999, pp. 43 -64. J. Raik, R. Ubar. High-Level Path Activation Technique to Speed Up Sequential Circuit Test Generation. ETW, Constance, May 25 -28, 1999, 5 p. R. Leveugle, R. Ubar. Modeling VHDL Clock-Driven Multi-Processes by Decision Diagrams. In "Mixed Design of Integrated Circuits and Systems". Kluwer Academic Publishers, 1999. R. Ubar, A. Moraviec, J. Raik. Cycle-based Simulation with Decision Diagrams. DATE. Munich, March 9 -12, 1999, pp. 454 -458. R. Ubar, A. Jutman. Hierarchical Design Error Diagnosis in Combinational Circuits by Stuck-at Fault Test Patterns. 6 th MIXDES, Krakow, June 17 -19, 1999, pp. 437 -442. TALLINN TECHNICAL UNIVERSITY, ESTONIA

d87681af2980cab76f918fdeaf84bd88.ppt