VHDL Лекция №

VHDL Лекция №

История и цели создания n n n Язык VHDL был разработан в 1983 г. по заказу МО США для формального описания логических схем на всех этапах разработки электронных систем. Аббревиатура VHDL (Very High Speed Integrated Circuit Hardware Description Language) переводится как язык описания высокоскоростных интегрированных схем. Синтаксис VHDL очень похож на язык Ада. Дело в том, что компания Intermetrics, которой Пентагон поручил специфицировать VHDL, имела большой опыт работы с языком Ада.

История и цели создания n n n Язык VHDL был разработан в 1983 г. по заказу МО США для формального описания логических схем на всех этапах разработки электронных систем. Аббревиатура VHDL (Very High Speed Integrated Circuit Hardware Description Language) переводится как язык описания высокоскоростных интегрированных схем. Синтаксис VHDL очень похож на язык Ада. Дело в том, что компания Intermetrics, которой Пентагон поручил специфицировать VHDL, имела большой опыт работы с языком Ада.

КЛАССЫ И ОБЪЕКТЫ n n VHDL не предусмотрена возможность создавать новые классы, они уже встроены и их всего три: ¨ constant - константа. ¨ variable - переменная; ¨ signal - сигнал; сигнал, введен для описания цифровых схем и обладает многими свойствам реальных сигналов в цифровой технике: скорость распространения, ¨ способы взаимодействия с другими сигналами и пр. ¨

КЛАССЫ И ОБЪЕКТЫ n n VHDL не предусмотрена возможность создавать новые классы, они уже встроены и их всего три: ¨ constant - константа. ¨ variable - переменная; ¨ signal - сигнал; сигнал, введен для описания цифровых схем и обладает многими свойствам реальных сигналов в цифровой технике: скорость распространения, ¨ способы взаимодействия с другими сигналами и пр. ¨

Объявление объектов n n Прежде чем использовать какой либо объект, его нужно объявить членом какого-нибудь класса. Например, объявляются три объекта х, у и gnd: ¨ constant gnd : bit : ='0'; ¨ variable y : bit; ¨ signal z : bit;

Объявление объектов n n Прежде чем использовать какой либо объект, его нужно объявить членом какого-нибудь класса. Например, объявляются три объекта х, у и gnd: ¨ constant gnd : bit : ='0'; ¨ variable y : bit; ¨ signal z : bit;

n Далее мы можем записать следующий VHDL код: ¨ y : = gnd; ¨ z <= y;

n Далее мы можем записать следующий VHDL код: ¨ y : = gnd; ¨ z <= y;

n n Первое - после объявления константы должно быть её определение (constant const : bit : ='1'; ) Константы могут объявляться в интерфейсах, архитектурах, процессах, процедурах и функциях. Если символов ": =" нет в декларации константы, то константа называется задержанной. Такие константы могут быть в разделе деклараций пакета. Соответствующая полная декларация должна быть в теле пакета.

n n Первое - после объявления константы должно быть её определение (constant const : bit : ='1'; ) Константы могут объявляться в интерфейсах, архитектурах, процессах, процедурах и функциях. Если символов ": =" нет в декларации константы, то константа называется задержанной. Такие константы могут быть в разделе деклараций пакета. Соответствующая полная декларация должна быть в теле пакета.

Объявления n n n Второе - сигналы объявляются в области объявлений архитектурного тела и видны во всем этом теле или в области объявлений интерфейса, тогда они видны во всех архитектурах, использующих данный интерфейс. Порты по умолчанию являются сигналами. Третье - переменные объявляются в области деклараций процесса, функции или процедуры и видны только там.

Объявления n n n Второе - сигналы объявляются в области объявлений архитектурного тела и видны во всем этом теле или в области объявлений интерфейса, тогда они видны во всех архитектурах, использующих данный интерфейс. Порты по умолчанию являются сигналами. Третье - переменные объявляются в области деклараций процесса, функции или процедуры и видны только там.

Объявления переменных n n n Eсть возможность сделать переменную глобальной, объявить ее в архитектуре или в интерфейсе следующим VHDL-кодом: shared variable y : bit; Переменным можно задавать начальное значение при объявлении: variable y : bit: ='1';

Объявления переменных n n n Eсть возможность сделать переменную глобальной, объявить ее в архитектуре или в интерфейсе следующим VHDL-кодом: shared variable y : bit; Переменным можно задавать начальное значение при объявлении: variable y : bit: ='1';

Пример комментариев n n n n n КОММЕНТАРИИ. . . прокомментируйте вашу позицию, а то непонятно. . . Комментарии отделяются от основного VHDL-кода двойным штрихом и действуют до конца строки: ---------------- -- Пример комментариев -- ---------------- -- -- Управление индикаторами сигналов LINK n. LEDL 1 <= GND when n. LINKA ='0' else TRI; -- канал А n. LEDL 2 <= GND when n. LINKB ='0' else TRI; -- канал В

Пример комментариев n n n n n КОММЕНТАРИИ. . . прокомментируйте вашу позицию, а то непонятно. . . Комментарии отделяются от основного VHDL-кода двойным штрихом и действуют до конца строки: ---------------- -- Пример комментариев -- ---------------- -- -- Управление индикаторами сигналов LINK n. LEDL 1 <= GND when n. LINKA ='0' else TRI; -- канал А n. LEDL 2 <= GND when n. LINKB ='0' else TRI; -- канал В

Типы данных n n n type boolean is (false, true); -- логический тип type bit is ('0', '1'); -- битовый тип type character is ( -- символьный тип

Типы данных n n n type boolean is (false, true); -- логический тип type bit is ('0', '1'); -- битовый тип type character is ( -- символьный тип

n n type severity_level is (note, warning, error, failure); -- перечислимый тип type integer is range -2147483647 to 2147483647; -- целый тип type real is range -1. 0 E 308 to 1. 0 E 308; -- вещественный тип type time is range -2147483648 to 2147483647; -- целый тип

n n type severity_level is (note, warning, error, failure); -- перечислимый тип type integer is range -2147483647 to 2147483647; -- целый тип type real is range -1. 0 E 308 to 1. 0 E 308; -- вещественный тип type time is range -2147483648 to 2147483647; -- целый тип

n n По аналогии пользователь может создавать свои типы данных, например, определим перечислимый тип - день недели: type day_t is (mon, tue, wen, thu, fri, sat, sun); signal day : day_t; day <= mon;

n n По аналогии пользователь может создавать свои типы данных, например, определим перечислимый тип - день недели: type day_t is (mon, tue, wen, thu, fri, sat, sun); signal day : day_t; day <= mon;

n n n Типы могут иметь подтипы (subtype). Так в библиотеке STD определены следующие подтипы: subtype natural is integer range 0 to integer'high; -- подтип натуральных чисел subtype pozitive is integer range 1 to integer'high; -- подтип положительных чисел Здесь integer'high - наибольшее значение типа integer. В данном случае integer'high = 2147483647 и наоборот integer'low = -2147483647. Это атрибуты

n n n Типы могут иметь подтипы (subtype). Так в библиотеке STD определены следующие подтипы: subtype natural is integer range 0 to integer'high; -- подтип натуральных чисел subtype pozitive is integer range 1 to integer'high; -- подтип положительных чисел Здесь integer'high - наибольшее значение типа integer. В данном случае integer'high = 2147483647 и наоборот integer'low = -2147483647. Это атрибуты

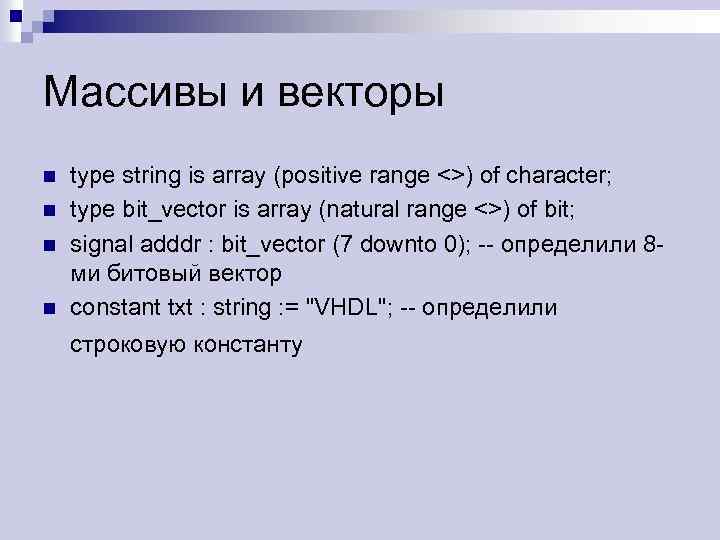

Массивы и векторы n n type string is array (positive range <>) of character; type bit_vector is array (natural range <>) of bit; signal adddr : bit_vector (7 downto 0); -- определили 8 ми битовый вектор constant txt : string : = "VHDL"; -- определили строковую константу

Массивы и векторы n n type string is array (positive range <>) of character; type bit_vector is array (natural range <>) of bit; signal adddr : bit_vector (7 downto 0); -- определили 8 ми битовый вектор constant txt : string : = "VHDL"; -- определили строковую константу

Физические типы данных n units -- единицы времени fs; ps = 1000 fs; ns = 1000 ps; us = 1000 ns; ms = 1000 us; sec = 1000 ms; min = 60 sec; hr = 60 min; end units;

Физические типы данных n units -- единицы времени fs; ps = 1000 fs; ns = 1000 ps; us = 1000 ns; ms = 1000 us; sec = 1000 ms; min = 60 sec; hr = 60 min; end units;

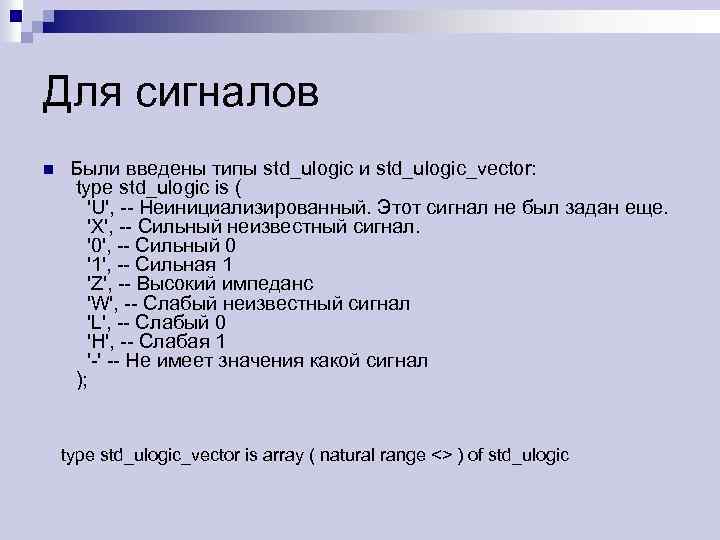

Для сигналов n Были введены типы std_ulogic и std_ulogic_vector: type std_ulogic is ( 'U', -- Неинициализированный. Этот сигнал не был задан еще. 'X', -- Сильный неизвестный сигнал. '0', -- Сильный 0 '1', -- Сильная 1 'Z', -- Высокий импеданс 'W', -- Слабый неизвестный сигнал 'L', -- Слабый 0 'H', -- Слабая 1 '-' -- Не имеет значения какой сигнал ); type std_ulogic_vector is array ( natural range <> ) of std_ulogic

Для сигналов n Были введены типы std_ulogic и std_ulogic_vector: type std_ulogic is ( 'U', -- Неинициализированный. Этот сигнал не был задан еще. 'X', -- Сильный неизвестный сигнал. '0', -- Сильный 0 '1', -- Сильная 1 'Z', -- Высокий импеданс 'W', -- Слабый неизвестный сигнал 'L', -- Слабый 0 'H', -- Слабая 1 '-' -- Не имеет значения какой сигнал ); type std_ulogic_vector is array ( natural range <> ) of std_ulogic

n type std_ulogic_vector is array ( natural range <> ) of std_ulogic

n type std_ulogic_vector is array ( natural range <> ) of std_ulogic

n n n В зависимости от наличия или отсутствия размерности, объявление типа массива может быть двух видов: type_name is array (range) of element_type; type_name is array (type range <>) of element_type;

n n n В зависимости от наличия или отсутствия размерности, объявление типа массива может быть двух видов: type_name is array (range) of element_type; type_name is array (type range <>) of element_type;

n n n Первый вид используется для типов с заданной размерностью и при объявлении объекта размерность уже будет задана типом: type BYTE is array (7 downto 0) of BIT; -- объявили 8 ми битовый тип signal BYT 1 : BYTE; -- объявили 8 -ми битовый массив

n n n Первый вид используется для типов с заданной размерностью и при объявлении объекта размерность уже будет задана типом: type BYTE is array (7 downto 0) of BIT; -- объявили 8 ми битовый тип signal BYT 1 : BYTE; -- объявили 8 -ми битовый массив

n n n Второй вид используется для типов без размерности, тогда размерность должна указываться при объявлении объекта: type MATRIX is array (POSITIVE range <>) of REAL; -- объявили вектор реальных чисел signal MATRIX 1 : MATRIX(1 to 3); -- объявили вектор из трех реальных чисел

n n n Второй вид используется для типов без размерности, тогда размерность должна указываться при объявлении объекта: type MATRIX is array (POSITIVE range <>) of REAL; -- объявили вектор реальных чисел signal MATRIX 1 : MATRIX(1 to 3); -- объявили вектор из трех реальных чисел

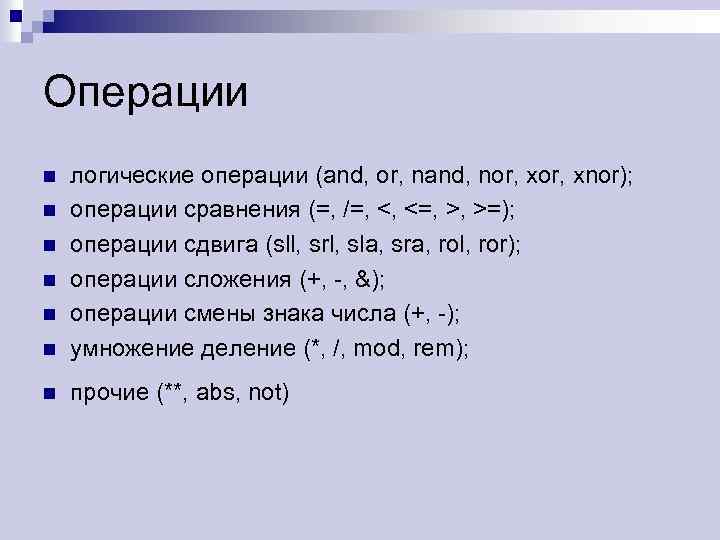

Операции n логические операции (and, or, nand, nor, xnor); операции сравнения (=, /=, <, <=, >, >=); операции сдвига (sll, srl, sla, sra, rol, ror); операции сложения (+, -, &); операции смены знака числа (+, -); умножение деление (*, /, mod, rem); n прочие (**, abs, not) n n n

Операции n логические операции (and, or, nand, nor, xnor); операции сравнения (=, /=, <, <=, >, >=); операции сдвига (sll, srl, sla, sra, rol, ror); операции сложения (+, -, &); операции смены знака числа (+, -); умножение деление (*, /, mod, rem); n прочие (**, abs, not) n n n

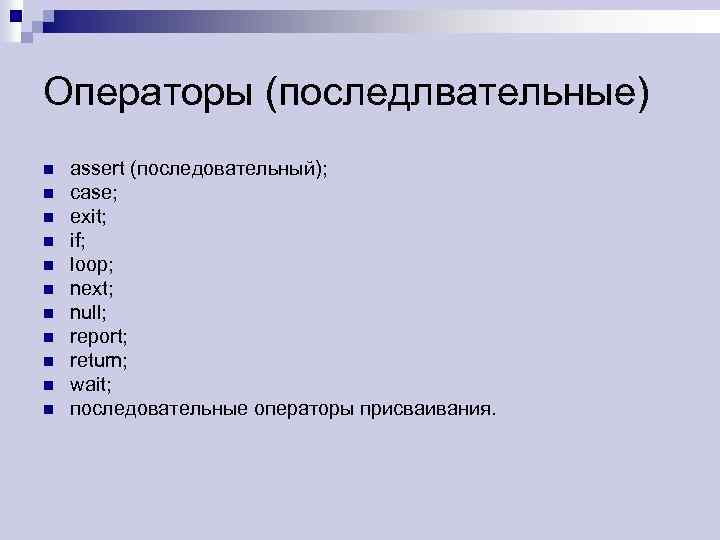

Операторы (последлвательные) n n n assert (последовательный); case; exit; if; loop; next; null; report; return; wait; последовательные операторы присваивания.

Операторы (последлвательные) n n n assert (последовательный); case; exit; if; loop; next; null; report; return; wait; последовательные операторы присваивания.

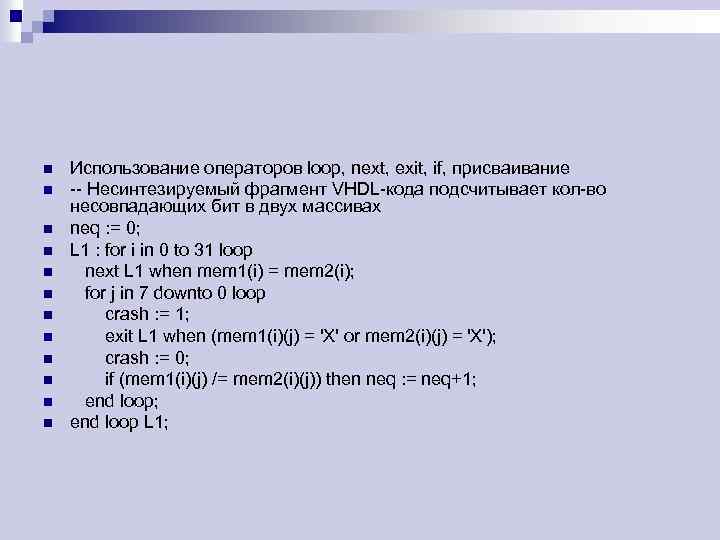

n n n Использование операторов loop, next, exit, if, присваивание -- Несинтезируемый фрагмент VHDL-кода подсчитывает кол-во несовпадающих бит в двух массивах neq : = 0; L 1 : for i in 0 to 31 loop next L 1 when mem 1(i) = mem 2(i); for j in 7 downto 0 loop crash : = 1; exit L 1 when (mem 1(i)(j) = 'X' or mem 2(i)(j) = 'X'); crash : = 0; if (mem 1(i)(j) /= mem 2(i)(j)) then neq : = neq+1; end loop; end loop L 1;

n n n Использование операторов loop, next, exit, if, присваивание -- Несинтезируемый фрагмент VHDL-кода подсчитывает кол-во несовпадающих бит в двух массивах neq : = 0; L 1 : for i in 0 to 31 loop next L 1 when mem 1(i) = mem 2(i); for j in 7 downto 0 loop crash : = 1; exit L 1 when (mem 1(i)(j) = 'X' or mem 2(i)(j) = 'X'); crash : = 0; if (mem 1(i)(j) /= mem 2(i)(j)) then neq : = neq+1; end loop; end loop L 1;

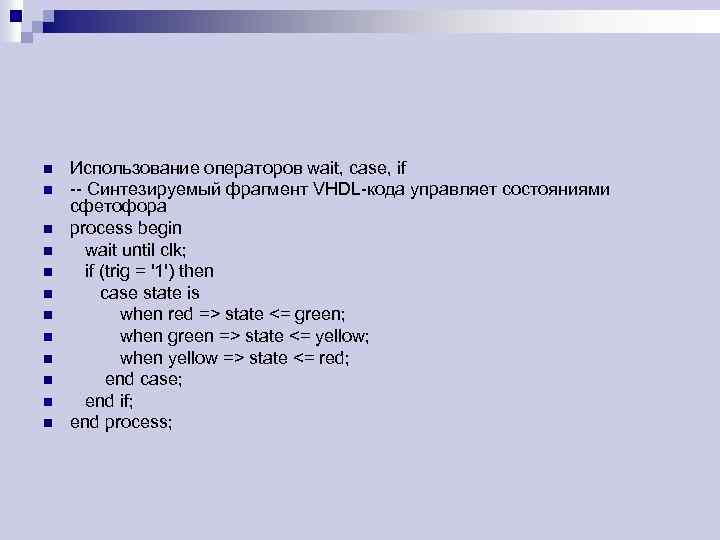

n n n Использование операторов wait, case, if -- Синтезируемый фрагмент VHDL-кода управляет состояниями сфетофора process begin wait until clk; if (trig = '1') then case state is when red => state <= green; when green => state <= yellow; when yellow => state <= red; end case; end if; end process;

n n n Использование операторов wait, case, if -- Синтезируемый фрагмент VHDL-кода управляет состояниями сфетофора process begin wait until clk; if (trig = '1') then case state is when red => state <= green; when green => state <= yellow; when yellow => state <= red; end case; end if; end process;

Параллельные операторы assert (параллельный); n block; n generate; n process; n применение компонентов (port map. . . ); n параллельные операторы присваивания. n

Параллельные операторы assert (параллельный); n block; n generate; n process; n применение компонентов (port map. . . ); n параллельные операторы присваивания. n

n Пример защелки с использованием охранного выражения L 1: block (LE = '1') begin Q <= guarded D; -- Выполнится только при LE = '1' n end block L 1; n n n

n Пример защелки с использованием охранного выражения L 1: block (LE = '1') begin Q <= guarded D; -- Выполнится только при LE = '1' n end block L 1; n n n

n n n Пример простых блоков BLOCK 1: block signal Q : std_logic; -- Этот сигнал Q виден только в BLOCK 1 begin Q <= A and B; end block BLOCK 1; ------------------ BLOCK 2: block signal Q : std_logic; -- Этот сигнал Q виден только в BLOCK 2 begin Q <= C and D; end block BLOCK 2;

n n n Пример простых блоков BLOCK 1: block signal Q : std_logic; -- Этот сигнал Q виден только в BLOCK 1 begin Q <= A and B; end block BLOCK 1; ------------------ BLOCK 2: block signal Q : std_logic; -- Этот сигнал Q виден только в BLOCK 2 begin Q <= C and D; end block BLOCK 2;

Интерфейс n n n n n entity NAME_ENTITY is -------------- generic ( -- Здесь указываются параметры); port ( -- Здесь указываются порты); -- Область объявлений begin --ставится, если далее следуют параллельные операторы интерфейса -- Параллельные операторы (обычно assert), вызовы подпрограмм end NAME_ENTITY;

Интерфейс n n n n n entity NAME_ENTITY is -------------- generic ( -- Здесь указываются параметры); port ( -- Здесь указываются порты); -- Область объявлений begin --ставится, если далее следуют параллельные операторы интерфейса -- Параллельные операторы (обычно assert), вызовы подпрограмм end NAME_ENTITY;

n n n in - входной порт (только для чтения значения сигнала); out - выходной порт (только для записи значения сигнала); inout - двунаправленный порт (чтение и запись); buffer - выходной порт, значение которого можно считывать; linkage - двунаправленный порт с ограниченным использованием (практически не используется).

n n n in - входной порт (только для чтения значения сигнала); out - выходной порт (только для записи значения сигнала); inout - двунаправленный порт (чтение и запись); buffer - выходной порт, значение которого можно считывать; linkage - двунаправленный порт с ограниченным использованием (практически не используется).

n Архитектура содержит две основные части: часть, содержащую описания (декларации); ¨ часть, содержащую исполняемые операторы. ¨

n Архитектура содержит две основные части: часть, содержащую описания (декларации); ¨ часть, содержащую исполняемые операторы. ¨

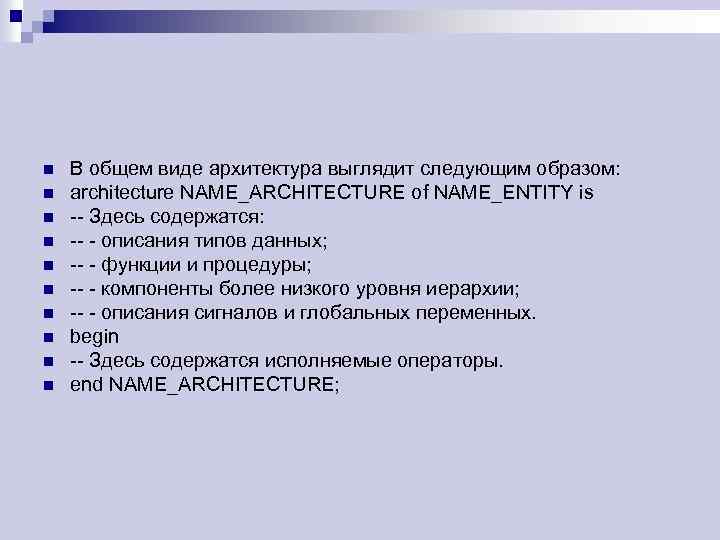

n n n n n В общем виде архитектура выглядит следующим образом: architecture NAME_ARCHITECTURE of NAME_ENTITY is -- Здесь содержатся: -- - описания типов данных; -- - функции и процедуры; -- - компоненты более низкого уровня иерархии; -- - описания сигналов и глобальных переменных. begin -- Здесь содержатся исполняемые операторы. end NAME_ARCHITECTURE;

n n n n n В общем виде архитектура выглядит следующим образом: architecture NAME_ARCHITECTURE of NAME_ENTITY is -- Здесь содержатся: -- - описания типов данных; -- - функции и процедуры; -- - компоненты более низкого уровня иерархии; -- - описания сигналов и глобальных переменных. begin -- Здесь содержатся исполняемые операторы. end NAME_ARCHITECTURE;

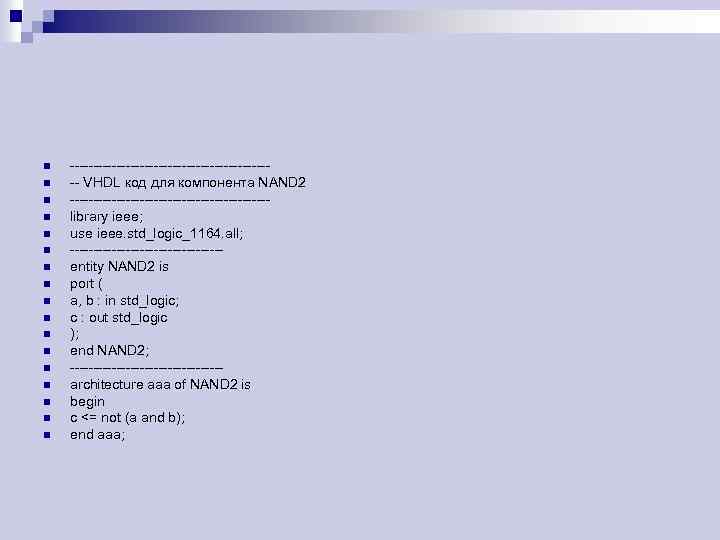

n n n n n ---------------------- -- VHDL код для компонента NAND 2 ---------------------- library ieee; use ieee. std_logic_1164. all; ----------------- entity NAND 2 is port ( a, b : in std_logic; c : out std_logic ); end NAND 2; ----------------- architecture aaa of NAND 2 is begin c <= not (a and b); end aaa;

n n n n n ---------------------- -- VHDL код для компонента NAND 2 ---------------------- library ieee; use ieee. std_logic_1164. all; ----------------- entity NAND 2 is port ( a, b : in std_logic; c : out std_logic ); end NAND 2; ----------------- architecture aaa of NAND 2 is begin c <= not (a and b); end aaa;

Структурное описание n n n n n n -- VHDL код для трех компонентов NAND 2 ------------------------- library ieee; use ieee. std_logic_1164. all; ----------------- entity NAND 2 X 3 is port ( a, b, c, d : in std_logic; q : out std_logic ); end NAND 2 X 3; ----------------- architecture bbb of NAND 2 X 3 is signal s 1, s 2 : std_logic; component NAND 2 port ( a, b : in std_logic; c : out std_logic); end component; begin D 1: NAND 2 port map (a => a, b => b, c => s 1); D 2: NAND 2 port map (a => c, b => d, c => s 2); D 3: NAND 2 port map (a =>s 1, b =>s 2, c =>q); end bbb;

Структурное описание n n n n n n -- VHDL код для трех компонентов NAND 2 ------------------------- library ieee; use ieee. std_logic_1164. all; ----------------- entity NAND 2 X 3 is port ( a, b, c, d : in std_logic; q : out std_logic ); end NAND 2 X 3; ----------------- architecture bbb of NAND 2 X 3 is signal s 1, s 2 : std_logic; component NAND 2 port ( a, b : in std_logic; c : out std_logic); end component; begin D 1: NAND 2 port map (a => a, b => b, c => s 1); D 2: NAND 2 port map (a => c, b => d, c => s 2); D 3: NAND 2 port map (a =>s 1, b =>s 2, c =>q); end bbb;

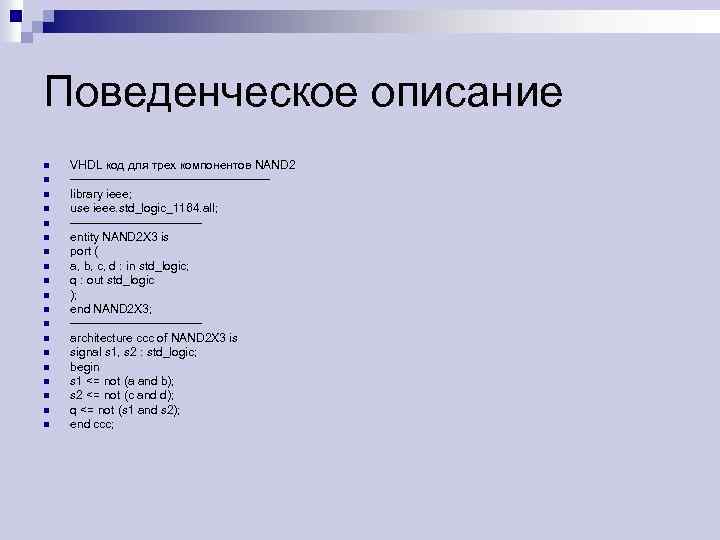

Поведенческое описание n n n n n VHDL код для трех компонентов NAND 2 ------------------------- library ieee; use ieee. std_logic_1164. all; ----------------- entity NAND 2 X 3 is port ( a, b, c, d : in std_logic; q : out std_logic ); end NAND 2 X 3; ----------------- architecture ccc of NAND 2 X 3 is signal s 1, s 2 : std_logic; begin s 1 <= not (a and b); s 2 <= not (c and d); q <= not (s 1 and s 2); end ccc;

Поведенческое описание n n n n n VHDL код для трех компонентов NAND 2 ------------------------- library ieee; use ieee. std_logic_1164. all; ----------------- entity NAND 2 X 3 is port ( a, b, c, d : in std_logic; q : out std_logic ); end NAND 2 X 3; ----------------- architecture ccc of NAND 2 X 3 is signal s 1, s 2 : std_logic; begin s 1 <= not (a and b); s 2 <= not (c and d); q <= not (s 1 and s 2); end ccc;

ПРОЦЕССЫ n n n В общем виде VHDL-процесс записывается так: LABEL: process (лист чувствительности) -- область деклараций begin --VHDL операторы end process;

ПРОЦЕССЫ n n n В общем виде VHDL-процесс записывается так: LABEL: process (лист чувствительности) -- область деклараций begin --VHDL операторы end process;

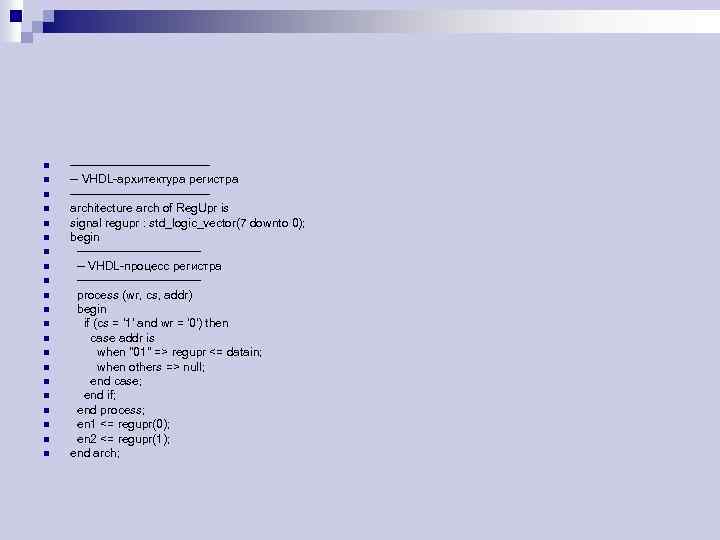

n n n n n n ------------------ -- VHDL-архитектура регистра ------------------ architecture arch of Reg. Upr is signal regupr : std_logic_vector(7 downto 0); begin ---------------- -- VHDL-процесс регистра ---------------- process (wr, cs, addr) begin if (cs = '1' and wr = '0') then case addr is when "01" => regupr <= datain; when others => null; end case; end if; end process; en 1 <= regupr(0); en 2 <= regupr(1); end arch;

n n n n n n ------------------ -- VHDL-архитектура регистра ------------------ architecture arch of Reg. Upr is signal regupr : std_logic_vector(7 downto 0); begin ---------------- -- VHDL-процесс регистра ---------------- process (wr, cs, addr) begin if (cs = '1' and wr = '0') then case addr is when "01" => regupr <= datain; when others => null; end case; end if; end process; en 1 <= regupr(0); en 2 <= regupr(1); end arch;

Атрибуты n n 1. 2. Атрибуты - это различные характеристики объектов VHDL. Они делятся на: Предопределенные и пользовательские.

Атрибуты n n 1. 2. Атрибуты - это различные характеристики объектов VHDL. Они делятся на: Предопределенные и пользовательские.

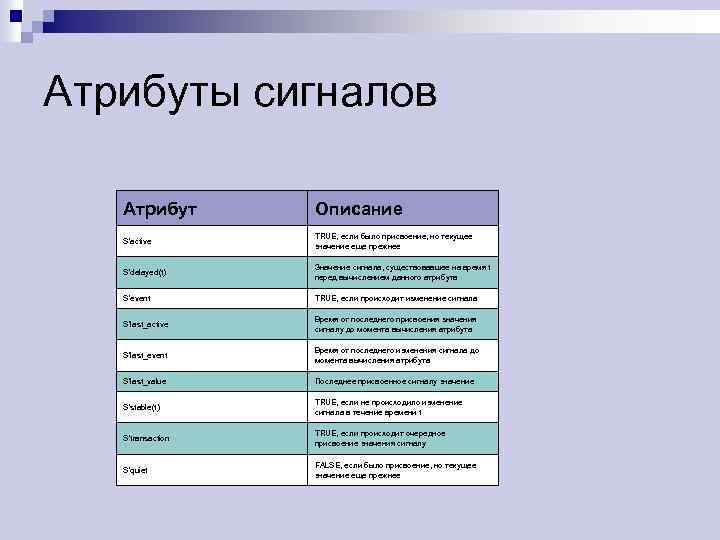

Атрибуты сигналов Атрибут Описание S'active TRUE, если было присвоение, но текущее значение еще прежнее S'delayed(t) Значение сигнала, существовавшее на время t перед вычислением данного атрибута S'event TRUE, если происходит изменение сигнала S'last_active Время от последнего присвоения значения сигналу до момента вычисления атрибута S'last_event Время от последнего изменения сигнала до момента вычисления атрибута S'last_value Последнее присвоенное сигналу значение S'stable(t) TRUE, если не происходило изменение сигнала в течение времени t S'transaction TRUE, если происходит очередное присвоение значения сигналу S'quiet FALSE, если было присвоение, но текущее значение еще прежнее

Атрибуты сигналов Атрибут Описание S'active TRUE, если было присвоение, но текущее значение еще прежнее S'delayed(t) Значение сигнала, существовавшее на время t перед вычислением данного атрибута S'event TRUE, если происходит изменение сигнала S'last_active Время от последнего присвоения значения сигналу до момента вычисления атрибута S'last_event Время от последнего изменения сигнала до момента вычисления атрибута S'last_value Последнее присвоенное сигналу значение S'stable(t) TRUE, если не происходило изменение сигнала в течение времени t S'transaction TRUE, если происходит очередное присвоение значения сигналу S'quiet FALSE, если было присвоение, но текущее значение еще прежнее

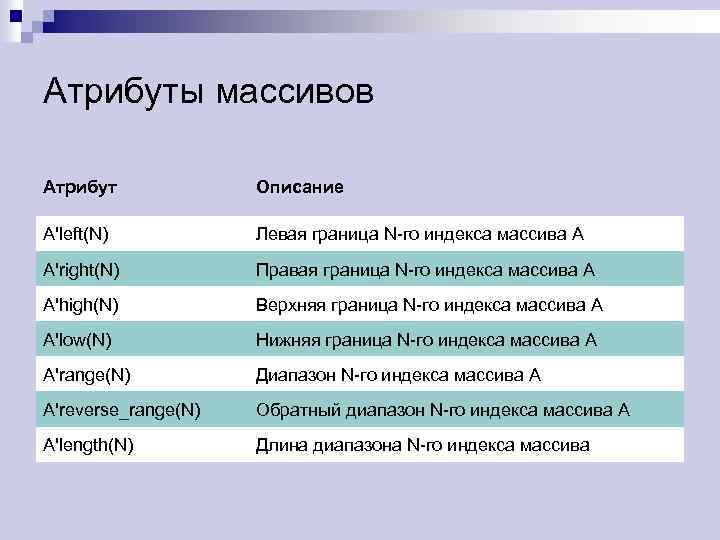

Атрибуты массивов Атрибут Описание A'left(N) Левая граница N-го индекса массива А A'right(N) Правая граница N-го индекса массива А A'high(N) Верхняя граница N-го индекса массива А A'low(N) Нижняя граница N-го индекса массива А A'range(N) Диапазон N-го индекса массива А A'reverse_range(N) Обратный диапазон N-го индекса массива А A'length(N) Длина диапазона N-го индекса массива

Атрибуты массивов Атрибут Описание A'left(N) Левая граница N-го индекса массива А A'right(N) Правая граница N-го индекса массива А A'high(N) Верхняя граница N-го индекса массива А A'low(N) Нижняя граница N-го индекса массива А A'range(N) Диапазон N-го индекса массива А A'reverse_range(N) Обратный диапазон N-го индекса массива А A'length(N) Длина диапазона N-го индекса массива

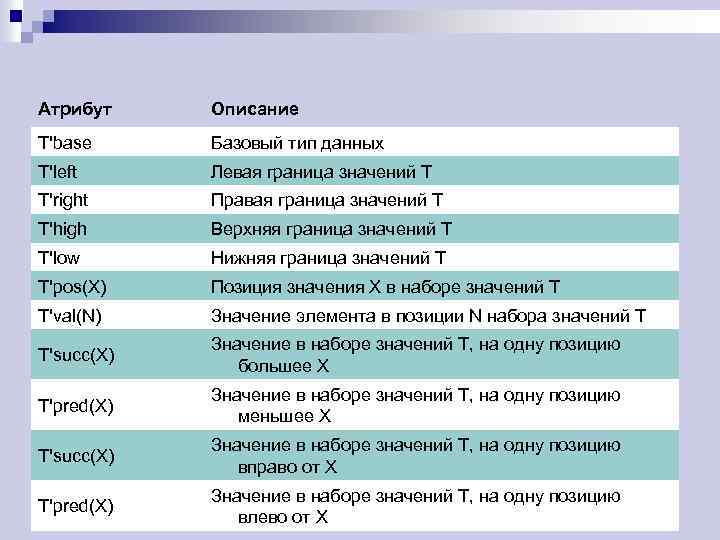

Атрибут Описание T'base Базовый тип данных T'left Левая граница значений T T'right Правая граница значений T T'high Верхняя граница значений T T'low Нижняя граница значений T T'pos(X) Позиция значения Х в наборе значений Т T'val(N) Значение элемента в позиции N набора значений Т T'succ(X) Значение в наборе значений T, на одну позицию большее X T'pred(X) Значение в наборе значений T, на одну позицию меньшее X T'succ(X) Значение в наборе значений T, на одну позицию вправо от X T'pred(X) Значение в наборе значений T, на одну позицию влево от X

Атрибут Описание T'base Базовый тип данных T'left Левая граница значений T T'right Правая граница значений T T'high Верхняя граница значений T T'low Нижняя граница значений T T'pos(X) Позиция значения Х в наборе значений Т T'val(N) Значение элемента в позиции N набора значений Т T'succ(X) Значение в наборе значений T, на одну позицию большее X T'pred(X) Значение в наборе значений T, на одну позицию меньшее X T'succ(X) Значение в наборе значений T, на одну позицию вправо от X T'pred(X) Значение в наборе значений T, на одну позицию влево от X

n n Так вот, чтобы поймать строб сигнала, нам как раз подходит атрибут S'event. Посмотрите в таблице 1. S'event дает TRUE, если происходит изменение сигнала, а это ни что иное как фронт сигнала (строб).

n n Так вот, чтобы поймать строб сигнала, нам как раз подходит атрибут S'event. Посмотрите в таблице 1. S'event дает TRUE, если происходит изменение сигнала, а это ни что иное как фронт сигнала (строб).

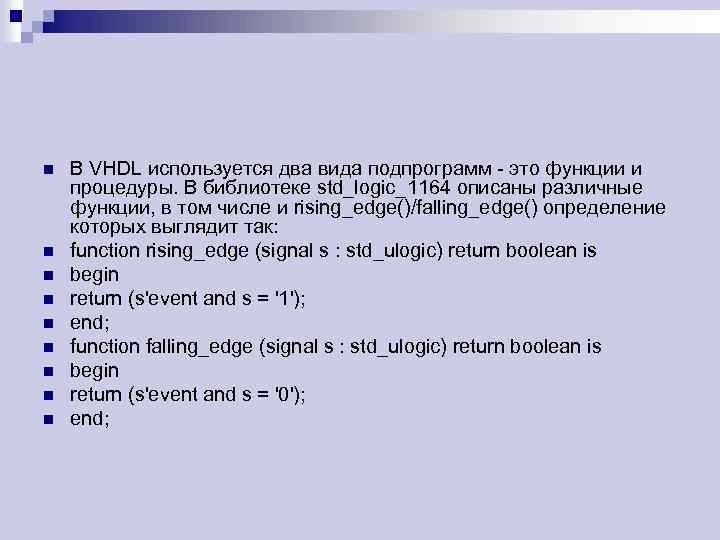

n n n n n В VHDL используется два вида подпрограмм - это функции и процедуры. В библиотеке std_logic_1164 описаны различные функции, в том числе и rising_edge()/falling_edge() определение которых выглядит так: function rising_edge (signal s : std_ulogic) return boolean is begin return (s'event and s = '1'); end; function falling_edge (signal s : std_ulogic) return boolean is begin return (s'event and s = '0'); end;

n n n n n В VHDL используется два вида подпрограмм - это функции и процедуры. В библиотеке std_logic_1164 описаны различные функции, в том числе и rising_edge()/falling_edge() определение которых выглядит так: function rising_edge (signal s : std_ulogic) return boolean is begin return (s'event and s = '1'); end; function falling_edge (signal s : std_ulogic) return boolean is begin return (s'event and s = '0'); end;

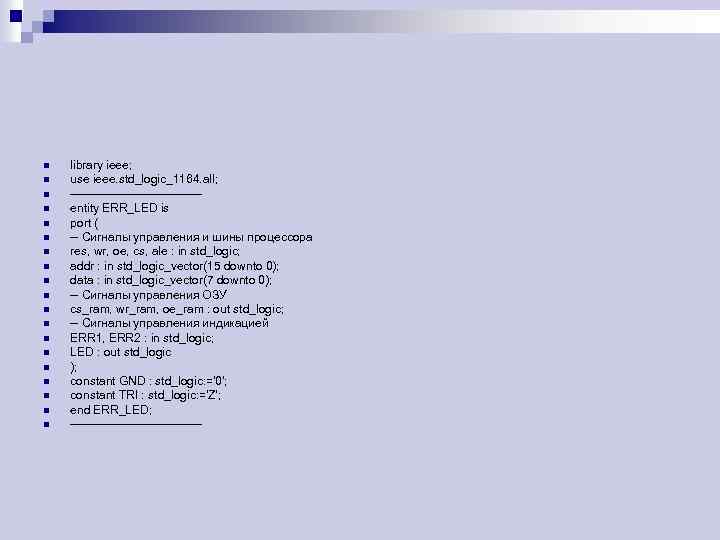

n n n n n library ieee; use ieee. std_logic_1164. all; ----------------- entity ERR_LED is port ( -- Сигналы управления и шины процессора res, wr, oe, cs, ale : in std_logic; addr : in std_logic_vector(15 downto 0); data : in std_logic_vector(7 downto 0); -- Сигналы управления ОЗУ cs_ram, wr_ram, oe_ram : out std_logic; -- Сигналы управления индикацией ERR 1, ERR 2 : in std_logic; LED : out std_logiс ); constant GND : std_logic: ='0'; constant TRI : std_logic: ='Z'; end ERR_LED; -----------------

n n n n n library ieee; use ieee. std_logic_1164. all; ----------------- entity ERR_LED is port ( -- Сигналы управления и шины процессора res, wr, oe, cs, ale : in std_logic; addr : in std_logic_vector(15 downto 0); data : in std_logic_vector(7 downto 0); -- Сигналы управления ОЗУ cs_ram, wr_ram, oe_ram : out std_logic; -- Сигналы управления индикацией ERR 1, ERR 2 : in std_logic; LED : out std_logiс ); constant GND : std_logic: ='0'; constant TRI : std_logic: ='Z'; end ERR_LED; -----------------

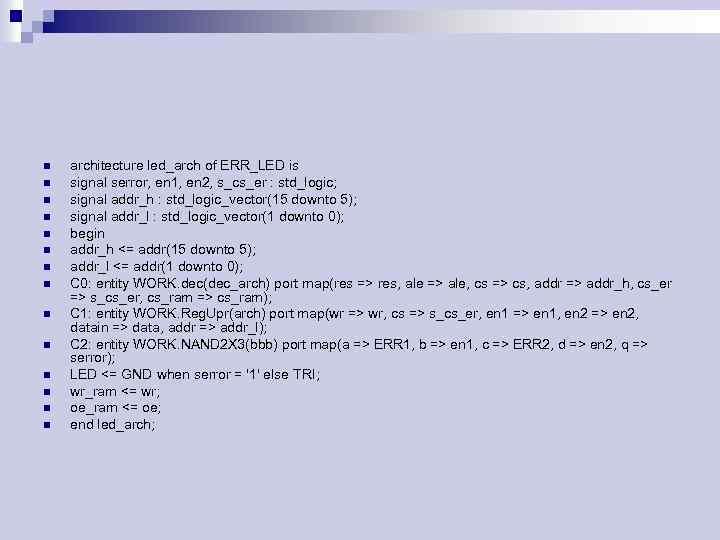

n n n n architecture led_arch of ERR_LED is signal serror, en 1, en 2, s_cs_er : std_logic; signal addr_h : std_logic_vector(15 downto 5); signal addr_l : std_logic_vector(1 downto 0); begin addr_h <= addr(15 downto 5); addr_l <= addr(1 downto 0); C 0: entity WORK. dec(dec_arch) port map(res => res, ale => ale, cs => cs, addr => addr_h, cs_er => s_cs_er, cs_ram => cs_ram); C 1: entity WORK. Reg. Upr(arch) port map(wr => wr, cs => s_cs_er, en 1 => en 1, en 2 => en 2, datain => data, addr => addr_l); C 2: entity WORK. NAND 2 X 3(bbb) port map(a => ERR 1, b => en 1, c => ERR 2, d => en 2, q => serror); LED <= GND when serror = '1' else TRI; wr_ram <= wr; oe_ram <= oe; end led_arch;

n n n n architecture led_arch of ERR_LED is signal serror, en 1, en 2, s_cs_er : std_logic; signal addr_h : std_logic_vector(15 downto 5); signal addr_l : std_logic_vector(1 downto 0); begin addr_h <= addr(15 downto 5); addr_l <= addr(1 downto 0); C 0: entity WORK. dec(dec_arch) port map(res => res, ale => ale, cs => cs, addr => addr_h, cs_er => s_cs_er, cs_ram => cs_ram); C 1: entity WORK. Reg. Upr(arch) port map(wr => wr, cs => s_cs_er, en 1 => en 1, en 2 => en 2, datain => data, addr => addr_l); C 2: entity WORK. NAND 2 X 3(bbb) port map(a => ERR 1, b => en 1, c => ERR 2, d => en 2, q => serror); LED <= GND when serror = '1' else TRI; wr_ram <= wr; oe_ram <= oe; end led_arch;