632b822c04804eed64ab91b7ff5a1577.ppt

- Количество слайдов: 30

Verification & Validation By: Amir Masoud Gharehbaghi Email: amgh@mehr. sharif. edu V&V Techniques

Outline Overview n Selective History n Theorem Proving n Model Checking n Hardware Verification n Assertion-Based Verification n Conclusions n V&V Techniques 2

What is Verification (Validation( n Functional Verification: ¨ Task of establishing that a given design accurately implements the intended behavior V&V Techniques 3

Verification&Validation Techniques n Simulation-based ¨ Apply inputs to design, simulate (or run), and check the results n Formal ¨ Mathematically proof the correctness of system against the properties n Semi-formal ¨ Combine V&V Techniques simulation and formal verification 4

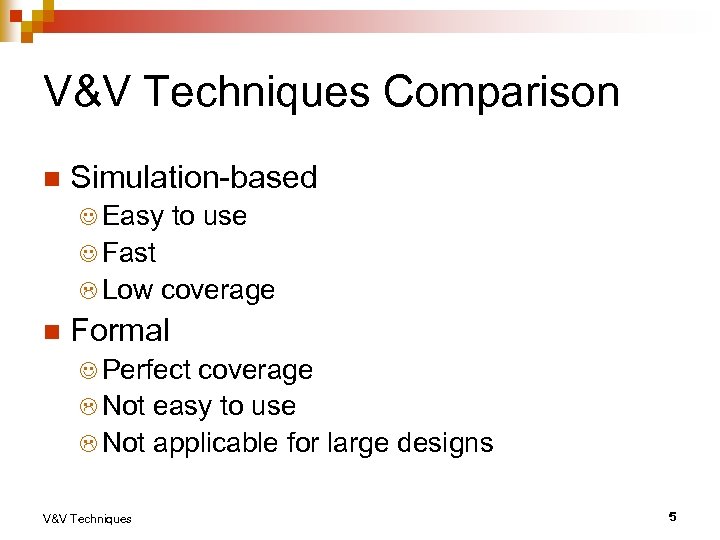

V&V Techniques Comparison n Simulation-based J Easy to use J Fast L Low n coverage Formal J Perfect coverage L Not easy to use L Not applicable for large designs V&V Techniques 5

Using Formal Methods n n Writing formal specifications Proving properties about the specification ¨ Theorem n proving Deriving implementation from a given specification ¨ Refinement n Verifying properties for a given implementation ¨ Property V&V Techniques checking 6

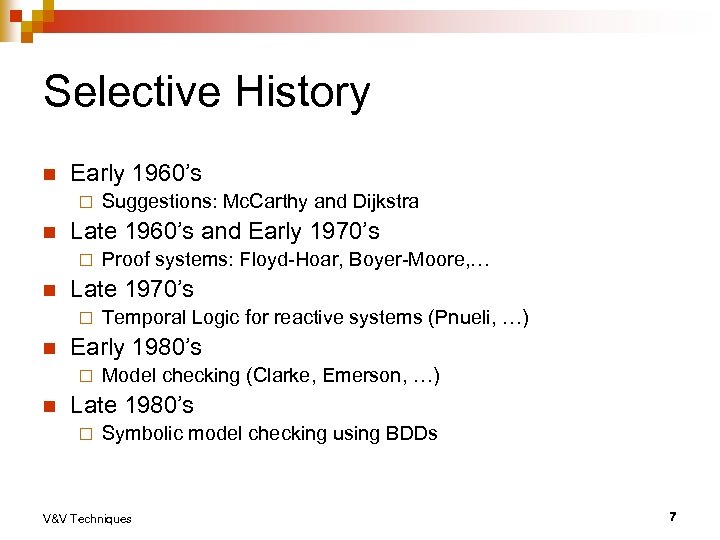

Selective History n Early 1960’s ¨ n Late 1960’s and Early 1970’s ¨ n Temporal Logic for reactive systems (Pnueli, …) Early 1980’s ¨ n Proof systems: Floyd-Hoar, Boyer-Moore, … Late 1970’s ¨ n Suggestions: Mc. Carthy and Dijkstra Model checking (Clarke, Emerson, …) Late 1980’s ¨ Symbolic model checking using BDDs V&V Techniques 7

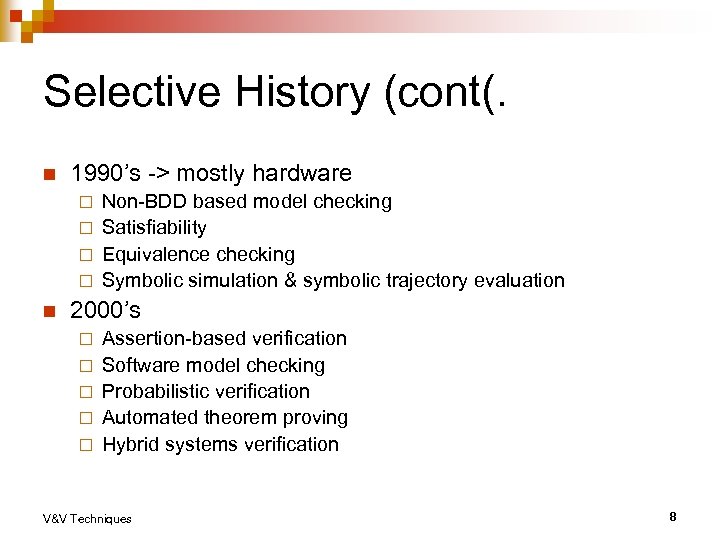

Selective History (cont(. n 1990’s -> mostly hardware Non-BDD based model checking ¨ Satisfiability ¨ Equivalence checking ¨ Symbolic simulation & symbolic trajectory evaluation ¨ n 2000’s ¨ ¨ ¨ Assertion-based verification Software model checking Probabilistic verification Automated theorem proving Hybrid systems verification V&V Techniques 8

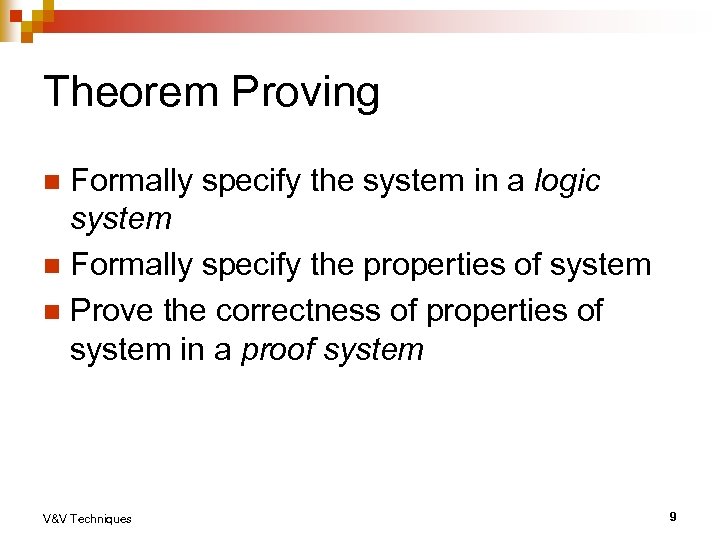

Theorem Proving Formally specify the system in a logic system n Formally specify the properties of system n Prove the correctness of properties of system in a proof system n V&V Techniques 9

Theorem Provers & Logic Systems n First-Order Logic ¨ ACL 2 ¨ Nqthm n High-Order Logic ¨ HOL ¨ PVS V&V Techniques 10

Temporal Logic n First-Order Logic + Temporal Operations Linear Temporal Logic (LTL( n Computational Tree Logic (CTL( n V&V Techniques 11

LTL Temporal Operations X: next n F: finally n G: globally n U: until n V&V Techniques 12

LTL Example p Xp n alert F halt n G (alert F halt ) n G (alert (alarm U halt ) ) n V&V Techniques 13

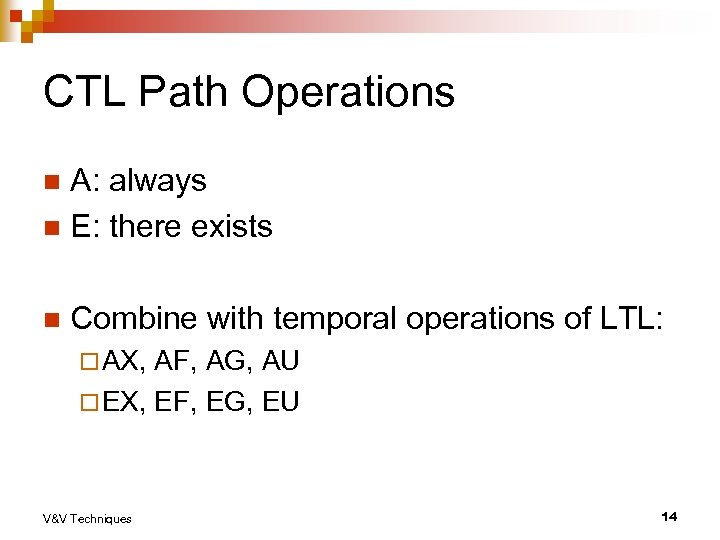

CTL Path Operations A: always n E: there exists n n Combine with temporal operations of LTL: ¨ AX, AF, AG, AU ¨ EX, EF, EG, EU V&V Techniques 14

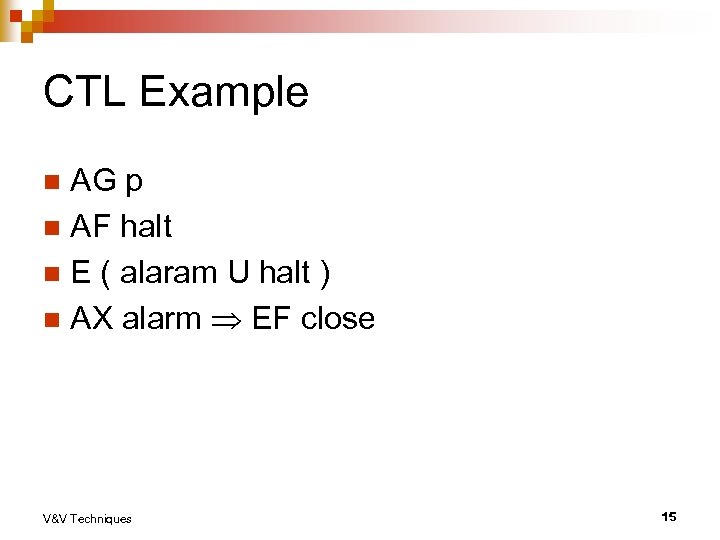

CTL Example AG p n AF halt n E ( alaram U halt ) n AX alarm EF close n V&V Techniques 15

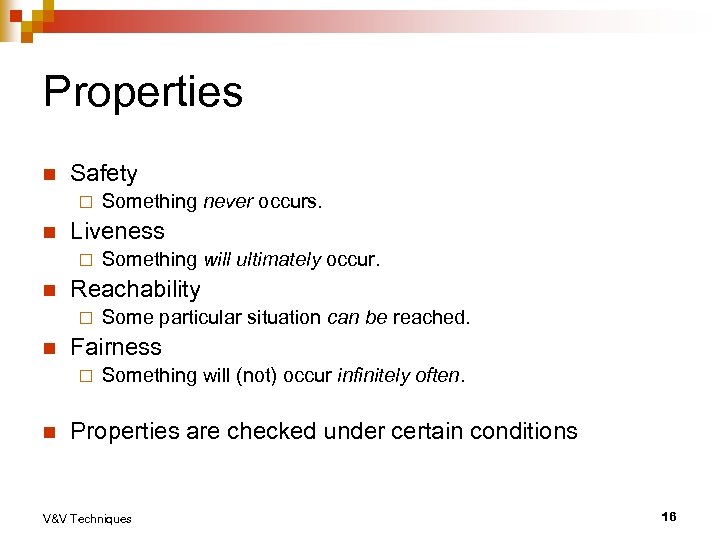

Properties n Safety ¨ n Liveness ¨ n Some particular situation can be reached. Fairness ¨ n Something will ultimately occur. Reachability ¨ n Something never occurs. Something will (not) occur infinitely often. Properties are checked under certain conditions V&V Techniques 16

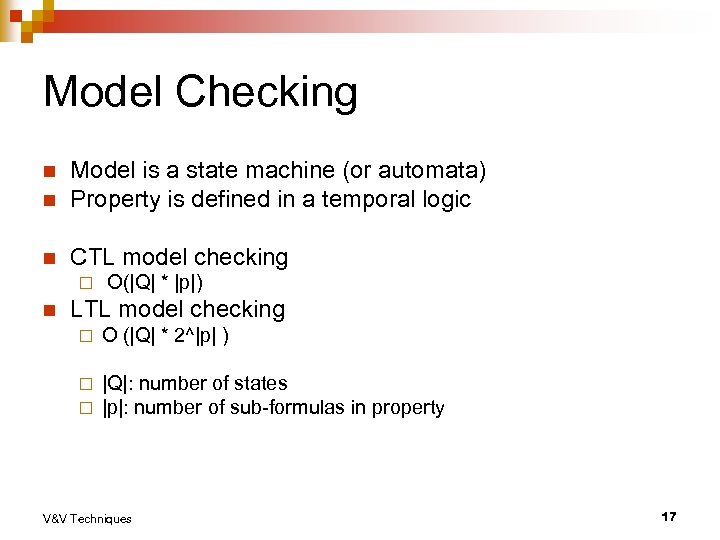

Model Checking n Model is a state machine (or automata) Property is defined in a temporal logic n CTL model checking n ¨ n O(|Q| * |p|) LTL model checking ¨ O (|Q| * 2^|p| ) ¨ ¨ |Q|: number of states |p|: number of sub-formulas in property V&V Techniques 17

State Explosion Problem n Both in LTL and CTL: ¨ An n automata is generated (explicitly) Number of states grow exponentially V&V Techniques 18

Symbolic Model Checking Symbolically (implicitly) represent states (and transition between states( n Use Binary Decision Diagram (BDD) to represent state variables n n Uses CTL properties V&V Techniques 19

Reduced Order BDD (ROBDD( A directed acyclic graph (DAG) with two leaf nodes (1, 0) n Represent Boolean functions n ¨ Compact ¨ Canonical ¨ Efficient operations (linear or quadratic) ¨ Simple to use V&V Techniques 20

Satisfiability (SAT) Checking n Satisfiability Checking: ¨ Check existence of a combination of values for a Boolean function that function is 1 n Check that ~f is unsatisfiable V&V Techniques 21

Bounded Model Checking Search for counter example by unfolding system in time until a bound is reached. n Use SAT checkers n n What about unbounded model checking? V&V Techniques 22

Symbolic Simulation n Simulate with symbolic (not explicit) values. ¨ Inputs: expressions ¨ Outputs: expressions n Originally based on BDD. V&V Techniques 23

Symbolic Trajectory Evaluation n Check properties of A=>C form. ¨ A: input variables’ values over time ¨ C: expected output variables’ values over time n n Symbolically simulate with given input values (A). Check that expected results (C) to be compatible (subset of) simulated output results. V&V Techniques 24

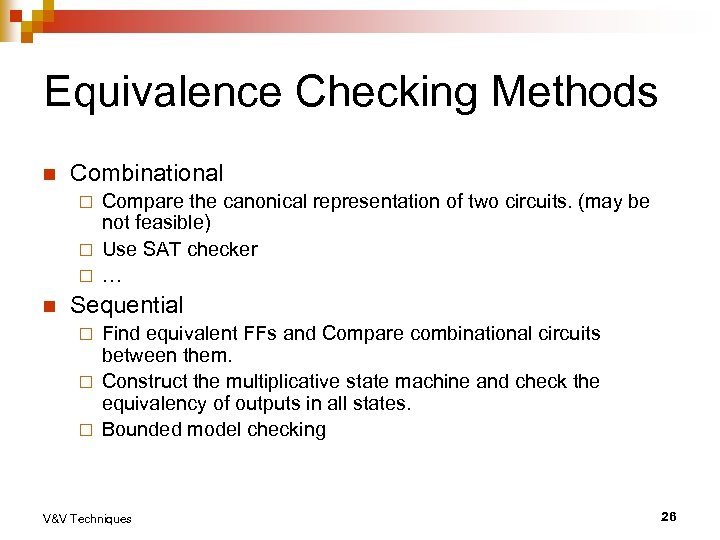

Equivalence Checking n Check equivalent behavior between two designs ¨ Same level of abstraction ¨ Different levels of abstraction Combinational n Sequential n V&V Techniques 25

Equivalence Checking Methods n Combinational Compare the canonical representation of two circuits. (may be not feasible) ¨ Use SAT checker ¨ … ¨ n Sequential Find equivalent FFs and Compare combinational circuits between them. ¨ Construct the multiplicative state machine and check the equivalency of outputs in all states. ¨ Bounded model checking ¨ V&V Techniques 26

Assertion-Based Verification n Assertion: property n Do property checking during simulation ¨ Embed in design ¨ Check in run-time V&V Techniques 27

Assertion Languages OVL: Open Verification library n PSL: Property Specification Language n ¨ Formerly “Sugar” System. Verilog n… n V&V Techniques 28

Coverage n Percentage of design covered during simulation ¨ Code n n Statement Path Condition … ¨ Signal ¨… V&V Techniques 29

Conclusions n Verification is a serious bottleneck for current designs ¨ Up n n n to 80 percent of design time Formal methods cannot be applied to real designs Simulation cannot guarantee correctness of designs Embedded system verification containing Hw/Sw requires new techniques V&V Techniques 30

632b822c04804eed64ab91b7ff5a1577.ppt