15_основная_память.ppt

- Количество слайдов: 19

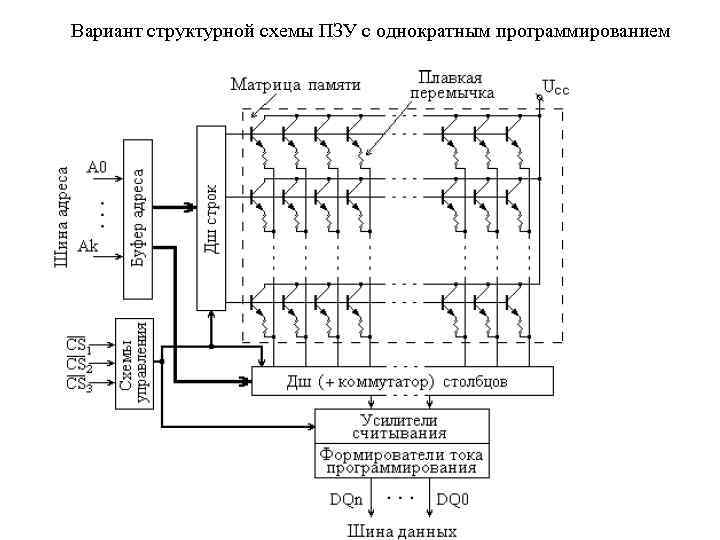

Вариант структурной схемы ПЗУ с однократным программированием

Вариант структурной схемы ПЗУ с однократным программированием

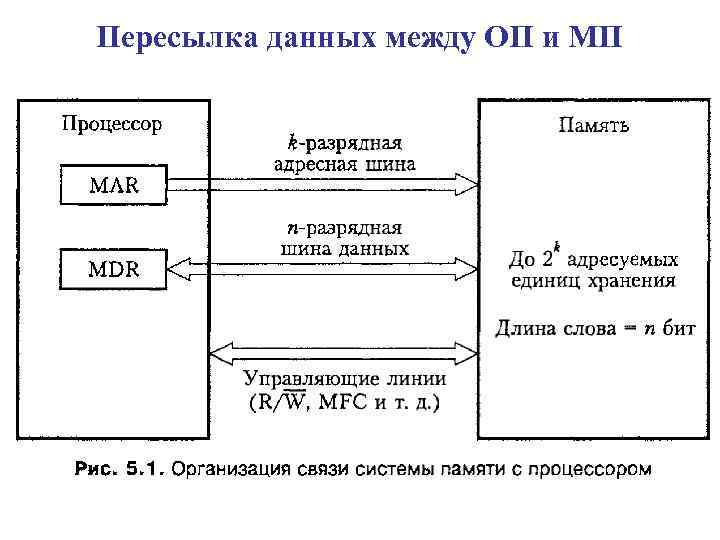

Пересылка данных между ОП и МП

Пересылка данных между ОП и МП

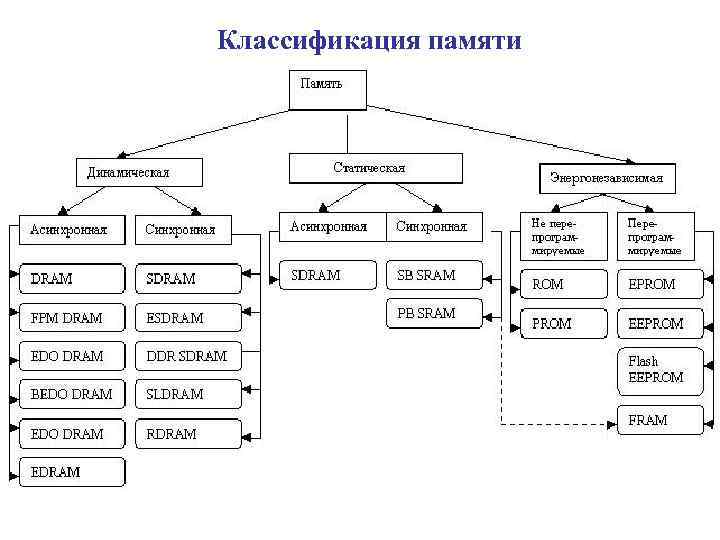

Классификация памяти

Классификация памяти

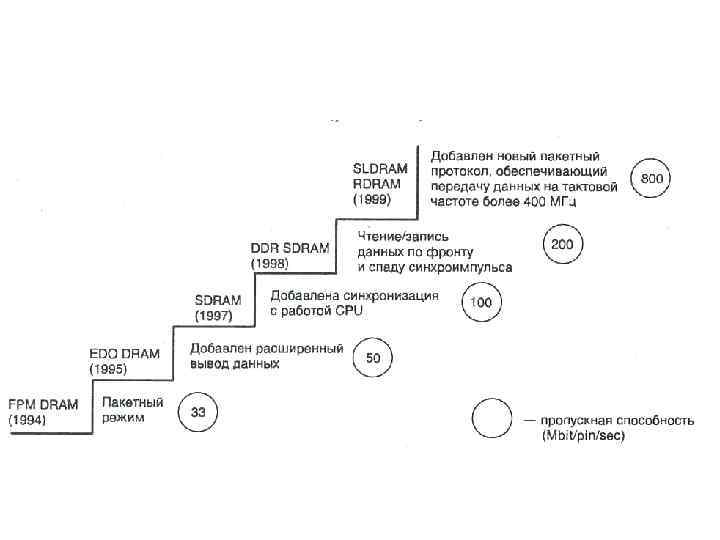

Микросхемы FPM DRAM Для i 80286 и i 80386 была разработана специальная быстрая память - FPM (fast page mode). Схема чтения для FPM DRAM описывается формулой 5 -3 -3 -3 (всего 14 тактов). Время доступа 60 нс, что, с учетом возможности работать на более высоких частотах шины, привело к увеличению производительности памяти по сравнению с традиционной DRAM приблизительно на 70%. Данный тип ИМС применялся в ПК примерно до 1994 года и использовался на компьютерах с i 80486 и в первых Pentium до 1995 года.

Микросхемы FPM DRAM Для i 80286 и i 80386 была разработана специальная быстрая память - FPM (fast page mode). Схема чтения для FPM DRAM описывается формулой 5 -3 -3 -3 (всего 14 тактов). Время доступа 60 нс, что, с учетом возможности работать на более высоких частотах шины, привело к увеличению производительности памяти по сравнению с традиционной DRAM приблизительно на 70%. Данный тип ИМС применялся в ПК примерно до 1994 года и использовался на компьютерах с i 80486 и в первых Pentium до 1995 года.

Микросхемы EDO DRAM В 1994 году появилась новая архитектура памяти - ИМС с гиперстраничным режимом доступа (НРМ, Hyper Page Mode), более известные как EDO (Extended Data Output — расширенное время удержания данных на выходе). Другое название - память с усовершенствованным выходом. Схема чтения 5 -2 -2 -2, что на 20% быстрее, чем у FPM. Время доступа порядка 30 -40 нс.

Микросхемы EDO DRAM В 1994 году появилась новая архитектура памяти - ИМС с гиперстраничным режимом доступа (НРМ, Hyper Page Mode), более известные как EDO (Extended Data Output — расширенное время удержания данных на выходе). Другое название - память с усовершенствованным выходом. Схема чтения 5 -2 -2 -2, что на 20% быстрее, чем у FPM. Время доступа порядка 30 -40 нс.

Главная особенность — увеличенное время доступности данных на выходе микросхемы. Временные параметры улучшаются за счет исключения циклов ожидания момента стабилизации данных на выходе микросхемы. EDO частично совмещала такты чтения, за счет чего появилась возможность считывания следующей порции данных, не дожидаясь окончательной передачи предыдущих.

Главная особенность — увеличенное время доступности данных на выходе микросхемы. Временные параметры улучшаются за счет исключения циклов ожидания момента стабилизации данных на выходе микросхемы. EDO частично совмещала такты чтения, за счет чего появилась возможность считывания следующей порции данных, не дожидаясь окончательной передачи предыдущих.

Микросхемы BEDO DRAM Новая модификация EDO известна как BEDO (Burst EDO - пакетная EDO, то есть пакетная пересылка данных). Производитель - VIA Technologies Новизна метода - при первом обращении считывается вся строка микросхемы, в которую входят последовательные слова пакета. За последовательной пересылкой слов (переключением столбцов) автоматически следит внутренний счетчик микросхемы. Это исключает необходимость выдавать адреса для всех ячеек пакета, но требует поддержки со стороны внешней логики. Способ позволяет сократить время считывания второго и последующих слов еще на один такт, благодаря чему формула приобретает вид 5 -1 -1 -1.

Микросхемы BEDO DRAM Новая модификация EDO известна как BEDO (Burst EDO - пакетная EDO, то есть пакетная пересылка данных). Производитель - VIA Technologies Новизна метода - при первом обращении считывается вся строка микросхемы, в которую входят последовательные слова пакета. За последовательной пересылкой слов (переключением столбцов) автоматически следит внутренний счетчик микросхемы. Это исключает необходимость выдавать адреса для всех ячеек пакета, но требует поддержки со стороны внешней логики. Способ позволяет сократить время считывания второго и последующих слов еще на один такт, благодаря чему формула приобретает вид 5 -1 -1 -1.

Микросхемы EDRAM Более быстрая версия DRAM была разработана подразделением фирмы Ramtron - компанией Enhanced Memory Systems. Технология реализована в вариантах FPM, EDO и BEDO. У микросхемы более быстрое ядро и внутренняя кэш-память – это главная особенность технологии. В роли кэш-памяти выступает статическая память (SRAM) емкостью 2048 бит.

Микросхемы EDRAM Более быстрая версия DRAM была разработана подразделением фирмы Ramtron - компанией Enhanced Memory Systems. Технология реализована в вариантах FPM, EDO и BEDO. У микросхемы более быстрое ядро и внутренняя кэш-память – это главная особенность технологии. В роли кэш-памяти выступает статическая память (SRAM) емкостью 2048 бит.

Ядро EDRAM имеет 2048 столбцов, каждый из которых соединен с внутренней кэш-памятью. При обращении к какой-либо ячейке одновременно считывается целая строка (2048 бит). Считанная строка заносится в SRAM, причем перенос информации в кэшпамять практически не сказывается на быстродействии, поскольку происходит за один такт. При дальнейших обращениях к ячейкам, относящимся к той же строке, данные берутся из более быстрой кэш-памяти. Следующее обращение к ядру происходит при доступе к ячейке, не расположенной в строке, хранимой в кэш-памяти микросхемы.

Ядро EDRAM имеет 2048 столбцов, каждый из которых соединен с внутренней кэш-памятью. При обращении к какой-либо ячейке одновременно считывается целая строка (2048 бит). Считанная строка заносится в SRAM, причем перенос информации в кэшпамять практически не сказывается на быстродействии, поскольку происходит за один такт. При дальнейших обращениях к ячейкам, относящимся к той же строке, данные берутся из более быстрой кэш-памяти. Следующее обращение к ядру происходит при доступе к ячейке, не расположенной в строке, хранимой в кэш-памяти микросхемы.

Микросхемы SLDRAM С 1995 года потенциальным конкурентом RDRAM на роль стандарта архитектуры памяти для будущих ПК выступает новый вид динамического ОЗУ, разработанный консорциумом производителей ВМ Sync. Link Consortium и известный под аббревиатурой SLDRAM. В отличие от RDRAM, технология которой является собственностью компаний Rambus и Intel, данный стандарт — открытый. На системном уровне технологии очень похожи. Данные и команды от контроллера к памяти и обратно в SLDRAM передаются пакетами по 4 или 8 посылок.

Микросхемы SLDRAM С 1995 года потенциальным конкурентом RDRAM на роль стандарта архитектуры памяти для будущих ПК выступает новый вид динамического ОЗУ, разработанный консорциумом производителей ВМ Sync. Link Consortium и известный под аббревиатурой SLDRAM. В отличие от RDRAM, технология которой является собственностью компаний Rambus и Intel, данный стандарт — открытый. На системном уровне технологии очень похожи. Данные и команды от контроллера к памяти и обратно в SLDRAM передаются пакетами по 4 или 8 посылок.

К одному контроллеру можно подключить до 8 микросхем памяти. Чтобы избежать запаздывания сигналов от микросхем, более удаленных от контроллера, временные характеристики для каждой микросхемы определяются и заносятся в ее управляющий регистр при включении питания. Идея SLDRAM чуть ли не целиком "портирована" в архитектуру нового поколения DDR 2.

К одному контроллеру можно подключить до 8 микросхем памяти. Чтобы избежать запаздывания сигналов от микросхем, более удаленных от контроллера, временные характеристики для каждой микросхемы определяются и заносятся в ее управляющий регистр при включении питания. Идея SLDRAM чуть ли не целиком "портирована" в архитектуру нового поколения DDR 2.

Микросхемы ESDRAM Это синхронная версия EDRAM, в которой используются те же приемы сокращения времени доступа. Операция записи в отличие от чтения происходит в обход кэш-памяти, что увеличивает производительность ESDRAM при возобновлении чтения из строки, уже находящейся в кэш-памяти. В микросхеме есть два банка, опэтому простои из-за подготовки к операциям чтения/записи сводятся к минимуму. Недостатки у рассматриваемой микросхемы те же, что и у EDRAM — усложнение контроллера, так как он должен учитывать возможность подготовки к чтению в кэш-память новой строки ядра. Кроме того, при произвольной последовательности адресов кэшпамять задействуется неэффективно.

Микросхемы ESDRAM Это синхронная версия EDRAM, в которой используются те же приемы сокращения времени доступа. Операция записи в отличие от чтения происходит в обход кэш-памяти, что увеличивает производительность ESDRAM при возобновлении чтения из строки, уже находящейся в кэш-памяти. В микросхеме есть два банка, опэтому простои из-за подготовки к операциям чтения/записи сводятся к минимуму. Недостатки у рассматриваемой микросхемы те же, что и у EDRAM — усложнение контроллера, так как он должен учитывать возможность подготовки к чтению в кэш-память новой строки ядра. Кроме того, при произвольной последовательности адресов кэшпамять задействуется неэффективно.

Микросхемы CDRAM (Cache DRAM) Разработан в корпорации Mitsubishi, и его можно рассматривать как пересмотренный вариант ESDRAM, свободный от некоторых ее несовершенств. Изменены емкость кэш-памяти и принцип размещения в ней данных. Емкость одного блока, помещаемого в кэш-память, уменьшена до 128 бит, таким образом, в 16 килобитовом кэше можно одновременно хранить копии из 128 участков памяти, что позволяет эффективнее использовать кэшпамять.

Микросхемы CDRAM (Cache DRAM) Разработан в корпорации Mitsubishi, и его можно рассматривать как пересмотренный вариант ESDRAM, свободный от некоторых ее несовершенств. Изменены емкость кэш-памяти и принцип размещения в ней данных. Емкость одного блока, помещаемого в кэш-память, уменьшена до 128 бит, таким образом, в 16 килобитовом кэше можно одновременно хранить копии из 128 участков памяти, что позволяет эффективнее использовать кэшпамять.

Изменены средства доступа: • используются раздельные адресные шины для статического кэша и динамического ядра; • перенос данных из динамического ядра в кэшпамять совмещен с выдачей данных на шину, поэтому частые, но короткие пересылки не снижают производительности ИМС при считывании из памяти больших объемов информации и уравнивают CDRAM с ESDRAM, а при чтении по выборочным адресам CDRAM явно выигрывает. Однако, вышеперечисленные изменения привели к еще большему усложнению контроллера памяти.

Изменены средства доступа: • используются раздельные адресные шины для статического кэша и динамического ядра; • перенос данных из динамического ядра в кэшпамять совмещен с выдачей данных на шину, поэтому частые, но короткие пересылки не снижают производительности ИМС при считывании из памяти больших объемов информации и уравнивают CDRAM с ESDRAM, а при чтении по выборочным адресам CDRAM явно выигрывает. Однако, вышеперечисленные изменения привели к еще большему усложнению контроллера памяти.

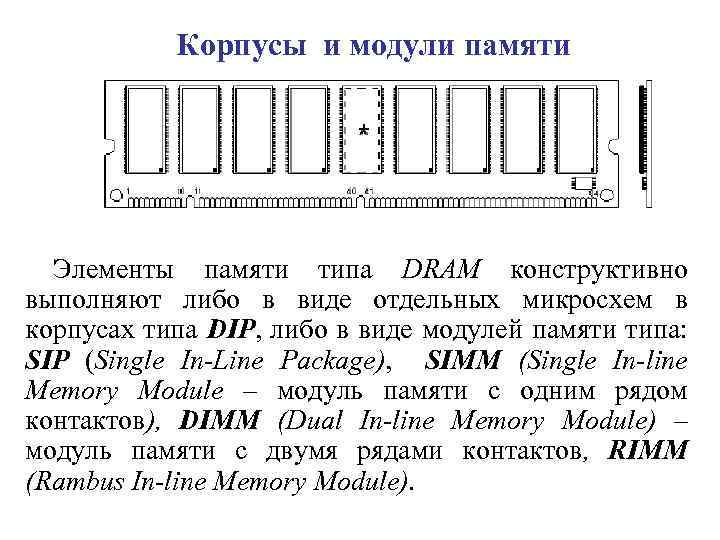

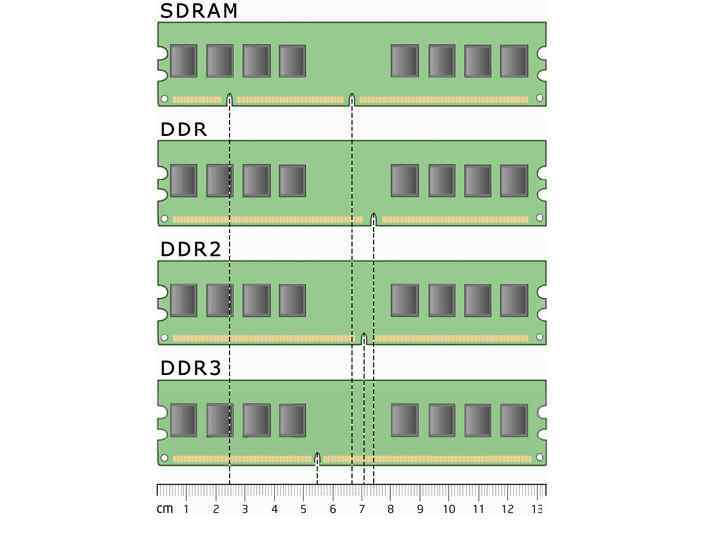

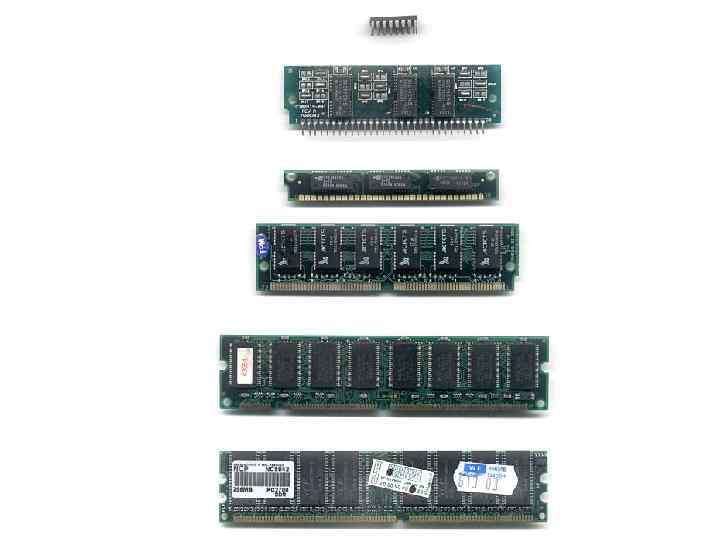

Корпусы и модули памяти Элементы памяти типа DRAM конструктивно выполняют либо в виде отдельных микросхем в корпусах типа DIP, либо в виде модулей памяти типа: SIP (Single In-Line Package), SIMM (Single In-line Memory Module – модуль памяти с одним рядом контактов), DIMM (Dual In-line Memory Module) – модуль памяти с двумя рядами контактов, RIMM (Rambus In-line Memory Module).

Корпусы и модули памяти Элементы памяти типа DRAM конструктивно выполняют либо в виде отдельных микросхем в корпусах типа DIP, либо в виде модулей памяти типа: SIP (Single In-Line Package), SIMM (Single In-line Memory Module – модуль памяти с одним рядом контактов), DIMM (Dual In-line Memory Module) – модуль памяти с двумя рядами контактов, RIMM (Rambus In-line Memory Module).

Модули RIMM Rambus In-line Memory Module менее распространены, в таких модулях выпускается память типа Direct RDRAM. Они представлены 184 -контактными прямоугольными платами, должны устанавливаться только в парах, а пустые разъёмы на материнской плате занимаются специальными заглушками. Это связано с особенностями конструкции таких модулей.

Модули RIMM Rambus In-line Memory Module менее распространены, в таких модулях выпускается память типа Direct RDRAM. Они представлены 184 -контактными прямоугольными платами, должны устанавливаться только в парах, а пустые разъёмы на материнской плате занимаются специальными заглушками. Это связано с особенностями конструкции таких модулей.