Лекция 5 Устройство ПЭВМ.pptx

- Количество слайдов: 35

УСТРОЙСТВО ПЭВМ ©А. В. Литвин

УСТРОЙСТВО ПЭВМ ©А. В. Литвин

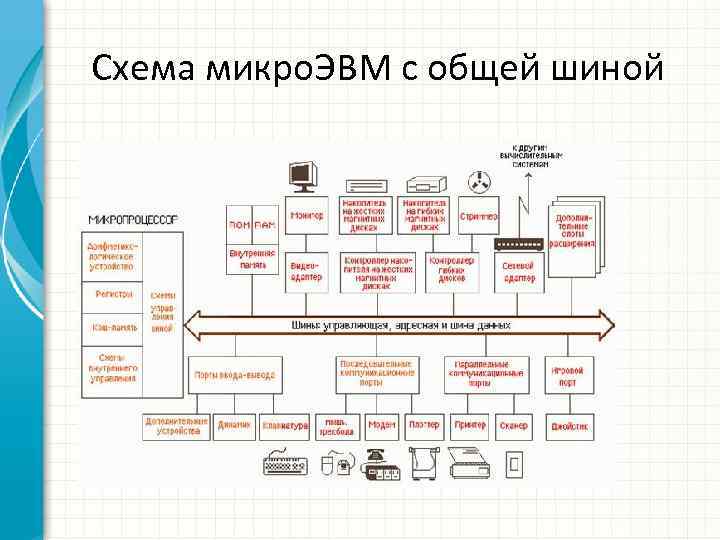

Схема микро. ЭВМ с общей шиной

Схема микро. ЭВМ с общей шиной

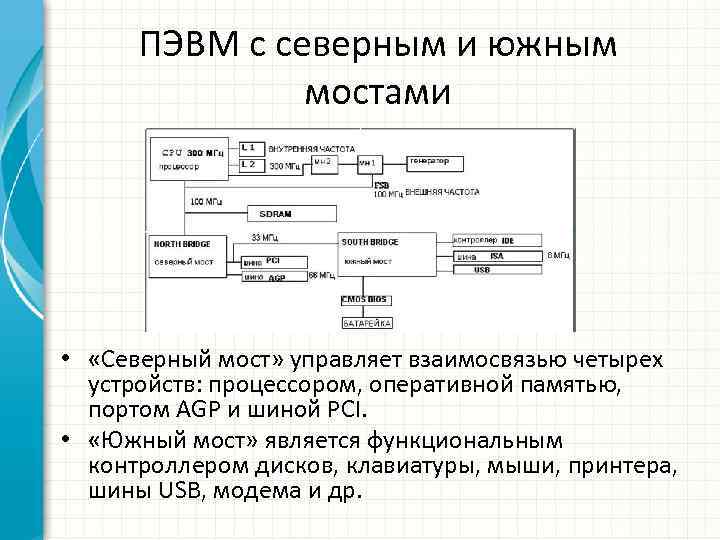

ПЭВМ с северным и южным мостами • «Северный мост» управляет взаимосвязью четырех устройств: процессором, оперативной памятью, портом AGP и шиной PCI. • «Южный мост» является функциональным контроллером дисков, клавиатуры, мыши, принтера, шины USB, модема и др.

ПЭВМ с северным и южным мостами • «Северный мост» управляет взаимосвязью четырех устройств: процессором, оперативной памятью, портом AGP и шиной PCI. • «Южный мост» является функциональным контроллером дисков, клавиатуры, мыши, принтера, шины USB, модема и др.

Шины ПЭВМ • FSB – локальная шина, обеспечивающая связь между процессором и северным мостом чипсета • PCI – локальная высокоскоростная шина, связывает процессор с оперативной памятью. • При частоте 66 МГц пропускная способность составляет 528 Мбайт / с. • Поддерживает режим авто конфигурации (plug-and -play). • ISA –Пропускная способность шины 5, 5 Мбайт / с, применяется для медленных устройств типа модема или звуковых карт.

Шины ПЭВМ • FSB – локальная шина, обеспечивающая связь между процессором и северным мостом чипсета • PCI – локальная высокоскоростная шина, связывает процессор с оперативной памятью. • При частоте 66 МГц пропускная способность составляет 528 Мбайт / с. • Поддерживает режим авто конфигурации (plug-and -play). • ISA –Пропускная способность шины 5, 5 Мбайт / с, применяется для медленных устройств типа модема или звуковых карт.

Шины ПЭВМ • USB – универсальная последовательная магистраль. Стандарт определяет взаимодействие с периферийным оборудованием, имеющим последовательный интерфейс. Предусматривает подключение до 256 устройств. • К шине можно подключать клавиатуру, мышь, джойстик и т. д.

Шины ПЭВМ • USB – универсальная последовательная магистраль. Стандарт определяет взаимодействие с периферийным оборудованием, имеющим последовательный интерфейс. Предусматривает подключение до 256 устройств. • К шине можно подключать клавиатуру, мышь, джойстик и т. д.

Шины ПЭВМ • AGP – видеоадаптер. Частота работы шины 33 МГц или 66 МГц, пропускная способность 1066 Мбайт / с. • SCSI (Small Computer System Interface) – интерфейс винчестеров • BIOS (ан гл. basic input/output system — «базовая система ввода-вывода» ) реализованна в виде микропрограмм, часть системного программного обеспечения, которая предназначается для предоставления операционной системе APIдоступа к аппаратуре компьютера и подключенным к нему устройствам.

Шины ПЭВМ • AGP – видеоадаптер. Частота работы шины 33 МГц или 66 МГц, пропускная способность 1066 Мбайт / с. • SCSI (Small Computer System Interface) – интерфейс винчестеров • BIOS (ан гл. basic input/output system — «базовая система ввода-вывода» ) реализованна в виде микропрограмм, часть системного программного обеспечения, которая предназначается для предоставления операционной системе APIдоступа к аппаратуре компьютера и подключенным к нему устройствам.

Процессоры x 86 • • Наиболее распространено семейство процессоров x 86: Intel 80286, 386, 486, Pentium. Они все совместимы по принципу «сверхувниз» . Внутри процессоров располагаются регистры: данных, команд, адреса. Шины: команд, данных, адреса. Разрядностью процессора является разрядность шины команд. Современный МП: Intel Core i 7 — семейство процессоров x 86 -64 Intel. Это первое семейство, использующее микроархитектуру Intel Nehalem, является преемником семейства Intel Core 2.

Процессоры x 86 • • Наиболее распространено семейство процессоров x 86: Intel 80286, 386, 486, Pentium. Они все совместимы по принципу «сверхувниз» . Внутри процессоров располагаются регистры: данных, команд, адреса. Шины: команд, данных, адреса. Разрядностью процессора является разрядность шины команд. Современный МП: Intel Core i 7 — семейство процессоров x 86 -64 Intel. Это первое семейство, использующее микроархитектуру Intel Nehalem, является преемником семейства Intel Core 2.

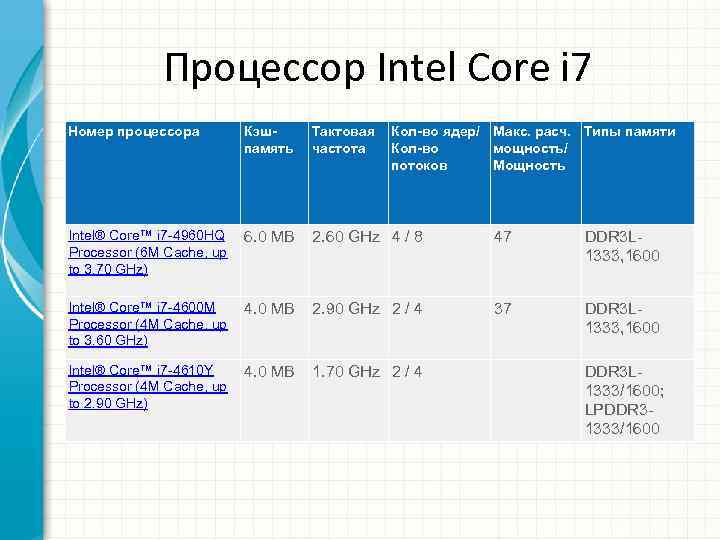

Процессор Intel Core i 7 Номер процессора Кэшпамять Тактовая частота Кол-во ядер/ Макс. расч. Типы памяти Кол-во мощность/ потоков Мощность Intel® Core™ i 7 -4960 HQ Processor (6 M Cache, up to 3. 70 GHz) 6. 0 MB 2. 60 GHz 4 / 8 47 DDR 3 L 1333, 1600 Intel® Core™ i 7 -4600 M Processor (4 M Cache, up to 3. 60 GHz) 4. 0 MB 2. 90 GHz 2 / 4 37 DDR 3 L 1333, 1600 Intel® Core™ i 7 -4610 Y Processor (4 M Cache, up to 2. 90 GHz) 4. 0 MB 1. 70 GHz 2 / 4 DDR 3 L 1333/1600; LPDDR 31333/1600

Процессор Intel Core i 7 Номер процессора Кэшпамять Тактовая частота Кол-во ядер/ Макс. расч. Типы памяти Кол-во мощность/ потоков Мощность Intel® Core™ i 7 -4960 HQ Processor (6 M Cache, up to 3. 70 GHz) 6. 0 MB 2. 60 GHz 4 / 8 47 DDR 3 L 1333, 1600 Intel® Core™ i 7 -4600 M Processor (4 M Cache, up to 3. 60 GHz) 4. 0 MB 2. 90 GHz 2 / 4 37 DDR 3 L 1333, 1600 Intel® Core™ i 7 -4610 Y Processor (4 M Cache, up to 2. 90 GHz) 4. 0 MB 1. 70 GHz 2 / 4 DDR 3 L 1333/1600; LPDDR 31333/1600

ОЗУ DDR 3 • Компания Transcend Information выпуспила 16 -Гбайт модулей DDR 3 -1600 RDIMM и 8 -Гбайт DDR 3 L-1333 RDIMM, совместимы с МП Intel Xeon и Core i 7. • 8 -Гбайт модули работают при напряжении 1, 35 В. • Частота модулей составляет 1333 МГц.

ОЗУ DDR 3 • Компания Transcend Information выпуспила 16 -Гбайт модулей DDR 3 -1600 RDIMM и 8 -Гбайт DDR 3 L-1333 RDIMM, совместимы с МП Intel Xeon и Core i 7. • 8 -Гбайт модули работают при напряжении 1, 35 В. • Частота модулей составляет 1333 МГц.

Структурная схема МП x 86 • • структурная схема МП x 86 содержит две относительно независимые части: операционное устройство (ОУ) и шинный интерфейс (ШИ). ОУ – выполняет заданные командой операции. ШИ- осуществляет выборку команд из памяти, а также обращение к памяти и внешним устройствам для считывания операндов и записи результатов. Оба устройства могут работать параллельно, что обеспечивает совмещение во времени процессов выборки и исполнения команд.

Структурная схема МП x 86 • • структурная схема МП x 86 содержит две относительно независимые части: операционное устройство (ОУ) и шинный интерфейс (ШИ). ОУ – выполняет заданные командой операции. ШИ- осуществляет выборку команд из памяти, а также обращение к памяти и внешним устройствам для считывания операндов и записи результатов. Оба устройства могут работать параллельно, что обеспечивает совмещение во времени процессов выборки и исполнения команд.

Архитектура X 86 • Операционное устройство МП содержит группу общих регистров, арифметикологическое устройство (АЛУ), регистр флагов F и блок управления.

Архитектура X 86 • Операционное устройство МП содержит группу общих регистров, арифметикологическое устройство (АЛУ), регистр флагов F и блок управления.

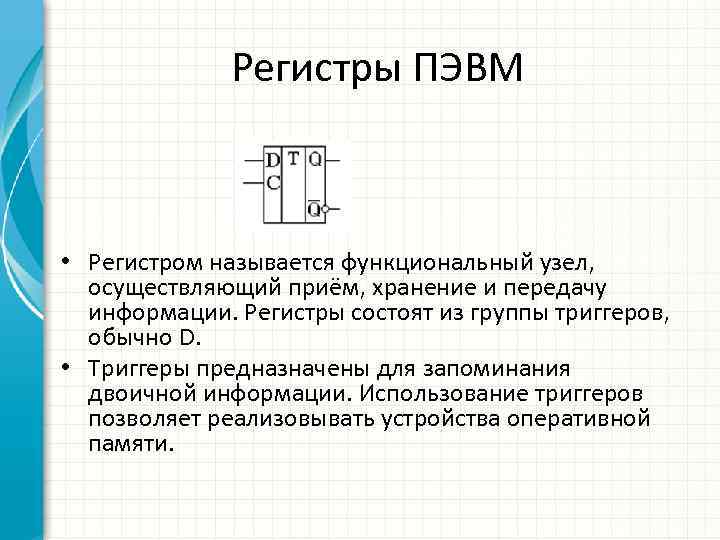

Регистры ПЭВМ • Регистром называется функциональный узел, осуществляющий приём, хранение и передачу информации. Регистры состоят из группы триггеров, обычно D. • Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти.

Регистры ПЭВМ • Регистром называется функциональный узел, осуществляющий приём, хранение и передачу информации. Регистры состоят из группы триггеров, обычно D. • Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти.

Регистры ПЭВМ • По типу приёма и выдачи информации различают 2 типа регистров: • С последовательным приёмом и выдачей информации — сдвиговые регистры. • С параллельным приёмом и выдачей информации — параллельные регистры. • Сдвиговые регистры представляют собой последовательно соединённую цепочку триггеров. Основной режим работы — сдвиг разрядов кода от одного триггера к другому на каждый импульс тактового сигнала.

Регистры ПЭВМ • По типу приёма и выдачи информации различают 2 типа регистров: • С последовательным приёмом и выдачей информации — сдвиговые регистры. • С параллельным приёмом и выдачей информации — параллельные регистры. • Сдвиговые регистры представляют собой последовательно соединённую цепочку триггеров. Основной режим работы — сдвиг разрядов кода от одного триггера к другому на каждый импульс тактового сигнала.

Назначения регистров x 86 • По назначению регистры различаются на: • аккумулятор — используется для хранения промежуточных результатов арифметических и логических операций и инструкций ввода-вывода; • флаговые — хранят признаки результатов арифметических и логических операций; • общего назначения — хранят операнды арифметических и логических выражений, индексы и адреса; • индексные — хранят индексы исходных и целевых элементов массива; • указательные — хранят указатели на специальные области памяти (указатель текущей операции, указатель базы, указатель стека); • сегментные — хранят адреса и селекторы сегментов памяти; • управляющие — хранят информацию, управляющую состоянием процессора, а также адреса системных таблиц.

Назначения регистров x 86 • По назначению регистры различаются на: • аккумулятор — используется для хранения промежуточных результатов арифметических и логических операций и инструкций ввода-вывода; • флаговые — хранят признаки результатов арифметических и логических операций; • общего назначения — хранят операнды арифметических и логических выражений, индексы и адреса; • индексные — хранят индексы исходных и целевых элементов массива; • указательные — хранят указатели на специальные области памяти (указатель текущей операции, указатель базы, указатель стека); • сегментные — хранят адреса и селекторы сегментов памяти; • управляющие — хранят информацию, управляющую состоянием процессора, а также адреса системных таблиц.

Типы регистров x 86 • • Существуют следующие типы регистров: Регистры общего назначения (РОН): EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP Регистр-указатель команд - EIP Регистр флагов - EFL (EFLAGS) Сегментные регистры - SS, CS, DS, ES Указатель команд IP хранит смещение следующей команды в текущем кодовом сегменте, т. е. указывает на следующую по порядку команду.

Типы регистров x 86 • • Существуют следующие типы регистров: Регистры общего назначения (РОН): EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP Регистр-указатель команд - EIP Регистр флагов - EFL (EFLAGS) Сегментные регистры - SS, CS, DS, ES Указатель команд IP хранит смещение следующей команды в текущем кодовом сегменте, т. е. указывает на следующую по порядку команду.

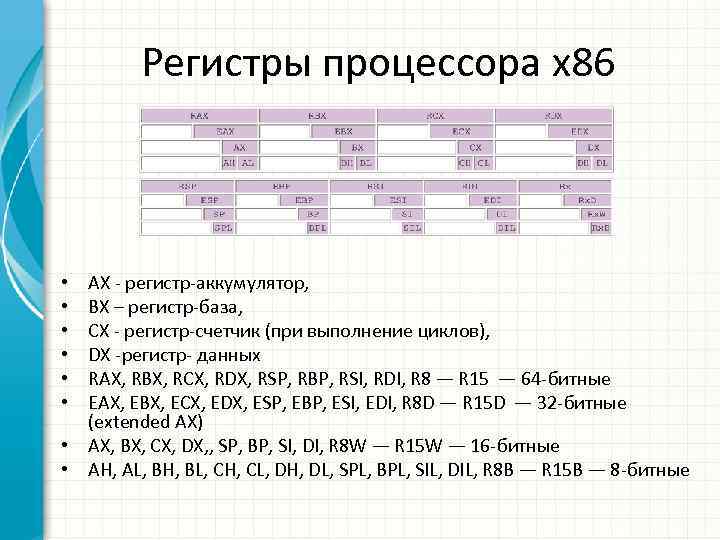

Регистры процессора x 86 AX - регистр-аккумулятор, BX – регистр-база, CX - регистр-счетчик (при выполнение циклов), DX -регистр- данных RAX, RBX, RCX, RDX, RSP, RBP, RSI, RDI, R 8 — R 15 — 64 -битные EAX, EBX, ECX, EDX, ESP, EBP, ESI, EDI, R 8 D — R 15 D — 32 -битные (extended AX) • AX, BX, CX, DX, , SP, BP, SI, DI, R 8 W — R 15 W — 16 -битные • AH, AL, BH, BL, CH, CL, DH, DL, SPL, BPL, SIL, DIL, R 8 B — R 15 B — 8 -битные • • •

Регистры процессора x 86 AX - регистр-аккумулятор, BX – регистр-база, CX - регистр-счетчик (при выполнение циклов), DX -регистр- данных RAX, RBX, RCX, RDX, RSP, RBP, RSI, RDI, R 8 — R 15 — 64 -битные EAX, EBX, ECX, EDX, ESP, EBP, ESI, EDI, R 8 D — R 15 D — 32 -битные (extended AX) • AX, BX, CX, DX, , SP, BP, SI, DI, R 8 W — R 15 W — 16 -битные • AH, AL, BH, BL, CH, CL, DH, DL, SPL, BPL, SIL, DIL, R 8 B — R 15 B — 8 -битные • • •

Команды x 86 Формат основных команд ассемблера: <команда > <операнд 1> , <операнд 2>; <команда > <операнд> Команда MOV копирует содержимое второго операнда в первый операнд. При этом содержимое второго операнда не изменяется. • Пример: mov ax, dx; mov cx, 5; mov dx, 3 f 8 h; • • • Команда MOV не воздействует на флажки.

Команды x 86 Формат основных команд ассемблера: <команда > <операнд 1> , <операнд 2>; <команда > <операнд> Команда MOV копирует содержимое второго операнда в первый операнд. При этом содержимое второго операнда не изменяется. • Пример: mov ax, dx; mov cx, 5; mov dx, 3 f 8 h; • • • Команда MOV не воздействует на флажки.

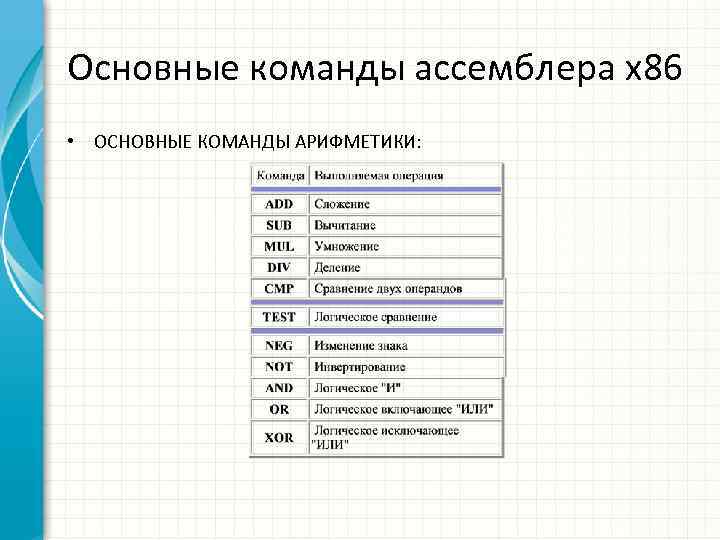

Основные команды ассемблера x 86 • ОСНОВНЫЕ КОМАНДЫ АРИФМЕТИКИ:

Основные команды ассемблера x 86 • ОСНОВНЫЕ КОМАНДЫ АРИФМЕТИКИ:

• Команды ADD, OR, ADC, SBB, AND, SUB, XOR, CMP - эти команды имеют два операнда и одинаковый формат. • Команда TEST также имеет два операнда. • Команды NEG и NOT имеют только один операнд, их формат намного проще.

• Команды ADD, OR, ADC, SBB, AND, SUB, XOR, CMP - эти команды имеют два операнда и одинаковый формат. • Команда TEST также имеет два операнда. • Команды NEG и NOT имеют только один операнд, их формат намного проще.

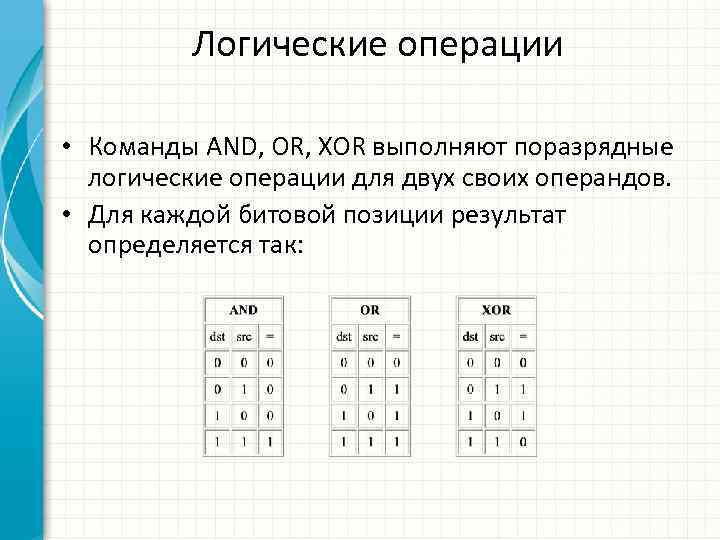

Логические операции • Команды AND, OR, XOR выполняют поразрядные логические операции для двух своих операндов. • Для каждой битовой позиции результат определяется так:

Логические операции • Команды AND, OR, XOR выполняют поразрядные логические операции для двух своих операндов. • Для каждой битовой позиции результат определяется так:

Команды сравнения двух операндов • Имеются две команды сравнения двух операндов, это команды CMP и TEST. • Результат операции никуда не записывается, результатом является установка флагов. Команды сравнения используется для условной передачи управления. • Команда CMP выполняет сравнение двух операндов "source" и "destin". • При этом выполняется арифметическая операция вычитания как по команде SUB. • Команда TEST выполняет побитовую операцию логического умножения, точно такую, как по команде AND. Порядок операндов безразличен. Результат логического умножения никуда не записывается.

Команды сравнения двух операндов • Имеются две команды сравнения двух операндов, это команды CMP и TEST. • Результат операции никуда не записывается, результатом является установка флагов. Команды сравнения используется для условной передачи управления. • Команда CMP выполняет сравнение двух операндов "source" и "destin". • При этом выполняется арифметическая операция вычитания как по команде SUB. • Команда TEST выполняет побитовую операцию логического умножения, точно такую, как по команде AND. Порядок операндов безразличен. Результат логического умножения никуда не записывается.

"Инкремент и декремент" Имеются две команды: INC - инкремент и DEC - декремент. Эти команды имеют только один операнд. Команда INC увеличивает операнд на единицу. • Команда DEC уменьшает операнд на единицу • •

"Инкремент и декремент" Имеются две команды: INC - инкремент и DEC - декремент. Эти команды имеют только один операнд. Команда INC увеличивает операнд на единицу. • Команда DEC уменьшает операнд на единицу • •

Примеры команд: • add ax, dx; add 5, 3; add ax, 3 f 8 h; • sub ax, bx; sub cx, cx; sub ax, bx; • neg ax; neg 5; neg 3 f 8 h; • cmp ax, dx; test cx, 3 f 8 h;

Примеры команд: • add ax, dx; add 5, 3; add ax, 3 f 8 h; • sub ax, bx; sub cx, cx; sub ax, bx; • neg ax; neg 5; neg 3 f 8 h; • cmp ax, dx; test cx, 3 f 8 h;

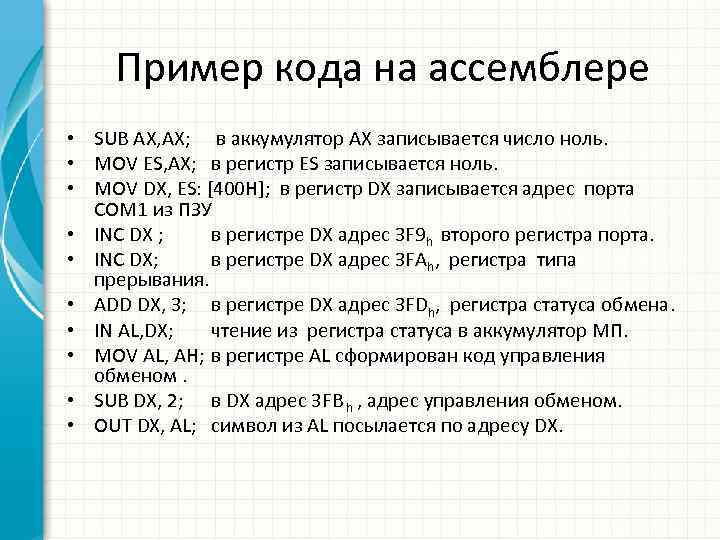

Пример кода на ассемблере • SUB AX, AX; в аккумулятор AX записывается число ноль. • MOV ES, AX; в регистр ES записывается ноль. • MOV DX, ES: [400 Н]; в регистр DX записывается адрес порта СОМ 1 из ПЗУ • INC DX ; в регистре DX адрес 3 F 9 h второго регистра порта. • INC DX; в регистре DX адрес 3 FAh, регистра типа прерывания. • ADD DX, 3; в регистре DX адрес 3 FDh, регистра статуса обмена. • IN AL, DX; чтение из регистра статуса в аккумулятор МП. • MOV AL, AH; в регистре АL сформирован код управления обменом. • SUB DX, 2; в DX адрес 3 FB h , адрес управления обменом. • OUT DX, AL; символ из AL посылается по адресу DX.

Пример кода на ассемблере • SUB AX, AX; в аккумулятор AX записывается число ноль. • MOV ES, AX; в регистр ES записывается ноль. • MOV DX, ES: [400 Н]; в регистр DX записывается адрес порта СОМ 1 из ПЗУ • INC DX ; в регистре DX адрес 3 F 9 h второго регистра порта. • INC DX; в регистре DX адрес 3 FAh, регистра типа прерывания. • ADD DX, 3; в регистре DX адрес 3 FDh, регистра статуса обмена. • IN AL, DX; чтение из регистра статуса в аккумулятор МП. • MOV AL, AH; в регистре АL сформирован код управления обменом. • SUB DX, 2; в DX адрес 3 FB h , адрес управления обменом. • OUT DX, AL; символ из AL посылается по адресу DX.

Обмен данными между ПЭВМ и ПУ • Обмен данными между ПЭВМ и ПУ может быть программно-управляемым, по прерыванию или с использованием прямого доступа к памяти (ПДП). • При программно-управляемом обмене осуществляется синхронная и асинхронная передача данных.

Обмен данными между ПЭВМ и ПУ • Обмен данными между ПЭВМ и ПУ может быть программно-управляемым, по прерыванию или с использованием прямого доступа к памяти (ПДП). • При программно-управляемом обмене осуществляется синхронная и асинхронная передача данных.

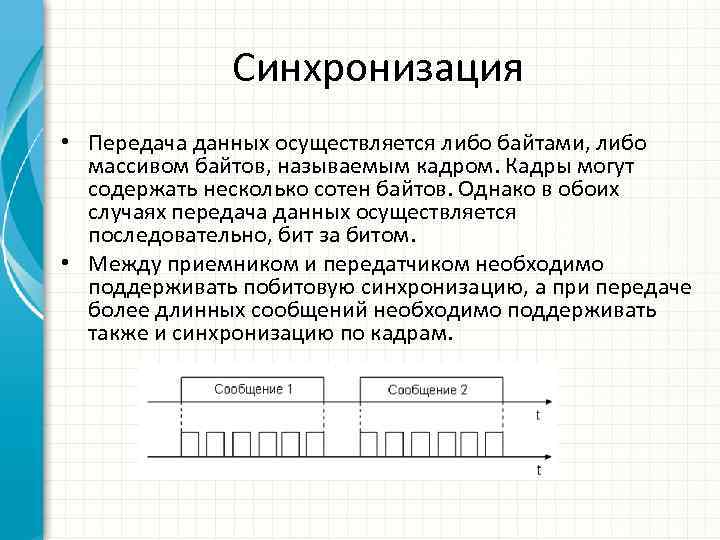

Синхронизация • Передача данных осуществляется либо байтами, либо массивом байтов, называемым кадром. Кадры могут содержать несколько сотен байтов. Однако в обоих случаях передача данных осуществляется последовательно, бит за битом. • Между приемником и передатчиком необходимо поддерживать побитовую синхронизацию, а при передаче более длинных сообщений необходимо поддерживать также и синхронизацию по кадрам.

Синхронизация • Передача данных осуществляется либо байтами, либо массивом байтов, называемым кадром. Кадры могут содержать несколько сотен байтов. Однако в обоих случаях передача данных осуществляется последовательно, бит за битом. • Между приемником и передатчиком необходимо поддерживать побитовую синхронизацию, а при передаче более длинных сообщений необходимо поддерживать также и синхронизацию по кадрам.

• При передаче данных отдельными байтами осуществляется только побитовая синхронизация. Такой режим работы называется асинхронным или стартстопным. • Этот режим удобен при невысоком качестве канала Так работает клавиатура дисплея или другого терминального устройства, с которого вводятся данные.

• При передаче данных отдельными байтами осуществляется только побитовая синхронизация. Такой режим работы называется асинхронным или стартстопным. • Этот режим удобен при невысоком качестве канала Так работает клавиатура дисплея или другого терминального устройства, с которого вводятся данные.

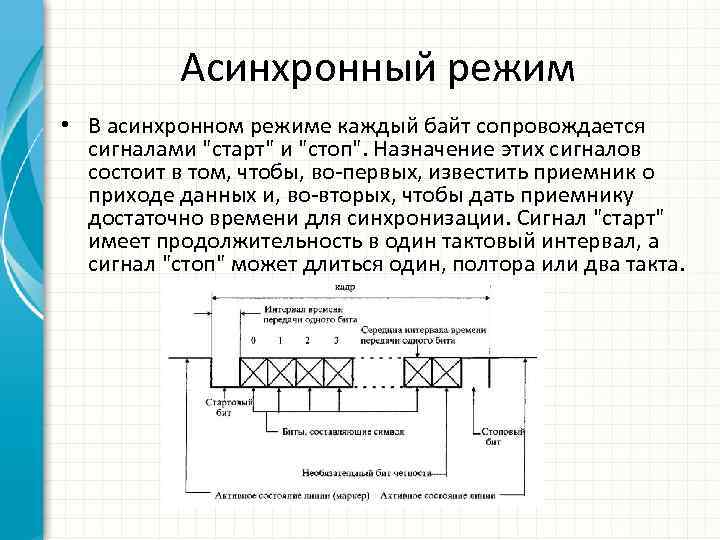

Асинхронный режим • В асинхронном режиме каждый байт сопровождается сигналами "старт" и "стоп". Назначение этих сигналов состоит в том, чтобы, во-первых, известить приемник о приходе данных и, во-вторых, чтобы дать приемнику достаточно времени для синхронизации. Сигнал "старт" имеет продолжительность в один тактовый интервал, а сигнал "стоп" может длиться один, полтора или два такта.

Асинхронный режим • В асинхронном режиме каждый байт сопровождается сигналами "старт" и "стоп". Назначение этих сигналов состоит в том, чтобы, во-первых, известить приемник о приходе данных и, во-вторых, чтобы дать приемнику достаточно времени для синхронизации. Сигнал "старт" имеет продолжительность в один тактовый интервал, а сигнал "стоп" может длиться один, полтора или два такта.

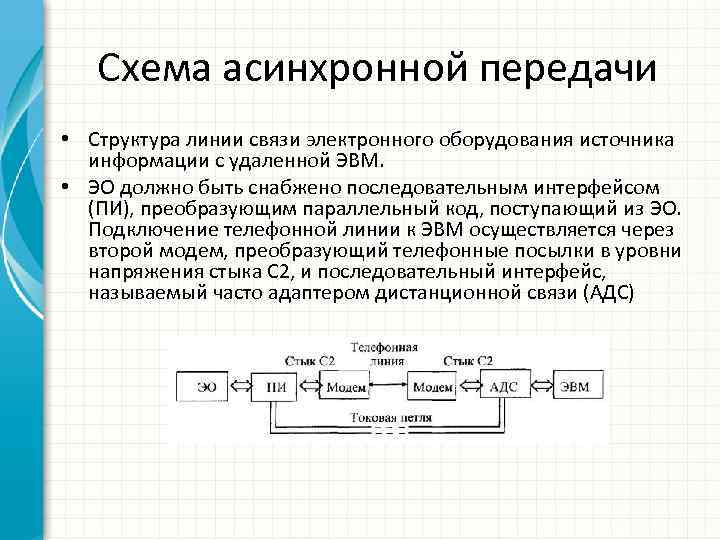

Схема асинхронной передачи • Структура линии связи электронного оборудования источника информации с удаленной ЭВМ. • ЭО должно быть снабжено последовательным интерфейсом (ПИ), преобразующим параллельный код, поступающий из ЭО. Подключение телефонной линии к ЭВМ осуществляется через второй модем, преобразующий телефонные посылки в уровни напряжения стыка С 2, и последовательный интерфейс, называемый часто адаптером дистанционной связи (АДС)

Схема асинхронной передачи • Структура линии связи электронного оборудования источника информации с удаленной ЭВМ. • ЭО должно быть снабжено последовательным интерфейсом (ПИ), преобразующим параллельный код, поступающий из ЭО. Подключение телефонной линии к ЭВМ осуществляется через второй модем, преобразующий телефонные посылки в уровни напряжения стыка С 2, и последовательный интерфейс, называемый часто адаптером дистанционной связи (АДС)

Синхронная передача данных • Эта передача данных базируется на согласовании таймеров передающего и принимающего устройств. • Для начала синхронизации и периодической проверки ее точности используются специальные символы. Передача прекращается по окончании блока и начинается при поступлении нового блока.

Синхронная передача данных • Эта передача данных базируется на согласовании таймеров передающего и принимающего устройств. • Для начала синхронизации и периодической проверки ее точности используются специальные символы. Передача прекращается по окончании блока и начинается при поступлении нового блока.

Синхронизация • При синхронном режиме передачи старт-стопные биты между каждой парой байт отсутствуют. • Пользовательские данные собираются в кадр, который предваряется байтами синхронизации. • Байт синхронизации содержит заранее известный код, например 0111110, который оповещает приемник о приходе кадра данных. • Используются специальные схемы кодирования данных, например, манчестерский код (Manchester Encoding), которые поддерживают синхронизацию.

Синхронизация • При синхронном режиме передачи старт-стопные биты между каждой парой байт отсутствуют. • Пользовательские данные собираются в кадр, который предваряется байтами синхронизации. • Байт синхронизации содержит заранее известный код, например 0111110, который оповещает приемник о приходе кадра данных. • Используются специальные схемы кодирования данных, например, манчестерский код (Manchester Encoding), которые поддерживают синхронизацию.

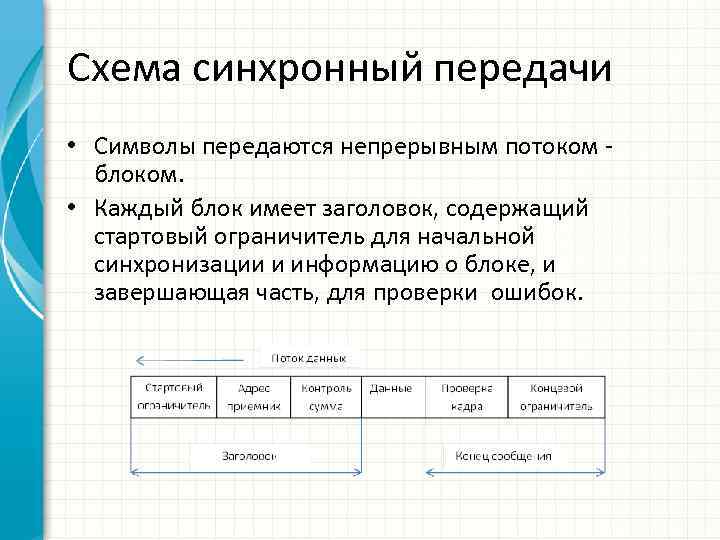

Схема синхронный передачи • Символы передаются непрерывным потоком блоком. • Каждый блок имеет заголовок, содержащий стартовый ограничитель для начальной синхронизации и информацию о блоке, и завершающая часть, для проверки ошибок.

Схема синхронный передачи • Символы передаются непрерывным потоком блоком. • Каждый блок имеет заголовок, содержащий стартовый ограничитель для начальной синхронизации и информацию о блоке, и завершающая часть, для проверки ошибок.

Cинхронно-последовательный интерфейс • SSI (англ. Synchronous Serial Interface, синхронно-последовательный интерфейс) — последовательный интерфейс передачи данных. Основан на RS 422, часто применяется в датчиках. • В SSI одно устройство является ведущим (управляющим) и задаёт синхронизацию для ведомого устройства. Использует 4 линии для передачи данных и импульсов синхронизации.

Cинхронно-последовательный интерфейс • SSI (англ. Synchronous Serial Interface, синхронно-последовательный интерфейс) — последовательный интерфейс передачи данных. Основан на RS 422, часто применяется в датчиках. • В SSI одно устройство является ведущим (управляющим) и задаёт синхронизацию для ведомого устройства. Использует 4 линии для передачи данных и импульсов синхронизации.

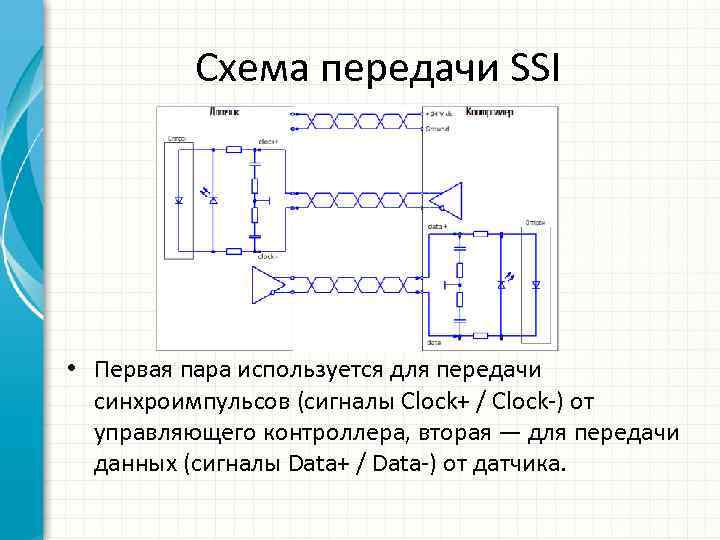

Схема передачи SSI • Первая пара используется для передачи синхроимпульсов (сигналы Clock+ / Clock-) от управляющего контроллера, вторая — для передачи данных (сигналы Data+ / Data-) от датчика.

Схема передачи SSI • Первая пара используется для передачи синхроимпульсов (сигналы Clock+ / Clock-) от управляющего контроллера, вторая — для передачи данных (сигналы Data+ / Data-) от датчика.

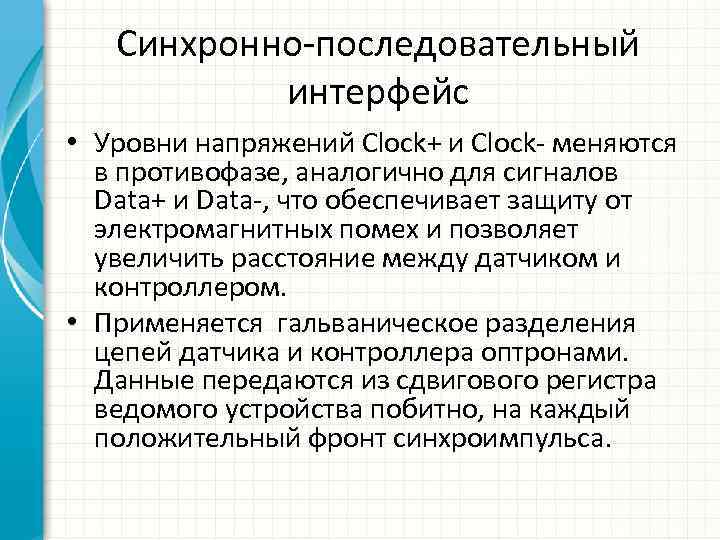

Cинхронно-последовательный интерфейс • Уровни напряжений Clock+ и Clock- меняются в противофазе, аналогично для сигналов Data+ и Data-, что обеспечивает защиту от электромагнитных помех и позволяет увеличить расстояние между датчиком и контроллером. • Применяется гальваническое разделения цепей датчика и контроллера оптронами. Данные передаются из сдвигового регистра ведомого устройства побитно, на каждый положительный фронт синхроимпульса.

Cинхронно-последовательный интерфейс • Уровни напряжений Clock+ и Clock- меняются в противофазе, аналогично для сигналов Data+ и Data-, что обеспечивает защиту от электромагнитных помех и позволяет увеличить расстояние между датчиком и контроллером. • Применяется гальваническое разделения цепей датчика и контроллера оптронами. Данные передаются из сдвигового регистра ведомого устройства побитно, на каждый положительный фронт синхроимпульса.