fb5052bff340d2cc859bad984f150fe8.ppt

- Количество слайдов: 26

Using FPGAs with Processors in YOUR Designs Class 5: Your Designs 9/27/2013 Warren Miller 1

Using FPGAs with Processors in YOUR Designs Class 5: Your Designs 9/27/2013 Warren Miller 1

This Week’s Agenda 9/23/13 9/24/13 9/25/13 9/26/13 9/27/13 An Intro to FPGAs with Processors Architecture Details Tool Support Application Examples A Review of YOUR Designs 2

This Week’s Agenda 9/23/13 9/24/13 9/25/13 9/26/13 9/27/13 An Intro to FPGAs with Processors Architecture Details Tool Support Application Examples A Review of YOUR Designs 2

Today’s Topics • Goals and Objectives – Understand the “best fit” for YOUR suggested applications • Architecture Review • Applications Positioning Review • Your Designs 3

Today’s Topics • Goals and Objectives – Understand the “best fit” for YOUR suggested applications • Architecture Review • Applications Positioning Review • Your Designs 3

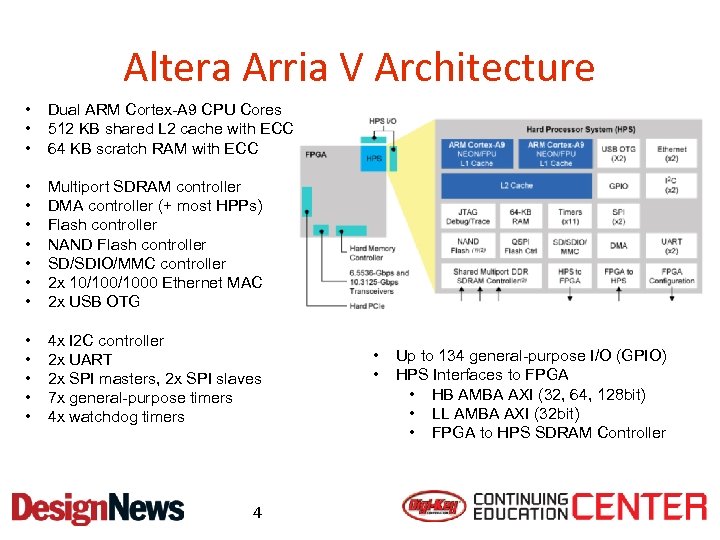

Altera Arria V Architecture • • • Dual ARM Cortex-A 9 CPU Cores 512 KB shared L 2 cache with ECC 64 KB scratch RAM with ECC • • Multiport SDRAM controller DMA controller (+ most HPPs) Flash controller NAND Flash controller SD/SDIO/MMC controller 2 x 10/1000 Ethernet MAC 2 x USB OTG • • • 4 x I 2 C controller 2 x UART 2 x SPI masters, 2 x SPI slaves 7 x general-purpose timers 4 x watchdog timers 4 • • Up to 134 general-purpose I/O (GPIO) HPS Interfaces to FPGA • HB AMBA AXI (32, 64, 128 bit) • LL AMBA AXI (32 bit) • FPGA to HPS SDRAM Controller

Altera Arria V Architecture • • • Dual ARM Cortex-A 9 CPU Cores 512 KB shared L 2 cache with ECC 64 KB scratch RAM with ECC • • Multiport SDRAM controller DMA controller (+ most HPPs) Flash controller NAND Flash controller SD/SDIO/MMC controller 2 x 10/1000 Ethernet MAC 2 x USB OTG • • • 4 x I 2 C controller 2 x UART 2 x SPI masters, 2 x SPI slaves 7 x general-purpose timers 4 x watchdog timers 4 • • Up to 134 general-purpose I/O (GPIO) HPS Interfaces to FPGA • HB AMBA AXI (32, 64, 128 bit) • LL AMBA AXI (32 bit) • FPGA to HPS SDRAM Controller

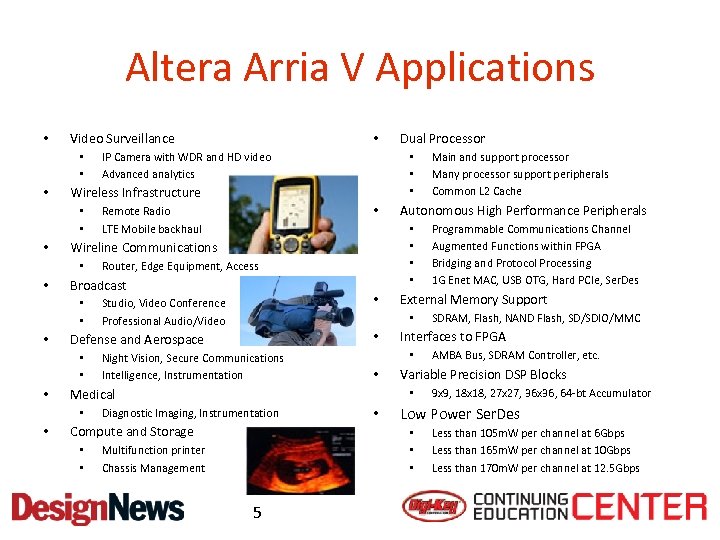

Altera Arria V Applications • Video Surveillance • • • Night Vision, Secure Communications Intelligence, Instrumentation • Compute and Storage • • • 5 9 x 9, 18 x 18, 27 x 27, 36 x 36, 64 -bt Accumulator Low Power Ser. Des • • • Multifunction printer Chassis Management AMBA Bus, SDRAM Controller, etc. Variable Precision DSP Blocks • Diagnostic Imaging, Instrumentation SDRAM, Flash, NAND Flash, SD/SDIO/MMC Interfaces to FPGA • Medical • • • Programmable Communications Channel Augmented Functions within FPGA Bridging and Protocol Processing 1 G Enet MAC, USB OTG, Hard PCIe, Ser. Des External Memory Support • Defense and Aerospace • • Studio, Video Conference Professional Audio/Video Main and support processor Many processor support peripherals Common L 2 Cache Autonomous High Performance Peripherals • • Router, Edge Equipment, Access Broadcast • • Remote Radio LTE Mobile backhaul Dual Processor • • • Wireline Communications • • IP Camera with WDR and HD video Advanced analytics Wireless Infrastructure • • Less than 105 m. W per channel at 6 Gbps Less than 165 m. W per channel at 10 Gbps Less than 170 m. W per channel at 12. 5 Gbps

Altera Arria V Applications • Video Surveillance • • • Night Vision, Secure Communications Intelligence, Instrumentation • Compute and Storage • • • 5 9 x 9, 18 x 18, 27 x 27, 36 x 36, 64 -bt Accumulator Low Power Ser. Des • • • Multifunction printer Chassis Management AMBA Bus, SDRAM Controller, etc. Variable Precision DSP Blocks • Diagnostic Imaging, Instrumentation SDRAM, Flash, NAND Flash, SD/SDIO/MMC Interfaces to FPGA • Medical • • • Programmable Communications Channel Augmented Functions within FPGA Bridging and Protocol Processing 1 G Enet MAC, USB OTG, Hard PCIe, Ser. Des External Memory Support • Defense and Aerospace • • Studio, Video Conference Professional Audio/Video Main and support processor Many processor support peripherals Common L 2 Cache Autonomous High Performance Peripherals • • Router, Edge Equipment, Access Broadcast • • Remote Radio LTE Mobile backhaul Dual Processor • • • Wireline Communications • • IP Camera with WDR and HD video Advanced analytics Wireless Infrastructure • • Less than 105 m. W per channel at 6 Gbps Less than 165 m. W per channel at 10 Gbps Less than 170 m. W per channel at 12. 5 Gbps

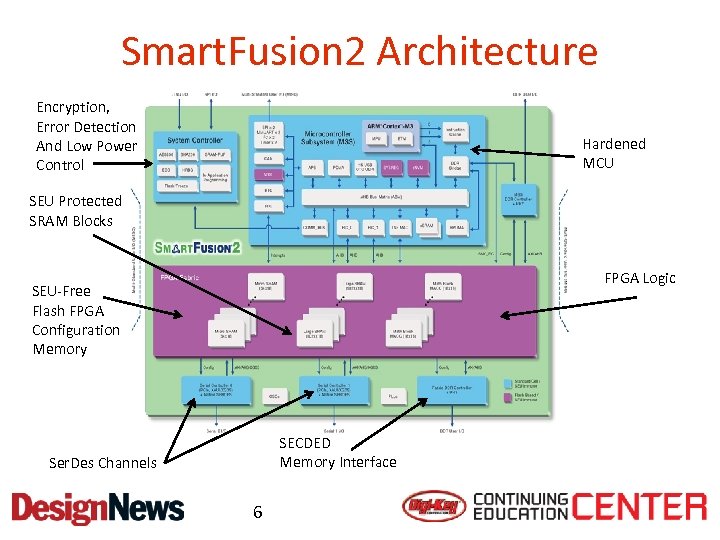

Smart. Fusion 2 Architecture Encryption, Error Detection And Low Power Control Hardened MCU SEU Protected SRAM Blocks FPGA Logic SEU-Free Flash FPGA Configuration Memory SECDED Memory Interface Ser. Des Channels 6

Smart. Fusion 2 Architecture Encryption, Error Detection And Low Power Control Hardened MCU SEU Protected SRAM Blocks FPGA Logic SEU-Free Flash FPGA Configuration Memory SECDED Memory Interface Ser. Des Channels 6

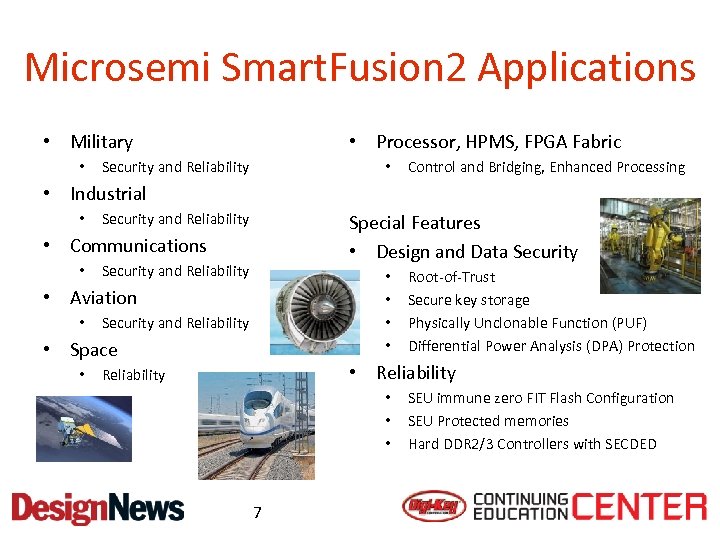

Microsemi Smart. Fusion 2 Applications • Military • • Processor, HPMS, FPGA Fabric Security and Reliability • Control and Bridging, Enhanced Processing • Industrial • Security and Reliability Special Features • Design and Data Security • Communications • Security and Reliability • • • Aviation • Security and Reliability • Space • Root-of-Trust Secure key storage Physically Unclonable Function (PUF) Differential Power Analysis (DPA) Protection • Reliability • • • 7 SEU immune zero FIT Flash Configuration SEU Protected memories Hard DDR 2/3 Controllers with SECDED

Microsemi Smart. Fusion 2 Applications • Military • • Processor, HPMS, FPGA Fabric Security and Reliability • Control and Bridging, Enhanced Processing • Industrial • Security and Reliability Special Features • Design and Data Security • Communications • Security and Reliability • • • Aviation • Security and Reliability • Space • Root-of-Trust Secure key storage Physically Unclonable Function (PUF) Differential Power Analysis (DPA) Protection • Reliability • • • 7 SEU immune zero FIT Flash Configuration SEU Protected memories Hard DDR 2/3 Controllers with SECDED

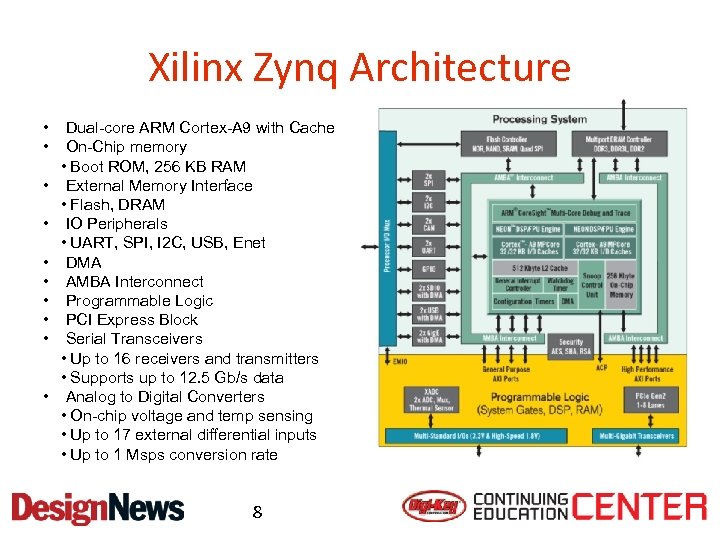

Xilinx Zynq Architecture • • • Dual-core ARM Cortex-A 9 with Cache On-Chip memory • Boot ROM, 256 KB RAM External Memory Interface • Flash, DRAM IO Peripherals • UART, SPI, I 2 C, USB, Enet DMA AMBA Interconnect Programmable Logic PCI Express Block Serial Transceivers • Up to 16 receivers and transmitters • Supports up to 12. 5 Gb/s data Analog to Digital Converters • On-chip voltage and temp sensing • Up to 17 external differential inputs • Up to 1 Msps conversion rate 8

Xilinx Zynq Architecture • • • Dual-core ARM Cortex-A 9 with Cache On-Chip memory • Boot ROM, 256 KB RAM External Memory Interface • Flash, DRAM IO Peripherals • UART, SPI, I 2 C, USB, Enet DMA AMBA Interconnect Programmable Logic PCI Express Block Serial Transceivers • Up to 16 receivers and transmitters • Supports up to 12. 5 Gb/s data Analog to Digital Converters • On-chip voltage and temp sensing • Up to 17 external differential inputs • Up to 1 Msps conversion rate 8

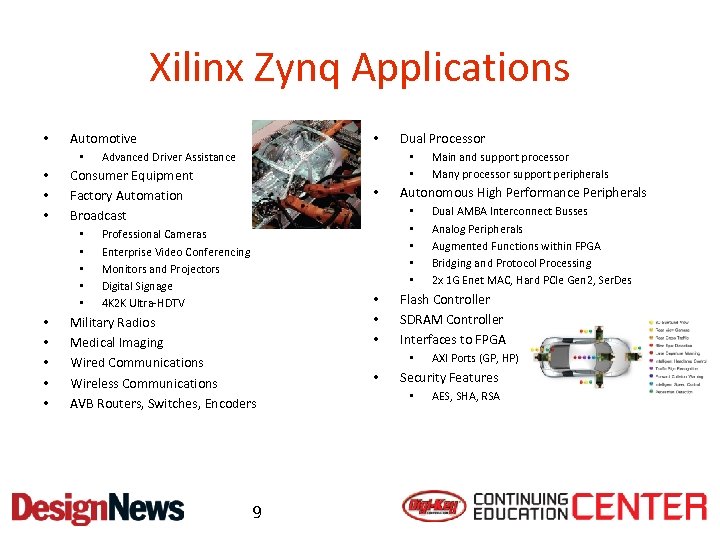

Xilinx Zynq Applications • Automotive • • Advanced Driver Assistance Dual Processor • • Consumer Equipment Factory Automation Broadcast • • • Autonomous High Performance Peripherals • • • Professional Cameras Enterprise Video Conferencing Monitors and Projectors Digital Signage 4 K 2 K Ultra-HDTV Military Radios Medical Imaging Wired Communications Wireless Communications AVB Routers, Switches, Encoders 9 • • • Dual AMBA Interconnect Busses Analog Peripherals Augmented Functions within FPGA Bridging and Protocol Processing 2 x 1 G Enet MAC, Hard PCIe Gen 2, Ser. Des Flash Controller SDRAM Controller Interfaces to FPGA • • Main and support processor Many processor support peripherals AXI Ports (GP, HP) Security Features • AES, SHA, RSA

Xilinx Zynq Applications • Automotive • • Advanced Driver Assistance Dual Processor • • Consumer Equipment Factory Automation Broadcast • • • Autonomous High Performance Peripherals • • • Professional Cameras Enterprise Video Conferencing Monitors and Projectors Digital Signage 4 K 2 K Ultra-HDTV Military Radios Medical Imaging Wired Communications Wireless Communications AVB Routers, Switches, Encoders 9 • • • Dual AMBA Interconnect Busses Analog Peripherals Augmented Functions within FPGA Bridging and Protocol Processing 2 x 1 G Enet MAC, Hard PCIe Gen 2, Ser. Des Flash Controller SDRAM Controller Interfaces to FPGA • • Main and support processor Many processor support peripherals AXI Ports (GP, HP) Security Features • AES, SHA, RSA

Your Applications • Thanks for your input! • Many good applications- too many to cover individually • Tried to combine some applications so I can cover as many key elements as possible • Hopefully will provide you with a good starting point… • Get an eval board and start using the tools! 10

Your Applications • Thanks for your input! • Many good applications- too many to cover individually • Tried to combine some applications so I can cover as many key elements as possible • Hopefully will provide you with a good starting point… • Get an eval board and start using the tools! 10

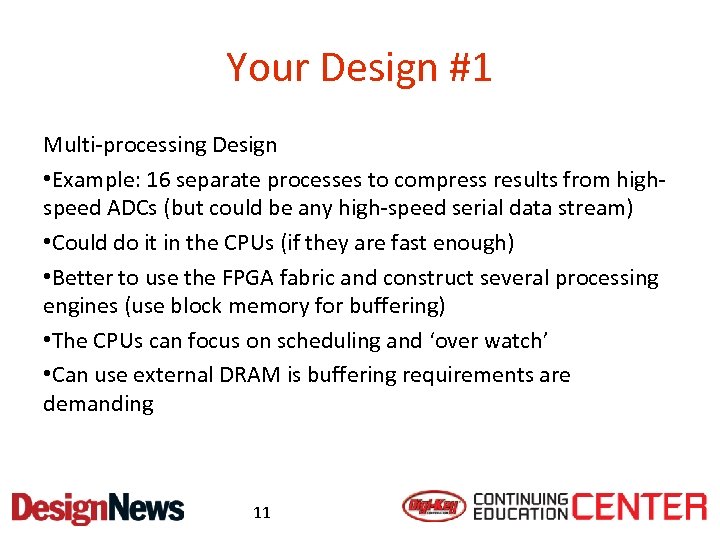

Your Design #1 Multi-processing Design • Example: 16 separate processes to compress results from highspeed ADCs (but could be any high-speed serial data stream) • Could do it in the CPUs (if they are fast enough) • Better to use the FPGA fabric and construct several processing engines (use block memory for buffering) • The CPUs can focus on scheduling and ‘over watch’ • Can use external DRAM is buffering requirements are demanding 11

Your Design #1 Multi-processing Design • Example: 16 separate processes to compress results from highspeed ADCs (but could be any high-speed serial data stream) • Could do it in the CPUs (if they are fast enough) • Better to use the FPGA fabric and construct several processing engines (use block memory for buffering) • The CPUs can focus on scheduling and ‘over watch’ • Can use external DRAM is buffering requirements are demanding 11

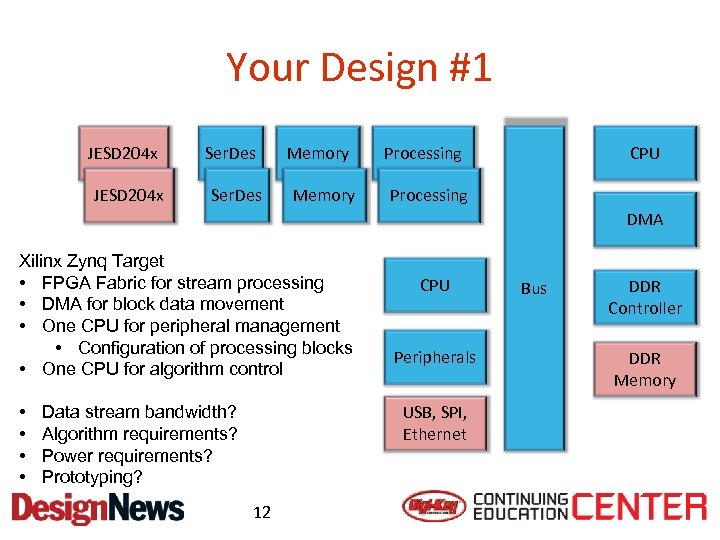

Your Design #1 JESD 204 x Ser. Des Memory Processing CPU Processing DMA Xilinx Zynq Target • FPGA Fabric for stream processing • DMA for block data movement • One CPU for peripheral management • Configuration of processing blocks • One CPU for algorithm control • • CPU Peripherals USB, SPI, Ethernet Data stream bandwidth? Algorithm requirements? Power requirements? Prototyping? 12 Bus DDR Controller DDR Memory

Your Design #1 JESD 204 x Ser. Des Memory Processing CPU Processing DMA Xilinx Zynq Target • FPGA Fabric for stream processing • DMA for block data movement • One CPU for peripheral management • Configuration of processing blocks • One CPU for algorithm control • • CPU Peripherals USB, SPI, Ethernet Data stream bandwidth? Algorithm requirements? Power requirements? Prototyping? 12 Bus DDR Controller DDR Memory

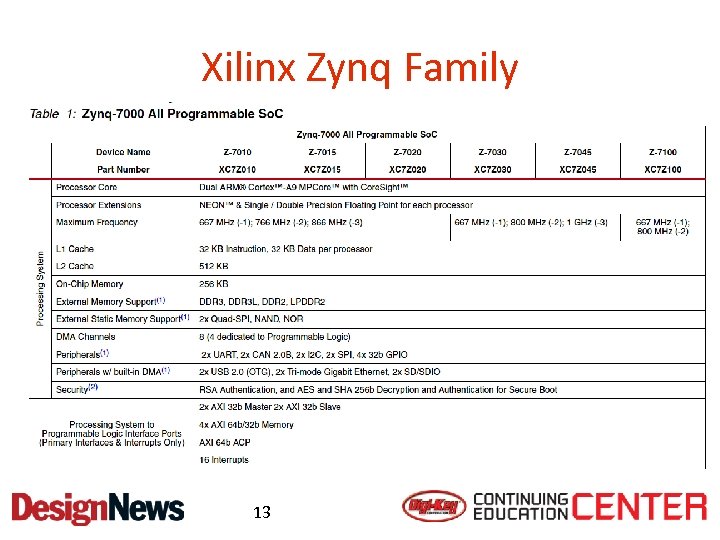

Xilinx Zynq Family 13

Xilinx Zynq Family 13

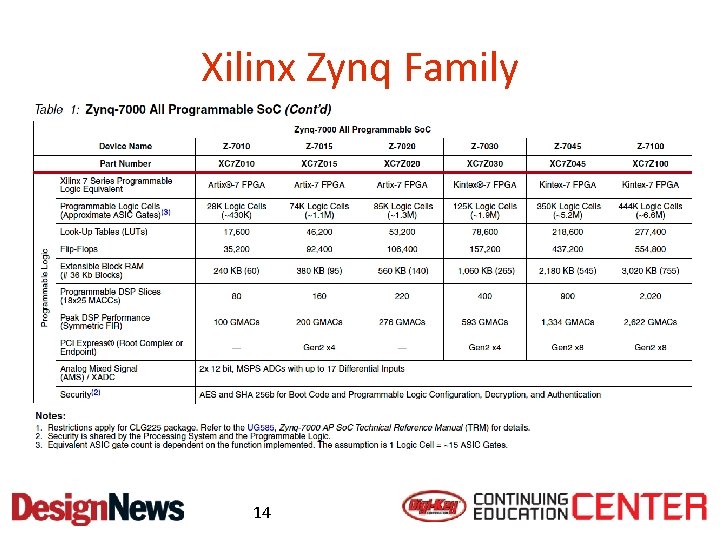

Xilinx Zynq Family 14

Xilinx Zynq Family 14

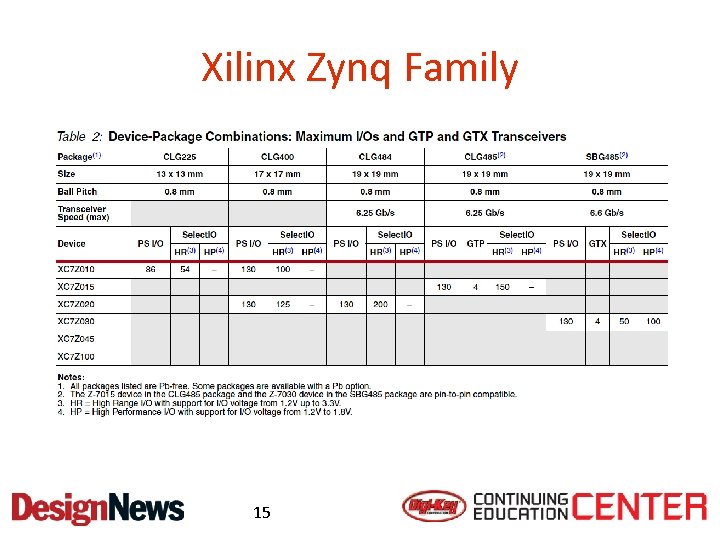

Xilinx Zynq Family 15

Xilinx Zynq Family 15

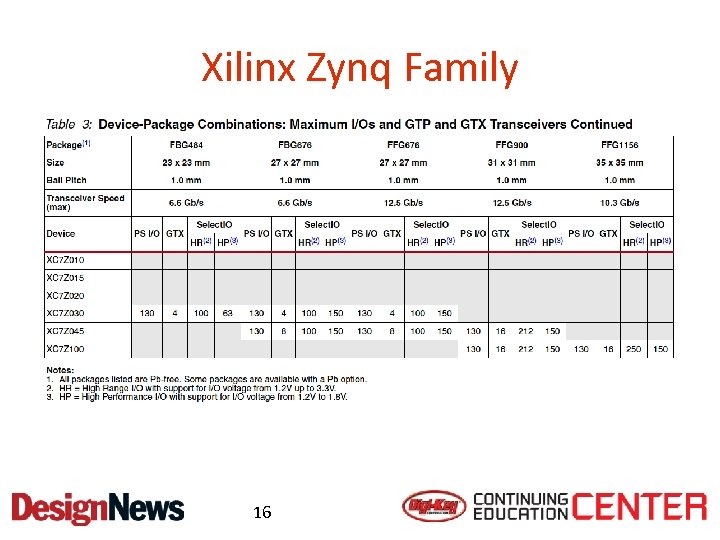

Xilinx Zynq Family 16

Xilinx Zynq Family 16

Your Design #2 Space Application • Between 10 – 50 MHz • Error Detection and Correction for external SRAM • Signal acquisition • Balance performance and Power consumption • Program in C or assembly 17

Your Design #2 Space Application • Between 10 – 50 MHz • Error Detection and Correction for external SRAM • Signal acquisition • Balance performance and Power consumption • Program in C or assembly 17

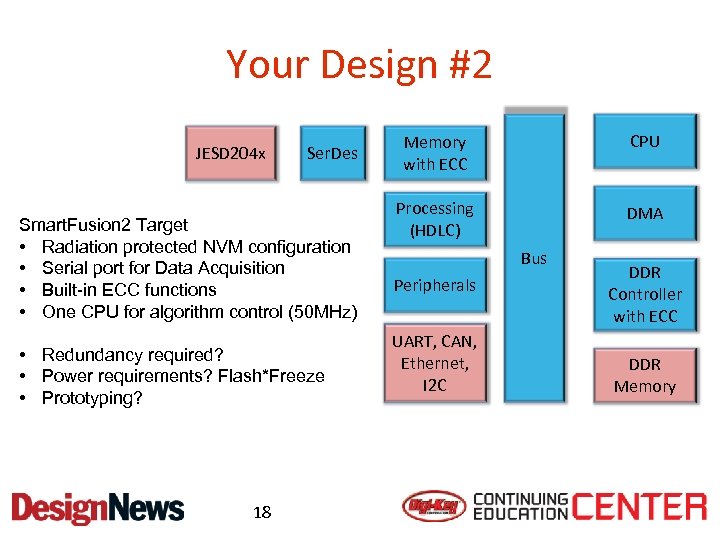

Your Design #2 JESD 204 x Ser. Des Smart. Fusion 2 Target • Radiation protected NVM configuration • Serial port for Data Acquisition • Built-in ECC functions • One CPU for algorithm control (50 MHz) • Redundancy required? • Power requirements? Flash*Freeze • Prototyping? 18 Memory with ECC CPU Processing (HDLC) DMA Bus Peripherals UART, CAN, Ethernet, I 2 C DDR Controller with ECC DDR Memory

Your Design #2 JESD 204 x Ser. Des Smart. Fusion 2 Target • Radiation protected NVM configuration • Serial port for Data Acquisition • Built-in ECC functions • One CPU for algorithm control (50 MHz) • Redundancy required? • Power requirements? Flash*Freeze • Prototyping? 18 Memory with ECC CPU Processing (HDLC) DMA Bus Peripherals UART, CAN, Ethernet, I 2 C DDR Controller with ECC DDR Memory

Your Design #3 Medical Application • Portable equipment • Bio Sensing • Low Power and efficient performance • Security • Wireless • Graphics User Interface (LCD, Keypad) 19

Your Design #3 Medical Application • Portable equipment • Bio Sensing • Low Power and efficient performance • Security • Wireless • Graphics User Interface (LCD, Keypad) 19

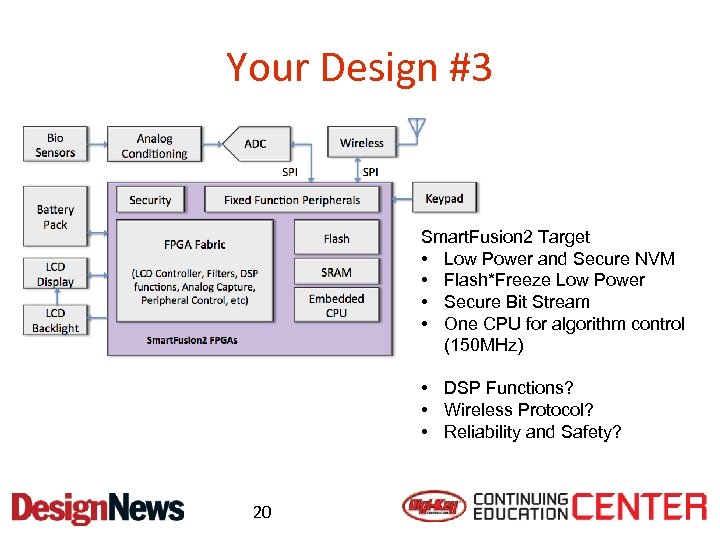

Your Design #3 Smart. Fusion 2 Target • Low Power and Secure NVM • Flash*Freeze Low Power • Secure Bit Stream • One CPU for algorithm control (150 MHz) • DSP Functions? • Wireless Protocol? • Reliability and Safety? 20

Your Design #3 Smart. Fusion 2 Target • Low Power and Secure NVM • Flash*Freeze Low Power • Secure Bit Stream • One CPU for algorithm control (150 MHz) • DSP Functions? • Wireless Protocol? • Reliability and Safety? 20

Your Design #4 Audio Processing (Test Equipment) • Spectral Acquisition • Spectral Analysis • Data Storage and Communication • GUI • Balance performance and Power consumption • Program in C or assembly 21

Your Design #4 Audio Processing (Test Equipment) • Spectral Acquisition • Spectral Analysis • Data Storage and Communication • GUI • Balance performance and Power consumption • Program in C or assembly 21

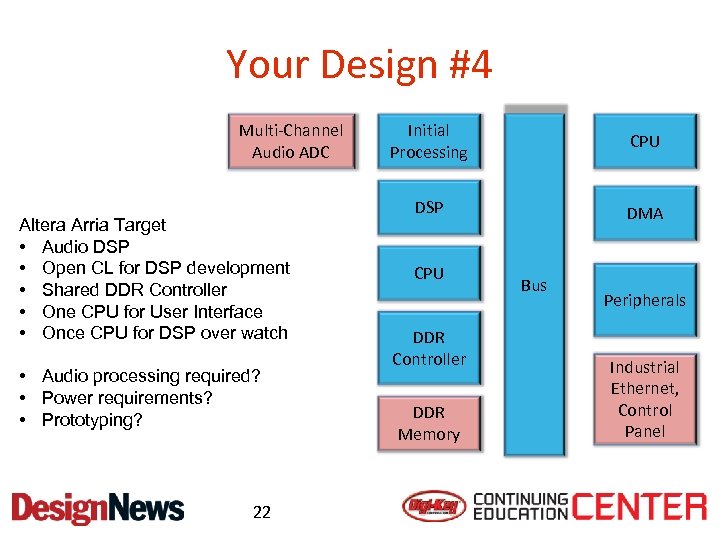

Your Design #4 Multi-Channel Audio ADC Altera Arria Target • Audio DSP • Open CL for DSP development • Shared DDR Controller • One CPU for User Interface • Once CPU for DSP over watch • Audio processing required? • Power requirements? • Prototyping? 22 Initial Processing CPU DSP DMA CPU DDR Controller DDR Memory Bus Peripherals Industrial Ethernet, Control Panel

Your Design #4 Multi-Channel Audio ADC Altera Arria Target • Audio DSP • Open CL for DSP development • Shared DDR Controller • One CPU for User Interface • Once CPU for DSP over watch • Audio processing required? • Power requirements? • Prototyping? 22 Initial Processing CPU DSP DMA CPU DDR Controller DDR Memory Bus Peripherals Industrial Ethernet, Control Panel

Your Design #5 Environmental Sensor • Vibration, Humidity, Temperature, Magnetic • Log sensor readings • Set trip points for wireless alarm • Central control collects data and dumps logs • Low Power, Low Performance • Program in C or assembly 23

Your Design #5 Environmental Sensor • Vibration, Humidity, Temperature, Magnetic • Log sensor readings • Set trip points for wireless alarm • Central control collects data and dumps logs • Low Power, Low Performance • Program in C or assembly 23

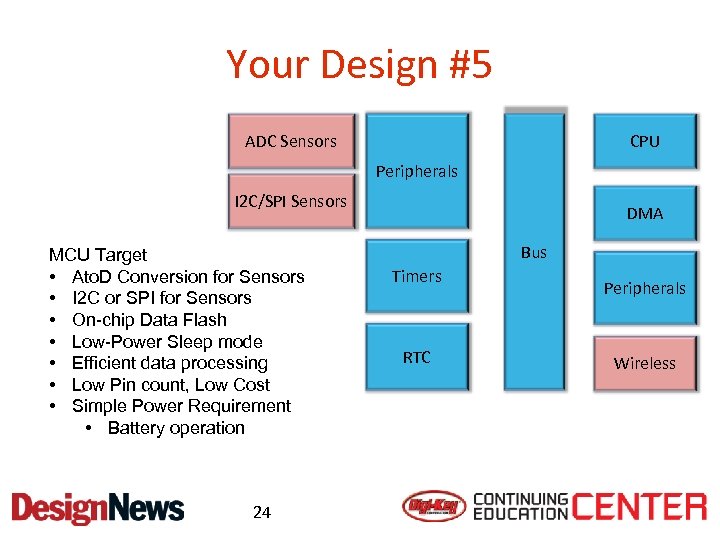

Your Design #5 ADC Sensors CPU Peripherals I 2 C/SPI Sensors MCU Target • Ato. D Conversion for Sensors • I 2 C or SPI for Sensors • On-chip Data Flash • Low-Power Sleep mode • Efficient data processing • Low Pin count, Low Cost • Simple Power Requirement • Battery operation 24 DMA Bus Timers RTC Peripherals Wireless

Your Design #5 ADC Sensors CPU Peripherals I 2 C/SPI Sensors MCU Target • Ato. D Conversion for Sensors • I 2 C or SPI for Sensors • On-chip Data Flash • Low-Power Sleep mode • Efficient data processing • Low Pin count, Low Cost • Simple Power Requirement • Battery operation 24 DMA Bus Timers RTC Peripherals Wireless

Additional Resources Altera Arria Web Page Altera Arria Development Kits Microsemi Smart. Fusion 2 Web Page Microsemi Smart. Fusion 2 Development Kits Xilinx Zynq Web Page Xilinx Zynq Development Kits All Programmable Planet Warren’s CEC Course on Application Specific Programmable Logic Devices 25

Additional Resources Altera Arria Web Page Altera Arria Development Kits Microsemi Smart. Fusion 2 Web Page Microsemi Smart. Fusion 2 Development Kits Xilinx Zynq Web Page Xilinx Zynq Development Kits All Programmable Planet Warren’s CEC Course on Application Specific Programmable Logic Devices 25

This Week’s Agenda 9/23/13 9/24/13 9/25/13 9/26/13 9/27/13 An Intro to FPGAs with Processors Architecture Details Tool Support Application Examples A Review of YOUR Designs ! E N O D 26

This Week’s Agenda 9/23/13 9/24/13 9/25/13 9/26/13 9/27/13 An Intro to FPGAs with Processors Architecture Details Tool Support Application Examples A Review of YOUR Designs ! E N O D 26