05 Память.ppt

- Количество слайдов: 26

Управление оперативной памятью

Управление оперативной памятью

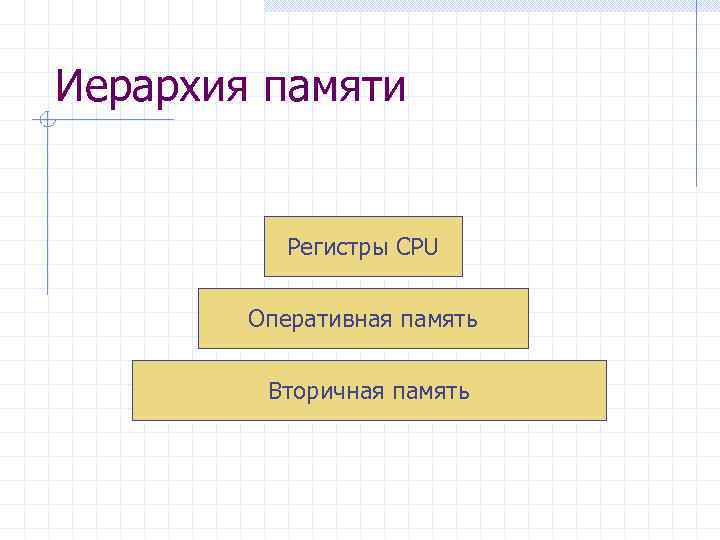

Иерархия памяти Регистры CPU Оперативная память Вторичная память

Иерархия памяти Регистры CPU Оперативная память Вторичная память

Иерархия памяти Регистры CPU Оперативная память SSD HDD Быстродействие, Цена за бит Ёмкость устройства Кэш-память CPU

Иерархия памяти Регистры CPU Оперативная память SSD HDD Быстродействие, Цена за бит Ёмкость устройства Кэш-память CPU

Локальность Принцип локальности или локализации обращений: Реальные программы в течение ограниченного промежутка времени работают с небольшим набором адресов памяти.

Локальность Принцип локальности или локализации обращений: Реальные программы в течение ограниченного промежутка времени работают с небольшим набором адресов памяти.

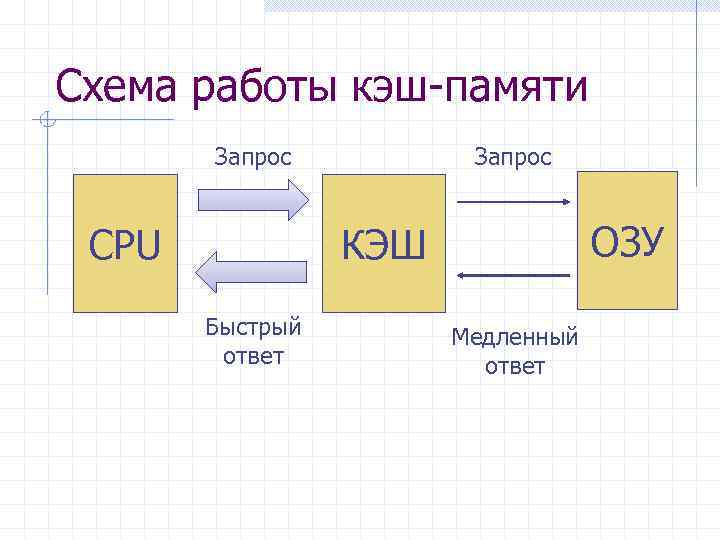

Схема работы кэш-памяти Запрос CPU ОЗУ КЭШ Быстрый ответ Медленный ответ

Схема работы кэш-памяти Запрос CPU ОЗУ КЭШ Быстрый ответ Медленный ответ

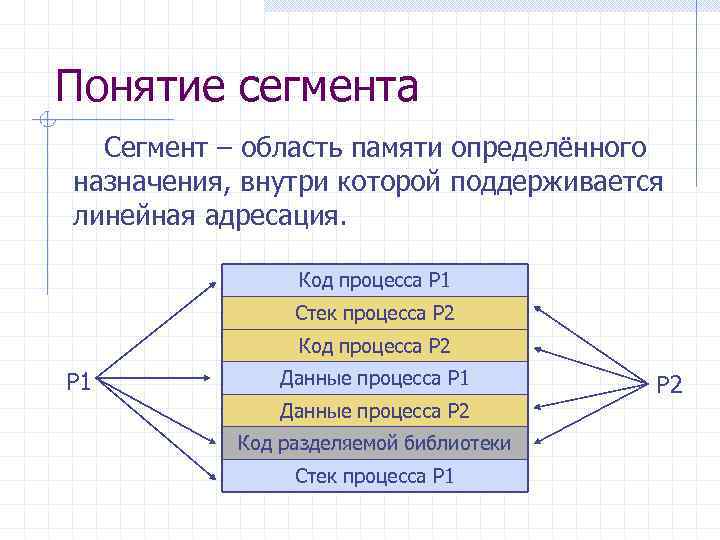

Понятие сегмента Сегмент – область памяти определённого назначения, внутри которой поддерживается линейная адресация. Код процесса P 1 Стек процесса P 2 Код процесса P 2 P 1 Данные процесса P 2 Код разделяемой библиотеки Стек процесса Р 1 P 2

Понятие сегмента Сегмент – область памяти определённого назначения, внутри которой поддерживается линейная адресация. Код процесса P 1 Стек процесса P 2 Код процесса P 2 P 1 Данные процесса P 2 Код разделяемой библиотеки Стек процесса Р 1 P 2

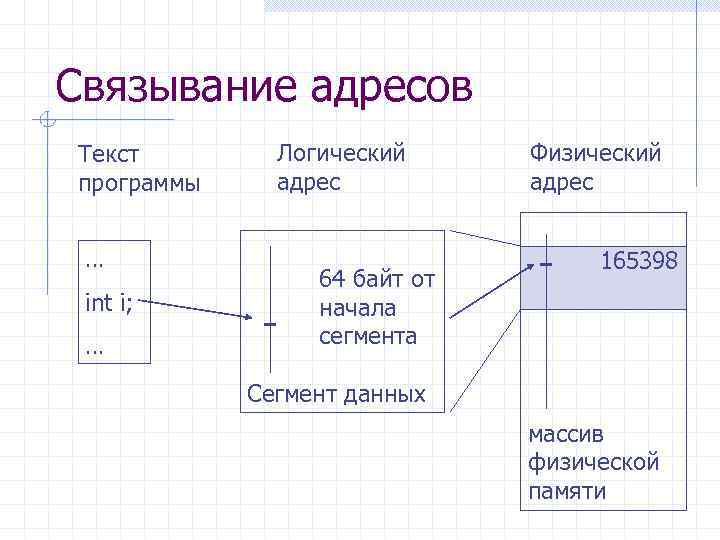

Связывание адресов Текст программы … int i; … Логический адрес 64 байт от начала сегмента Физический адрес 165398 Сегмент данных массив физической памяти

Связывание адресов Текст программы … int i; … Логический адрес 64 байт от начала сегмента Физический адрес 165398 Сегмент данных массив физической памяти

Связывание адресов Этап компиляции Вся информация о расположении программы в памяти известна при компиляции Этап загрузки ОС осуществляет коррекцию адресов при загрузке программы Этап выполнения Программа может быть перемещена в памяти в процессе выполнения

Связывание адресов Этап компиляции Вся информация о расположении программы в памяти известна при компиляции Этап загрузки ОС осуществляет коррекцию адресов при загрузке программы Этап выполнения Программа может быть перемещена в памяти в процессе выполнения

Функции системы управления памятью отображение адресного пространства процесса на конкретные области физической памяти; распределение памяти между конкурирующими процессами; контроль доступа к адресным пространствам процессов; выгрузка процессов (целиком или частично) во внешнюю память, когда в оперативной памяти недостаточно места; учет свободной и занятой памяти.

Функции системы управления памятью отображение адресного пространства процесса на конкретные области физической памяти; распределение памяти между конкурирующими процессами; контроль доступа к адресным пространствам процессов; выгрузка процессов (целиком или частично) во внешнюю память, когда в оперативной памяти недостаточно места; учет свободной и занятой памяти.

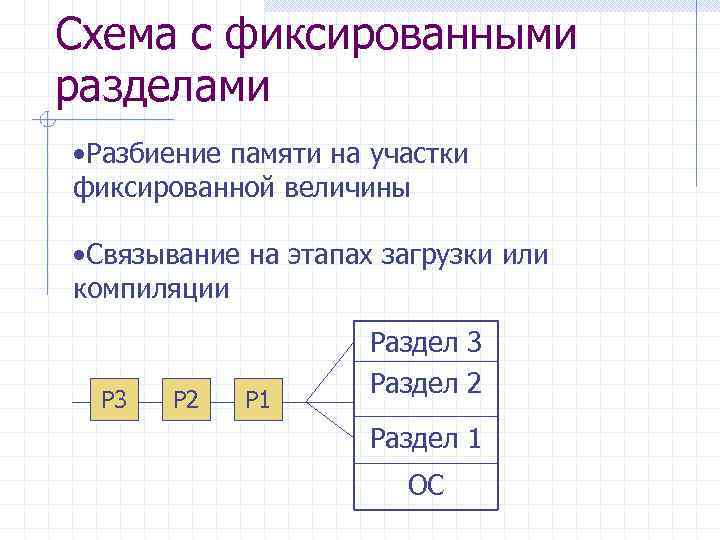

Схема с фиксированными разделами • Разбиение памяти на участки фиксированной величины • Связывание на этапах загрузки или компиляции P 3 P 2 P 1 Раздел 3 Раздел 2 Раздел 1 ОС

Схема с фиксированными разделами • Разбиение памяти на участки фиксированной величины • Связывание на этапах загрузки или компиляции P 3 P 2 P 1 Раздел 3 Раздел 2 Раздел 1 ОС

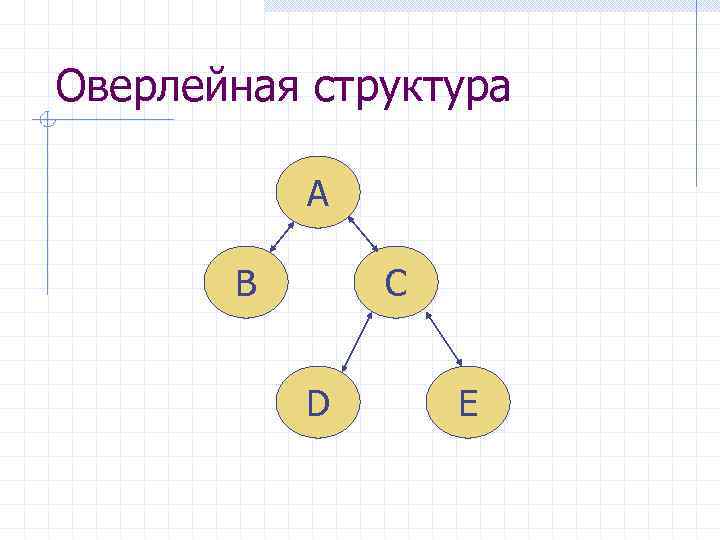

Оверлейная структура А B C D E

Оверлейная структура А B C D E

Свопинг (swapping) Свопинг - перемещение выполняющегося процесса целиком из оперативной памяти на внешний носитель. Процесс может быть возвращен в то же место или в другое.

Свопинг (swapping) Свопинг - перемещение выполняющегося процесса целиком из оперативной памяти на внешний носитель. Процесс может быть возвращен в то же место или в другое.

Схема с переменными разделами В начале память свободна и не разделена на разделы При загрузке процесса ему выделяется необходимый объем памяти При выгрузке память освобождается

Схема с переменными разделами В начале память свободна и не разделена на разделы При загрузке процесса ему выделяется необходимый объем памяти При выгрузке память освобождается

Схема с переменными разделами P 1 ОС P 2 P 1 ОС P 3 P 2 P 4 ОС

Схема с переменными разделами P 1 ОС P 2 P 1 ОС P 3 P 2 P 4 ОС

Стратегии размещения Стратегия первого подходящего (first fit) Стратегия лучшего подходящего (best fit) Стратегия наименее подходящего (worst fit)

Стратегии размещения Стратегия первого подходящего (first fit) Стратегия лучшего подходящего (best fit) Стратегия наименее подходящего (worst fit)

Страничная память Физическая и логическая память представляются состоящими из блоков одинакового размера, называемых страницы (page) для логической памяти, кадры (frame) для физической. Размер страниц фиксирован и обычно кратен степени 2. Одна страница соответствует одному кадру.

Страничная память Физическая и логическая память представляются состоящими из блоков одинакового размера, называемых страницы (page) для логической памяти, кадры (frame) для физической. Размер страниц фиксирован и обычно кратен степени 2. Одна страница соответствует одному кадру.

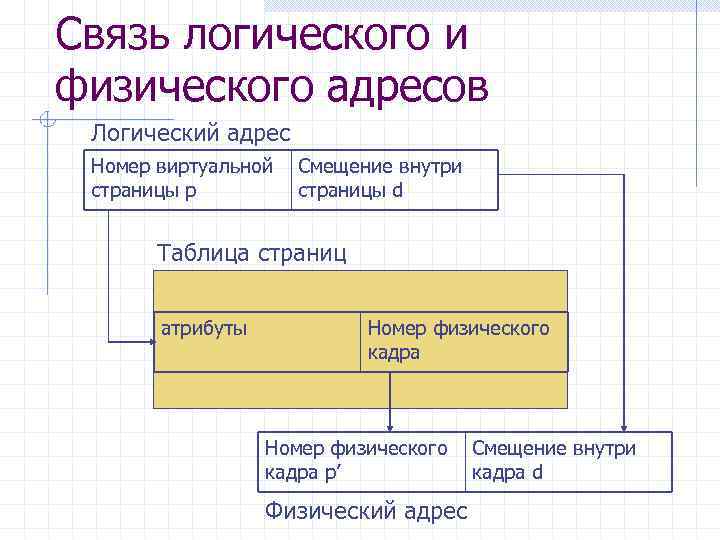

Связь логического и физического адресов Логический адрес Номер виртуальной страницы p Смещение внутри страницы d Таблица страниц атрибуты Номер физического кадра p’ Физический адрес Смещение внутри кадра d

Связь логического и физического адресов Логический адрес Номер виртуальной страницы p Смещение внутри страницы d Таблица страниц атрибуты Номер физического кадра p’ Физический адрес Смещение внутри кадра d

Сегментная организация памяти Является следствием логического разделения памяти Размер сегмента ограничен адресным пространством CPU, может меняться динамически

Сегментная организация памяти Является следствием логического разделения памяти Размер сегмента ограничен адресным пространством CPU, может меняться динамически

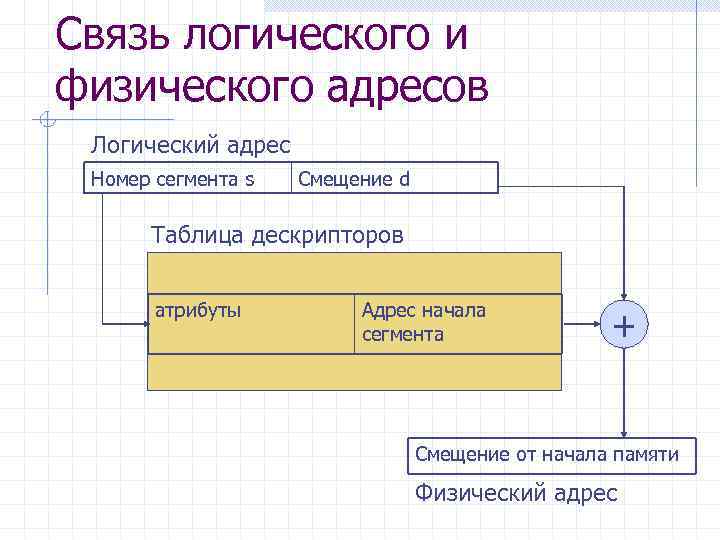

Связь логического и физического адресов Логический адрес Номер сегмента s Смещение d Таблица дескрипторов атрибуты Адрес начала сегмента + Смещение от начала памяти Физический адрес

Связь логического и физического адресов Логический адрес Номер сегмента s Смещение d Таблица дескрипторов атрибуты Адрес начала сегмента + Смещение от начала памяти Физический адрес

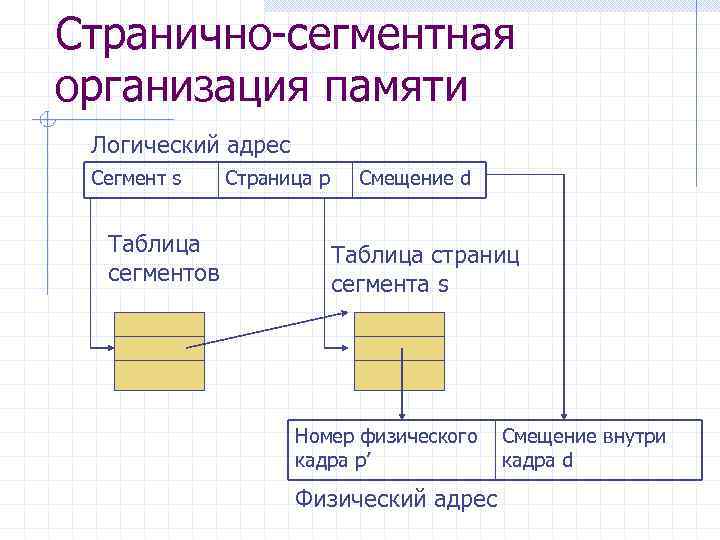

Странично-сегментная организация памяти Логический адрес Сегмент s Таблица сегментов Страница p Смещение d Таблица страниц cегмента s Номер физического кадра p’ Физический адрес Смещение внутри кадра d

Странично-сегментная организация памяти Логический адрес Сегмент s Таблица сегментов Страница p Смещение d Таблица страниц cегмента s Номер физического кадра p’ Физический адрес Смещение внутри кадра d

Виртуальная память Память процесса разбивается на части (например страницы) Выполняется динамическая трансляция логического адреса в физический При отсутствии страницы в ОЗУ она догружается (подкачивается) с жесткого диска.

Виртуальная память Память процесса разбивается на части (например страницы) Выполняется динамическая трансляция логического адреса в физический При отсутствии страницы в ОЗУ она догружается (подкачивается) с жесткого диска.

Виртуальная память Программа не ограничена объемом ОЗУ и имеет доступ к всему адресному пространству CPU Возможно частое и гибкое перемещение процессов в памяти, что позволяет разместить больше процессов Объем ввода-вывода меньше, чем в свопинге Обеспечивается контроль доступа к памяти и защита адресных пространств процессов

Виртуальная память Программа не ограничена объемом ОЗУ и имеет доступ к всему адресному пространству CPU Возможно частое и гибкое перемещение процессов в памяти, что позволяет разместить больше процессов Объем ввода-вывода меньше, чем в свопинге Обеспечивается контроль доступа к памяти и защита адресных пространств процессов

Структура таблицы страниц Структура адреса: (p, d) где p – номер виртуальной страницы, d – смещение Запись таблицы страниц: n n n номер физического кадра бит присутствия биты защиты бит модификации …

Структура таблицы страниц Структура адреса: (p, d) где p – номер виртуальной страницы, d – смещение Запись таблицы страниц: n n n номер физического кадра бит присутствия биты защиты бит модификации …

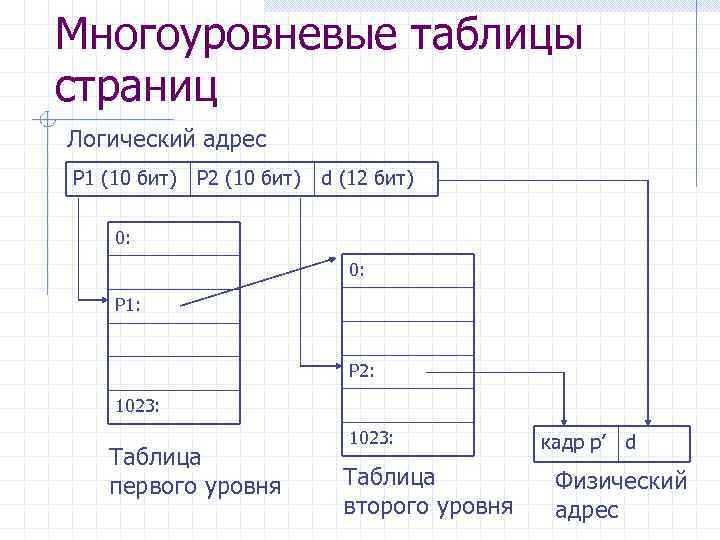

Многоуровневые таблицы страниц Логический адрес P 1 (10 бит) P 2 (10 бит) d (12 бит) 0: 0: P 1: P 2: 1023: Таблица первого уровня 1023: Таблица второго уровня кадр p’ d Физический адрес

Многоуровневые таблицы страниц Логический адрес P 1 (10 бит) P 2 (10 бит) d (12 бит) 0: 0: P 1: P 2: 1023: Таблица первого уровня 1023: Таблица второго уровня кадр p’ d Физический адрес

Translation Lookaside Buffer (TLB) Номер страницы атрибуты Номер физического кадра ? = Номер страницы ? =

Translation Lookaside Buffer (TLB) Номер страницы атрибуты Номер физического кадра ? = Номер страницы ? =

Инвертированная таблица страниц Записи соответствуют физическим кадрам Достаточно одной таблицы на все процессы Усложнён поиск необходимой записи – можно применить хеширование

Инвертированная таблица страниц Записи соответствуют физическим кадрам Достаточно одной таблицы на все процессы Усложнён поиск необходимой записи – можно применить хеширование