9dc10826c3ddbe4bff3a8530c846211c.ppt

- Количество слайдов: 24

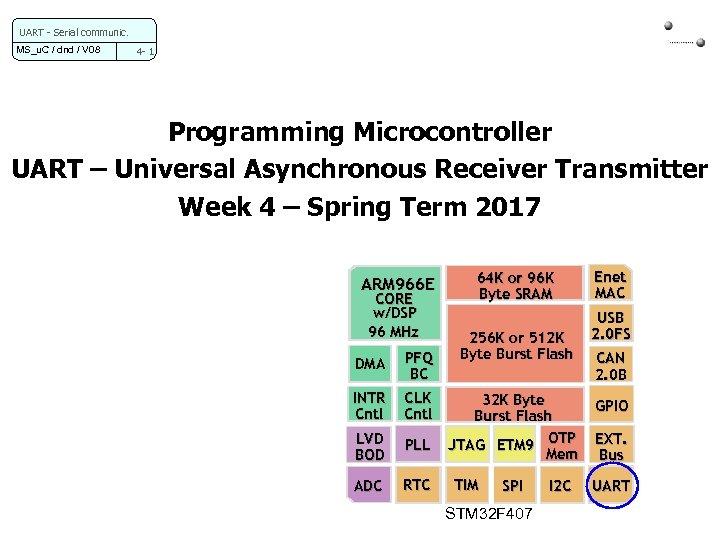

UART - Serial communic. MS_u. C / dnd / V 08 4 - 1 Programming Microcontroller UART – Universal Asynchronous Receiver Transmitter Week 4 – Spring Term 2017 ARM 966 E CORE w/DSP 96 MHz DMA PFQ BC INTR Cntl CLK Cntl LVD BOD PLL ADC RTC 64 K or 96 K Byte SRAM 256 K or 512 K Byte Burst Flash 32 K Byte Burst Flash JTAG ETM 9 OTP Mem TIM SPI STM 32 F 407 I 2 C Enet MAC USB 2. 0 FS CAN 2. 0 B GPIO EXT. Bus UART

UART - Serial communic. MS_u. C / dnd / V 08 4 - 1 Programming Microcontroller UART – Universal Asynchronous Receiver Transmitter Week 4 – Spring Term 2017 ARM 966 E CORE w/DSP 96 MHz DMA PFQ BC INTR Cntl CLK Cntl LVD BOD PLL ADC RTC 64 K or 96 K Byte SRAM 256 K or 512 K Byte Burst Flash 32 K Byte Burst Flash JTAG ETM 9 OTP Mem TIM SPI STM 32 F 407 I 2 C Enet MAC USB 2. 0 FS CAN 2. 0 B GPIO EXT. Bus UART

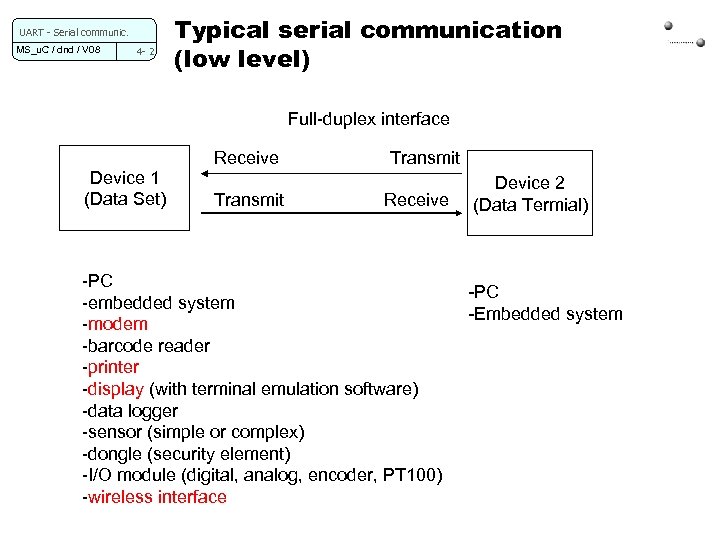

UART - Serial communic. MS_u. C / dnd / V 08 4 - 2 Typical serial communication (low level) Full-duplex interface Device 1 (Data Set) Receive Transmit Receive -PC -embedded system -modem -barcode reader -printer -display (with terminal emulation software) -data logger -sensor (simple or complex) -dongle (security element) -I/O module (digital, analog, encoder, PT 100) -wireless interface Device 2 (Data Termial) -PC -Embedded system

UART - Serial communic. MS_u. C / dnd / V 08 4 - 2 Typical serial communication (low level) Full-duplex interface Device 1 (Data Set) Receive Transmit Receive -PC -embedded system -modem -barcode reader -printer -display (with terminal emulation software) -data logger -sensor (simple or complex) -dongle (security element) -I/O module (digital, analog, encoder, PT 100) -wireless interface Device 2 (Data Termial) -PC -Embedded system

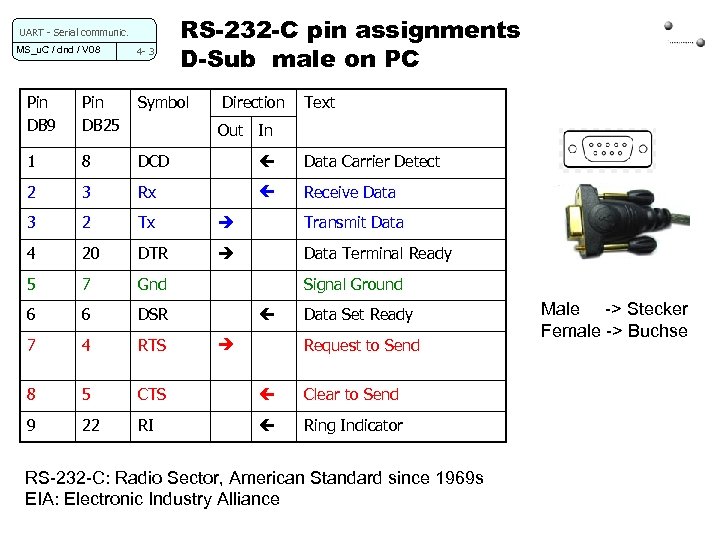

UART - Serial communic. MS_u. C / dnd / V 08 4 - 3 RS-232 -C pin assignments D-Sub male on PC Pin DB 9 Pin DB 25 Symbol Direction Text 1 8 DCD Data Carrier Detect 2 3 Rx Receive Data 3 2 Tx Transmit Data 4 20 DTR Data Terminal Ready 5 7 Gnd 6 6 DSR 7 4 RTS 8 5 CTS Clear to Send 9 22 RI Ring Indicator Out In Signal Ground Data Set Ready Request to Send RS-232 -C: Radio Sector, American Standard since 1969 s EIA: Electronic Industry Alliance Male -> Stecker Female -> Buchse

UART - Serial communic. MS_u. C / dnd / V 08 4 - 3 RS-232 -C pin assignments D-Sub male on PC Pin DB 9 Pin DB 25 Symbol Direction Text 1 8 DCD Data Carrier Detect 2 3 Rx Receive Data 3 2 Tx Transmit Data 4 20 DTR Data Terminal Ready 5 7 Gnd 6 6 DSR 7 4 RTS 8 5 CTS Clear to Send 9 22 RI Ring Indicator Out In Signal Ground Data Set Ready Request to Send RS-232 -C: Radio Sector, American Standard since 1969 s EIA: Electronic Industry Alliance Male -> Stecker Female -> Buchse

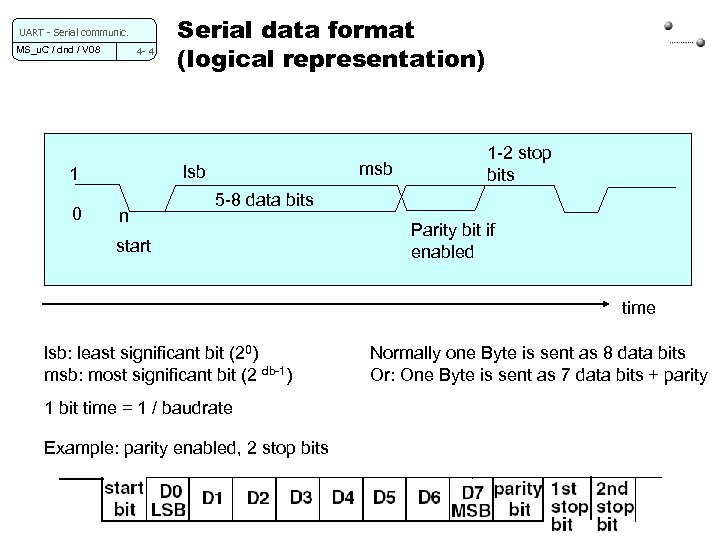

UART - Serial communic. MS_u. C / dnd / V 08 4 - 4 msb lsb 1 0 Serial data format (logical representation) n 1 -2 stop bits 5 -8 data bits start Parity bit if enabled time lsb: least significant bit (20) msb: most significant bit (2 db-1) 1 bit time = 1 / baudrate Example: parity enabled, 2 stop bits Normally one Byte is sent as 8 data bits Or: One Byte is sent as 7 data bits + parity

UART - Serial communic. MS_u. C / dnd / V 08 4 - 4 msb lsb 1 0 Serial data format (logical representation) n 1 -2 stop bits 5 -8 data bits start Parity bit if enabled time lsb: least significant bit (20) msb: most significant bit (2 db-1) 1 bit time = 1 / baudrate Example: parity enabled, 2 stop bits Normally one Byte is sent as 8 data bits Or: One Byte is sent as 7 data bits + parity

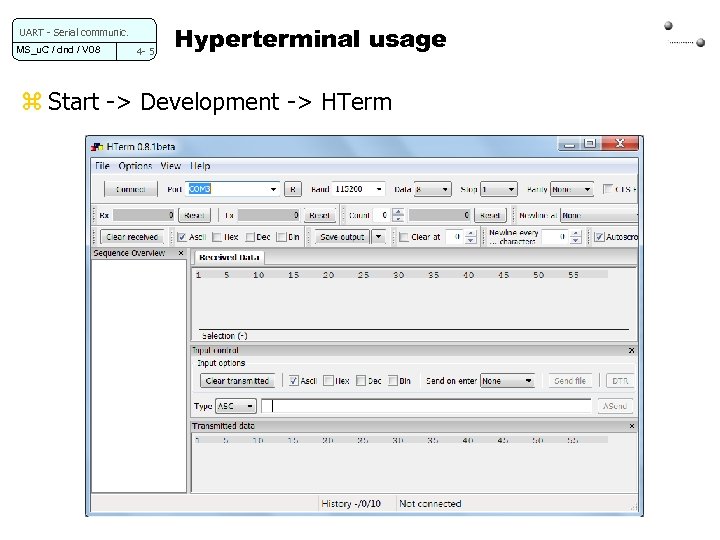

UART - Serial communic. MS_u. C / dnd / V 08 4 - 5 Hyperterminal usage z Start -> Development -> HTerm

UART - Serial communic. MS_u. C / dnd / V 08 4 - 5 Hyperterminal usage z Start -> Development -> HTerm

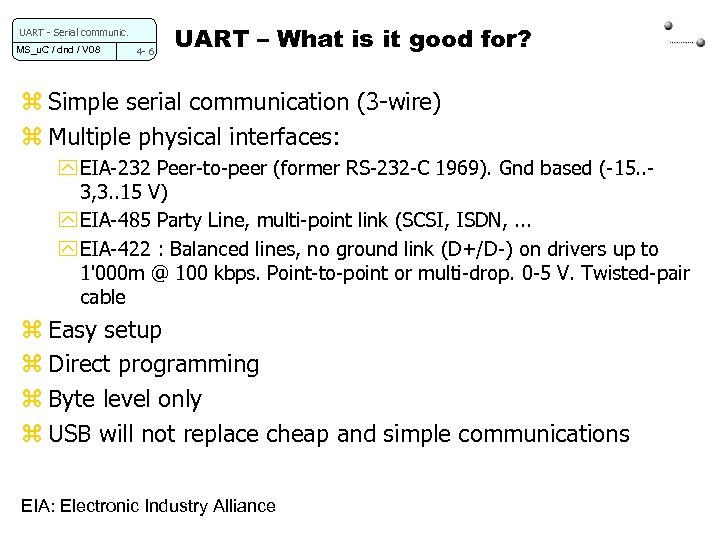

UART - Serial communic. MS_u. C / dnd / V 08 4 - 6 UART – What is it good for? z Simple serial communication (3 -wire) z Multiple physical interfaces: y EIA-232 Peer-to-peer (former RS-232 -C 1969). Gnd based (-15. . 3, 3. . 15 V) y EIA-485 Party Line, multi-point link (SCSI, ISDN, . . . y EIA-422 : Balanced lines, no ground link (D+/D-) on drivers up to 1'000 m @ 100 kbps. Point-to-point or multi-drop. 0 -5 V. Twisted-pair cable z Easy setup z Direct programming z Byte level only z USB will not replace cheap and simple communications EIA: Electronic Industry Alliance

UART - Serial communic. MS_u. C / dnd / V 08 4 - 6 UART – What is it good for? z Simple serial communication (3 -wire) z Multiple physical interfaces: y EIA-232 Peer-to-peer (former RS-232 -C 1969). Gnd based (-15. . 3, 3. . 15 V) y EIA-485 Party Line, multi-point link (SCSI, ISDN, . . . y EIA-422 : Balanced lines, no ground link (D+/D-) on drivers up to 1'000 m @ 100 kbps. Point-to-point or multi-drop. 0 -5 V. Twisted-pair cable z Easy setup z Direct programming z Byte level only z USB will not replace cheap and simple communications EIA: Electronic Industry Alliance

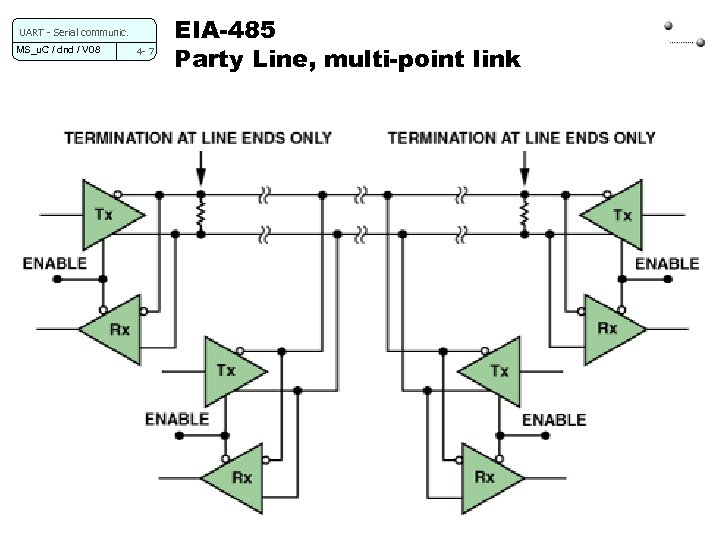

UART - Serial communic. MS_u. C / dnd / V 08 4 - 7 EIA-485 Party Line, multi-point link

UART - Serial communic. MS_u. C / dnd / V 08 4 - 7 EIA-485 Party Line, multi-point link

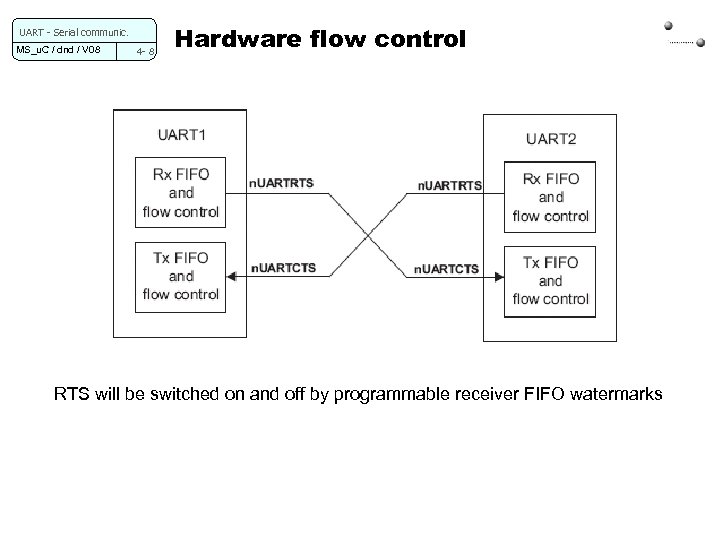

UART - Serial communic. MS_u. C / dnd / V 08 4 - 8 Hardware flow control RTS will be switched on and off by programmable receiver FIFO watermarks

UART - Serial communic. MS_u. C / dnd / V 08 4 - 8 Hardware flow control RTS will be switched on and off by programmable receiver FIFO watermarks

UART - Serial communic. MS_u. C / dnd / V 08 4 - 9 UART features (1/3) z Full duplex, asynchronous communications z NRZ standard format (Mark/Space) z Configurable oversampling method by 16 or by 8 to give flexibility between speed and clock tolerance z Fractional baud rate generator systems y Common programmable transmit and receive baud rate (refer to the datasheets for the value of the baud rate at the maximum APB frequency z z Programmable data word length (8 or 9 bits) Configurable stop bits - support for 1 or 2 stop bits Transmitter clock output for synchronous transmission Ir. DA SIR encoder decoder y Support for 3/16 bit duration for normal mode

UART - Serial communic. MS_u. C / dnd / V 08 4 - 9 UART features (1/3) z Full duplex, asynchronous communications z NRZ standard format (Mark/Space) z Configurable oversampling method by 16 or by 8 to give flexibility between speed and clock tolerance z Fractional baud rate generator systems y Common programmable transmit and receive baud rate (refer to the datasheets for the value of the baud rate at the maximum APB frequency z z Programmable data word length (8 or 9 bits) Configurable stop bits - support for 1 or 2 stop bits Transmitter clock output for synchronous transmission Ir. DA SIR encoder decoder y Support for 3/16 bit duration for normal mode

UART - Serial communic. MS_u. C / dnd / V 08 4 - 10 USART features (2/3) z Smartcard emulation capability y The Smartcard interface supports the asynchronous protocol Smartcards as defined in the ISO 7816 -3 standards y 0. 5, 1. 5 stop bits for Smartcard operation z Single-wire half-duplex communication z Configurable multi buffer communication using DMA (direct memory access) y Buffering of received/transmitted bytes in reserved SRAM using centralized DMA z Separate enable bits for transmitter and receiver z Transfer detection flags y Receive buffer full y Transmit buffer empty y End of transmission flags

UART - Serial communic. MS_u. C / dnd / V 08 4 - 10 USART features (2/3) z Smartcard emulation capability y The Smartcard interface supports the asynchronous protocol Smartcards as defined in the ISO 7816 -3 standards y 0. 5, 1. 5 stop bits for Smartcard operation z Single-wire half-duplex communication z Configurable multi buffer communication using DMA (direct memory access) y Buffering of received/transmitted bytes in reserved SRAM using centralized DMA z Separate enable bits for transmitter and receiver z Transfer detection flags y Receive buffer full y Transmit buffer empty y End of transmission flags

UART - Serial communic. MS_u. C / dnd / V 08 4 - 11 USART features (3/3) z Parity control y Transmits parity bit y Checks parity of received data byte z Four error detection flags y Overrun error y Noise detection y Frame error y Parity error z Ten interrupt sources with flags z Multiprocessor communication - enter into mute mode if address match does not occur z Wake up from mute mode (by idle line detection or address mark detection) z Two receiver wakeup modes: Address bit (MSB, 9 th bit), Idle line

UART - Serial communic. MS_u. C / dnd / V 08 4 - 11 USART features (3/3) z Parity control y Transmits parity bit y Checks parity of received data byte z Four error detection flags y Overrun error y Noise detection y Frame error y Parity error z Ten interrupt sources with flags z Multiprocessor communication - enter into mute mode if address match does not occur z Wake up from mute mode (by idle line detection or address mark detection) z Two receiver wakeup modes: Address bit (MSB, 9 th bit), Idle line

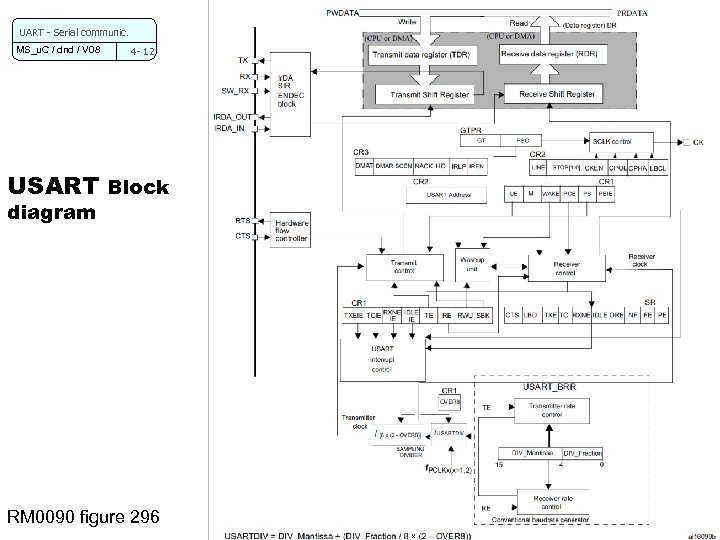

UART - Serial communic. MS_u. C / dnd / V 08 4 - 12 USART Block diagram RM 0090 figure 296

UART - Serial communic. MS_u. C / dnd / V 08 4 - 12 USART Block diagram RM 0090 figure 296

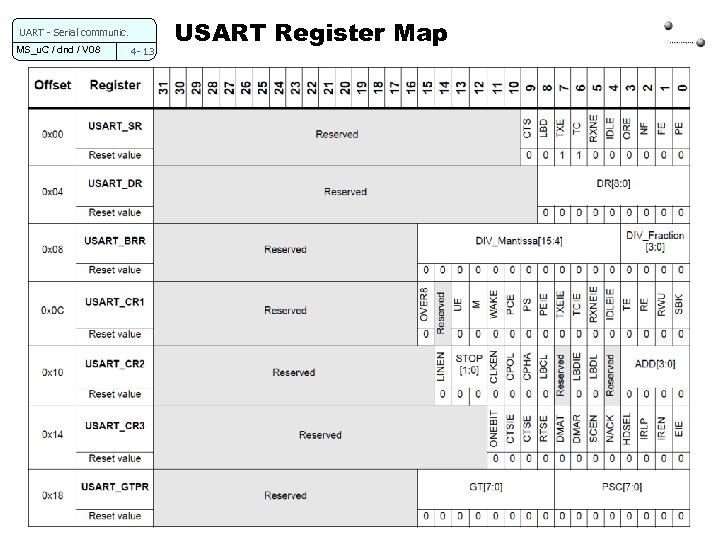

UART - Serial communic. MS_u. C / dnd / V 08 4 - 13 USART Register Map

UART - Serial communic. MS_u. C / dnd / V 08 4 - 13 USART Register Map

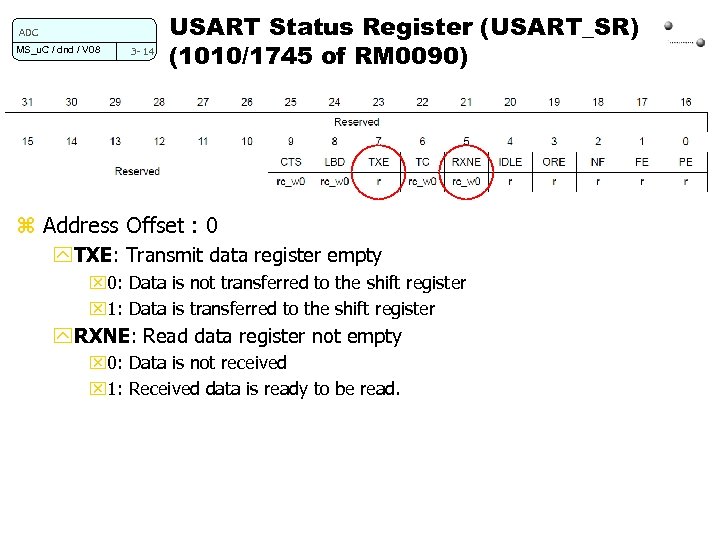

ADC MS_u. C / dnd / V 08 3 - 14 USART Status Register (USART_SR) (1010/1745 of RM 0090) z Address Offset : 0 y TXE: Transmit data register empty x 0: Data is not transferred to the shift register x 1: Data is transferred to the shift register y RXNE: Read data register not empty x 0: Data is not received x 1: Received data is ready to be read.

ADC MS_u. C / dnd / V 08 3 - 14 USART Status Register (USART_SR) (1010/1745 of RM 0090) z Address Offset : 0 y TXE: Transmit data register empty x 0: Data is not transferred to the shift register x 1: Data is transferred to the shift register y RXNE: Read data register not empty x 0: Data is not received x 1: Received data is ready to be read.

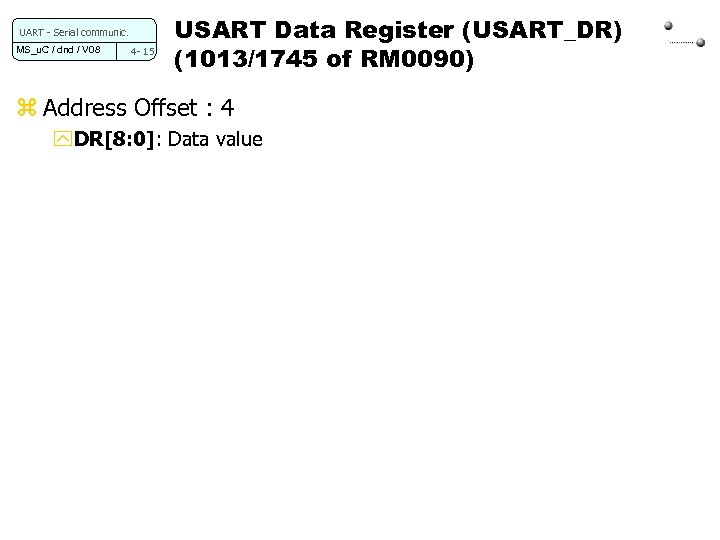

UART - Serial communic. MS_u. C / dnd / V 08 4 - 15 USART Data Register (USART_DR) (1013/1745 of RM 0090) z Address Offset : 4 y DR[8: 0]: Data value

UART - Serial communic. MS_u. C / dnd / V 08 4 - 15 USART Data Register (USART_DR) (1013/1745 of RM 0090) z Address Offset : 4 y DR[8: 0]: Data value

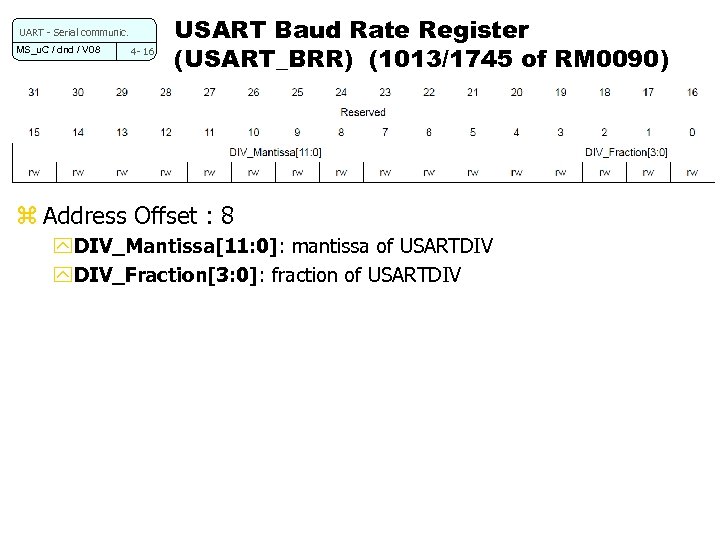

UART - Serial communic. MS_u. C / dnd / V 08 4 - 16 USART Baud Rate Register (USART_BRR) (1013/1745 of RM 0090) z Address Offset : 8 y DIV_Mantissa[11: 0]: mantissa of USARTDIV y DIV_Fraction[3: 0]: fraction of USARTDIV

UART - Serial communic. MS_u. C / dnd / V 08 4 - 16 USART Baud Rate Register (USART_BRR) (1013/1745 of RM 0090) z Address Offset : 8 y DIV_Mantissa[11: 0]: mantissa of USARTDIV y DIV_Fraction[3: 0]: fraction of USARTDIV

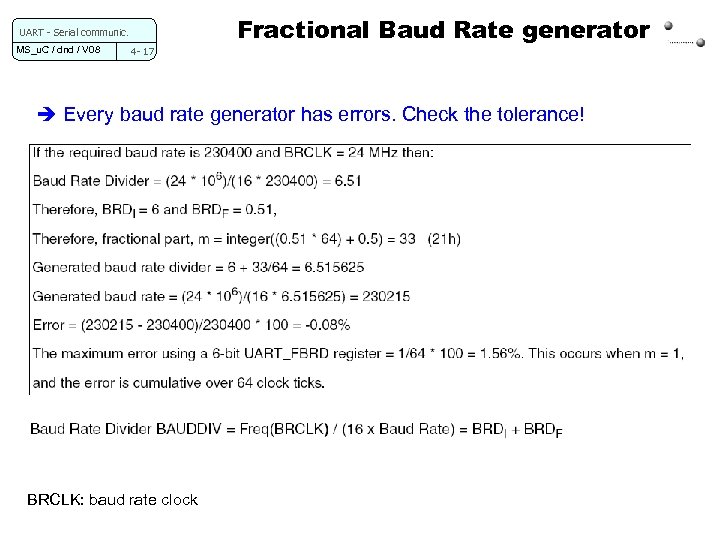

UART - Serial communic. MS_u. C / dnd / V 08 4 - 17 Fractional Baud Rate generator Every baud rate generator has errors. Check the tolerance! BRCLK: baud rate clock

UART - Serial communic. MS_u. C / dnd / V 08 4 - 17 Fractional Baud Rate generator Every baud rate generator has errors. Check the tolerance! BRCLK: baud rate clock

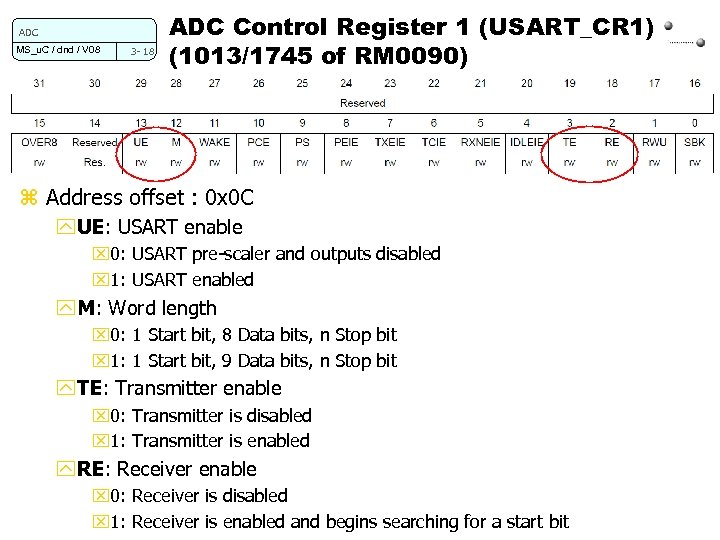

ADC MS_u. C / dnd / V 08 3 - 18 ADC Control Register 1 (USART_CR 1) (1013/1745 of RM 0090) z Address offset : 0 x 0 C y UE: USART enable x 0: USART pre-scaler and outputs disabled x 1: USART enabled y M: Word length x 0: 1 Start bit, 8 Data bits, n Stop bit x 1: 1 Start bit, 9 Data bits, n Stop bit y TE: Transmitter enable x 0: Transmitter is disabled x 1: Transmitter is enabled y RE: Receiver enable x 0: Receiver is disabled x 1: Receiver is enabled and begins searching for a start bit

ADC MS_u. C / dnd / V 08 3 - 18 ADC Control Register 1 (USART_CR 1) (1013/1745 of RM 0090) z Address offset : 0 x 0 C y UE: USART enable x 0: USART pre-scaler and outputs disabled x 1: USART enabled y M: Word length x 0: 1 Start bit, 8 Data bits, n Stop bit x 1: 1 Start bit, 9 Data bits, n Stop bit y TE: Transmitter enable x 0: Transmitter is disabled x 1: Transmitter is enabled y RE: Receiver enable x 0: Receiver is disabled x 1: Receiver is enabled and begins searching for a start bit

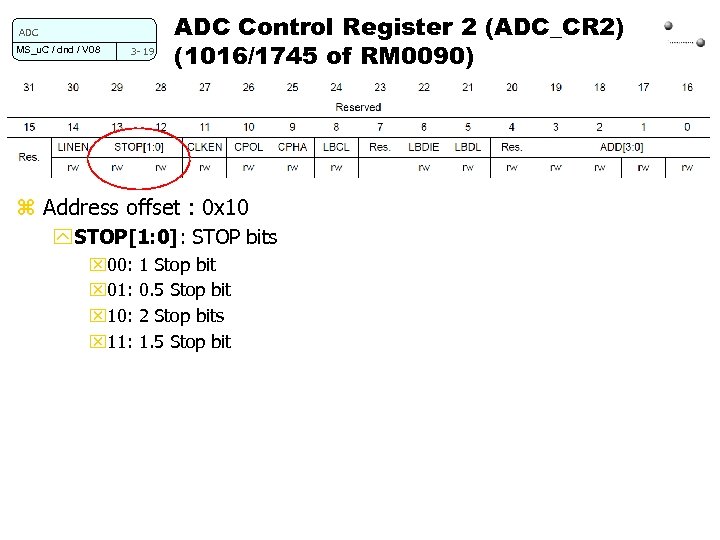

ADC MS_u. C / dnd / V 08 3 - 19 ADC Control Register 2 (ADC_CR 2) (1016/1745 of RM 0090) z Address offset : 0 x 10 y STOP[1: 0]: STOP bits x 00: x 01: x 10: x 11: 1 Stop bit 0. 5 Stop bit 2 Stop bits 1. 5 Stop bit

ADC MS_u. C / dnd / V 08 3 - 19 ADC Control Register 2 (ADC_CR 2) (1016/1745 of RM 0090) z Address offset : 0 x 10 y STOP[1: 0]: STOP bits x 00: x 01: x 10: x 11: 1 Stop bit 0. 5 Stop bit 2 Stop bits 1. 5 Stop bit

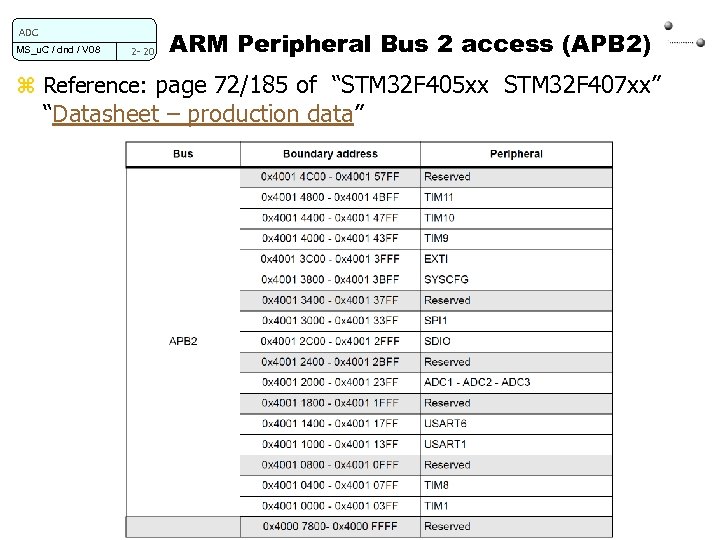

ADC MS_u. C / dnd / V 08 2 - 20 ARM Peripheral Bus 2 access (APB 2) z Reference: page 72/185 of “STM 32 F 405 xx STM 32 F 407 xx” “Datasheet – production data”

ADC MS_u. C / dnd / V 08 2 - 20 ARM Peripheral Bus 2 access (APB 2) z Reference: page 72/185 of “STM 32 F 405 xx STM 32 F 407 xx” “Datasheet – production data”

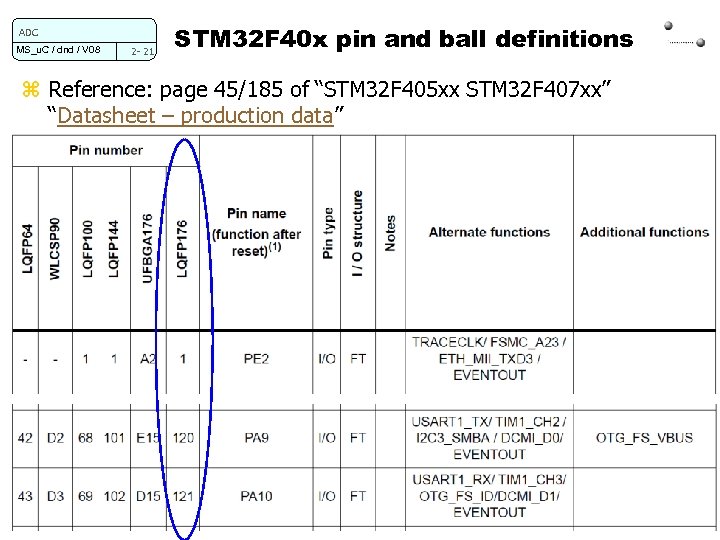

ADC MS_u. C / dnd / V 08 2 - 21 STM 32 F 40 x pin and ball definitions z Reference: page 45/185 of “STM 32 F 405 xx STM 32 F 407 xx” “Datasheet – production data”

ADC MS_u. C / dnd / V 08 2 - 21 STM 32 F 40 x pin and ball definitions z Reference: page 45/185 of “STM 32 F 405 xx STM 32 F 407 xx” “Datasheet – production data”

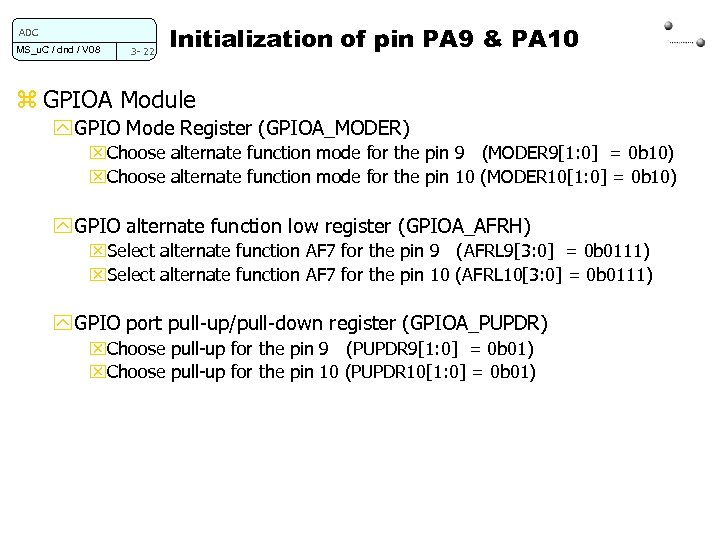

ADC MS_u. C / dnd / V 08 3 - 22 Initialization of pin PA 9 & PA 10 z GPIOA Module y GPIO Mode Register (GPIOA_MODER) x. Choose alternate function mode for the pin 9 (MODER 9[1: 0] = 0 b 10) x. Choose alternate function mode for the pin 10 (MODER 10[1: 0] = 0 b 10) y GPIO alternate function low register (GPIOA_AFRH) x. Select alternate function AF 7 for the pin 9 (AFRL 9[3: 0] = 0 b 0111) x. Select alternate function AF 7 for the pin 10 (AFRL 10[3: 0] = 0 b 0111) y GPIO port pull-up/pull-down register (GPIOA_PUPDR) x. Choose pull-up for the pin 9 (PUPDR 9[1: 0] = 0 b 01) x. Choose pull-up for the pin 10 (PUPDR 10[1: 0] = 0 b 01)

ADC MS_u. C / dnd / V 08 3 - 22 Initialization of pin PA 9 & PA 10 z GPIOA Module y GPIO Mode Register (GPIOA_MODER) x. Choose alternate function mode for the pin 9 (MODER 9[1: 0] = 0 b 10) x. Choose alternate function mode for the pin 10 (MODER 10[1: 0] = 0 b 10) y GPIO alternate function low register (GPIOA_AFRH) x. Select alternate function AF 7 for the pin 9 (AFRL 9[3: 0] = 0 b 0111) x. Select alternate function AF 7 for the pin 10 (AFRL 10[3: 0] = 0 b 0111) y GPIO port pull-up/pull-down register (GPIOA_PUPDR) x. Choose pull-up for the pin 9 (PUPDR 9[1: 0] = 0 b 01) x. Choose pull-up for the pin 10 (PUPDR 10[1: 0] = 0 b 01)

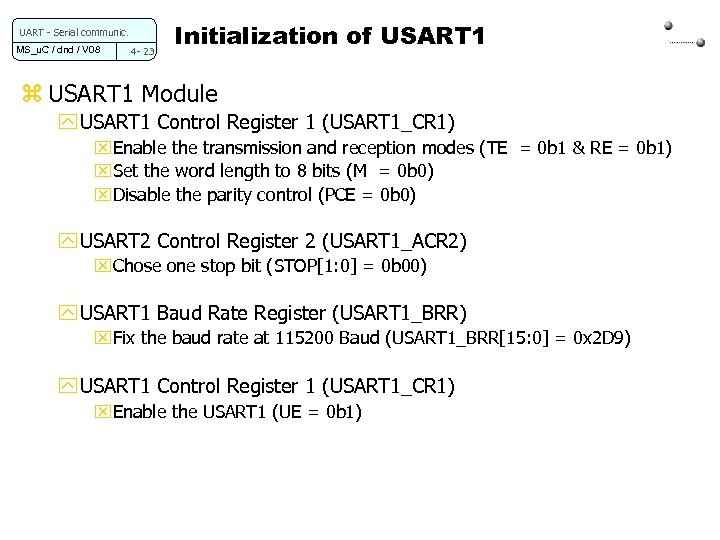

UART - Serial communic. MS_u. C / dnd / V 08 4 - 23 Initialization of USART 1 z USART 1 Module y USART 1 Control Register 1 (USART 1_CR 1) x. Enable the transmission and reception modes (TE = 0 b 1 & RE = 0 b 1) x. Set the word length to 8 bits (M = 0 b 0) x. Disable the parity control (PCE = 0 b 0) y USART 2 Control Register 2 (USART 1_ACR 2) x. Chose one stop bit (STOP[1: 0] = 0 b 00) y USART 1 Baud Rate Register (USART 1_BRR) x. Fix the baud rate at 115200 Baud (USART 1_BRR[15: 0] = 0 x 2 D 9) y USART 1 Control Register 1 (USART 1_CR 1) x. Enable the USART 1 (UE = 0 b 1)

UART - Serial communic. MS_u. C / dnd / V 08 4 - 23 Initialization of USART 1 z USART 1 Module y USART 1 Control Register 1 (USART 1_CR 1) x. Enable the transmission and reception modes (TE = 0 b 1 & RE = 0 b 1) x. Set the word length to 8 bits (M = 0 b 0) x. Disable the parity control (PCE = 0 b 0) y USART 2 Control Register 2 (USART 1_ACR 2) x. Chose one stop bit (STOP[1: 0] = 0 b 00) y USART 1 Baud Rate Register (USART 1_BRR) x. Fix the baud rate at 115200 Baud (USART 1_BRR[15: 0] = 0 x 2 D 9) y USART 1 Control Register 1 (USART 1_CR 1) x. Enable the USART 1 (UE = 0 b 1)

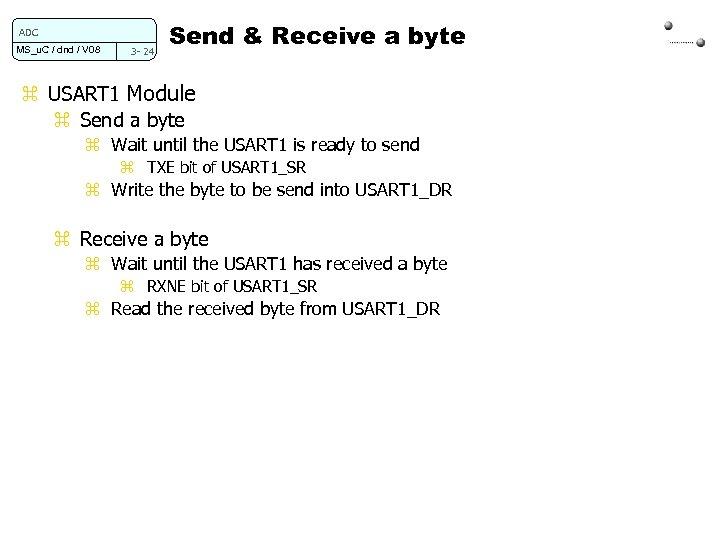

ADC MS_u. C / dnd / V 08 3 - 24 Send & Receive a byte z USART 1 Module z Send a byte z Wait until the USART 1 is ready to send z TXE bit of USART 1_SR z Write the byte to be send into USART 1_DR z Receive a byte z Wait until the USART 1 has received a byte z RXNE bit of USART 1_SR z Read the received byte from USART 1_DR

ADC MS_u. C / dnd / V 08 3 - 24 Send & Receive a byte z USART 1 Module z Send a byte z Wait until the USART 1 is ready to send z TXE bit of USART 1_SR z Write the byte to be send into USART 1_DR z Receive a byte z Wait until the USART 1 has received a byte z RXNE bit of USART 1_SR z Read the received byte from USART 1_DR