5.Базовые основы памяти.ppt

- Количество слайдов: 17

Триггеры (Базовые основы памяти) Микросхемы и принципы работы

Память является необходимым компонентом любого компьютера. Без памяти не было бы компьютеров, по крайней мере таких, какие есть сейчас. Память используется для хранения как команд, так и данных. Сегодня мы рассмотрим основы создания памяти, начиная с уровня вентилей. Мы увидим, как они работают, как из них можно построить память большей емкости. Не конспектировать!

Триггеры, или защёлки Чтобы иметь один бит памяти, нужна схема, которая каким-то образом «запоминает» предыдущие входные значения. Такую схему можно сконструировать из двух вентилей НЕИЛИ. Аналогичные схемы можно построить и из вентилей НЕ-И. Мы не будем их рассматривать, поскольку они идентичны схемам с вентилями НЕ-ИЛИ

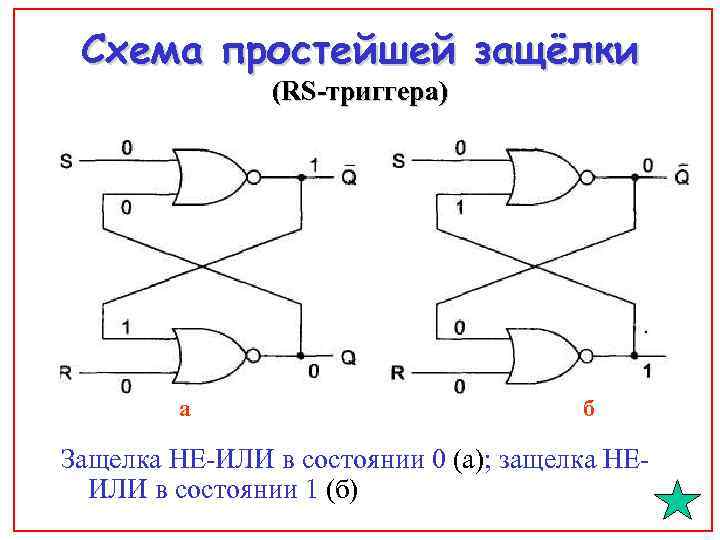

Схема простейшей защёлки (RS-триггера) а б Защелка НЕ-ИЛИ в состоянии 0 (а); защелка НЕИЛИ в состоянии 1 (б)

А В НЕИЛИ 0 0 1 0 1 0 0 1 1 0 Таблица истинности для функции НЕ-ИЛИ

Некоторое объяснение… 1. Триггер = переводится с английского как защёлка 2. У простейшей защёлки есть два входа: S (Setting — установка) и R (Resetting — сброс). У нее также есть два выхода: Q и инвертированное Q. 3. В отличие от комбинаторной схемы, выходные сигналы защелки не определяются текущими входными сигналами. 4. Чтобы понять, как работает защелка, предположим, что S = 0 и R = 0 (вообще сигнал на этих входах равен 0 большую часть времени). Предположим также, что Q = 0. Так как Q возвращается в верхний вентиль НЕ-ИЛИ и оба входа этого вентиля равны 0, то его выход, инвертированное Q, равен 1. Единица возвращается в нижний вентиль, у которого один вход = 0, а другой = 1. На выходе получается Q = 0.

Продолжение объяснения… 5. А теперь давайте представим, что Q = 1, a R и S все еще равны 0. Верхний вентиль имеет входы 0 и 1 и выход Q (то есть 0), который возвращается в нижний вентиль. 6. Могут ли оба выхода = 0 ? Нет, так как в этом случае оба вентиля имели бы на входе два 0, что привело бы к единице на выходе, а не к нулю. 7. Точно так же невозможно иметь оба выхода = 1, поскольку это привело бы к входным сигналам 0 и 1, что вызовет на выходе 0, а не 1. В итоге: при R = S = 0 защелка имеет два устойчивых состояния, которые мы будем называть 0 и 1 в зависимости от Q.

Действие входных сигналов на состояние защелки Предположим, что S принимает значение 1, в то время как Q = 0. Тогда входные сигналы верхнего вентиля равны 1 и 0, что ведет к выходному сигналу инвертированному Q=0. Это изменение делает оба входа в нижний вентиль равными 0, и, следовательно, выходной сигнал равняется 1. Таким образом, установка S = 1 переключает состояние с 0 на 1. Установка R = 1, когда защелка находится в состоянии 0, не вызывает изменений, поскольку выход нижнего вентиля НЕ-ИЛИ равен 0 как для входов 10, так и для входов 11. Очевидно, что установка S = 1 при состоянии защелки 1 (то есть при Q= 1) не вызывает изменений, но установка R в значение 1 приводит к изменению состояния защелки. Таким образом, если S = 1, то Q = 1 независимо от предыдущего состояния защелки. Сходным образом переход R в значение 1 вызывает Q = 0. Схема «запоминает» , какой сигнал был последним: S или R. Используя это свойство, мы можем строить компьютерную память.

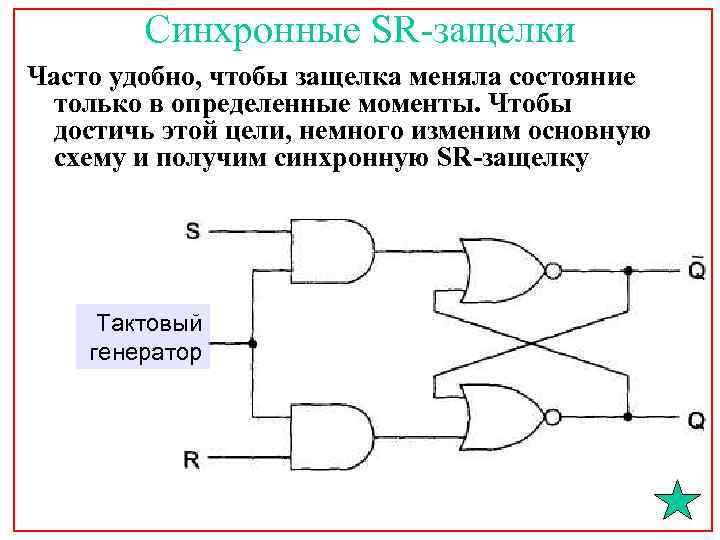

Синхронные SR-защелки Часто удобно, чтобы защелка меняла состояние только в определенные моменты. Чтобы достичь этой цели, немного изменим основную схему и получим синхронную SR-защелку Тактовый генератор

Синхронные SR-защелки • Пока синхронизирующий вход =0, такая защелка не меняет своего состояния. • Как только тактовый генератор подаёт импульс, т. е. вход=1, значения R и S изменяют состояние защелки. • Тем не менее продолжает сохраняться неопределенность состояния, когда R и S =1. В этом случае состояние выходов не определено, и значение защелки может быть как =0, так и =1.

JK-триггеры. • Для того, чтобы защелки не имели неопределенного состояния, следует не допускать R и S =1. • Достигается усложнением схемы. Такие схемы и называются JK-триггеры. • При подаче R и S =1 схема осуществляет переброс состояния (например, из 1 в 0 и наоборот)

Синхронные D-защелки • Для того, чтобы защелки не имели неопределенного состояния, можно просто использовать только один вход. • Единственный входной сигнал инвертируется и подается на микросхему. Поэтому R и S никогда не будут одновременно =1.

Синхронные D-защелки Когда вход синхронизации = 1, текущее значение D отбирается и сохраняется в защелке. Такая схема, которая называется синхронной dзащелкой, представляет собой память объемом 1 бит. Чтобы загрузить в память текущее значение D, нужно пустить положительный импульс по линии синхронизирующего сигнала

Синхронные D-защелки • Схема, рассмотренная нами, требует 11 транзисторов. • Более сложные схемы (именно они обычно используются на практике) могут хранить 1 бит всего на 6 транзисторах • Для получения 8 -ми битной схемы такие защёлки должны объединяться в блоки по 8 штук. • Реальные микросхемы памяти имеют более сложную структуру, чем рассмотренная нами.

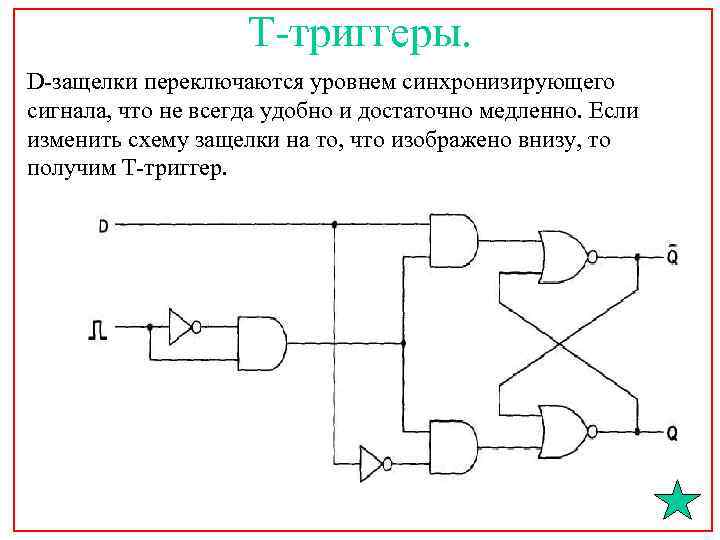

Т-триггеры. D-защелки переключаются уровнем синхронизирующего сигнала, что не всегда удобно и достаточно медленно. Если изменить схему защелки на то, что изображено внизу, то получим Т-триггер.

Т-триггеры. • Т-триггер запускается не уровнем синхронизирующего сигнала, а перепадом сигнала. • Очень короткая временная задержка при прохождении сигнала через инвертор приводит к появлению короткого импульса на выходе вентиля И • Такой импульс и переключает микросхему в другое устойчивое состояние (т. е. происходит переброс состояния микросхемы). • Т-триггеры имеют разнообразное применение, но чаще всего это – кэш-память.

5.Базовые основы памяти.ppt