0001f196495c325a3ac6f062b0f97ad6.ppt

- Количество слайдов: 67

TOPIC 6 INPUT/OUTPUT AND INTERFACING

TOPIC 6 INPUT/OUTPUT AND INTERFACING

6. 1 Input/output Operation Content n Definition n Data Transfering Technique n Direct transfer n Interrupt n Direct Memory Access (DMA). n I/O mechanisms (Handshaking)

6. 1 Input/output Operation Content n Definition n Data Transfering Technique n Direct transfer n Interrupt n Direct Memory Access (DMA). n I/O mechanisms (Handshaking)

6. 1. 1 n n Definition In computing, input/output(I/O), refers to the communication between an information processing system (such as a computer), and the outside world possibly a human, or another information processing system. Inputs are the signals or data received by the system, and Output are the signals or data sent from the system. Examples of I/O devices: Input devices - Keyboard, mouse Output Devices - video screen, printer and etc.

6. 1. 1 n n Definition In computing, input/output(I/O), refers to the communication between an information processing system (such as a computer), and the outside world possibly a human, or another information processing system. Inputs are the signals or data received by the system, and Output are the signals or data sent from the system. Examples of I/O devices: Input devices - Keyboard, mouse Output Devices - video screen, printer and etc.

6. 1. 2 Data Transfering Technique Three technique are possible for I/O operations: n Direct Transfer n Interrupt n Direct Memory Access

6. 1. 2 Data Transfering Technique Three technique are possible for I/O operations: n Direct Transfer n Interrupt n Direct Memory Access

6. 1. 2. 1 Direct Transfer n n Also known as Programmed I/O. With Programmed I/O , data are exchange between the CPU and I/O module. The CPU executes a program that gives it direct control of the I/O operation. When the CPU executes an instruction relating to the I/O, it issues a command to the appropriate I/O module. The CPU periodically check the status of the I/O module until it finds the I/O operation is complete.

6. 1. 2. 1 Direct Transfer n n Also known as Programmed I/O. With Programmed I/O , data are exchange between the CPU and I/O module. The CPU executes a program that gives it direct control of the I/O operation. When the CPU executes an instruction relating to the I/O, it issues a command to the appropriate I/O module. The CPU periodically check the status of the I/O module until it finds the I/O operation is complete.

… cont’d n Programmed I/O takes place when an instruction in the program performs the data transfer; for example: MOVE. B Keyboard, D 0 - to read a byte of data from the keyboard and puts it in D 0. Some microprocessors have special instructions that are used only for I/O; for example: OUT 50 n

… cont’d n Programmed I/O takes place when an instruction in the program performs the data transfer; for example: MOVE. B Keyboard, D 0 - to read a byte of data from the keyboard and puts it in D 0. Some microprocessors have special instructions that are used only for I/O; for example: OUT 50 n

6. 1. 2. 2 Interrupt n n A computer executes instructions sequentially unless a jump or a branch is made. An interrupt is a process or a signal that stops a microprocessor/microcontroller from what it is doing so that something else can happen. In other words an interrupt is defined as a break in the normal flow of operation of a computer caused by an interrupt signal. An interrupt may be a signal from a peripheral (i. e. , a hardware interrupt) or an internally-generated call to the operating system (i. e. , a software interrupt).

6. 1. 2. 2 Interrupt n n A computer executes instructions sequentially unless a jump or a branch is made. An interrupt is a process or a signal that stops a microprocessor/microcontroller from what it is doing so that something else can happen. In other words an interrupt is defined as a break in the normal flow of operation of a computer caused by an interrupt signal. An interrupt may be a signal from a peripheral (i. e. , a hardware interrupt) or an internally-generated call to the operating system (i. e. , a software interrupt).

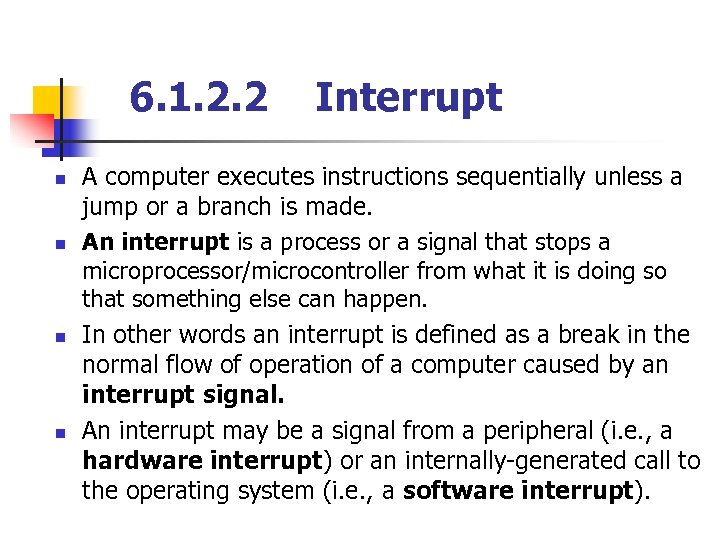

Interrupt Sequence When CPU receives an interrupt signal, it takes a specified action. Interrupt signals can cause a program to suspend itself temporarily to service the interrupt. When the interrupt has been addressed or processed, the computer’s attention can be returned to the process or program it was executing before the interrupt with the exact same conditions prevailing.

Interrupt Sequence When CPU receives an interrupt signal, it takes a specified action. Interrupt signals can cause a program to suspend itself temporarily to service the interrupt. When the interrupt has been addressed or processed, the computer’s attention can be returned to the process or program it was executing before the interrupt with the exact same conditions prevailing.

Sources of Interrupt n n Internal fault (e. g. divide by zero, overflow) Software External hardware - maskable - non maskable RESET

Sources of Interrupt n n Internal fault (e. g. divide by zero, overflow) Software External hardware - maskable - non maskable RESET

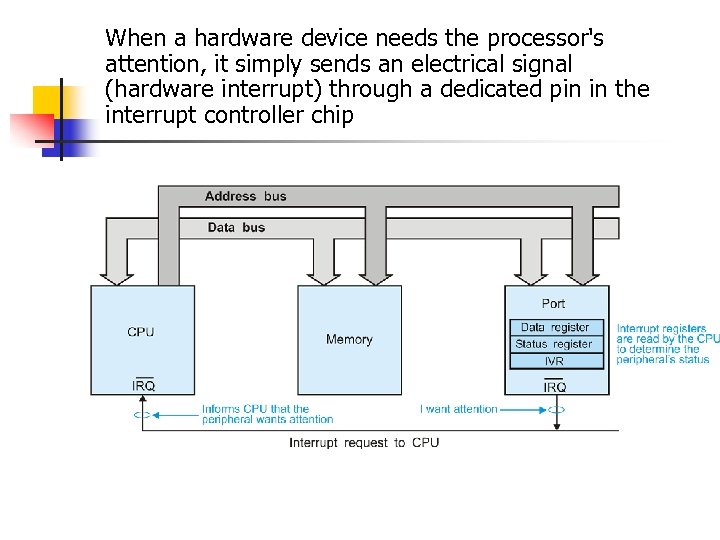

When a hardware device needs the processor's attention, it simply sends an electrical signal (hardware interrupt) through a dedicated pin in the interrupt controller chip

When a hardware device needs the processor's attention, it simply sends an electrical signal (hardware interrupt) through a dedicated pin in the interrupt controller chip

n n Hardware interrupts: every keystroke generates an interrupt signal. Interrupts can also be generated by other devices, such as a printer, to indicate that some event has occurred. Software interrupts: Interrupt signals initiated by programs. Exceptions belong to a special type of software interrupts. They are generated by the processor itself whenever some unexpected critical event occurs. Three types of exceptions: faults, traps and aborts.

n n Hardware interrupts: every keystroke generates an interrupt signal. Interrupts can also be generated by other devices, such as a printer, to indicate that some event has occurred. Software interrupts: Interrupt signals initiated by programs. Exceptions belong to a special type of software interrupts. They are generated by the processor itself whenever some unexpected critical event occurs. Three types of exceptions: faults, traps and aborts.

Interrupt categories Microcomputer interrupts fall into two basic categories: - maskable and - non-maskable. n n The CPU of the microcomputer has interrupt signal line for each category of interrupt.

Interrupt categories Microcomputer interrupts fall into two basic categories: - maskable and - non-maskable. n n The CPU of the microcomputer has interrupt signal line for each category of interrupt.

Maskable Interrupt n n External hardware interrupts are maskable interrupts. The interrupt request signal indicates the presence of one or more of these interrupts. Maskable interrupts can be masked out or locked out for short periods of time by the software to allow the CPU to perform critical operations. The programmer is responsible for ensuring that interrupts are managed in a timely manner.

Maskable Interrupt n n External hardware interrupts are maskable interrupts. The interrupt request signal indicates the presence of one or more of these interrupts. Maskable interrupts can be masked out or locked out for short periods of time by the software to allow the CPU to perform critical operations. The programmer is responsible for ensuring that interrupts are managed in a timely manner.

Non-maskable Interrupt n n Non-maskable interrupts cannot be masked out. They are used for conditions that require immediate attention by the microcomputer. Microprocessors sometimes have a special interrupt request input called a non-maskable interrupt request. Non-maskable interrupts are necessary when the interrupt is caused by a critical event that must not be missed; for example: interrupts from the internal hard disks, modems, fax cards, and sometimes out-of- tolerance condition. If this feature is available, a power out-of- tolerance condition will force the microcomputer to execute its save data program.

Non-maskable Interrupt n n Non-maskable interrupts cannot be masked out. They are used for conditions that require immediate attention by the microcomputer. Microprocessors sometimes have a special interrupt request input called a non-maskable interrupt request. Non-maskable interrupts are necessary when the interrupt is caused by a critical event that must not be missed; for example: interrupts from the internal hard disks, modems, fax cards, and sometimes out-of- tolerance condition. If this feature is available, a power out-of- tolerance condition will force the microcomputer to execute its save data program.

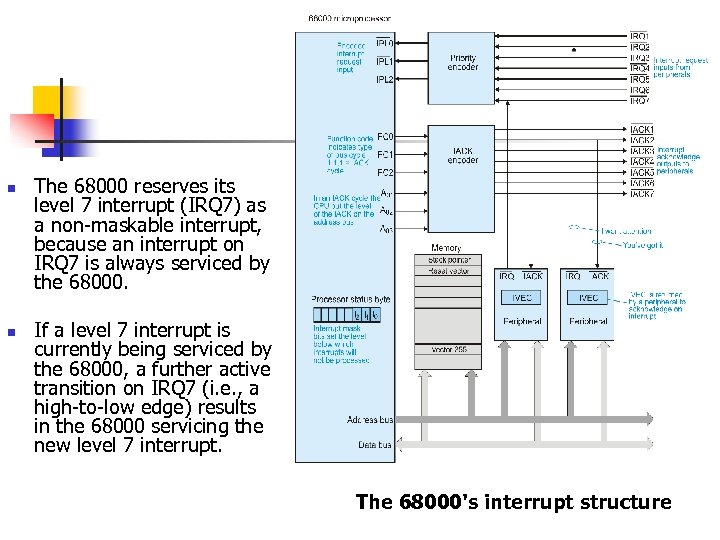

n n The 68000 reserves its level 7 interrupt (IRQ 7) as a non-maskable interrupt, because an interrupt on IRQ 7 is always serviced by the 68000. If a level 7 interrupt is currently being serviced by the 68000, a further active transition on IRQ 7 (i. e. , a high-to-low edge) results in the 68000 servicing the new level 7 interrupt. The 68000's interrupt structure

n n The 68000 reserves its level 7 interrupt (IRQ 7) as a non-maskable interrupt, because an interrupt on IRQ 7 is always serviced by the 68000. If a level 7 interrupt is currently being serviced by the 68000, a further active transition on IRQ 7 (i. e. , a high-to-low edge) results in the 68000 servicing the new level 7 interrupt. The 68000's interrupt structure

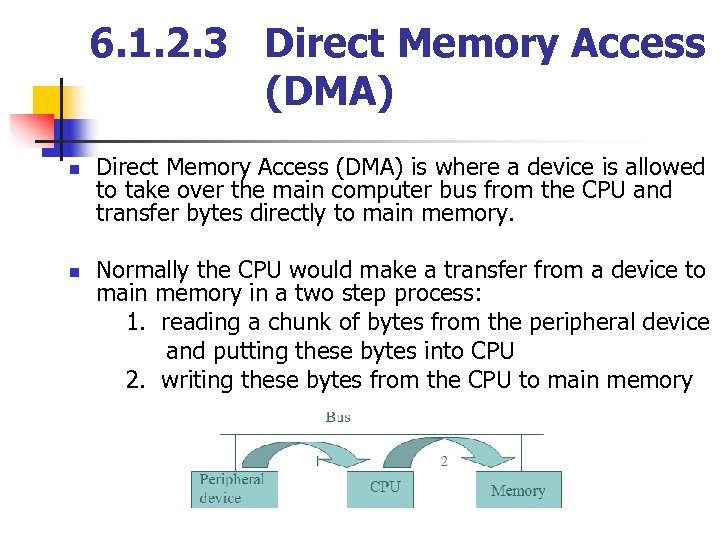

6. 1. 2. 3 Direct Memory Access (DMA) n Direct Memory Access (DMA) is where a device is allowed to take over the main computer bus from the CPU and transfer bytes directly to main memory. Normally the CPU would make a transfer from a device to main memory in a two step process: 1. reading a chunk of bytes from the peripheral device and putting these bytes into CPU 2. writing these bytes from the CPU to main memory n

6. 1. 2. 3 Direct Memory Access (DMA) n Direct Memory Access (DMA) is where a device is allowed to take over the main computer bus from the CPU and transfer bytes directly to main memory. Normally the CPU would make a transfer from a device to main memory in a two step process: 1. reading a chunk of bytes from the peripheral device and putting these bytes into CPU 2. writing these bytes from the CPU to main memory n

n With DMA it's a one step process of sending the bytes directly from the device to memory. moves data between a peripheral and the CPU's memory without the direct intervention of the CPU itself n n DMA provides the fastest possible means of transferring data between an interface and memory, as it requires no CPU overhead and leaves the CPU free to do useful work. While DMA is going on, the CPU can't do too much since the main bus is being used by the DMA transfer.

n With DMA it's a one step process of sending the bytes directly from the device to memory. moves data between a peripheral and the CPU's memory without the direct intervention of the CPU itself n n DMA provides the fastest possible means of transferring data between an interface and memory, as it requires no CPU overhead and leaves the CPU free to do useful work. While DMA is going on, the CPU can't do too much since the main bus is being used by the DMA transfer.

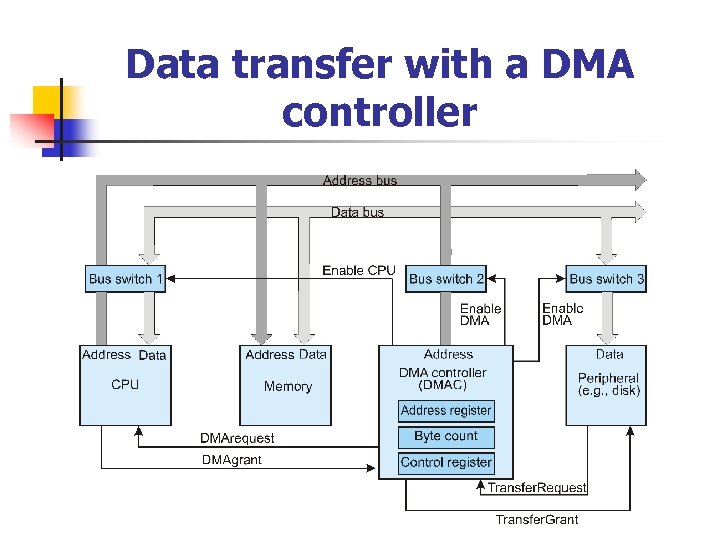

Data transfer with a DMA controller

Data transfer with a DMA controller

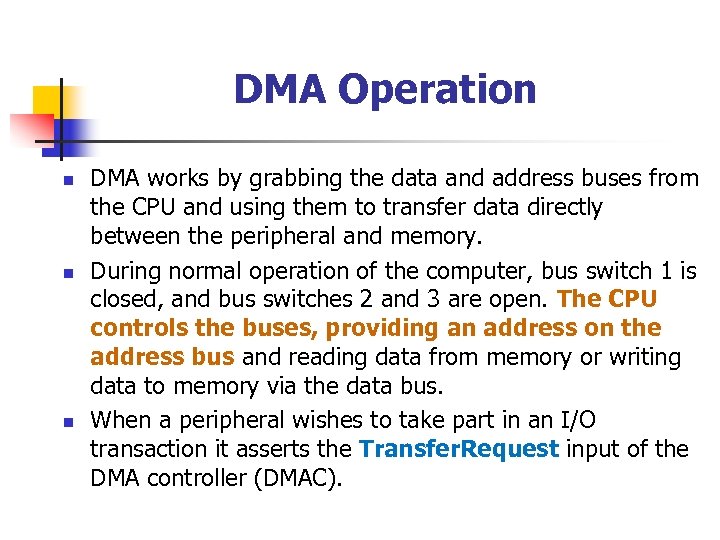

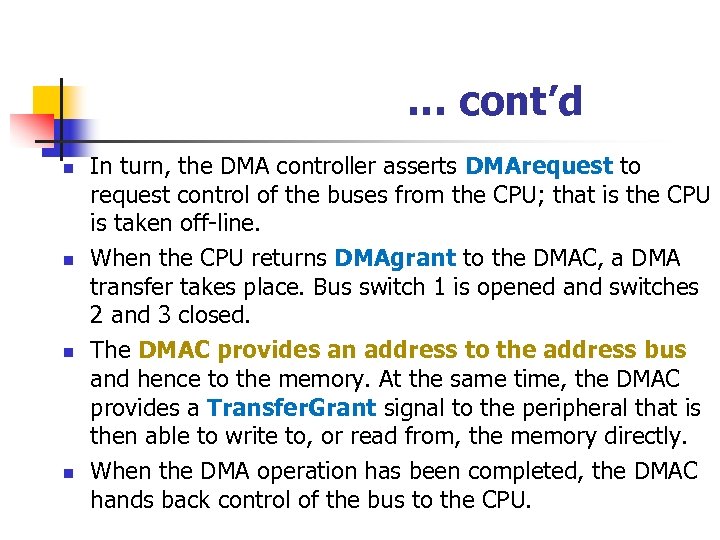

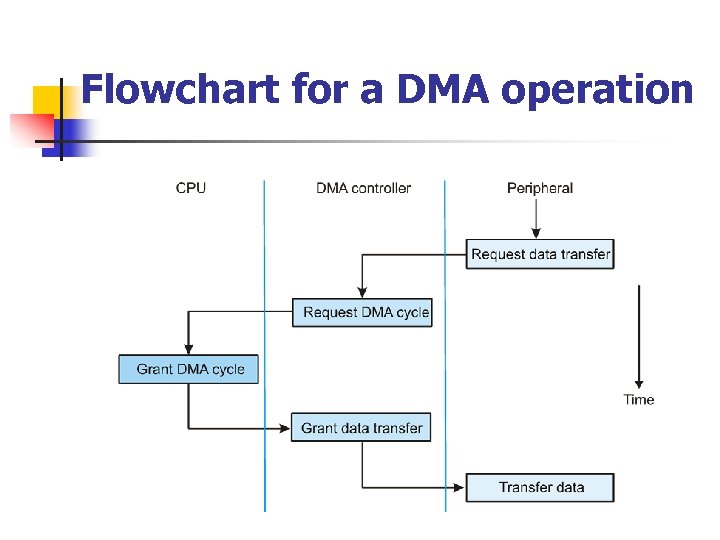

DMA Operation n DMA works by grabbing the data and address buses from the CPU and using them to transfer data directly between the peripheral and memory. During normal operation of the computer, bus switch 1 is closed, and bus switches 2 and 3 are open. The CPU controls the buses, providing an address on the address bus and reading data from memory or writing data to memory via the data bus. When a peripheral wishes to take part in an I/O transaction it asserts the Transfer. Request input of the DMA controller (DMAC).

DMA Operation n DMA works by grabbing the data and address buses from the CPU and using them to transfer data directly between the peripheral and memory. During normal operation of the computer, bus switch 1 is closed, and bus switches 2 and 3 are open. The CPU controls the buses, providing an address on the address bus and reading data from memory or writing data to memory via the data bus. When a peripheral wishes to take part in an I/O transaction it asserts the Transfer. Request input of the DMA controller (DMAC).

… cont’d n n In turn, the DMA controller asserts DMArequest to request control of the buses from the CPU; that is the CPU is taken off-line. When the CPU returns DMAgrant to the DMAC, a DMA transfer takes place. Bus switch 1 is opened and switches 2 and 3 closed. The DMAC provides an address to the address bus and hence to the memory. At the same time, the DMAC provides a Transfer. Grant signal to the peripheral that is then able to write to, or read from, the memory directly. When the DMA operation has been completed, the DMAC hands back control of the bus to the CPU.

… cont’d n n In turn, the DMA controller asserts DMArequest to request control of the buses from the CPU; that is the CPU is taken off-line. When the CPU returns DMAgrant to the DMAC, a DMA transfer takes place. Bus switch 1 is opened and switches 2 and 3 closed. The DMAC provides an address to the address bus and hence to the memory. At the same time, the DMAC provides a Transfer. Grant signal to the peripheral that is then able to write to, or read from, the memory directly. When the DMA operation has been completed, the DMAC hands back control of the bus to the CPU.

Flowchart for a DMA operation

Flowchart for a DMA operation

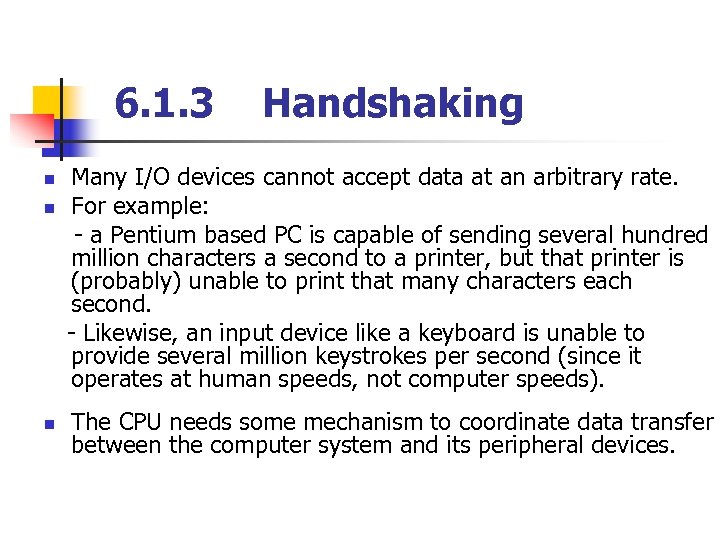

6. 1. 3 Handshaking n Many I/O devices cannot accept data at an arbitrary rate. n For example: - a Pentium based PC is capable of sending several hundred million characters a second to a printer, but that printer is (probably) unable to print that many characters each second. - Likewise, an input device like a keyboard is unable to provide several million keystrokes per second (since it operates at human speeds, not computer speeds). n The CPU needs some mechanism to coordinate data transfer between the computer system and its peripheral devices.

6. 1. 3 Handshaking n Many I/O devices cannot accept data at an arbitrary rate. n For example: - a Pentium based PC is capable of sending several hundred million characters a second to a printer, but that printer is (probably) unable to print that many characters each second. - Likewise, an input device like a keyboard is unable to provide several million keystrokes per second (since it operates at human speeds, not computer speeds). n The CPU needs some mechanism to coordinate data transfer between the computer system and its peripheral devices.

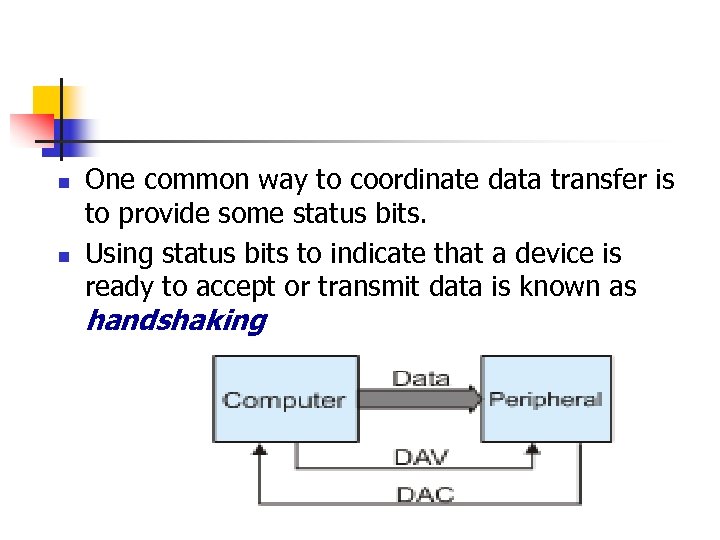

n n One common way to coordinate data transfer is to provide some status bits. Using status bits to indicate that a device is ready to accept or transmit data is known as handshaking

n n One common way to coordinate data transfer is to provide some status bits. Using status bits to indicate that a device is ready to accept or transmit data is known as handshaking

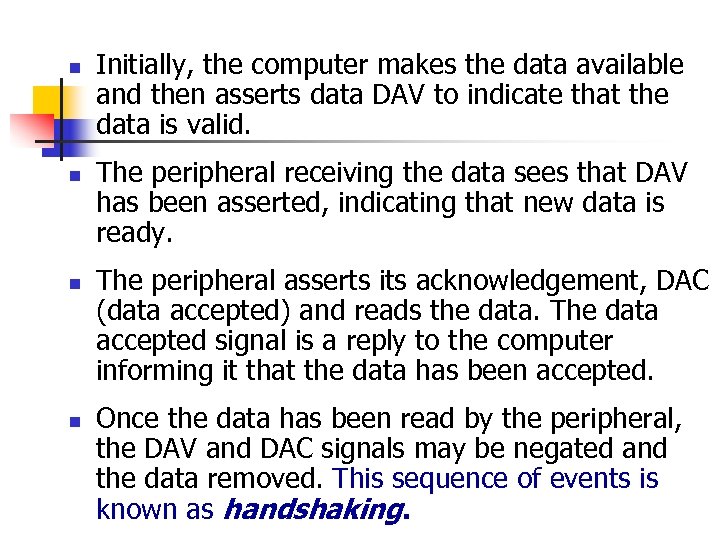

n n Initially, the computer makes the data available and then asserts data DAV to indicate that the data is valid. The peripheral receiving the data sees that DAV has been asserted, indicating that new data is ready. The peripheral asserts its acknowledgement, DAC (data accepted) and reads the data. The data accepted signal is a reply to the computer informing it that the data has been accepted. Once the data has been read by the peripheral, the DAV and DAC signals may be negated and the data removed. This sequence of events is known as handshaking.

n n Initially, the computer makes the data available and then asserts data DAV to indicate that the data is valid. The peripheral receiving the data sees that DAV has been asserted, indicating that new data is ready. The peripheral asserts its acknowledgement, DAC (data accepted) and reads the data. The data accepted signal is a reply to the computer informing it that the data has been accepted. Once the data has been read by the peripheral, the DAV and DAC signals may be negated and the data removed. This sequence of events is known as handshaking.

6. 2 Interface Content: n Definition n Concept of interfacing n Serial and parallel data transmission techniques n RS 232 standard n A/D and D/A Converters n Interface chips (serial & parallel)

6. 2 Interface Content: n Definition n Concept of interfacing n Serial and parallel data transmission techniques n RS 232 standard n A/D and D/A Converters n Interface chips (serial & parallel)

6. 2. 1 n n Definition I/O Interface is required whenever the I/O device is driven by the processor. An interface is an assembly of electronic circuits that make the computer compatible with the peripheral units. This compatibility permits the computer and the peripheral units to communicate intelligently. The compatibility involves logic levels, timing or speed, and control.

6. 2. 1 n n Definition I/O Interface is required whenever the I/O device is driven by the processor. An interface is an assembly of electronic circuits that make the computer compatible with the peripheral units. This compatibility permits the computer and the peripheral units to communicate intelligently. The compatibility involves logic levels, timing or speed, and control.

… cont’d 1. When digital data is transmitted between two units, the binary voltage or current levels must be compatible. Logic-level conversion is often required to properly interface different types of logic circuits. For example, logic-level shifting is often required to properly interface bipolar and MOS circuits. 2. The speed of the data transmission must also be compatible. Some type of temporary storage between the two units may be required as a buffer to match the high-speed CPU to a low-speed peripheral unit

… cont’d 1. When digital data is transmitted between two units, the binary voltage or current levels must be compatible. Logic-level conversion is often required to properly interface different types of logic circuits. For example, logic-level shifting is often required to properly interface bipolar and MOS circuits. 2. The speed of the data transmission must also be compatible. Some type of temporary storage between the two units may be required as a buffer to match the high-speed CPU to a low-speed peripheral unit

3. Control is another function of the interface. There are status lines that tell when the computeror peripheral unit is ready or busy, and strobe lines that actually initiate the data transfers. This process is often referred to as “handshaking. ” The type of information exchanged between the I/O unit and the peripheral devices includes data, addressing, and control signals. In some computers, peripheral units are addressed as storage locations, and all memory reference instructions can be used in performing I/O operations. No special I/O instructions are used in these computers

3. Control is another function of the interface. There are status lines that tell when the computeror peripheral unit is ready or busy, and strobe lines that actually initiate the data transfers. This process is often referred to as “handshaking. ” The type of information exchanged between the I/O unit and the peripheral devices includes data, addressing, and control signals. In some computers, peripheral units are addressed as storage locations, and all memory reference instructions can be used in performing I/O operations. No special I/O instructions are used in these computers

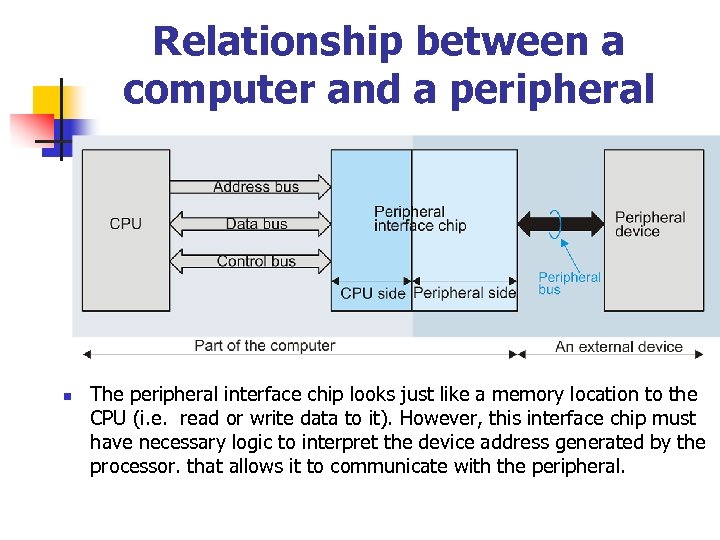

Relationship between a computer and a peripheral n The peripheral interface chip looks just like a memory location to the CPU (i. e. read or write data to it). However, this interface chip must have necessary logic to interpret the device address generated by the processor. that allows it to communicate with the peripheral.

Relationship between a computer and a peripheral n The peripheral interface chip looks just like a memory location to the CPU (i. e. read or write data to it). However, this interface chip must have necessary logic to interpret the device address generated by the processor. that allows it to communicate with the peripheral.

Method of transmitting digital data There are two methods of transmitting digital data : - parallel and - serial transmissions. n n Microprocessors are by nature parallel machines. They transmit/receive data in parallel bits (8, 16, 32, 64). It is required sometimes to send the data serially.

Method of transmitting digital data There are two methods of transmitting digital data : - parallel and - serial transmissions. n n Microprocessors are by nature parallel machines. They transmit/receive data in parallel bits (8, 16, 32, 64). It is required sometimes to send the data serially.

Parallel data transmission n n all bits of the binary data are transmitted simultaneously. For example, to transmit an 8 – bit binary number in parallel from one unit to another, eight transmission lines are required. Each bit requires its own separate data path. All bits of a word are transmitted at the same time.

Parallel data transmission n n all bits of the binary data are transmitted simultaneously. For example, to transmit an 8 – bit binary number in parallel from one unit to another, eight transmission lines are required. Each bit requires its own separate data path. All bits of a word are transmitted at the same time.

… cont’d n n This method of transmission can move a significant amount of data in a given period of time. Its disadvantage is the large number of interconnecting cables between the two units. For large binary words, cabling becomes complex and expensive. This is particularly true if the distance between the two units is great. Long multiwire cables are not only expensive, but also require special interfacing to minimize noise and distortion problems. Examples: connections between a computer and a printer (Most printers are within 6 meters or 20 feet).

… cont’d n n This method of transmission can move a significant amount of data in a given period of time. Its disadvantage is the large number of interconnecting cables between the two units. For large binary words, cabling becomes complex and expensive. This is particularly true if the distance between the two units is great. Long multiwire cables are not only expensive, but also require special interfacing to minimize noise and distortion problems. Examples: connections between a computer and a printer (Most printers are within 6 meters or 20 feet).

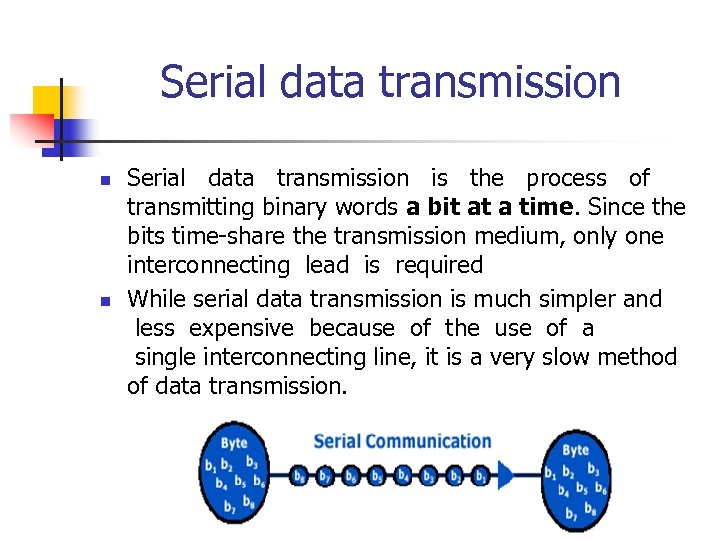

Serial data transmission n n Serial data transmission is the process of transmitting binary words a bit at a time. Since the bits time-share the transmission medium, only one interconnecting lead is required While serial data transmission is much simpler and less expensive because of the use of a single interconnecting line, it is a very slow method of data transmission.

Serial data transmission n n Serial data transmission is the process of transmitting binary words a bit at a time. Since the bits time-share the transmission medium, only one interconnecting lead is required While serial data transmission is much simpler and less expensive because of the use of a single interconnecting line, it is a very slow method of data transmission.

… cont’d n n n Serial data transmission is useful in systems where high speed is not a requirement. Serial data transmission techniques are widely used in transmitting data between a computer and its peripheral units. While the computer operates at very high speeds, most peripheral units are slow because of their electromechanical nature. Slower serial data transmission is more compatible with such devices. Since the speed of serial transmission is more than adequate in such units, the advantages of low cost and simplicity of the signal interconnecting line can be obtained.

… cont’d n n n Serial data transmission is useful in systems where high speed is not a requirement. Serial data transmission techniques are widely used in transmitting data between a computer and its peripheral units. While the computer operates at very high speeds, most peripheral units are slow because of their electromechanical nature. Slower serial data transmission is more compatible with such devices. Since the speed of serial transmission is more than adequate in such units, the advantages of low cost and simplicity of the signal interconnecting line can be obtained.

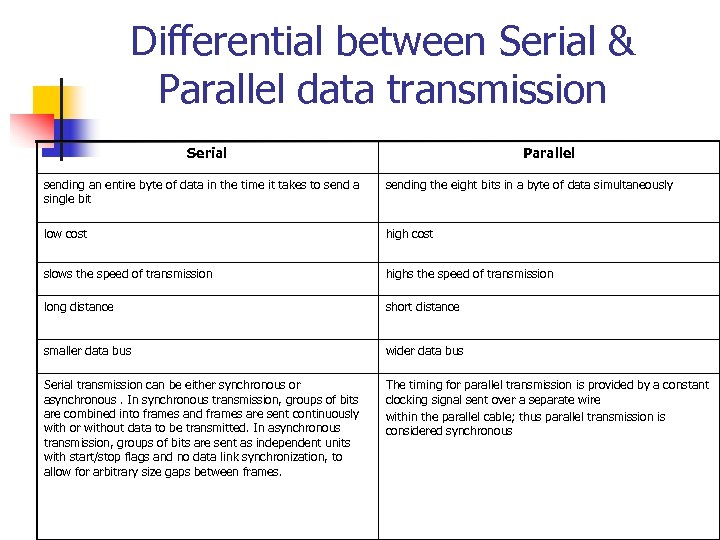

Differential between Serial & Parallel data transmission Serial Parallel sending an entire byte of data in the time it takes to send a single bit sending the eight bits in a byte of data simultaneously low cost high cost slows the speed of transmission highs the speed of transmission long distance short distance smaller data bus wider data bus Serial transmission can be either synchronous or asynchronous. In synchronous transmission, groups of bits are combined into frames and frames are sent continuously with or without data to be transmitted. In asynchronous transmission, groups of bits are sent as independent units with start/stop flags and no data link synchronization, to allow for arbitrary size gaps between frames. The timing for parallel transmission is provided by a constant clocking signal sent over a separate wire within the parallel cable; thus parallel transmission is considered synchronous

Differential between Serial & Parallel data transmission Serial Parallel sending an entire byte of data in the time it takes to send a single bit sending the eight bits in a byte of data simultaneously low cost high cost slows the speed of transmission highs the speed of transmission long distance short distance smaller data bus wider data bus Serial transmission can be either synchronous or asynchronous. In synchronous transmission, groups of bits are combined into frames and frames are sent continuously with or without data to be transmitted. In asynchronous transmission, groups of bits are sent as independent units with start/stop flags and no data link synchronization, to allow for arbitrary size gaps between frames. The timing for parallel transmission is provided by a constant clocking signal sent over a separate wire within the parallel cable; thus parallel transmission is considered synchronous

Synchronous Communication (synchronised transmit & receive clocks) n n There are two methods for serial communication: - Synchronous & - Asynchronous. In Synchronous serial communication the receiver must know when to “read” the next bit coming from the sender, this can be achieved by sharing a clock between sender and receiver.

Synchronous Communication (synchronised transmit & receive clocks) n n There are two methods for serial communication: - Synchronous & - Asynchronous. In Synchronous serial communication the receiver must know when to “read” the next bit coming from the sender, this can be achieved by sharing a clock between sender and receiver.

… cont’d n n In most forms of serial Synchronous communication, if there is no data available at a given time to transmit, a fill character will be sent instead so that data is always being transmitted. Synchronous communication is usually more efficient because only data bits are transmitted between sender and receiver, however it will be more costly because extra wiring and control circuits are required to share a clock signal between the sender and receiver. More complex interface (high data rates supported up to ~ 10 Gbps) Used for: Connections between computer and telephony networks

… cont’d n n In most forms of serial Synchronous communication, if there is no data available at a given time to transmit, a fill character will be sent instead so that data is always being transmitted. Synchronous communication is usually more efficient because only data bits are transmitted between sender and receiver, however it will be more costly because extra wiring and control circuits are required to share a clock signal between the sender and receiver. More complex interface (high data rates supported up to ~ 10 Gbps) Used for: Connections between computer and telephony networks

Asynchronous Communication (independent transmit & receive clocks) Simple interface (limited data rate, typically < 64 kbps) n No clock sent (Tx & Rx have own clocks) Asynchronous transmission allows data to be transmitted without the sender having to send a clock signal to the receiver. n Instead, special bits will be added to each word in order to synchronize the sending and receiving of the data. n Used for connecting: Printer, Terminal, Modem, home connections to the Internet n

Asynchronous Communication (independent transmit & receive clocks) Simple interface (limited data rate, typically < 64 kbps) n No clock sent (Tx & Rx have own clocks) Asynchronous transmission allows data to be transmitted without the sender having to send a clock signal to the receiver. n Instead, special bits will be added to each word in order to synchronize the sending and receiving of the data. n Used for connecting: Printer, Terminal, Modem, home connections to the Internet n

Asynchronous serial communication characterictics n n Serial communication requires the following four parameters: The baud rate of the transmission The number of data bits encoding a character The sense of the optional parity bit The number of stop bits Baud rate is a measure of how fast data are moving between instruments that use serial communication. The baud rate is identical to the maximum number of bits of information, including control bits, that are transmitted per second.

Asynchronous serial communication characterictics n n Serial communication requires the following four parameters: The baud rate of the transmission The number of data bits encoding a character The sense of the optional parity bit The number of stop bits Baud rate is a measure of how fast data are moving between instruments that use serial communication. The baud rate is identical to the maximum number of bits of information, including control bits, that are transmitted per second.

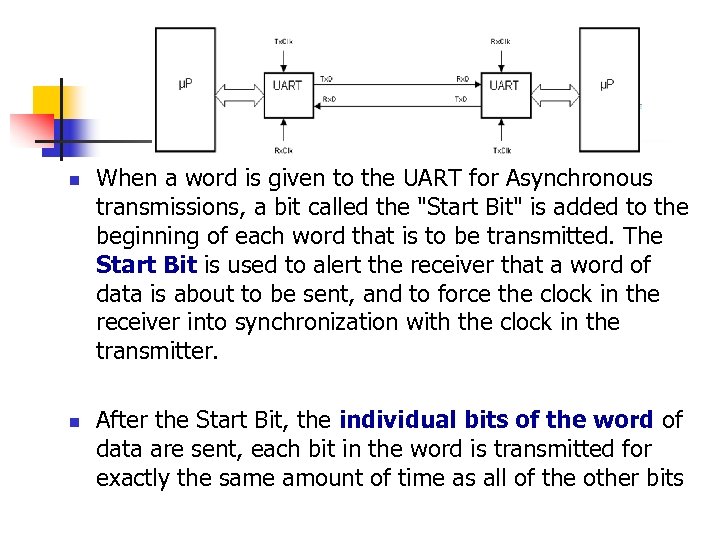

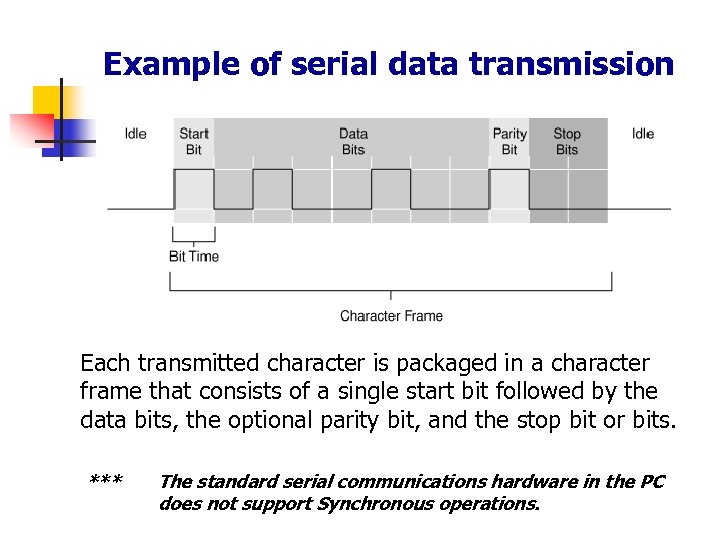

n n When a word is given to the UART for Asynchronous transmissions, a bit called the "Start Bit" is added to the beginning of each word that is to be transmitted. The Start Bit is used to alert the receiver that a word of data is about to be sent, and to force the clock in the receiver into synchronization with the clock in the transmitter. After the Start Bit, the individual bits of the word of data are sent, each bit in the word is transmitted for exactly the same amount of time as all of the other bits

n n When a word is given to the UART for Asynchronous transmissions, a bit called the "Start Bit" is added to the beginning of each word that is to be transmitted. The Start Bit is used to alert the receiver that a word of data is about to be sent, and to force the clock in the receiver into synchronization with the clock in the transmitter. After the Start Bit, the individual bits of the word of data are sent, each bit in the word is transmitted for exactly the same amount of time as all of the other bits

… cont’d n When the entire data word has been sent, the transmitter may add a Parity Bit that the transmitter generates. The Parity Bit may be used by the receiver to perform simple error checking. n Then at least one Stop Bit is sent by the transmitter. If the Stop Bit does not appear when it is supposed to, the UART considers the entire word to be garbled and will report a Framing Error.

… cont’d n When the entire data word has been sent, the transmitter may add a Parity Bit that the transmitter generates. The Parity Bit may be used by the receiver to perform simple error checking. n Then at least one Stop Bit is sent by the transmitter. If the Stop Bit does not appear when it is supposed to, the UART considers the entire word to be garbled and will report a Framing Error.

Example of serial data transmission Each transmitted character is packaged in a character frame that consists of a single start bit followed by the data bits, the optional parity bit, and the stop bit or bits. *** The standard serial communications hardware in the PC does not support Synchronous operations.

Example of serial data transmission Each transmitted character is packaged in a character frame that consists of a single start bit followed by the data bits, the optional parity bit, and the stop bit or bits. *** The standard serial communications hardware in the PC does not support Synchronous operations.

RS 232 Standard n n There are many different recommended standards of serial port communication, including the following most common type: RS-232, RS-449, RS-422, RS-423 RS-232 (Recommended Standard 232) is a standard for serial binary single-ended data and control signals connecting between a DTE (Data Terminal Equipment) and a DCE (Data Circuit-terminating Equipment). It is commonly used in computer serial ports. RS-232 -compatible port was a standard feature for serial communications, such as modem connections, on many computers.

RS 232 Standard n n There are many different recommended standards of serial port communication, including the following most common type: RS-232, RS-449, RS-422, RS-423 RS-232 (Recommended Standard 232) is a standard for serial binary single-ended data and control signals connecting between a DTE (Data Terminal Equipment) and a DCE (Data Circuit-terminating Equipment). It is commonly used in computer serial ports. RS-232 -compatible port was a standard feature for serial communications, such as modem connections, on many computers.

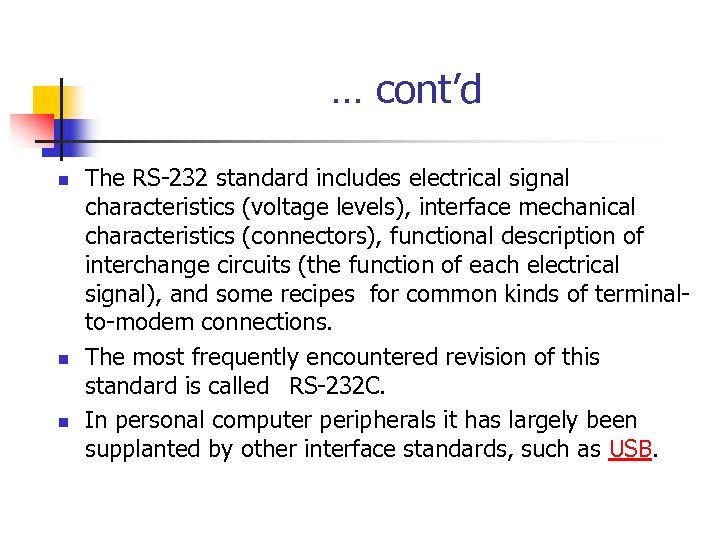

… cont’d n n n The RS-232 standard includes electrical signal characteristics (voltage levels), interface mechanical characteristics (connectors), functional description of interchange circuits (the function of each electrical signal), and some recipes for common kinds of terminalto-modem connections. The most frequently encountered revision of this standard is called RS-232 C. In personal computer peripherals it has largely been supplanted by other interface standards, such as USB.

… cont’d n n n The RS-232 standard includes electrical signal characteristics (voltage levels), interface mechanical characteristics (connectors), functional description of interchange circuits (the function of each electrical signal), and some recipes for common kinds of terminalto-modem connections. The most frequently encountered revision of this standard is called RS-232 C. In personal computer peripherals it has largely been supplanted by other interface standards, such as USB.

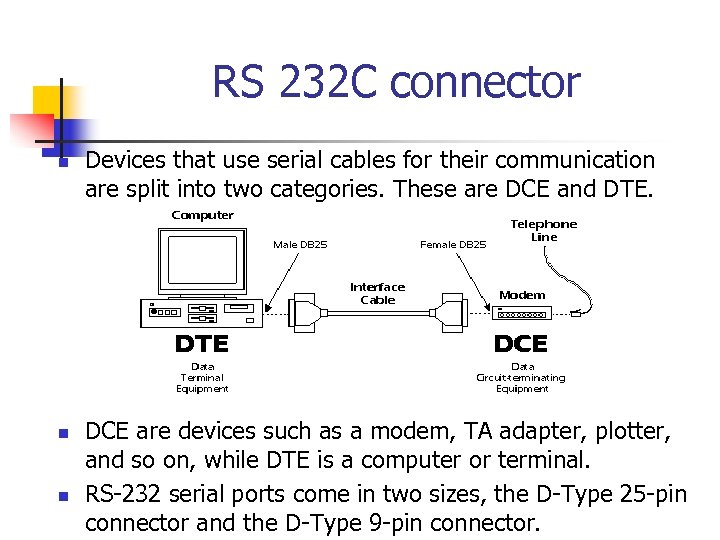

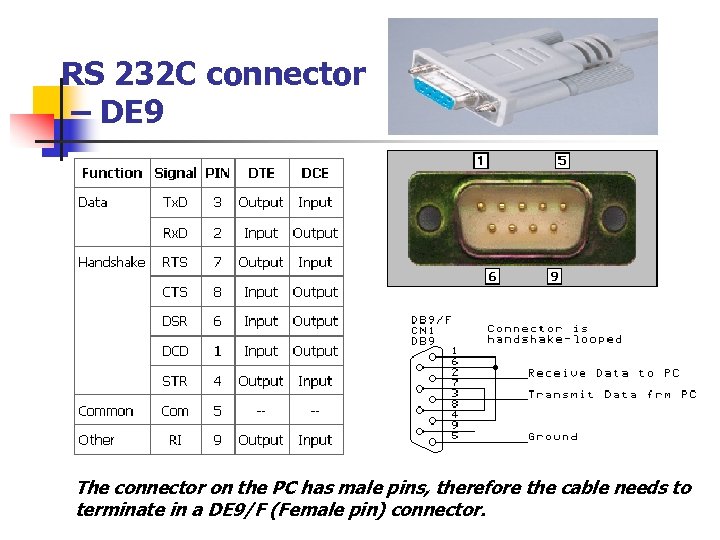

RS 232 C connector n n n Devices that use serial cables for their communication are split into two categories. These are DCE and DTE. DCE are devices such as a modem, TA adapter, plotter, and so on, while DTE is a computer or terminal. RS-232 serial ports come in two sizes, the D-Type 25 -pin connector and the D-Type 9 -pin connector.

RS 232 C connector n n n Devices that use serial cables for their communication are split into two categories. These are DCE and DTE. DCE are devices such as a modem, TA adapter, plotter, and so on, while DTE is a computer or terminal. RS-232 serial ports come in two sizes, the D-Type 25 -pin connector and the D-Type 9 -pin connector.

RS 232 C connector – DE 9 The connector on the PC has male pins, therefore the cable needs to terminate in a DE 9/F (Female pin) connector.

RS 232 C connector – DE 9 The connector on the PC has male pins, therefore the cable needs to terminate in a DE 9/F (Female pin) connector.

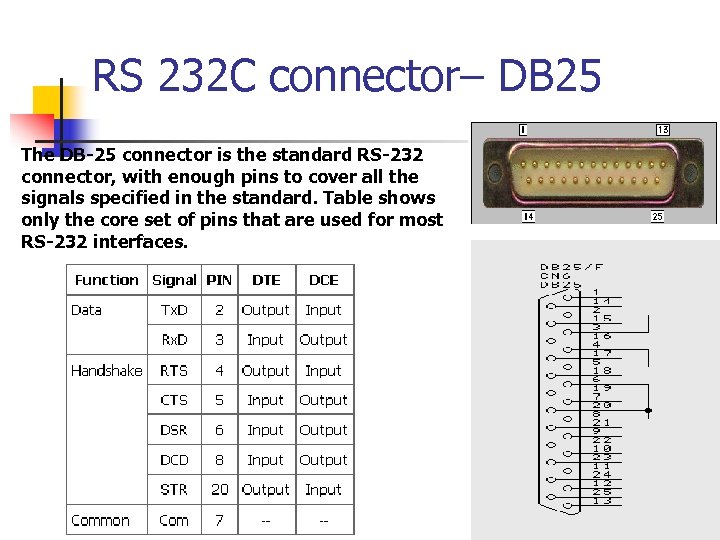

RS 232 C connector– DB 25 The DB-25 connector is the standard RS-232 connector, with enough pins to cover all the signals specified in the standard. Table shows only the core set of pins that are used for most RS-232 interfaces.

RS 232 C connector– DB 25 The DB-25 connector is the standard RS-232 connector, with enough pins to cover all the signals specified in the standard. Table shows only the core set of pins that are used for most RS-232 interfaces.

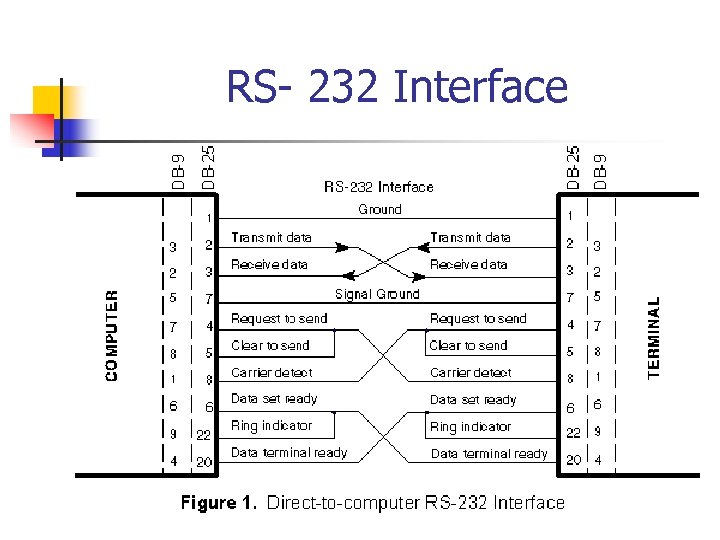

RS- 232 Interface

RS- 232 Interface

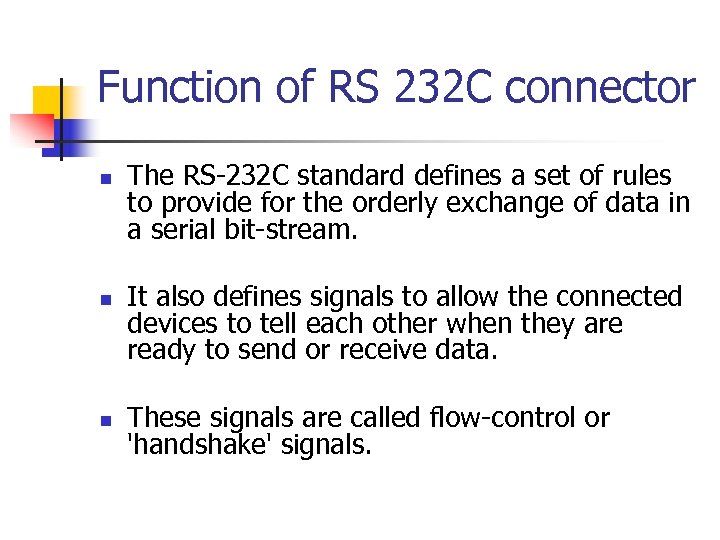

Function of RS 232 C connector n n n The RS-232 C standard defines a set of rules to provide for the orderly exchange of data in a serial bit-stream. It also defines signals to allow the connected devices to tell each other when they are ready to send or receive data. These signals are called flow-control or 'handshake' signals.

Function of RS 232 C connector n n n The RS-232 C standard defines a set of rules to provide for the orderly exchange of data in a serial bit-stream. It also defines signals to allow the connected devices to tell each other when they are ready to send or receive data. These signals are called flow-control or 'handshake' signals.

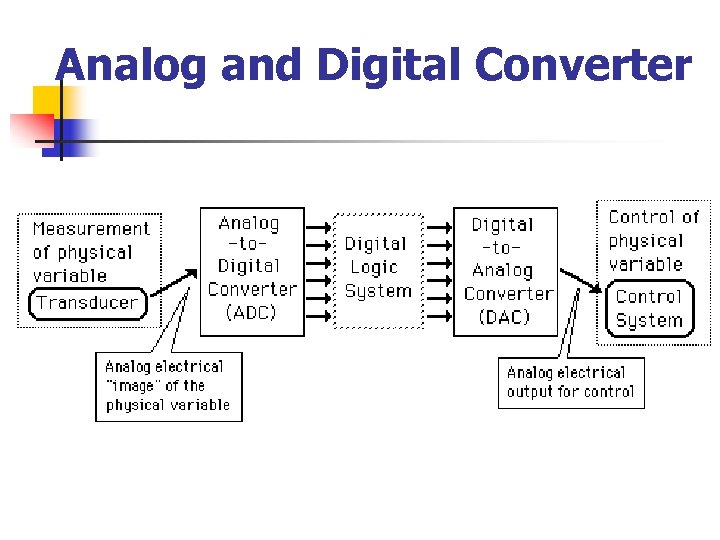

Analog and Digital Converter

Analog and Digital Converter

Analog to Digital Converter (ADC) n n An analog-to-digital converter is a device that converts a continuous quantity to a discrete digital number. The basic principle of operation is to use the comparator principle to determine whether or not to turn on a particular bit of the binary number output. ADC is an electronic device that converts an input analog voltage (or current) to a digital number proportional to the magnitude of the voltage or current. Some non-electronic or only partially electronic devices, such as rotary encoders, can also be considered ADCs.

Analog to Digital Converter (ADC) n n An analog-to-digital converter is a device that converts a continuous quantity to a discrete digital number. The basic principle of operation is to use the comparator principle to determine whether or not to turn on a particular bit of the binary number output. ADC is an electronic device that converts an input analog voltage (or current) to a digital number proportional to the magnitude of the voltage or current. Some non-electronic or only partially electronic devices, such as rotary encoders, can also be considered ADCs.

Digital to Analog Converter n n n A digital-to-analog converter (DAC or D-to-A) is a device that converts a digital (usually binary) code to an analog signal (current, voltage, or electric charge). A DAC converts an abstract finite-precision number (usually a fixed-point binary number) into a concrete physical quantity (e. g. , a voltage or a pressure). DACs are often used to convert finite-precision time series data to a continually varying physical signal.

Digital to Analog Converter n n n A digital-to-analog converter (DAC or D-to-A) is a device that converts a digital (usually binary) code to an analog signal (current, voltage, or electric charge). A DAC converts an abstract finite-precision number (usually a fixed-point binary number) into a concrete physical quantity (e. g. , a voltage or a pressure). DACs are often used to convert finite-precision time series data to a continually varying physical signal.

USART 8251 ( Universal Synchronous and Asynchronous Receiver and Transmitter) n n n The 8251 is a USART (Universal Synchronous Asynchronous Receiver Transmitter) for serial data communication. As a peripheral device of a microcomputer system, the 8251 receives parallel data from the CPU and transmits serial data after conversion. This device also receives serial data from the outside and transmits parallel data to the CPU after conversion. It allows connecting a microcomputer system to a variety of external devices, e. g. mouse or trackball, serial keyboards and terminals, printers and plotters with RS 232 interface, microcontroller development systems, flashprogrammers, etc.

USART 8251 ( Universal Synchronous and Asynchronous Receiver and Transmitter) n n n The 8251 is a USART (Universal Synchronous Asynchronous Receiver Transmitter) for serial data communication. As a peripheral device of a microcomputer system, the 8251 receives parallel data from the CPU and transmits serial data after conversion. This device also receives serial data from the outside and transmits parallel data to the CPU after conversion. It allows connecting a microcomputer system to a variety of external devices, e. g. mouse or trackball, serial keyboards and terminals, printers and plotters with RS 232 interface, microcontroller development systems, flashprogrammers, etc.

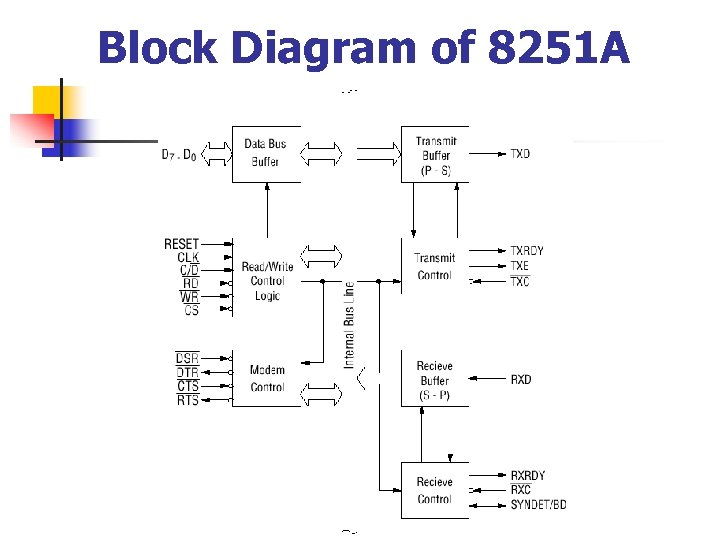

Block Diagram of 8251 A

Block Diagram of 8251 A

PPI 8255 (Programmable Peripheral Interface) n n n The 8255 A programmable peripheral interface (PPI) implements a general-purpose I/O interface to connect peripheral equipment to a microcomputer system bus. The functional configuration of each port is programmed by the systems software. Features: - Three 8 -bit Peripheral Ports - Ports A, B, and C - Three programming modes for Peripheral Ports: Mode 0 (Basic Input/Output), Mode 1 (Strobed Input/Output), and Mode 2 (Bidirectional) - Total of 24 programmable I/O lines - 8 -bit bidirectional system data bus with standard microprocessor interface controls

PPI 8255 (Programmable Peripheral Interface) n n n The 8255 A programmable peripheral interface (PPI) implements a general-purpose I/O interface to connect peripheral equipment to a microcomputer system bus. The functional configuration of each port is programmed by the systems software. Features: - Three 8 -bit Peripheral Ports - Ports A, B, and C - Three programming modes for Peripheral Ports: Mode 0 (Basic Input/Output), Mode 1 (Strobed Input/Output), and Mode 2 (Bidirectional) - Total of 24 programmable I/O lines - 8 -bit bidirectional system data bus with standard microprocessor interface controls

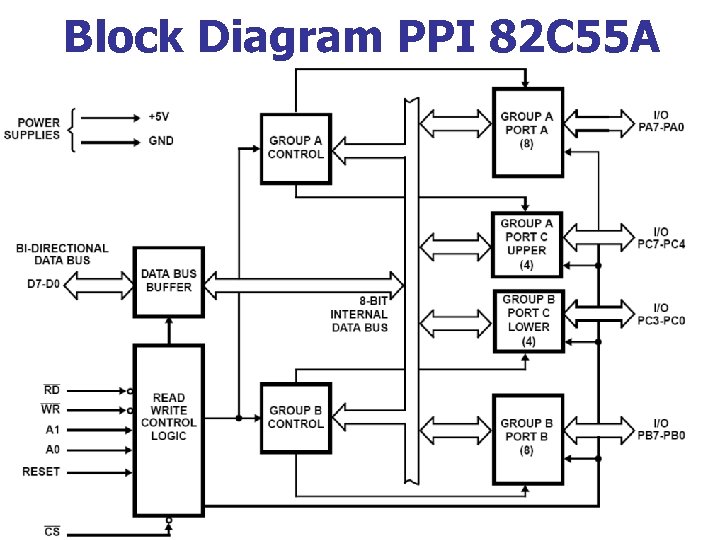

Block Diagram PPI 82 C 55 A

Block Diagram PPI 82 C 55 A

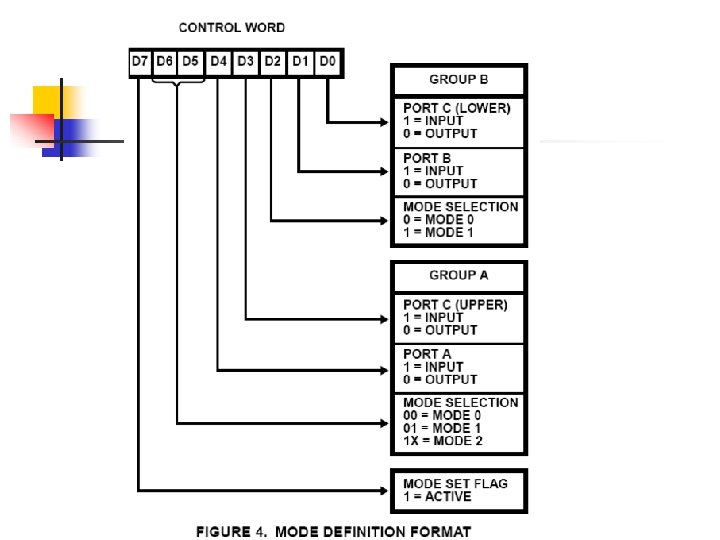

Operating Modes n n The configuration is required before the chip can be used. The configuration tells the 8255 whether ports are input or output and even some strange arrangements called bi-directional and strobed. The 8255 allows for three operating modes: n Mode 0: Ports A and B operate as either inputs or outputs and Port C is divided into two 4 -bit groups either of which can be operated as inputs or outputs n Mode 1: Same as Mode 0 but Port C is used for handshaking and control n Mode 2: Port A is bidirectional (both input and output) and Port C is used for handshaking. Port B is not used.

Operating Modes n n The configuration is required before the chip can be used. The configuration tells the 8255 whether ports are input or output and even some strange arrangements called bi-directional and strobed. The 8255 allows for three operating modes: n Mode 0: Ports A and B operate as either inputs or outputs and Port C is divided into two 4 -bit groups either of which can be operated as inputs or outputs n Mode 1: Same as Mode 0 but Port C is used for handshaking and control n Mode 2: Port A is bidirectional (both input and output) and Port C is used for handshaking. Port B is not used.

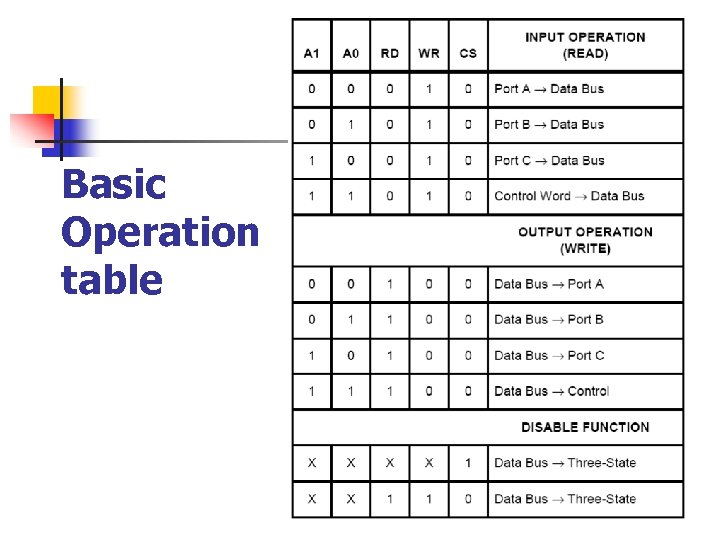

Control Word n n The control word contains information such as “mode”, “bit set”, “bit reset”, etc. , that initializes the functional configuration of the 82 C 55 A. Each of the Control blocks (Group A and Group B) accepts “commands” from the Read/Write Control logic, receives “control words” from the internal data bus and issues the proper commands to its associated ports. n n Control Group A - Port A and Port C upper (C 7 - C 4) Control Group B - Port B and Port C lower (C 3 - C 0) The control word register can be both written and read as shown in the “Basic Operation” table. When the control word is read, bit D 7 will always be a logic “ 1”, as this implies control word mode information.

Control Word n n The control word contains information such as “mode”, “bit set”, “bit reset”, etc. , that initializes the functional configuration of the 82 C 55 A. Each of the Control blocks (Group A and Group B) accepts “commands” from the Read/Write Control logic, receives “control words” from the internal data bus and issues the proper commands to its associated ports. n n Control Group A - Port A and Port C upper (C 7 - C 4) Control Group B - Port B and Port C lower (C 3 - C 0) The control word register can be both written and read as shown in the “Basic Operation” table. When the control word is read, bit D 7 will always be a logic “ 1”, as this implies control word mode information.

Basic Operation table

Basic Operation table

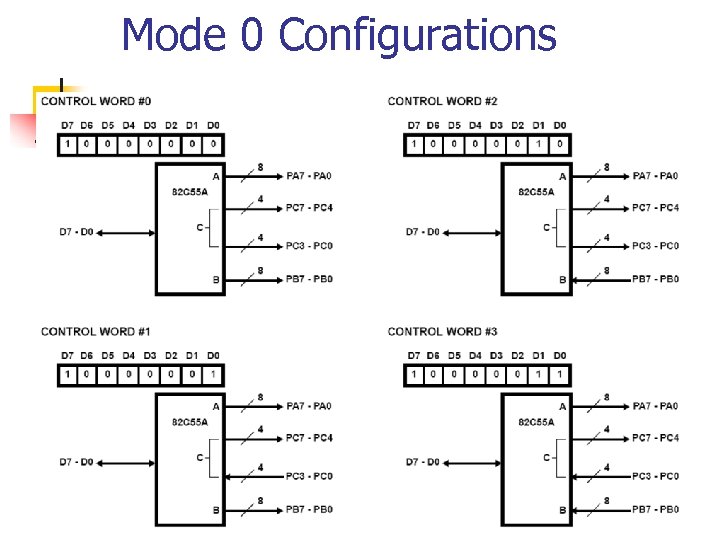

Mode 0 (Basic Input/Output) n n n This functional configuration provides simple input and output operations for each of the three ports. No handshaking is required, data is simply written to or read from a specific port. Mode 0 Basic Functional Definitions: Two 8 -bit ports and two 4 -bit ports Any Port can be input or output Outputs are latched Input are not latched 16 different Input/Output configurations possible

Mode 0 (Basic Input/Output) n n n This functional configuration provides simple input and output operations for each of the three ports. No handshaking is required, data is simply written to or read from a specific port. Mode 0 Basic Functional Definitions: Two 8 -bit ports and two 4 -bit ports Any Port can be input or output Outputs are latched Input are not latched 16 different Input/Output configurations possible

Mode 0 Configurations

Mode 0 Configurations

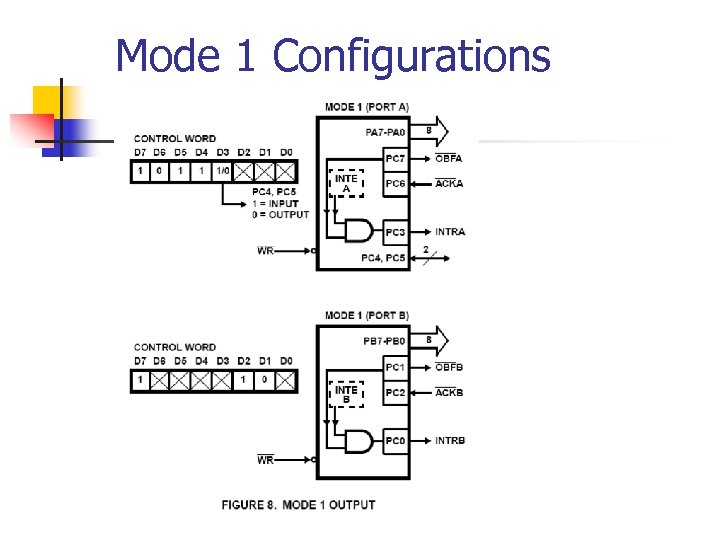

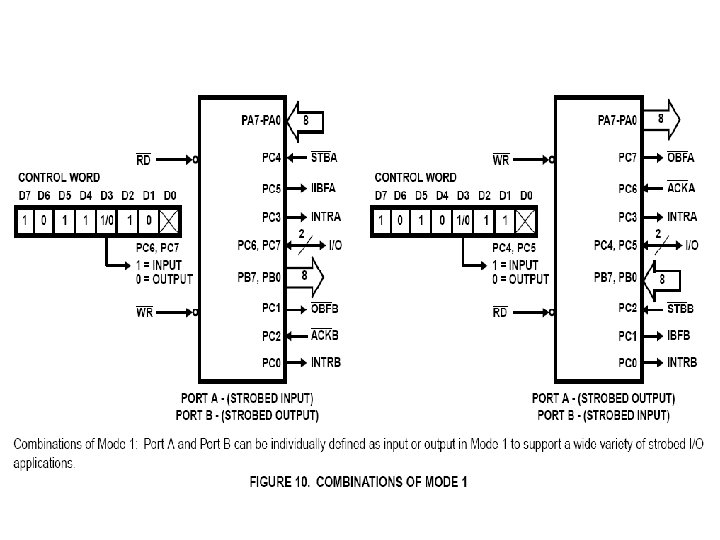

Mode 1 (Strobed Input/Output) n n n This functional configuration provides a means for transferring I/O data to or from a specified port in conjunction with strobes or “hand shaking” signals. In mode 1, port A and port B use the lines on port C to generate or accept these “hand shaking” signals. Mode 1 Basic Function Definitions: Two Groups (Group A and Group B) Each group contains one 8 -bit port and one 4 -bit control/data port The 8 -bit data port can be either input or output. Both inputs and outputs are latched. The 4 -bit port is used for control and status of the 8 -bit port.

Mode 1 (Strobed Input/Output) n n n This functional configuration provides a means for transferring I/O data to or from a specified port in conjunction with strobes or “hand shaking” signals. In mode 1, port A and port B use the lines on port C to generate or accept these “hand shaking” signals. Mode 1 Basic Function Definitions: Two Groups (Group A and Group B) Each group contains one 8 -bit port and one 4 -bit control/data port The 8 -bit data port can be either input or output. Both inputs and outputs are latched. The 4 -bit port is used for control and status of the 8 -bit port.

Mode 1 Configurations

Mode 1 Configurations

Mode 2 (Strobed Bi-Directional Bus I/O) n n The functional configuration provides a means for communicating with a peripheral device or structure on a single 8 -bit bus for both transmitting and receiving data (bi-directional bus I/O). “Hand shaking” signals are provided to maintain proper bus flow discipline similar to Mode 1. Interrupt generation and enable/disable functions are also available. Mode 2 Basic Functional Definitions: Used in Group A only One 8 -bit, bi-directional bus Port (Port A) and a 5 -bit control Port (Port C) Both inputs and outputs are latched The 5 -bit control port (Port C) is used for control and status for the 8 -bit, bi-directional bus port (Port A)

Mode 2 (Strobed Bi-Directional Bus I/O) n n The functional configuration provides a means for communicating with a peripheral device or structure on a single 8 -bit bus for both transmitting and receiving data (bi-directional bus I/O). “Hand shaking” signals are provided to maintain proper bus flow discipline similar to Mode 1. Interrupt generation and enable/disable functions are also available. Mode 2 Basic Functional Definitions: Used in Group A only One 8 -bit, bi-directional bus Port (Port A) and a 5 -bit control Port (Port C) Both inputs and outputs are latched The 5 -bit control port (Port C) is used for control and status for the 8 -bit, bi-directional bus port (Port A)

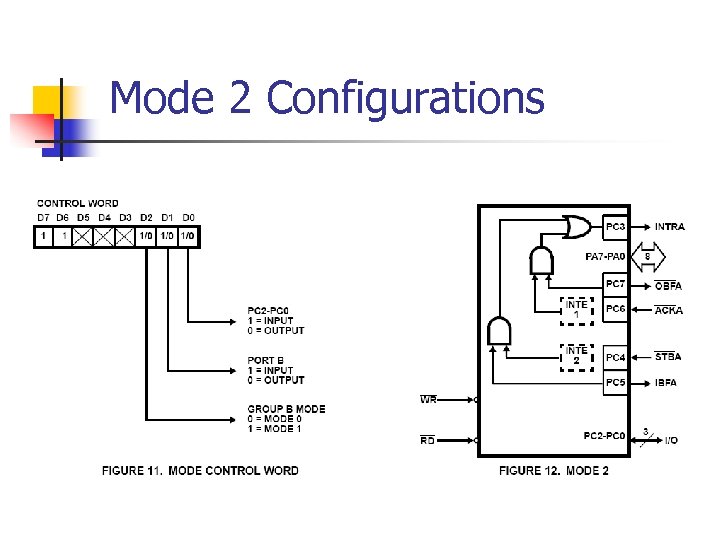

Mode 2 Configurations

Mode 2 Configurations