05eedc575d12f4284c257d01bb9938c4.ppt

- Количество слайдов: 33

TOF Electronics Overview J. Schambach University of Texas Do. E Review, BNL, 25 Sep 2006 1

Outline • • Electronics “Essential Model” Trigger & DAQ Interfaces Board Status Production & Testing 2

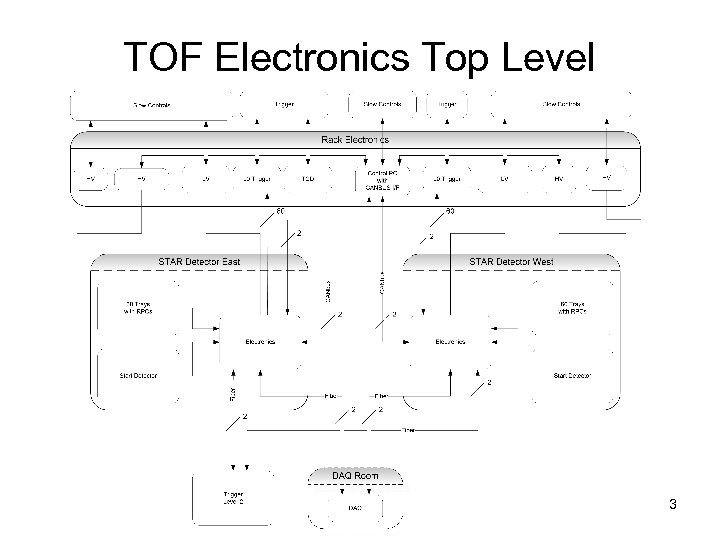

TOF Electronics Top Level 3

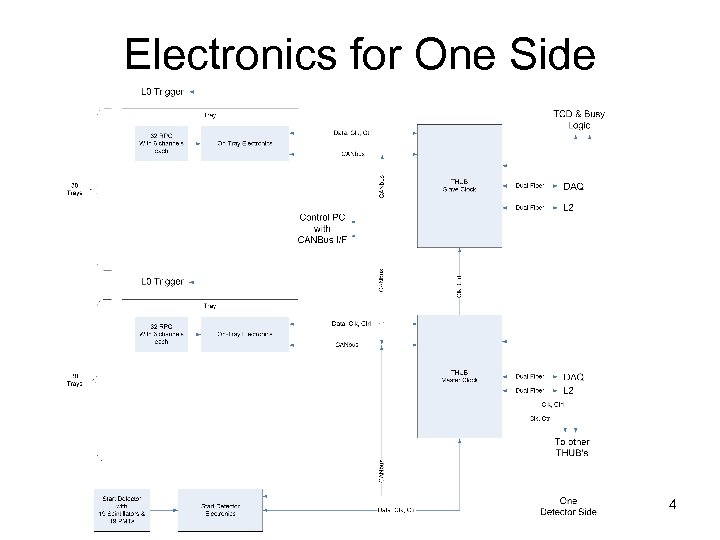

Electronics for One Side 4

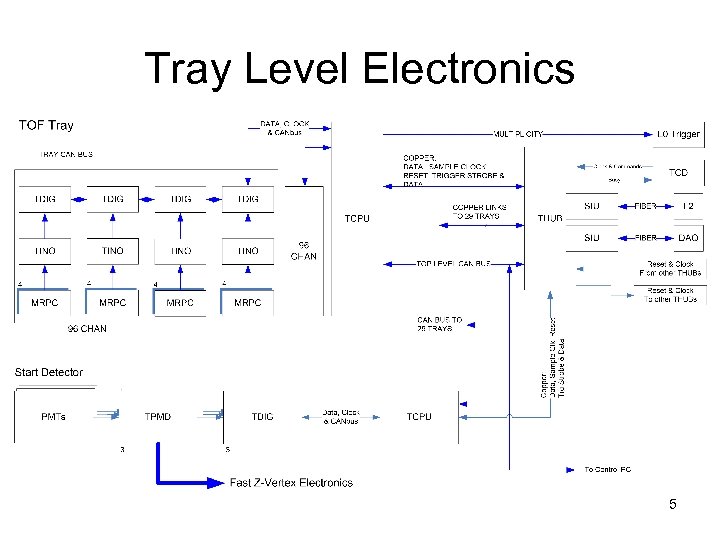

Tray Level Electronics 5

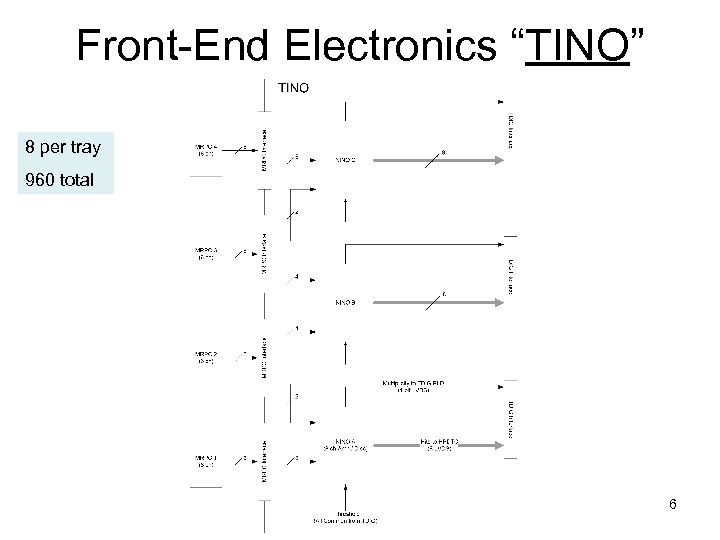

Front-End Electronics “TINO” 8 per tray 960 total 6

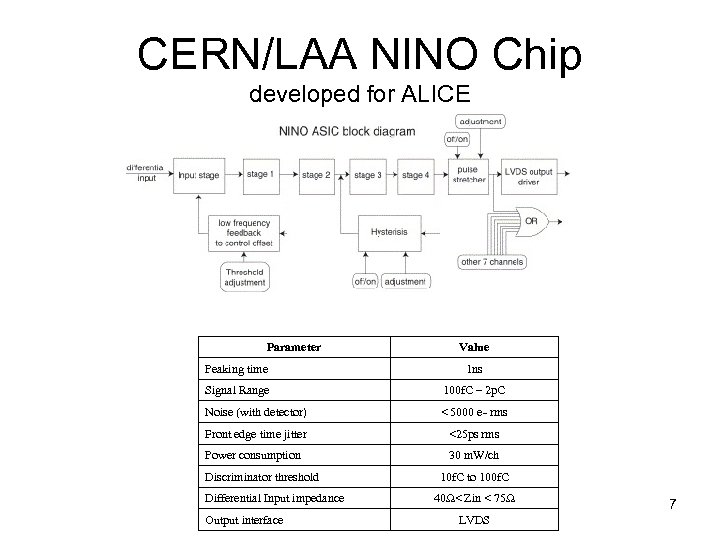

CERN/LAA NINO Chip developed for ALICE Parameter Value Peaking time 1 ns Signal Range 100 f. C – 2 p. C Noise (with detector) < 5000 e- rms Front edge time jitter <25 ps rms Power consumption 30 m. W/ch Discriminator threshold Differential Input impedance Output interface 10 f. C to 100 f. C 40Ω< Zin < 75Ω LVDS 7

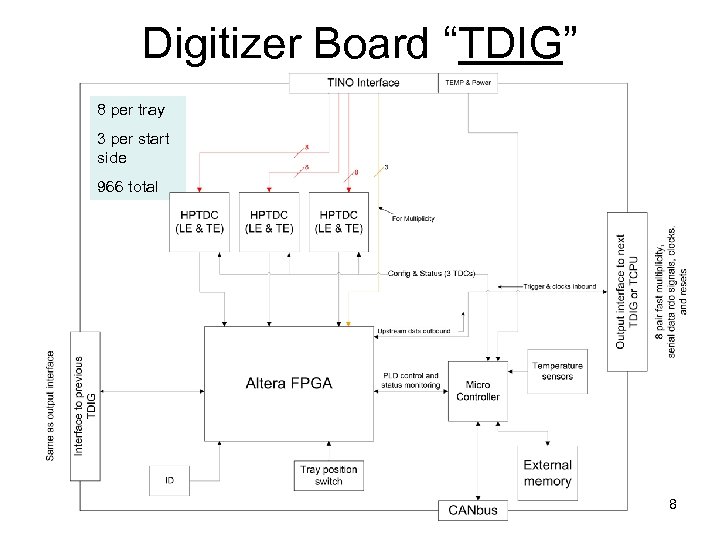

Digitizer Board “TDIG” 8 per tray 3 per start side 966 total 8

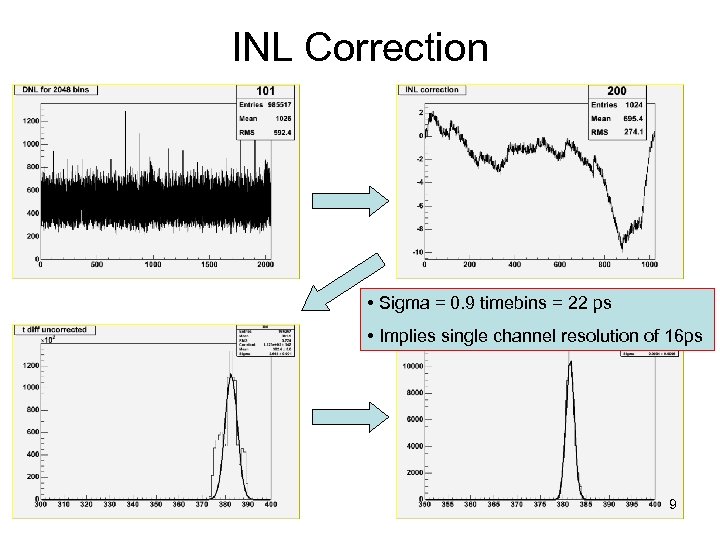

INL Correction • Sigma = 0. 9 timebins = 22 ps • Implies single channel resolution of 16 ps 9

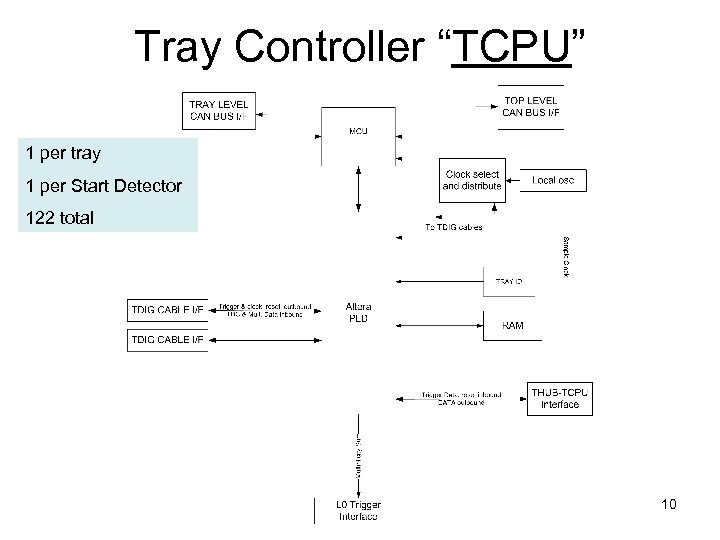

Tray Controller “TCPU” 1 per tray 1 per Start Detector 122 total 10

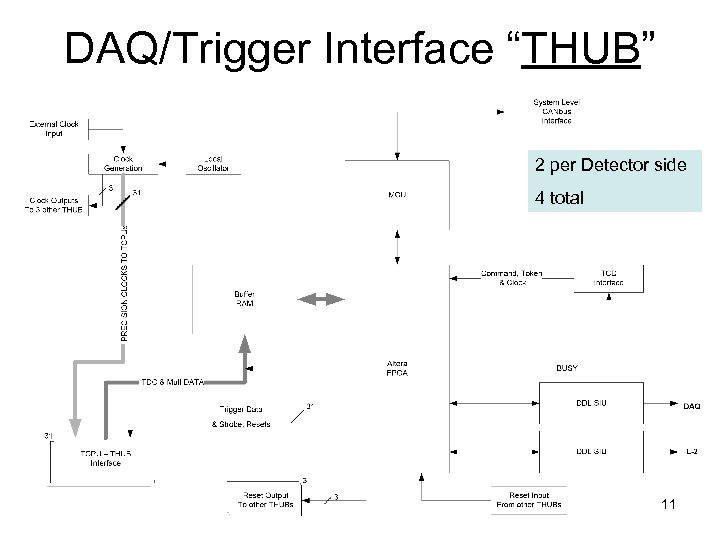

DAQ/Trigger Interface “THUB” 2 per Detector side 4 total 11

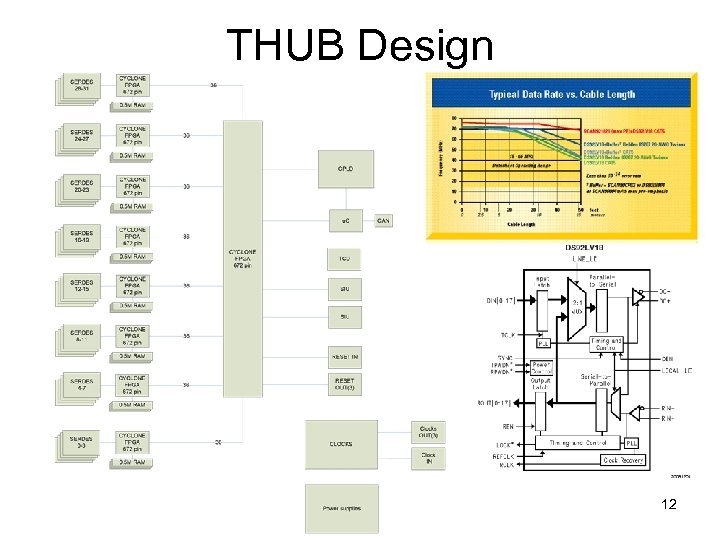

THUB Design 12

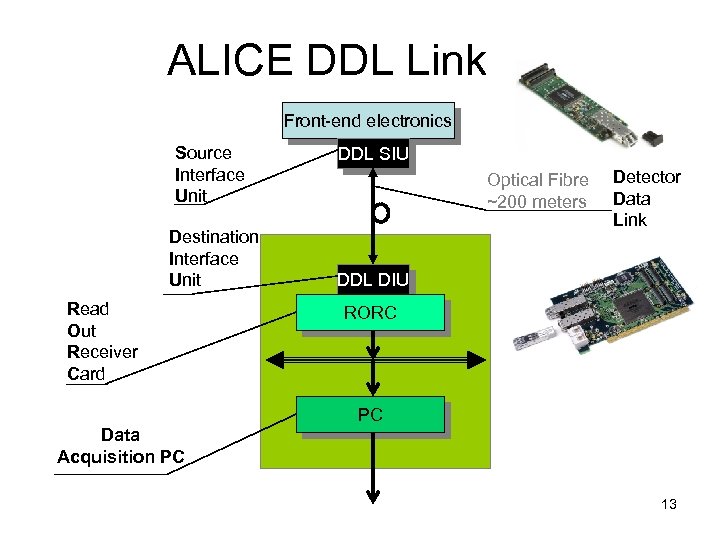

ALICE DDL Link Front-end electronics Source Interface Unit Destination Interface Unit Read Out Receiver Card DDL SIU Optical Fibre ~200 meters Detector Data Link DDL DIU RORC PC Data Acquisition PC 13

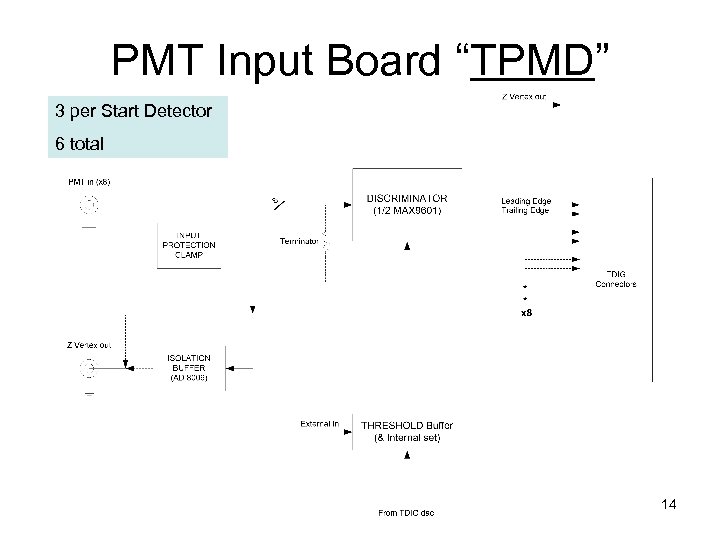

PMT Input Board “TPMD” 3 per Start Detector 6 total 14

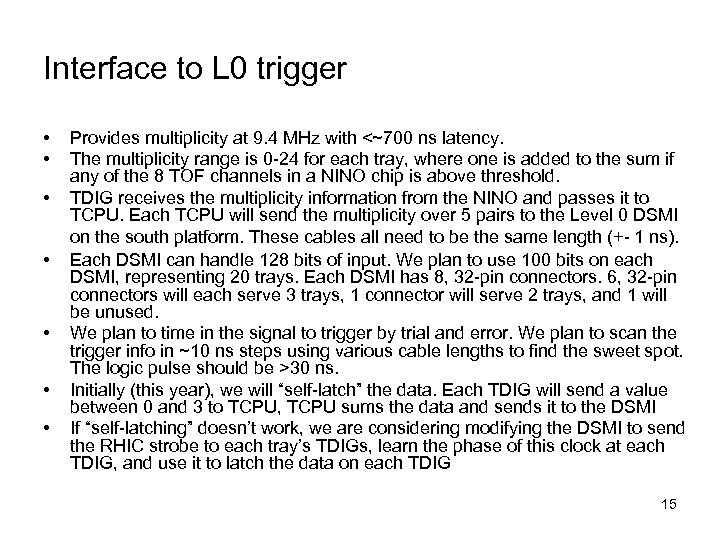

Interface to L 0 trigger • • Provides multiplicity at 9. 4 MHz with <~700 ns latency. The multiplicity range is 0 -24 for each tray, where one is added to the sum if any of the 8 TOF channels in a NINO chip is above threshold. TDIG receives the multiplicity information from the NINO and passes it to TCPU. Each TCPU will send the multiplicity over 5 pairs to the Level 0 DSMI on the south platform. These cables all need to be the same length (+- 1 ns). Each DSMI can handle 128 bits of input. We plan to use 100 bits on each DSMI, representing 20 trays. Each DSMI has 8, 32 -pin connectors. 6, 32 -pin connectors will each serve 3 trays, 1 connector will serve 2 trays, and 1 will be unused. We plan to time in the signal to trigger by trial and error. We plan to scan the trigger info in ~10 ns steps using various cable lengths to find the sweet spot. The logic pulse should be >30 ns. Initially (this year), we will “self-latch” the data. Each TDIG will send a value between 0 and 3 to TCPU, TCPU sums the data and sends it to the DSMI If “self-latching” doesn’t work, we are considering modifying the DSMI to send the RHIC strobe to each tray’s TDIGs, learn the phase of this clock at each TDIG, and use it to latch the data on each TDIG 15

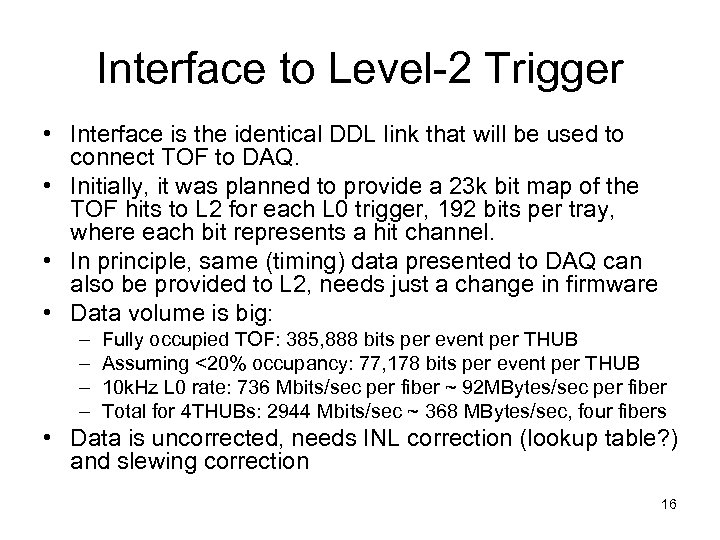

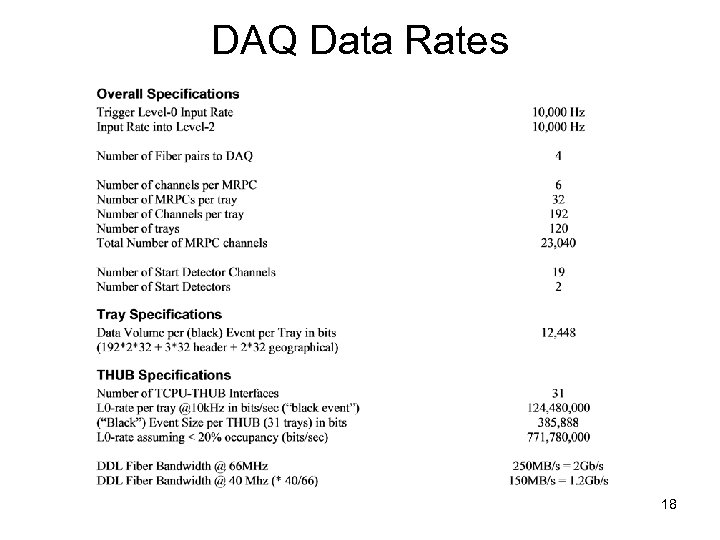

Interface to Level-2 Trigger • Interface is the identical DDL link that will be used to connect TOF to DAQ. • Initially, it was planned to provide a 23 k bit map of the TOF hits to L 2 for each L 0 trigger, 192 bits per tray, where each bit represents a hit channel. • In principle, same (timing) data presented to DAQ can also be provided to L 2, needs just a change in firmware • Data volume is big: – – Fully occupied TOF: 385, 888 bits per event per THUB Assuming <20% occupancy: 77, 178 bits per event per THUB 10 k. Hz L 0 rate: 736 Mbits/sec per fiber ~ 92 MBytes/sec per fiber Total for 4 THUBs: 2944 Mbits/sec ~ 368 MBytes/sec, four fibers • Data is uncorrected, needs INL correction (lookup table? ) and slewing correction 16

Interface to DAQ • • The TOF system needs to be faster than the upgraded TPC so as not to introduce any additional dead time. The TOF information is only useful in a STAR event if the TPC is also readout in that event (for tracking). The system is able to handle L 0 accept commands at >10 k. Hz. The system will not process L 2 -accept or Abort commands, but rather pass those on to DAQ (as separate events) over the fiber for DAQ to process. The current system design foresees sending all events to DAQ independent of any higher level trigger decisions for each Level-0 trigger. This design does not require much memory on THUB other than a small amount (arranged as a FIFO) to decouple the clock domain on the TCPU (SERDES) side from the clock domain of the SIU interface. 17

DAQ Data Rates 18

Current System Status 19

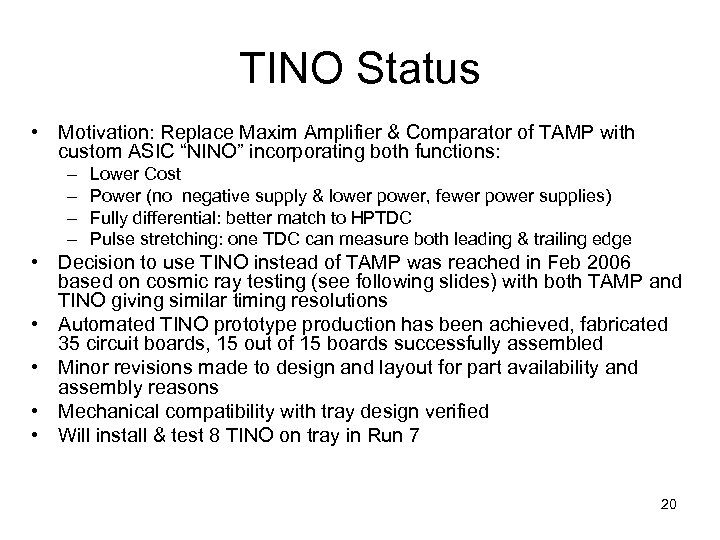

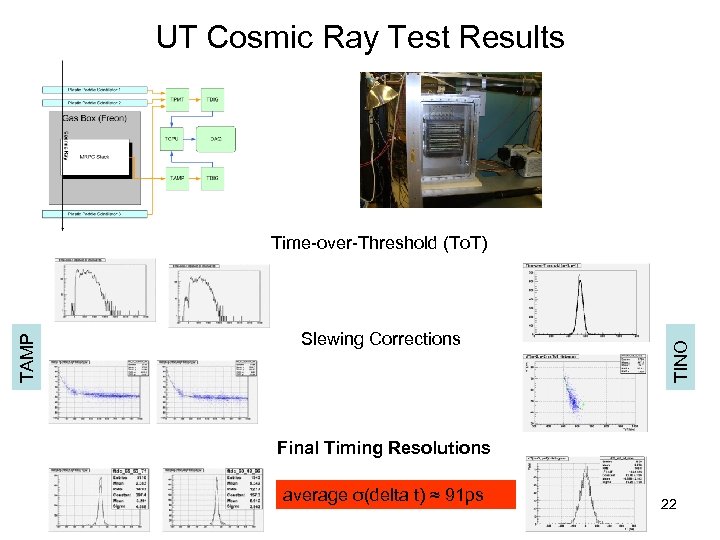

TINO Status • Motivation: Replace Maxim Amplifier & Comparator of TAMP with custom ASIC “NINO” incorporating both functions: – – Lower Cost Power (no negative supply & lower power, fewer power supplies) Fully differential: better match to HPTDC Pulse stretching: one TDC can measure both leading & trailing edge • Decision to use TINO instead of TAMP was reached in Feb 2006 based on cosmic ray testing (see following slides) with both TAMP and TINO giving similar timing resolutions • Automated TINO prototype production has been achieved, fabricated 35 circuit boards, 15 out of 15 boards successfully assembled • Minor revisions made to design and layout for part availability and assembly reasons • Mechanical compatibility with tray design verified • Will install & test 8 TINO on tray in Run 7 20

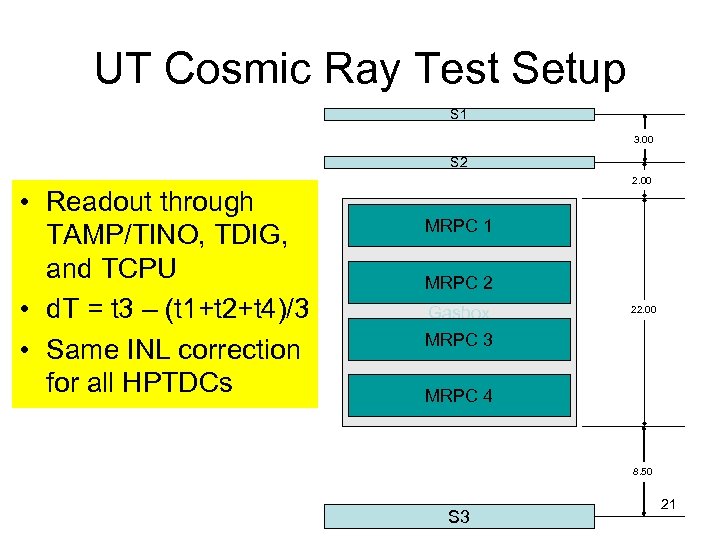

UT Cosmic Ray Test Setup S 1 3. 00 S 2 • Readout through TAMP/TINO, TDIG, and TCPU • d. T = t 3 – (t 1+t 2+t 4)/3 • Same INL correction for all HPTDCs 2. 00 MRPC 1 MRPC 2 Gasbox MRPC 3 22. 00 MRPC 4 8. 50 S 3 21

UT Cosmic Ray Test Results Slewing Corrections TINO TAMP Time-over-Threshold (To. T) Final Timing Resolutions average σ(delta t) ≈ 91 ps 22

TINO Test Plan • NINO chips were fully tested @ CERN after packaging • Confirm timing & crosstalk performance of TINO design in TDIG RFI environment • Verify input to output integrity of each PCB assembly • Verify PCB assembly, current drain • Measure, with TDIG readout, for each channel: – Threshold input voltage required to produce “ 0” discrimination threshold – Overall gain, (input discrimination level @ max. threshold) – Output pulse width “stretch” 23

TINO Test Items Needed • Power supply with accurate current metering • Pulser with – MRPC input attenuator / shaping / connector jig – PC interface (for automated testing) • Production TDIG • PC with readout / control software to implement desired degree of test automation 24

TPMD (start side FEE) • New replacement for “TPMT” to match start detector electronics to tray electronics • Design considerations: – Map 4 channels max. per HPTDC to minimize crosstalk effect – Outputs provided for (“fast”) Z-vertex FEE (not part of the TOF project) • Status: – Design and layout completed – Printed Circuit Boards and parts ordered 25

THUB Status • Needed to concentrate data before sending to DAQ in order to reduce the number of DAQ-fiber interfaces • Also provides interface to Level-2 • Prototype designed @ UT, first board delivered in April 2006 with 4 SERDES links assembled • TCPU-THUB interfaces implemented as SERDES on daughter cards; distributes trigger, clock, and resets to TCPU, receives data from TCPU • SERDES link works reliably up to ~25 feet @ 40 MHz, > 50 feet @ 20 MHz. Need about 30 feet for start detector cable run • A cable delay test performed with a TCPU clock driven by a SERDES derived clock and a Run 5 TDIG shows no difference in timing resolution. This indicates derived clock has small enough jitter to operate HPTDC reliably. • Probably use 20 MHz on SERDES link, multiply to 40 MHz on TCPU. Will try to add buffer to see if cable length at 40 MHz can be increased. 26

THUB Plans • Need another revision for final THUB – Add Level-2 interface (SIU) – Correct minor issues with prototype – Possibly place SERDES on main board (no daughter cards)? • Need about 3 weeks of circuit design work and about 4 weeks for layout of final revision • Production and assembly takes about 4 weeks (only 4 boards are needed) • Board locations on the STAR magnet have been documented within STAR • Cable runs were discussed with R. Brown • Two prototype THUB (one for East and one for West side) will be ready Nov 2006 for installation in Run 7. • Final revision of THUB is not needed until Run 8. Final design review will depend on TCPU design, probably combined with TCPU Final Design Review 27

TDIG & TCPU Status • New design for TDIG almost completed • Plan to build 4 to confirm functionality, then order about 20 for Run 7 and bench testing • TCPU design will start as soon as TDIG design is finished • Details presented in Lloyds talk • See also Geary Eppley’s talk regarding the Blue. Sky contract for these boards 28

Production & Testing 29

Schedule • TDIG Design close to being finished, prototype production to start soon. • TINO design finished and first 15 boards produced and assembled. Final production can start as soon as compatibility with new TDIG has been bench tested • TCPU R&D should be finished by Jan 07 • TPMD design finished and production of 15 cards has started. Delivery expected in 5 weeks. • THUB design should be ready for final design review in Jan 07. • Plan for a system test with all electronics components • Final Design review shortly after first TCPU prototypes have been bench tested (Jan 2007) 30

Production • TDIG production rate: ~100 boards per month. Total production should start in Dec 06 and be finished in less than 18 months (~Apr 2008) • TINO production will stay ahead of TDIG production at about the same rate • TCPU production will be in parallel to TDIG production, but need fewer boards • TPMD production can be finished with one order • THUB production can be finished in one order 31

Electronics Testing • Bare board testing and simple stuffed board testing at Vendor • Simple single board functionality testing • Test board set of 8 TINO, 8 TDIG, and TCPU (all tray electronics) as a set on a real tray top • Test installed electronics on a tray in a cosmic ray setup 32

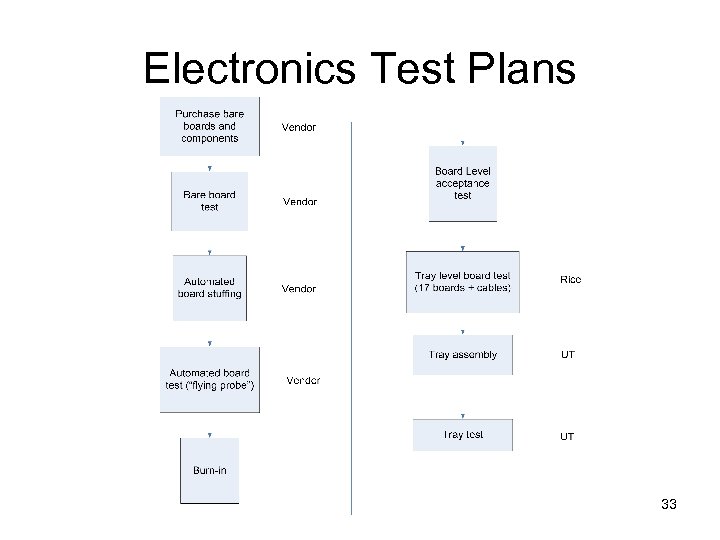

Electronics Test Plans 33

05eedc575d12f4284c257d01bb9938c4.ppt