Типы и устройство памяти вычислительных машин.ppt

- Количество слайдов: 96

Типы и устройство памяти вычислительных машин Лапина Анастасия Андреевна

Типы и устройство памяти вычислительных машин Лапина Анастасия Андреевна

Оперативная память • специальная внутренняя память ЭВМ, позволяющая быстро записывать в нее и считывать из нее необходимую информацию.

Оперативная память • специальная внутренняя память ЭВМ, позволяющая быстро записывать в нее и считывать из нее необходимую информацию.

• Информация в этой памяти хранится лишь до отключения питания компьютера, поэтому ее называют энергозависимой, временной памятью • "RAM" (Random Access Memory память произвольного доступа).

• Информация в этой памяти хранится лишь до отключения питания компьютера, поэтому ее называют энергозависимой, временной памятью • "RAM" (Random Access Memory память произвольного доступа).

• Обычно в ПК используется DRAM динамическая память. • При этом во время работы компьютера информация может постоянно обновляться.

• Обычно в ПК используется DRAM динамическая память. • При этом во время работы компьютера информация может постоянно обновляться.

• ОЗУ большинства современных компьютеров представляет собой модули динамической памя ти, содержащие полупроводниковые БИС ЗУ, организованные по принципу устройств с произвольным доступом.

• ОЗУ большинства современных компьютеров представляет собой модули динамической памя ти, содержащие полупроводниковые БИС ЗУ, организованные по принципу устройств с произвольным доступом.

• Память динамического типа дешевле, чем статического, и её плотность выше, что позволяет на том же пространстве кремниевой подложки размещать больше ячеек памяти, но при этом её быстродействие ниже.

• Память динамического типа дешевле, чем статического, и её плотность выше, что позволяет на том же пространстве кремниевой подложки размещать больше ячеек памяти, но при этом её быстродействие ниже.

• Память динамического типа дешевле, чем статического, и её плотность выше, что позволяет на том же пространстве кремниевой подложки размещать больше ячеек памяти, но при этом её быстродействие ниже. • Статическая, наоборот, более быстрая память, но она и дороже

• Память динамического типа дешевле, чем статического, и её плотность выше, что позволяет на том же пространстве кремниевой подложки размещать больше ячеек памяти, но при этом её быстродействие ниже. • Статическая, наоборот, более быстрая память, но она и дороже

• DRAM используется для хранения разряда (бита или трита)

• DRAM используется для хранения разряда (бита или трита)

• Трит — логарифмическая единица измерения в теории информации, минимальная целая единица измерения информации источников с тремя равновероятными сообщениями.

• Трит — логарифмическая единица измерения в теории информации, минимальная целая единица измерения информации источников с тремя равновероятными сообщениями.

• 1 трит равен log 23 бит ≈ 1, 585 бит.

• 1 трит равен log 23 бит ≈ 1, 585 бит.

• По аналогии с понятием Байт существует понятие Трайт. • Впервые термин использовался в ЭВМ троичной логики Сетунь 70, где он равнялся 6 тритам.

• По аналогии с понятием Байт существует понятие Трайт. • Впервые термин использовался в ЭВМ троичной логики Сетунь 70, где он равнялся 6 тритам.

• Аналогом трита в квантовых компьютерах является кутрит (q трит).

• Аналогом трита в квантовых компьютерах является кутрит (q трит).

• В оперативной памяти находятся все выполняемые в данный конкретный момент времени программы. • Элементы текстов, данных, программы и т. д. , располагаются в специальных ячейках памяти.

• В оперативной памяти находятся все выполняемые в данный конкретный момент времени программы. • Элементы текстов, данных, программы и т. д. , располагаются в специальных ячейках памяти.

• В настоящее время достаточно широко используется кэш-память (Caсhe Memory). • Она бывает внутренняя (встроенная, например, в процессор размером от 128 Кб) и внешняя.

• В настоящее время достаточно широко используется кэш-память (Caсhe Memory). • Она бывает внутренняя (встроенная, например, в процессор размером от 128 Кб) и внешняя.

• Внешняя кэш память это сверхоперативная память, расположенная как буфер между процессором и ОЗУ и повышающая производительность ПК.

• Внешняя кэш память это сверхоперативная память, расположенная как буфер между процессором и ОЗУ и повышающая производительность ПК.

• Она служит для уменьшения количества тактов ожидания процессора при обращения к более медленной RAM и имеет размер от 64 Кб до 1 Мб.

• Она служит для уменьшения количества тактов ожидания процессора при обращения к более медленной RAM и имеет размер от 64 Кб до 1 Мб.

• Ядро микросхемы динамической памяти состоит из множества ячеек, каждая из которых хранит всего один бит информации.

• Ядро микросхемы динамической памяти состоит из множества ячеек, каждая из которых хранит всего один бит информации.

• На физическом уровне ячейки объединяются в прямоугольную матрицу, горизонтальные линейки которой называются строками (ROW), а вертикальные столбцами (Column) или страницами (Page).

• На физическом уровне ячейки объединяются в прямоугольную матрицу, горизонтальные линейки которой называются строками (ROW), а вертикальные столбцами (Column) или страницами (Page).

• Линейки представляют собой обыкновенные проводники, на пересечении которых находится "сердце" ячейки несложное устройство, состоящее из одного транзистора и одного конденсатора.

• Линейки представляют собой обыкновенные проводники, на пересечении которых находится "сердце" ячейки несложное устройство, состоящее из одного транзистора и одного конденсатора.

• Конденсатору отводится роль непосредственного хранителя информации. • Правда, хранит он очень немного всего один бит.

• Конденсатору отводится роль непосредственного хранителя информации. • Правда, хранит он очень немного всего один бит.

• Отсутствие заряда на обкладках соответствует логическому нулю, а его наличие логической единице. • Транзистор же играет роль "ключа", удерживающего конденсатор от разряда.

• Отсутствие заряда на обкладках соответствует логическому нулю, а его наличие логической единице. • Транзистор же играет роль "ключа", удерживающего конденсатор от разряда.

• В спокойном состоянии транзистор закрыт. • Но, стоит подать на соответствующую строку матрицы электрический сигнал, как спустя мгновение другое он откроется, соединяя обкладку конденсатора с соответствующим ей столбцом.

• В спокойном состоянии транзистор закрыт. • Но, стоит подать на соответствующую строку матрицы электрический сигнал, как спустя мгновение другое он откроется, соединяя обкладку конденсатора с соответствующим ей столбцом.

• Чувствительный усилитель (sense amp), подключенный к каждому из столбцов матрицы, реагируя на слабый поток электронов, устремившихся через открытые транзисторы с обкладок конденсаторов, считывает всю страницу целиком.

• Чувствительный усилитель (sense amp), подключенный к каждому из столбцов матрицы, реагируя на слабый поток электронов, устремившихся через открытые транзисторы с обкладок конденсаторов, считывает всю страницу целиком.

• Именно страница является минимальной порцией обмена с ядром динамической памяти. • Чтение/запись отдельно взятой ячейки невозможно

• Именно страница является минимальной порцией обмена с ядром динамической памяти. • Чтение/запись отдельно взятой ячейки невозможно

• Открытие одной строки приводит к открытию всех, подключенных к ней транзисторов, а, следовательно, разряду закрепленных за этими транзисторами конденсаторов.

• Открытие одной строки приводит к открытию всех, подключенных к ней транзисторов, а, следовательно, разряду закрепленных за этими транзисторами конденсаторов.

• Чтение ячейки деструктивно по своей природе, поскольку sense amp (чувствительный усилитель) разряжает конденсатор в процессе считывания его заряда. • "Благодаря" этому динамическая память представляет собой память разового действия.

• Чтение ячейки деструктивно по своей природе, поскольку sense amp (чувствительный усилитель) разряжает конденсатор в процессе считывания его заряда. • "Благодаря" этому динамическая память представляет собой память разового действия.

• Ввиду микроскопических размеров, а, следовательно, емкости конденсатора записанная на нем информация хранится крайне недолго, буквально сотые, а то тысячные доли секунды. • Причина тому саморазряд конденсатора.

• Ввиду микроскопических размеров, а, следовательно, емкости конденсатора записанная на нем информация хранится крайне недолго, буквально сотые, а то тысячные доли секунды. • Причина тому саморазряд конденсатора.

• Для борьбы с "забывчивостью" памяти прибегают к ее регенерации периодическому считыванию ячеек с последующей перезаписью.

• Для борьбы с "забывчивостью" памяти прибегают к ее регенерации периодическому считыванию ячеек с последующей перезаписью.

• В зависимости от конструктивных особенностей "регенератор" может находиться как в контроллере, так и в самой микросхеме памяти.

• В зависимости от конструктивных особенностей "регенератор" может находиться как в контроллере, так и в самой микросхеме памяти.

• В первую очередь выделим среди них линии адреса и линии данных. • Линии адреса, как и следует из их названия, служат для выбора адреса ячейки памяти, а линии данных для чтения и для записи ее содержимого.

• В первую очередь выделим среди них линии адреса и линии данных. • Линии адреса, как и следует из их названия, служат для выбора адреса ячейки памяти, а линии данных для чтения и для записи ее содержимого.

• Необходимый режим работы определяется состоянием специального вывода Write Enable (Разрешение Записи).

• Необходимый режим работы определяется состоянием специального вывода Write Enable (Разрешение Записи).

• Низкий уровень сигнала WE готовит микросхему к считыванию состояния линий данных и записи полученной информации в соответствующую ячейку.

• Низкий уровень сигнала WE готовит микросхему к считыванию состояния линий данных и записи полученной информации в соответствующую ячейку.

• Высокий, наоборот, заставляет Высокий считать содержимое ячейки и "выплюнуть" его значения в линии данных.

• Высокий, наоборот, заставляет Высокий считать содержимое ячейки и "выплюнуть" его значения в линии данных.

Эволюция динамической памяти. • Оперативная память персональных компьютеров сегодня, как и десять лет тому назад, строится на базе относительно недорогой динамической памяти DRAM (Dynamic Random Access Memory).

Эволюция динамической памяти. • Оперативная память персональных компьютеров сегодня, как и десять лет тому назад, строится на базе относительно недорогой динамической памяти DRAM (Dynamic Random Access Memory).

DIP • DIP корпус это исторически самая древняя реализация DRAM. • DIP корпус соответствует стандарту IC.

DIP • DIP корпус это исторически самая древняя реализация DRAM. • DIP корпус соответствует стандарту IC.

• Обычно это маленький черный корпус из пластмассы, по обеим сторонам которого располагаются металлические контакты.

• Обычно это маленький черный корпус из пластмассы, по обеим сторонам которого располагаются металлические контакты.

• Микросхемы (по другому, чипы) динамического ОЗУ устанавливаются так называемыми банками. • Банки бывают на 64, 256 Кбайт, 1 и 4 Мбайт.

• Микросхемы (по другому, чипы) динамического ОЗУ устанавливаются так называемыми банками. • Банки бывают на 64, 256 Кбайт, 1 и 4 Мбайт.

• Каждый банк состоит из девяти отдельных одинаковых чипов. • Из них восемь чипов предназначены для хранения информации, а девятый чип служит для проверки четности остальных восьми микросхем этого банка.

• Каждый банк состоит из девяти отдельных одинаковых чипов. • Из них восемь чипов предназначены для хранения информации, а девятый чип служит для проверки четности остальных восьми микросхем этого банка.

SIPP (SIP) —модули памяти • Эти модули представляют собой маленькие платы с несколькими напаянными микросхемами DRAM.

SIPP (SIP) —модули памяти • Эти модули представляют собой маленькие платы с несколькими напаянными микросхемами DRAM.

• SIPP является сокращением слов Single Inline Package. • SIPP модули соединяются с системной платой с помощью контактных штырьков.

• SIPP является сокращением слов Single Inline Package. • SIPP модули соединяются с системной платой с помощью контактных штырьков.

• Под контактной колодкой находятся 30 маленьких штырьков, которые вставляются в соответствующую панель системной платы. • Модули SIPP имели определенные вырезы, которые не позволяли вставить их в разъемы неправильным образом.

• Под контактной колодкой находятся 30 маленьких штырьков, которые вставляются в соответствующую панель системной платы. • Модули SIPP имели определенные вырезы, которые не позволяли вставить их в разъемы неправильным образом.

SIMM-модули. • Single Inline Memory Module (Модуль памяти с однорядным расположением выводов. ) Он включает в себя все то, что для DIP называлось банком.

SIMM-модули. • Single Inline Memory Module (Модуль памяти с однорядным расположением выводов. ) Он включает в себя все то, что для DIP называлось банком.

• Модули SIMM могут иметь объем 256 Кбайт, 1, 2, 4, 8, 16 и 32 Мбайт. Соединение SIMM модулей с системной платой осуществляется с помощью колодок.

• Модули SIMM могут иметь объем 256 Кбайт, 1, 2, 4, 8, 16 и 32 Мбайт. Соединение SIMM модулей с системной платой осуществляется с помощью колодок.

DIMM • Dual Inline Memory Module (Модуль памяти с двойным расположением выводов). • В модуле DIMM имеется 168 контактов, которые расположены с двух сторон платы и разделены изолятором. Также изменились и разъемы для DIMM модулей.

DIMM • Dual Inline Memory Module (Модуль памяти с двойным расположением выводов). • В модуле DIMM имеется 168 контактов, которые расположены с двух сторон платы и разделены изолятором. Также изменились и разъемы для DIMM модулей.

• Следует отметить, что разъем DIMM имеют много разновидностей DRAM. К тому же вплоть до последнего времени модули DIMM не имели средств самоконфигурирования (в отличие от SIMM модулей).

• Следует отметить, что разъем DIMM имеют много разновидностей DRAM. К тому же вплоть до последнего времени модули DIMM не имели средств самоконфигурирования (в отличие от SIMM модулей).

• Поэтому для облегчения выбора нужного модуля пользователям на материнских платах разные типы DIMM имеют от одного до трех вырезов на модуле памяти.

• Поэтому для облегчения выбора нужного модуля пользователям на материнских платах разные типы DIMM имеют от одного до трех вырезов на модуле памяти.

SDRAM. • Synchronic DRAM (динамическое ОЗУ с синхронным интерфейсом). • Этим они отличаются от FPM и EDO DRAM, работающих по асинхронному интерфейсу.

SDRAM. • Synchronic DRAM (динамическое ОЗУ с синхронным интерфейсом). • Этим они отличаются от FPM и EDO DRAM, работающих по асинхронному интерфейсу.

• Микросхемы SDRAM работают синхронно с контроллером, что гарантирует завершение цикла в строго заданный срок. • Кроме того, номера строк и столбцов подаются одновременно, с таким расчетом, чтобы к приходу следующего тактового импульса сигналы уже успели стабилизироваться и были готовы к считыванию.

• Микросхемы SDRAM работают синхронно с контроллером, что гарантирует завершение цикла в строго заданный срок. • Кроме того, номера строк и столбцов подаются одновременно, с таким расчетом, чтобы к приходу следующего тактового импульса сигналы уже успели стабилизироваться и были готовы к считыванию.

• С асинхронным интерфейсом процессор должен ожидать, пока DRAM закончит выполнение своих внутренних операций. • Они обычно занимают 60 нс.

• С асинхронным интерфейсом процессор должен ожидать, пока DRAM закончит выполнение своих внутренних операций. • Они обычно занимают 60 нс.

• В DRAM с синхронным управлением происходит защелкивание информации от процессора под управлением системных часов. • Триггеры запоминают адреса, сигналы управления и данных.

• В DRAM с синхронным управлением происходит защелкивание информации от процессора под управлением системных часов. • Триггеры запоминают адреса, сигналы управления и данных.

• Другое преимущество синхронного интерфейса это то, что системные часы задают временные границы, необходимые DRAM.

• Другое преимущество синхронного интерфейса это то, что системные часы задают временные границы, необходимые DRAM.

• Это, во первых, уменьшает трафик по локальной шине (нет “лишних” сигналов) • Во вторых, позволяет упростить операции ввода вывода (в операциях пересылки центральный процессор либо контроллер DMA уже не должен выделять полезную информацию среди служебных импульсов и битов четности)

• Это, во первых, уменьшает трафик по локальной шине (нет “лишних” сигналов) • Во вторых, позволяет упростить операции ввода вывода (в операциях пересылки центральный процессор либо контроллер DMA уже не должен выделять полезную информацию среди служебных импульсов и битов четности)

• В третьих, все операции ввода/вывода на локальной шине стали управляться одними и теми же синхроимпульсами, что само по себе хорошо.

• В третьих, все операции ввода/вывода на локальной шине стали управляться одними и теми же синхроимпульсами, что само по себе хорошо.

• В SDRAM реализован усовершенствованный пакетный режим обмена. • Контроллер может запросить как одну, так и несколько последовательных ячеек памяти, а при желании всю строку целиком. • Это стало возможным благодаря использованию полноразрядного адресного счетчика.

• В SDRAM реализован усовершенствованный пакетный режим обмена. • Контроллер может запросить как одну, так и несколько последовательных ячеек памяти, а при желании всю строку целиком. • Это стало возможным благодаря использованию полноразрядного адресного счетчика.

• Количество матриц (банков) памяти в SDRAM увеличено с одного до двух (четырех). • Это позволяет обращаться к ячейкам одного банка параллельно с перезарядкой внутренних цепей другого, что вдвое увеличивает предельно допустимую тактовую частоту. • Разрядность шины данных увеличилась с 32 до 64 бит, что еще вдвое увеличило ее производительность.

• Количество матриц (банков) памяти в SDRAM увеличено с одного до двух (четырех). • Это позволяет обращаться к ячейкам одного банка параллельно с перезарядкой внутренних цепей другого, что вдвое увеличивает предельно допустимую тактовую частоту. • Разрядность шины данных увеличилась с 32 до 64 бит, что еще вдвое увеличило ее производительность.

Rambus (RDRAM, RIMM) • RDRAM представляет собой спецификацию, созданную и запатентованную фирмой Rambus, Inc. За счет использования обоих границ сигнала достигается частота работы памяти в 800 МГц.

Rambus (RDRAM, RIMM) • RDRAM представляет собой спецификацию, созданную и запатентованную фирмой Rambus, Inc. За счет использования обоих границ сигнала достигается частота работы памяти в 800 МГц.

• Один канал Direct Rambus максимум может поддерживать 32 чипа DRDRAM. • На материнской плате может использоваться до трех RIMM модулей. Используются 64 Мбит, 128 Мбит и 256 Мбит устройства.

• Один канал Direct Rambus максимум может поддерживать 32 чипа DRDRAM. • На материнской плате может использоваться до трех RIMM модулей. Используются 64 Мбит, 128 Мбит и 256 Мбит устройства.

Основных отличий от памяти предыдущих поколений всего три: • увеличение тактовой частоты за счет сокращения разрядности шины; • одновременная передача номеров строки и столба ячейки; • увеличение количества банков для усиления параллелизма.

Основных отличий от памяти предыдущих поколений всего три: • увеличение тактовой частоты за счет сокращения разрядности шины; • одновременная передача номеров строки и столба ячейки; • увеличение количества банков для усиления параллелизма.

• Чтобы расширить память сверх 32 х устройств, могут использоваться два чипа повторителя. • С одним повторителем канал может поддерживать 64 устройства с 6 ю RIMM модулями, а с двумя 128 устройств на 12 модулях.

• Чтобы расширить память сверх 32 х устройств, могут использоваться два чипа повторителя. • С одним повторителем канал может поддерживать 64 устройства с 6 ю RIMM модулями, а с двумя 128 устройств на 12 модулях.

• Организация и режимы работы памяти IMB-совместимых ПЭВМ.

• Организация и режимы работы памяти IMB-совместимых ПЭВМ.

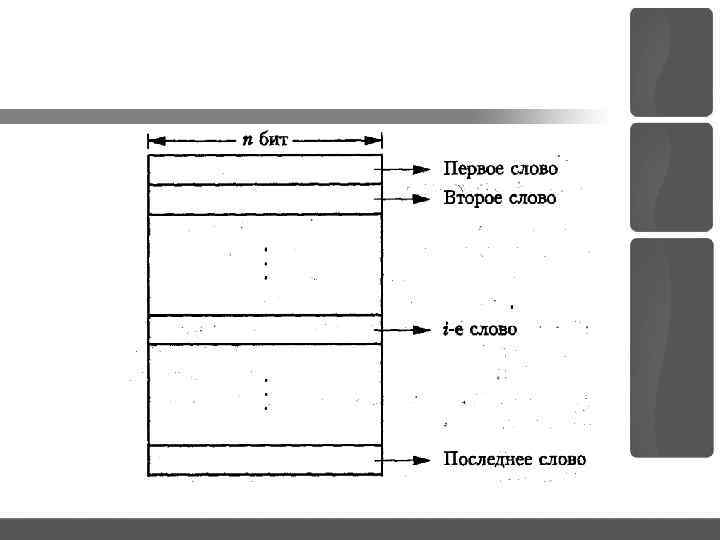

• Память состоит из многих миллионов ячеек, в каждой из которых содержится один бит информации, имеющий значение 0 или 1.

• Память состоит из многих миллионов ячеек, в каждой из которых содержится один бит информации, имеющий значение 0 или 1.

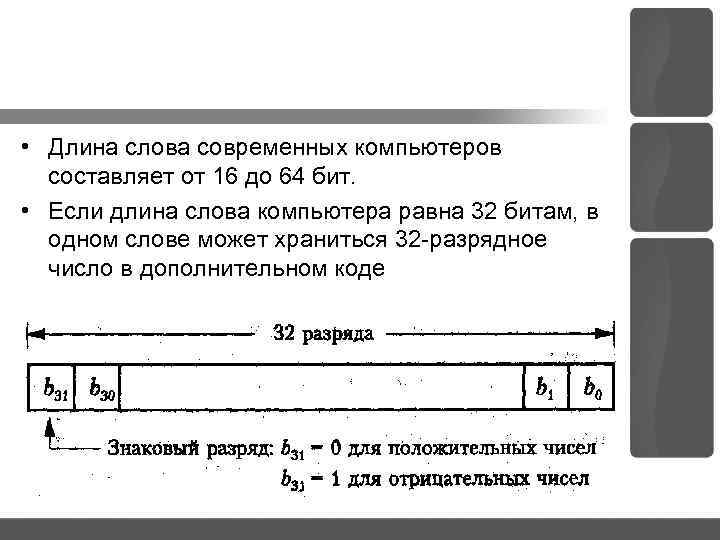

• Длина слова современных компьютеров составляет от 16 до 64 бит. • Если длина слова компьютера равна 32 битам, в одном слове может храниться 32 разрядное число в дополнительном коде

• Длина слова современных компьютеров составляет от 16 до 64 бит. • Если длина слова компьютера равна 32 битам, в одном слове может храниться 32 разрядное число в дополнительном коде

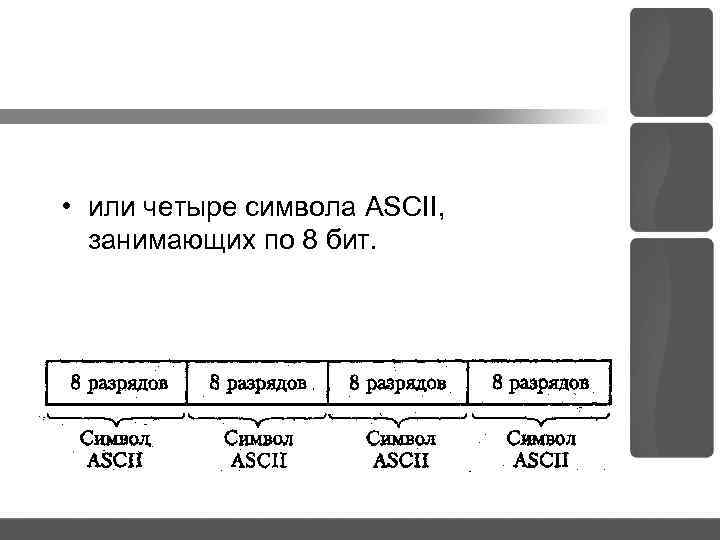

• или четыре символа ASCII, занимающих по 8 бит.

• или четыре символа ASCII, занимающих по 8 бит.

• Восемь идущих подряд битов называются байтом. • Для пред ставления машинной команды требуется одно или несколько слов.

• Восемь идущих подряд битов называются байтом. • Для пред ставления машинной команды требуется одно или несколько слов.

• Для доступа к памяти с целью записи или чтения отдельных элементов информации, будь то слова или байты, необходимы имена или адреса, определяющие их расположение в памяти.

• Для доступа к памяти с целью записи или чтения отдельных элементов информации, будь то слова или байты, необходимы имена или адреса, определяющие их расположение в памяти.

• В качестве адресов традиционно используются числа из диапазона от 0 до 2^k 1 со значением k, достаточным для адресации всей памяти компьютера.

• В качестве адресов традиционно используются числа из диапазона от 0 до 2^k 1 со значением k, достаточным для адресации всей памяти компьютера.

• Все 2^k адресов составляют адресное пространство компьютера. • Следовательно, память состоит из 2^k адресуемых элементов.

• Все 2^k адресов составляют адресное пространство компьютера. • Следовательно, память состоит из 2^k адресуемых элементов.

• Например, использование 24 разрядных (как в процессоре 80286) адресов позволяет адресовать 2^24 (16777216) элементов памяти.

• Например, использование 24 разрядных (как в процессоре 80286) адресов позволяет адресовать 2^24 (16777216) элементов памяти.

• Обычно это количество адресуемых элементов обозначается как 16 М (16 мега), где 1 М – 2^20 (1048576) (адресное пространство МП 8086 и 80186)

• Обычно это количество адресуемых элементов обозначается как 16 М (16 мега), где 1 М – 2^20 (1048576) (адресное пространство МП 8086 и 80186)

Байтовая адресация Итак, у нас есть три основные единицы информации: бит, байт и слово. • Байт всегда равен 8 битам • Длина слова обычно колеблется от 16 до 64 бит • Отдельные биты, как правило, не адресуются

Байтовая адресация Итак, у нас есть три основные единицы информации: бит, байт и слово. • Байт всегда равен 8 битам • Длина слова обычно колеблется от 16 до 64 бит • Отдельные биты, как правило, не адресуются

• Чаще всего адреса назначаются байтам памяти. • Именно так адресуется память большинства современных компьютеров, и именно этот способ адресации мы будем использовать.

• Чаще всего адреса назначаются байтам памяти. • Именно так адресуется память большинства современных компьютеров, и именно этот способ адресации мы будем использовать.

• Память, в которой каждый байт имеет отдельный адрес, называется памятью с байтовой адресацией. • Последовательные байты имеют адреса 0, 1, 2 и т. д.

• Память, в которой каждый байт имеет отдельный адрес, называется памятью с байтовой адресацией. • Последовательные байты имеют адреса 0, 1, 2 и т. д.

• При использовании слов длиной 32 бита последовательные слова имеют адреса 1, 4, 8, . . . , и каждое слово состоит из 4 байт.

• При использовании слов длиной 32 бита последовательные слова имеют адреса 1, 4, 8, . . . , и каждое слово состоит из 4 байт.

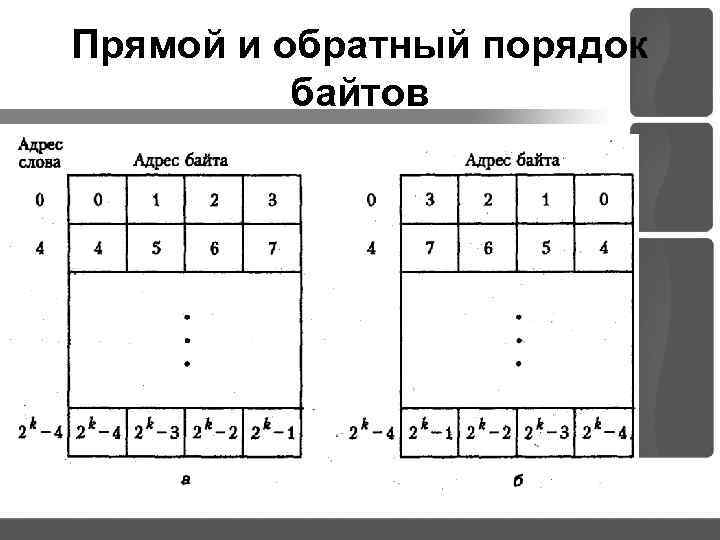

Прямой и обратный порядок байтов

Прямой и обратный порядок байтов

• Обратным порядком байтов (big endian) называется система адресации, при которой байты адресуются слева направо, так что самый старший байт слова (расположенный с левого края) имеет наименьший адрес.

• Обратным порядком байтов (big endian) называется система адресации, при которой байты адресуются слева направо, так что самый старший байт слова (расположенный с левого края) имеет наименьший адрес.

• Прямым порядком байтов (little endian) называется противоположная система адресации, при которой байты адресуются справа налево, так что наименьший адрес имеет самый младший байт слова (расположенный с правого края)

• Прямым порядком байтов (little endian) называется противоположная система адресации, при которой байты адресуются справа налево, так что наименьший адрес имеет самый младший байт слова (расположенный с правого края)

• Слова «старший» и «младший» определяют вес бита, то есть степень двойки, соответствующей данному биту, когда слово представляет число.

• Слова «старший» и «младший» определяют вес бита, то есть степень двойки, соответствующей данному биту, когда слово представляет число.

• В обеих этих системах адреса байтов 0, 4, 8 и т. д. применяются в качестве адресов последовательных слов памяти в операциях чтения и записи слов

• В обеих этих системах адреса байтов 0, 4, 8 и т. д. применяются в качестве адресов последовательных слов памяти в операциях чтения и записи слов

• Наряду с порядком байтов в слове важно также определить порядок битов в байте. • Наиболее естественный порядок битов для кодирования числовых данных (непосредственно соответствующий их разрядам) «слева направо» : b 32, …. , b 1, b 0. • Однако существуют компьютеры, для которых характерен обратный порядок битов.

• Наряду с порядком байтов в слове важно также определить порядок битов в байте. • Наиболее естественный порядок битов для кодирования числовых данных (непосредственно соответствующий их разрядам) «слева направо» : b 32, …. , b 1, b 0. • Однако существуют компьютеры, для которых характерен обратный порядок битов.

Расположение слов в памяти • В случае 32 разрядных слов их естественные границы располагаются по адресам 0, 4, 8 и т. д. • При этом мы говорим, что слова выровнены по адресам в памяти.

Расположение слов в памяти • В случае 32 разрядных слов их естественные границы располагаются по адресам 0, 4, 8 и т. д. • При этом мы говорим, что слова выровнены по адресам в памяти.

• Если говорить в общем, слова считаются выровненными в памяти в том случае, если адрес начала каждого слова кратен количеству байтов в нем.

• Если говорить в общем, слова считаются выровненными в памяти в том случае, если адрес начала каждого слова кратен количеству байтов в нем.

• По практическим причинам, связанным с манипулированием двоично кодирован ными адресами, количество байтов в слове обычно является степенью двойки.

• По практическим причинам, связанным с манипулированием двоично кодирован ными адресами, количество байтов в слове обычно является степенью двойки.

• Если длина слова равна 16 бит (2 байтам), выровненные слова начинаются по байтовым адресам 0, 2, 4, . . . • А если она равна 64 бит (т. е. 8 байтам), то выровненные слова начинаются по байтовым адресам 0, 8, 16, . .

• Если длина слова равна 16 бит (2 байтам), выровненные слова начинаются по байтовым адресам 0, 2, 4, . . . • А если она равна 64 бит (т. е. 8 байтам), то выровненные слова начинаются по байтовым адресам 0, 8, 16, . .

• Не существует причины, по которой слова не могли бы начинаться с произвольных адресов. • Такие слова называются невыровненными. • Как правило, слова выравниваются по адресам памяти, но иногда этот принцип нарушатся.

• Не существует причины, по которой слова не могли бы начинаться с произвольных адресов. • Такие слова называются невыровненными. • Как правило, слова выравниваются по адресам памяти, но иногда этот принцип нарушатся.

Доступ к числам, символам и символьным строкам • Обычно число занимает целое слово. • Поэтому, для того чтобы обратиться к нему в памяти, нужно указать адрес слова, по которому оно, это число, хранится.

Доступ к числам, символам и символьным строкам • Обычно число занимает целое слово. • Поэтому, для того чтобы обратиться к нему в памяти, нужно указать адрес слова, по которому оно, это число, хранится.

• Точно так же доступ к отдельно хранящемуся в памяти символу осуществляется по адресу его байта.

• Точно так же доступ к отдельно хранящемуся в памяти символу осуществляется по адресу его байта.

• Во многих приложениях необходимо обрабатывать строки символов переменной длины. • Для доступа к такой строке нужно указать адрес байта, в котором хра нится ее первый символ.

• Во многих приложениях необходимо обрабатывать строки символов переменной длины. • Для доступа к такой строке нужно указать адрес байта, в котором хра нится ее первый символ.

• Последовательные символы строки содержатся в последовательных байтах. • Существует два способа определения длины строки.

• Последовательные символы строки содержатся в последовательных байтах. • Существует два способа определения длины строки.

• Первый из них заключается в использовании специального управляющего символа, обозначающего конец строки и являющегося ее последним символом.

• Первый из них заключается в использовании специального управляющего символа, обозначающего конец строки и являющегося ее последним символом.

• Второй способ состоит в использовании отдельного слова памяти или регистра процессора, содержащего число, которое определяет длину строки в байтах

• Второй способ состоит в использовании отдельного слова памяти или регистра процессора, содержащего число, которое определяет длину строки в байтах

Операции с памятью • И команды программ, и данные, являющиеся операндами этих команд, хранятся в памяти. • Для выполнения команды управляющие схемы процессора должны инициировать пересылку содержащего ее слова или слов из памяти в процессор.

Операции с памятью • И команды программ, и данные, являющиеся операндами этих команд, хранятся в памяти. • Для выполнения команды управляющие схемы процессора должны инициировать пересылку содержащего ее слова или слов из памяти в процессор.

10010101100110

10010101100110

• Операнды и результаты также должны пересылаться между памятью и про цессором. • Таким образом, для выполнения команды программы необходимо произвести две операции с памятью:

• Операнды и результаты также должны пересылаться между памятью и про цессором. • Таким образом, для выполнения команды программы необходимо произвести две операции с памятью:

• Load (или Read, или Fetch), то есть загрузка (или чтение, или выборка соответственно) • Store (или Write), то есть сохранение (или запись).

• Load (или Read, или Fetch), то есть загрузка (или чтение, или выборка соответственно) • Store (или Write), то есть сохранение (или запись).