RISC(Основная).ppt

- Количество слайдов: 18

Типы архитектуры микропроцессора по набору команд: RISC- и CISC – процессоры.

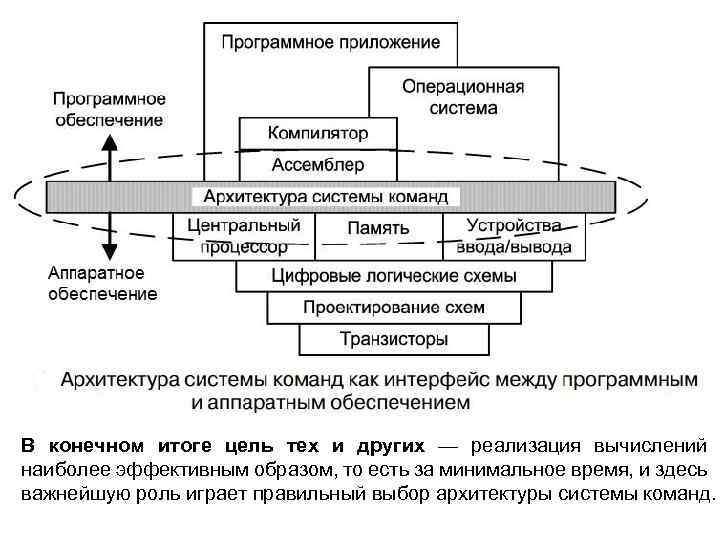

Системой команд вычислительной машины называют полный перечень команд, которые способна выполнять данная ВМ. В свою очередь, под архитектурой системы команд (АСК) принято определять те средства вычислительной машины, которые видны и доступны программисту. АСК можно рассматривать как линию согласования нужд разработчиков программного обеспечения с возможностями создателей аппаратуры вычислительной машины.

В конечном итоге цель тех и других — реализация вычислений наиболее эффективным образом, то есть за минимальное время, и здесь важнейшую роль играет правильный выбор архитектуры системы команд.

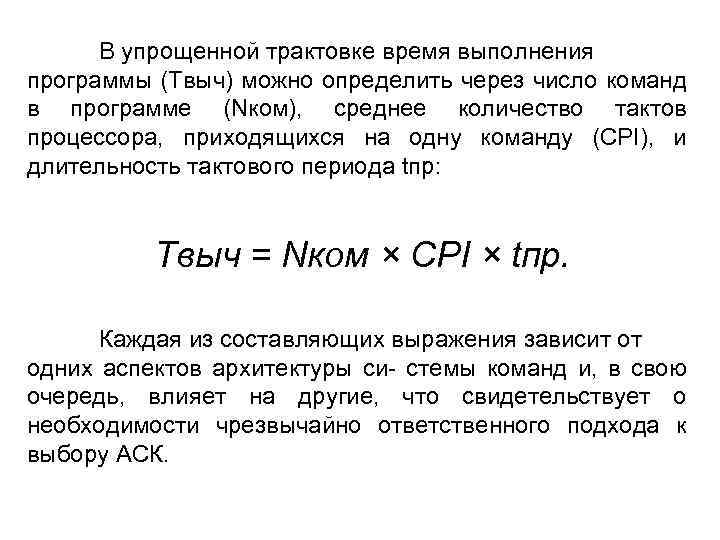

В упрощенной трактовке время выполнения программы (Tвыч) можно определить через число команд в программе (Nком), среднее количество тактов процессора, приходящихся на одну команду (CPI), и длительность тактового периода tпр: Tвыч = Nком × CPI × tпр. Каждая из составляющих выражения зависит от одних аспектов архитектуры си- стемы команд и, в свою очередь, влияет на другие, что свидетельствует о необходимости чрезвычайно ответственного подхода к выбору АСК.

Аккумуляторная архитектура В АА для хранения одного из операндов арифметической или логической операции в процессоре имеется выделенный регистр — аккумулятор. В этот же регистр заносится и результат операции. Поскольку адрес одного из операндов предопределен, в командах обработки достаточно явно указать местоположение только второго операнда. Изначально оба операнда хранятся в основной памяти, и до выполнения операции один из них нужно загрузить в аккумулятор. После выполнения команды результат заносится в аккумулятор, и если этот результат не является операндом для последующей команды, то его требуется сохранить в ячейке памяти. Для загрузки в аккумулятор содержимого ячейки x предусмотрена команда загрузки load x. По этой команде информация считывается из ячейки памяти x, выход памяти подключается ко входам аккумулятора, и происходит занесение считанных данных в аккумулятор. Запись содержимого аккумулятора в ячейку x осуществляется командой сохранения store x, при выполнении которой выходы аккумулятора подключаются к шине, после чего информация с шины записывается в память.

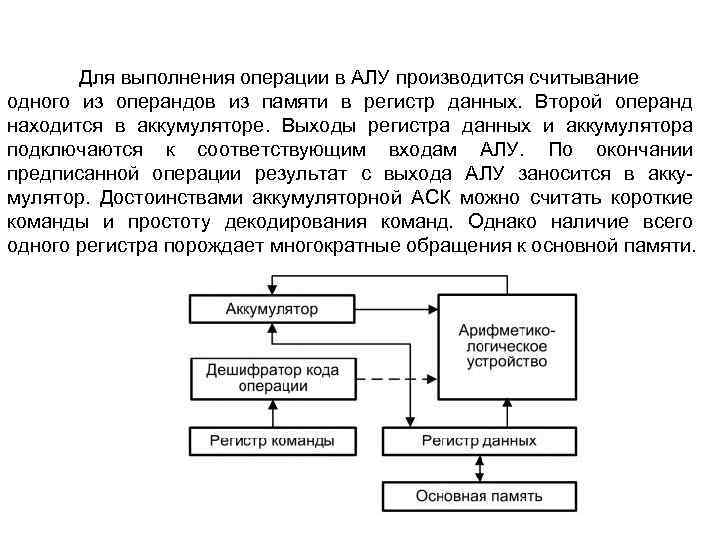

Для выполнения операции в АЛУ производится считывание одного из операндов из памяти в регистр данных. Второй операнд находится в аккумуляторе. Выходы регистра данных и аккумулятора подключаются к соответствующим входам АЛУ. По окончании предписанной операции результат с выхода АЛУ заносится в аккумулятор. Достоинствами аккумуляторной АСК можно считать короткие команды и простоту декодирования команд. Однако наличие всего одного регистра порождает многократные обращения к основной памяти.

Регистровая архитектура В машинах данного типа процессор включает в себя массив регистров общего назначения (РОН). Разрядность регистров обычно совпадает с размером машинного слова. К любому регистру можно обратиться, указав его номер. Регистровая архитектура допускает расположение операндов как в регистрах, так и в основной памяти, поэтому в рамках данной АСК выделяют три формата команд обработки: 1) регистр-регистр (операнды могут находиться только в регистрах. В них же засылается и результат. ) 2)регистр-память (предполагает, что один из операндов размещается в регистре, а второй в основной памяти. Результат обычно замещает один из операндов. ) 3) память-память (в командах формата «память-память» оба операнда хранятся в основной памяти. Результат заносится в память. )

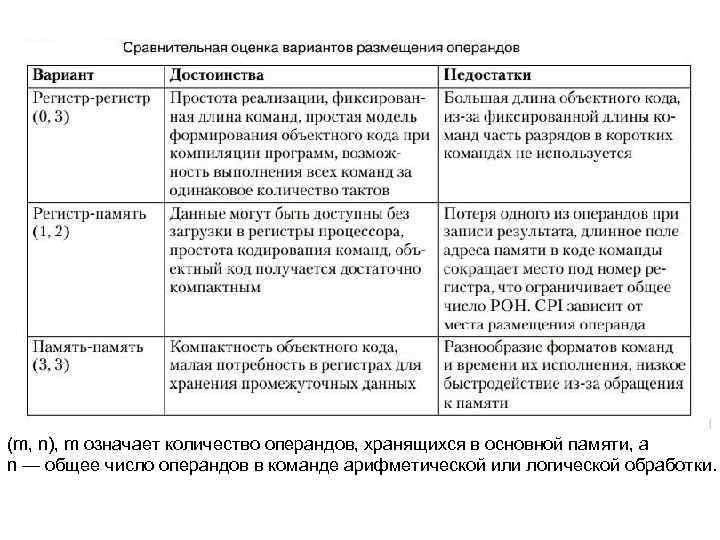

(m, n), m означает количество операндов, хранящихся в основной памяти, а n — общее число операндов в команде арифметической или логической обработки.

Основные черты CISCархитектур • В основе архитектуры CISC (Complex Instruction Set Computer) лежит эффективное использование памяти и относительная простота ассемблерного программирования (но достаточно сложная аппаратная реализация). • Каждая команда CISC-процессора включает в себя несколько операций. Это уменьшает количество операторов, требующихся для реализации конкретной программы, и предоставляет для программиста удобный и быстрый набор команд. Для CISC-процессоров характерны следующие черты:

• Большое число машинных команд • Большое количество методов адресации памяти, включая специализированные способы индексации с помощью массивов. • Формат команд: операция и два операнда: источник и адрес результата. • Команды переменной длины, длина часто меняется в зависимости от способа адресации. • Команды обмена типа Р-П, П-Р, Р-Р. • Небольшое количество (8 -12) РОН. Это результат наличия команд, оперирующих непосредственно с памятью и ограниченности места на микросхеме, предназначенных для целей, отличных от декодирования и исполнения команд и хранения микрокоманд. • Микропрограммная реализация набора команд.

Проблемы и недостатки CISCархитектур • Усложнение набора команд и аппаратной реализации с каждым новым поколением компьютеров. • Различным командам для выполнения требуется разное количество машинных тактов. • Многоформатность команд. Обмен с памятью в процессе выполнения команды делает практически невозможной глубокую конвейеризацию арифметики, т. е. ограничивается тактовая частота процессора, а значит, и его производительность. Большинство современных компьютеров типа IBM PC относятся к CISC архитектуре. Возникновение RISC-архитектур • Прорыв в схематехнике. • Семантический разрыв. Эта проблема возникла перехода к ЯВУ: сложные операторы, характерные для ЯВУ, существенно отличаются от простых машинных операций, реализуемых в большинстве ВМ.

Идея RISC-архитектуры Основная идея RISC-архитектуры состояла в том, что последовательность простых команд, давая тот же результат, что и последовательность составных команд, может выполняться на более простой физической архитектуре процессора. CISC-процессоры проектировались под нужды asm-программистов, RISC-процессоры проектировались в расчете на типовой код, генерируемый компилятором.

Реализация RISC-архитектур Результаты глубокого анализа показали, что основные усилия должны быть направлены на • упрощение набора команд, • эффективную реализацию конвейерной обработки путем тщательного планирования компилятором его загрузки -- отделение медленной памяти от быстрой памяти (высокоскоростных регистров) (две инструкции Load/Store), -- использование регистровых окон.

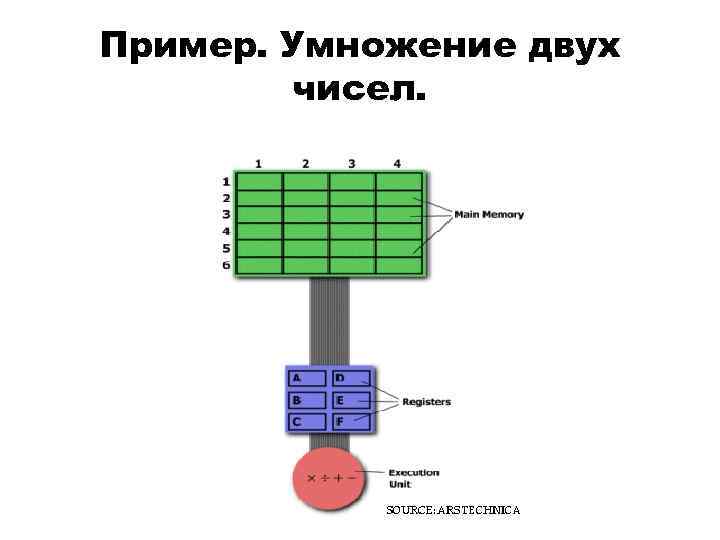

Пример. Умножение двух чисел.

Две реализации умножения двух чисел • The CISC Approach • The RISC Approach MULT 2: 3, 5: 2 LOAD A, 2: 3 LOAD B, 5: 2 PROD A, B STORE 2: 3, A

Характеристики RISCархитектур • Время выполнения большинства команд составляет один машинный такт. • Простые команды (аппаратная реализация). • Все команды имеют одинаковую длину так, что каждая команда может быть исполнена за один такт применения микропрограмм. • Набор команд обычно включает в среднем 128 наиболее часто используемых команд. • Небольшое число способов адресации (4). • Операнды располагаются в регистрах. Стек памяти редко используется для передачи параметров процедур, вместо этого используются регистры. • Формат чаще трехадресный: команда берет операнды из двух регистров и помещает результат в третий регистр. • Доступ к памяти только посредством команд Чтение и Запись. • Все операции, кроме Чтения и Записи, имеют тип Р-Р. • Устройство управления с жесткой логикой. • Большой файл регистров общего назначения.

Сравнение архитектур • CISC - Акцент на оборудование Операции обработки данных реализуются только в формате «память - память» . Исполнение операций, таких как загрузка в память, арифметические действия кодируется в одной инструкции. - Многобайтовые команды Нефиксированным значением длины команды. Сложные команды Одна или менее команд за один цикл процессора - • RISC - - Акценкт на програмное обеспечение Операции обработки данных реализуются только в формате «регистр - регистр» (операнды выбираются из оперативных регистров процессора, и результат операции записывается также в регистр; а обмен между оперативными регистрами и памятью выполняется только с помощью команд загрузки/записи). Однобайтовые команды Фиксированная длина машинных инструкций (например, 32 бита) и простой формат команды. Простые команды Несколько команд за один цикл процессора

RISC(Основная).ppt