af99b8df7a0e2e73b8a4cd21cde86502.ppt

- Количество слайдов: 27

The Tablet PC at Five Chuck Thacker Distinguished Engineer Microsoft Corporation July 20, 2005

Talk outline • • Tablet history The Tablet today Tablet futures Limits on computers – What Moore actually said. – Implications for computers. – Other limits • What about software? • Conclusions

Prehistory – before 2000 • Lots of earlier attempts – mostly failures. – DEC, Go, Newton, Pen Windows • Technology wasn’t ready • But vertical markets had limited success. • Needed: better UI, better handwriting recognition (without relying on it). • Key: Better digitizer (with hover).

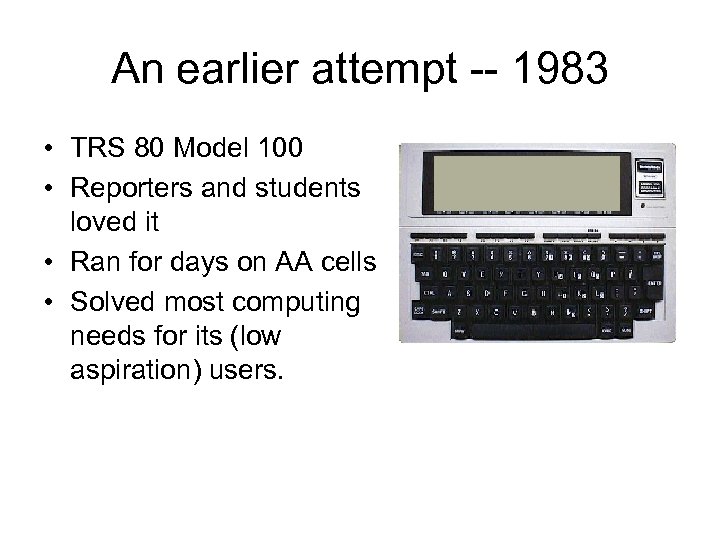

An earlier attempt -- 1983 • TRS 80 Model 100 • Reporters and students loved it • Ran for days on AA cells • Solved most computing needs for its (low aspiration) users.

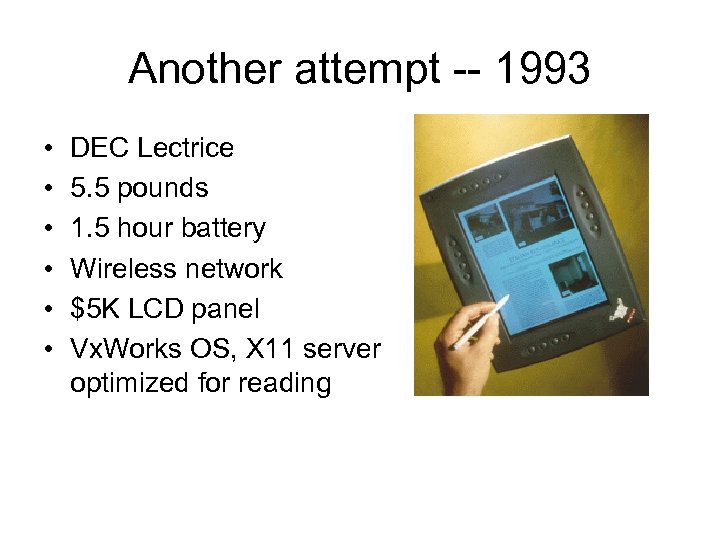

Another attempt -- 1993 • • • DEC Lectrice 5. 5 pounds 1. 5 hour battery Wireless network $5 K LCD panel Vx. Works OS, X 11 server optimized for reading

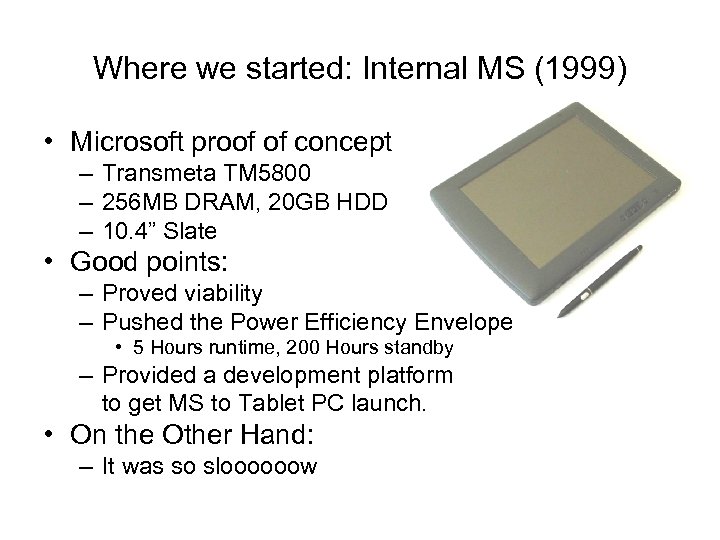

Where we started: Internal MS (1999) • Microsoft proof of concept – Transmeta TM 5800 – 256 MB DRAM, 20 GB HDD – 10. 4” Slate • Good points: – Proved viability – Pushed the Power Efficiency Envelope • 5 Hours runtime, 200 Hours standby – Provided a development platform to get MS to Tablet PC launch. • On the Other Hand: – It was so sloooooow

Today’s Market: New Slates Motion Computing Sahara i 213 12. 1”, 1. 6 GHz Centrino LE 1600 NEC Versa. Pro, 10. 4”, 1. 1 GHz Fujitsu 5000 Tatung TTAB 10. 4”, 1 GHz ULV LS 800 10. 4/12. 1, Indoor/Outdoor 1. 1 GHz ULV Tatung B 12 D 12. 1” 1. 2 GHz Centrino

Today’s Market: New Convertibles Acer Toshiba M 200, 12. 1” SXGA+ C 1 xx Gateway M 275 14. 1”, DVD C 300 C 250 2 GHz Pentium -M Fujitsu 1. 8 GHz Pentium-M Averatec C 3500 AMD 2200+ 12. 1”, DVD Electrovaya 1. 4 GHz Centrino T 4000 12. 1”, Biometrics Scribbler SC-2200 SHARP View. Sonic 12. 1”, 1 GHz Actius TN 10 W 12. 1”, 1. 1 GHz IBM Think. Pad x 41 HP tc 4200

Today’s Market: New Hybrids & Ruggeds Ruggedized Hybrid Itronix HP Compaq TC 1100 ULV 8. 4”, 933 MHz ULV Walkabout Hammerhead Celeron or Pentium 10. 4”, 1. 1 GHz 10. 4”, 4. 5 lbs 933 MHz P-III M Xplore i. X 104 10. 4” 1. 1 GHz ULV

Concept Design: New hinge

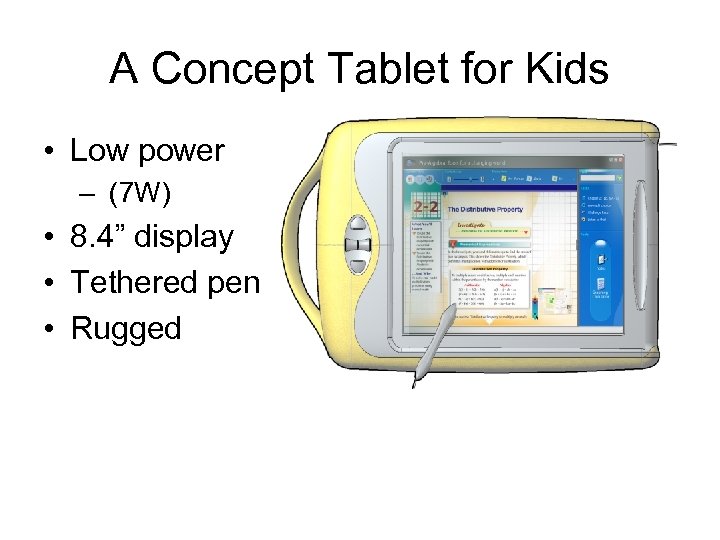

A Concept Tablet for Kids • Low power – (7 W) • 8. 4” display • Tethered pen • Rugged

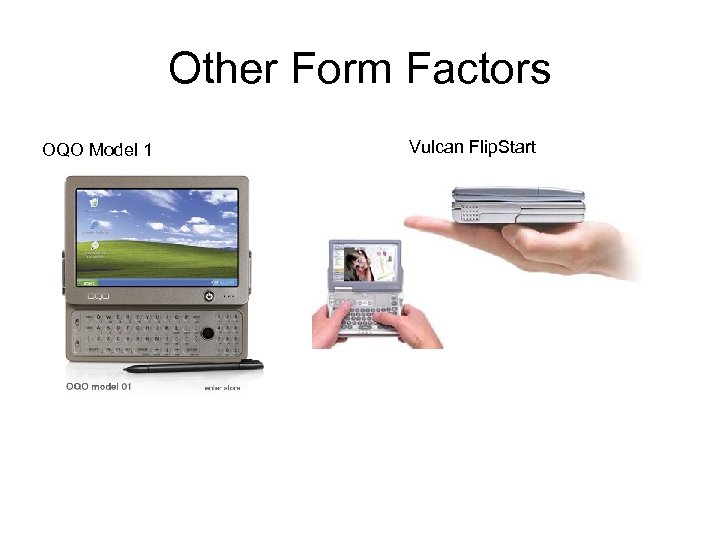

Other Form Factors OQO Model 1 Vulcan Flip. Start

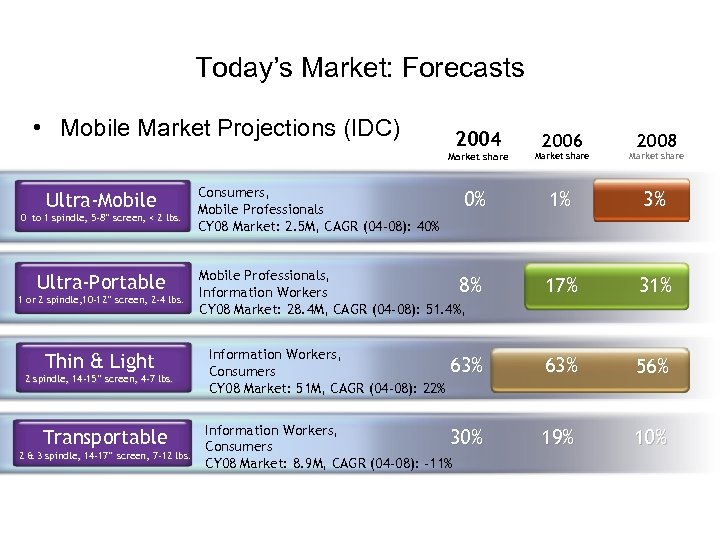

Today’s Market: Forecasts • Mobile Market Projections (IDC) 0 to 1 spindle, 5 -8” screen, < 2 lbs. Ultra-Portable 1 or 2 spindle, 10 -12” screen, 2 -4 lbs. Thin & Light 2 spindle, 14 -15” screen, 4 -7 lbs. Transportable 2 & 3 spindle, 14 -17” screen, 7 -12 lbs. 2006 2008 Market share Ultra-Mobile 2004 Market share 1% 3% 17% 31% 63% 56% Information Workers, 30% Consumers CY 08 Market: 8. 9 M, CAGR (04 -08): -11% 19% 10% Consumers, Mobile Professionals CY 08 Market: 2. 5 M, CAGR (04 -08): 40% 0% Mobile Professionals, 8% Information Workers CY 08 Market: 28. 4 M, CAGR (04 -08): 51. 4%, Information Workers, Consumers CY 08 Market: 51 M, CAGR (04 -08): 22%

Moore’s Law (1967) • Not really a “law”, but an observation, intended to hold for “. . the next few years”. • (Nt/A)(t 1) = (Nt/A)(t 0) * 1. 58 t 1 -t 0 (t in years) • Most exponential curves in the real world turn out to be “S” shaped, but Moore’s observation has held for 35 years.

The Woolly Bear Book of VLSI scaling • Scaling requires lithography and process changes. • Get more and faster transistors in the same area. • Power per transistor goes down, power per unit area goes up (sometimes way up). • Power ≈ CV 2 f (plus leakage)

How to use Moore’s Law • Lower cost: Same Nt, reduced A (“die shrinks”) used in video consoles. • More complex chips: Larger Nt, same A. – Lower the voltage and increase frequency – Add larger caches to overcome latency – Add architectural features to increase ILP • Superchips (SOC): Increase Nt and A.

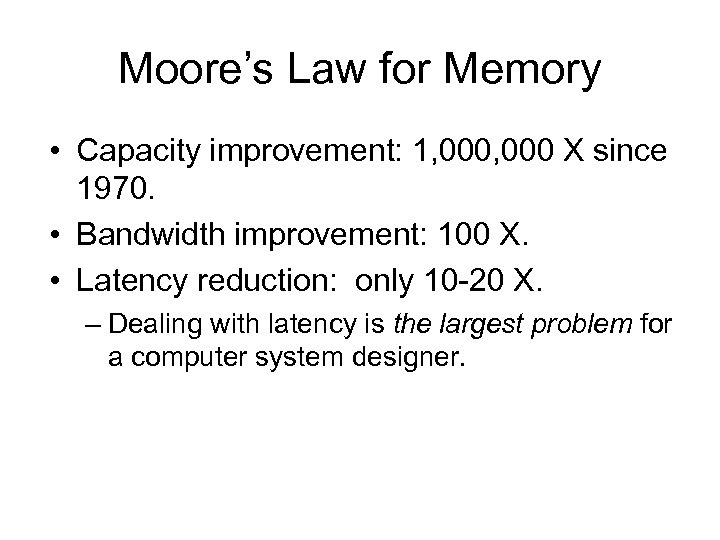

Moore’s Law for Memory • Capacity improvement: 1, 000 X since 1970. • Bandwidth improvement: 100 X. • Latency reduction: only 10 -20 X. – Dealing with latency is the largest problem for a computer system designer.

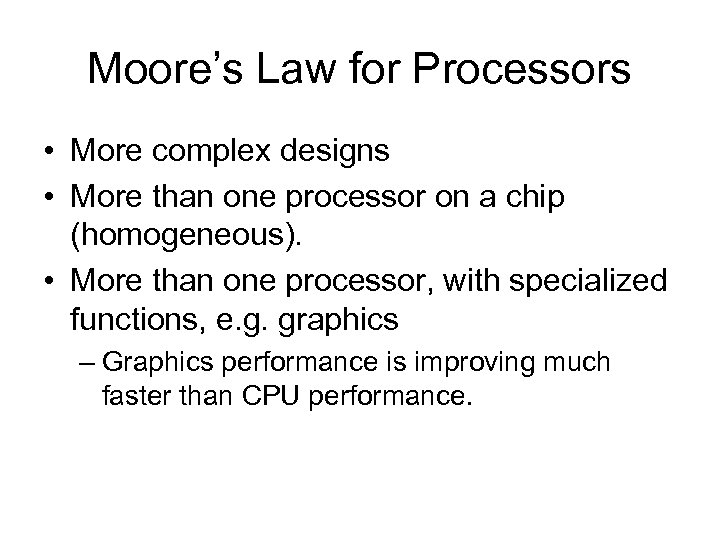

Moore’s Law for Processors • More complex designs • More than one processor on a chip (homogeneous). • More than one processor, with specialized functions, e. g. graphics – Graphics performance is improving much faster than CPU performance.

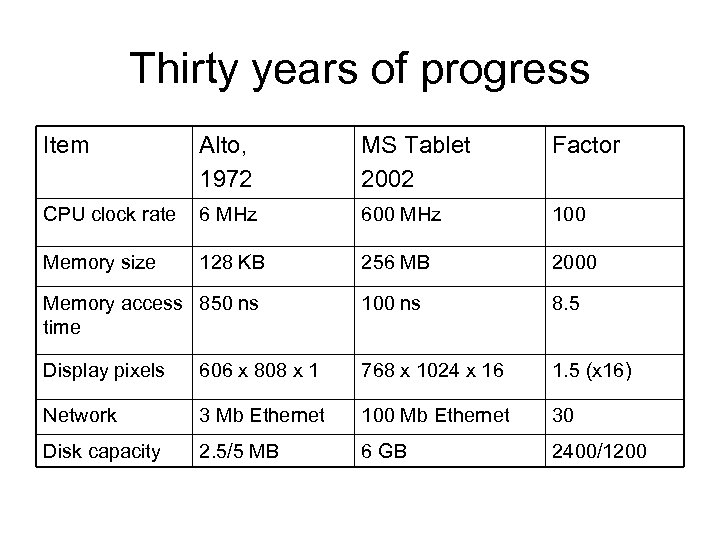

Thirty years of progress Item Alto, 1972 MS Tablet 2002 Factor CPU clock rate 6 MHz 600 MHz 100 Memory size 128 KB 256 MB 2000 Memory access 850 ns time 100 ns 8. 5 Display pixels 606 x 808 x 1 768 x 1024 x 16 1. 5 (x 16) Network 3 Mb Ethernet 100 Mb Ethernet 30 Disk capacity 2. 5/5 MB 6 GB 2400/1200

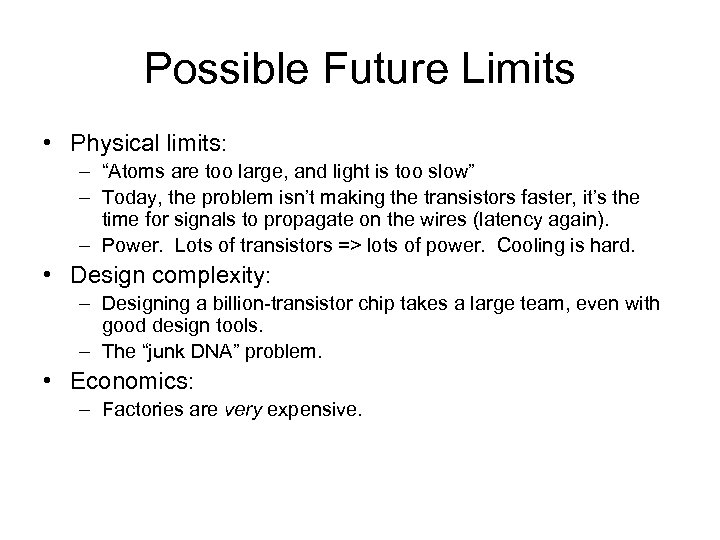

Possible Future Limits • Physical limits: – “Atoms are too large, and light is too slow” – Today, the problem isn’t making the transistors faster, it’s the time for signals to propagate on the wires (latency again). – Power. Lots of transistors => lots of power. Cooling is hard. • Design complexity: – Designing a billion-transistor chip takes a large team, even with good design tools. – The “junk DNA” problem. • Economics: – Factories are very expensive.

Scaling Limits • Voltage scaling is about over. It’s very hard to operate below 1 volt. • Frequency increases are also difficult. – Intel runs out at 3 – 4 GHz. • Static leakage is also a big problem. • So, we’ll see more transistors in the future, but they won’t be better or faster transistors.

Future processors • We’ll see chips with many processor cores. • Each core will be simpler than today’s superscalar machines. Probably hyperthreaded, to hide latency. • Optimized to increase thread-level parallelism, rather than instruction-level parallelism. • The story about caching is very unclear… • See Intel’s “Platform 2015” white papers.

Other Limits • Not all technologies used in computers follow Moore’s Law – Disks don’t – Displays don’t – Batteries don’t • The bandwidth vs. latency problem. – See D. Patterson, “Latency Lags Bandwidth”, CACM, October 2004

What about software? • For scientific computing and servers, the future seems fine. – There are lots of important problems that are embarrassingly parallel. • For client software, the picture is more bleak.

Many-core challenges for clients • Windows doesn’t use threads well – Exceptions: Kernel, SQL – Competitors don’t do any better • Applications don’t use threads well – Outlook is the poster child – Until recently, inking on Tablet was problematic • Problems: – – – Writing multi-threaded code is hard Threading model and primitives are overly complicated Threads don’t compose Debugging multi-threaded code is harder Testing multi-threaded code is a crapshoot Tool support isn’t very good

Possible paths forward • Better language support for parallelism – Cω, Atomic transactions • Better tools – Analyze liveness and safety statically – Model checking – Dynamic race detection • Better libraries • Better education

Conclusions • Popularity of portable devices, including Tablet PC, is growing • Much of the innovation in the industry is in this area. • Energy-efficiency can open up new markets. • Silicon trends favor the high end • There are lots of challenges and opportunities for new software.

af99b8df7a0e2e73b8a4cd21cde86502.ppt