Л1. Технология ПО и Порты ввода-вывода AVR.ppt

- Количество слайдов: 23

Технология разработки программного обеспечения для МК

МОДЕЛИ МИКРОКОНТРОЛЛЕРОВ AVR В настоящее время в серийном производстве у Atmel находятся семейства AVR ATtiny, ATmega и ATXmega. Также все еще можно встретить в продаже чипы семейства Classic типа AT 90. Classic AVR – это классические (первые) модели AVR, что следует и из их названия. Постепенно заменяются микроконтроллерами семейств Tiny и Mega. Tiny AVR – недорогие микроконтроллеры с малым количеством выходных контактов, чаще в восьмивыводном исполнении. Используются в системах, где не требуются сложные вычислительные алгоритмы. Mega AVR – мощные микроконтроллеры, включающие большой набор периферии. Это семейство имеет самое большое разнообразие моделей для выбора. AVR XMEGA – новое семейство компании Atmel переносит 8/16 -битные микроконтроллеры на новый уровень системных характеристик. В этой связи, микроконтроллеры AVR XMEGA могут выступать в качестве эталонных 8/16 битных микроконтроллеров. Независимо от выбора семейства микроконтроллеров AVR, следует помнить, что система команд всех семейств совместима, поэтому возможен простой перенос программы со слабого на более мощный микроконтроллер.

Периферия Микроконтроллер предназначен для выполнения задач управления. Поэтому периферия микроконтроллеров AVR включает устройства взаимодействия с внешним миром: • • • цифровые порты DIO (от 3 до 53 линий ввода и вывода), контроллер внешних прерываний IRQ, таймеры-счетчики T/C, широтно-импульсные модуляторы PWM. сторожевой таймер Watchdog timer, Система реального времени RTC, аналоговые компараторы AC, 10/12 -разрядный 8/16 -канальный АЦП ADC, последовательные интерфейсы USART, SPI, TWI, CAN, USB, средство внутрисхемной отладки JTAG/Debug. Wire, устройство сброса по понижению питания.

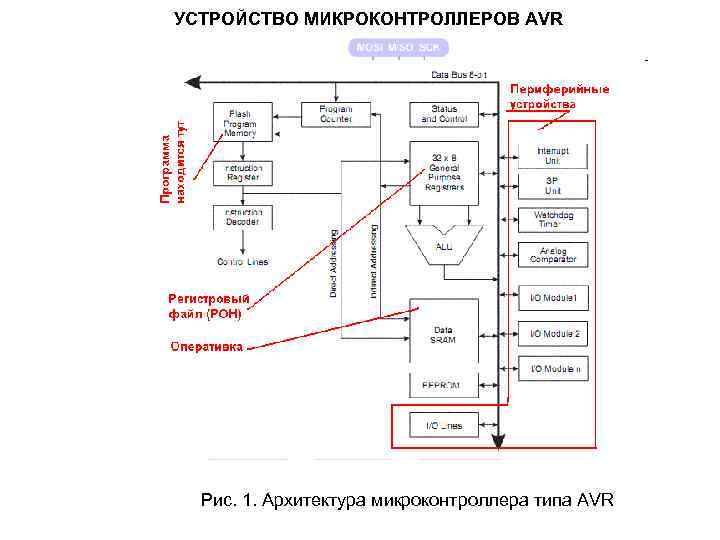

УСТРОЙСТВО МИКРОКОНТРОЛЛЕРОВ AVR Рис. 1. Архитектура микроконтроллера типа AVR

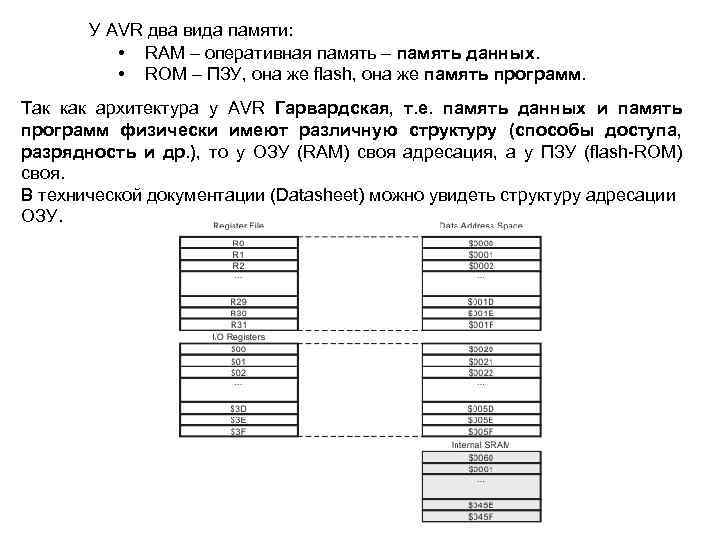

У AVR два вида памяти: • RAM – оперативная память – память данных. • ROM – ПЗУ, она же flash, она же память программ. Так как архитектура у AVR Гарвардская, т. е. память данных и память программ физически имеют различную структуру (способы доступа, разрядность и др. ), то у ОЗУ (RAM) своя адресация, а у ПЗУ (flash-ROM) своя. В технической документации (Datasheet) можно увидеть структуру адресации ОЗУ.

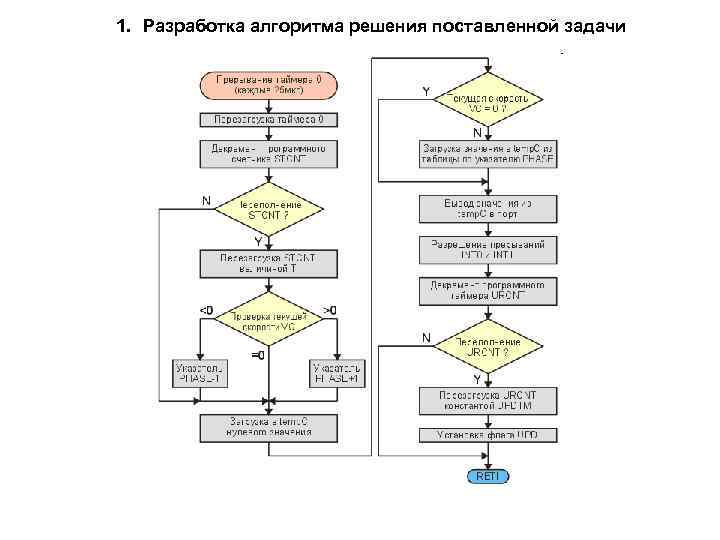

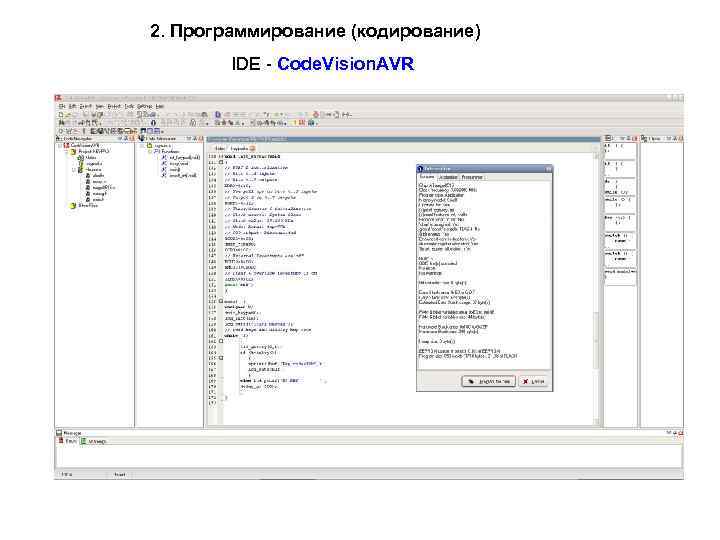

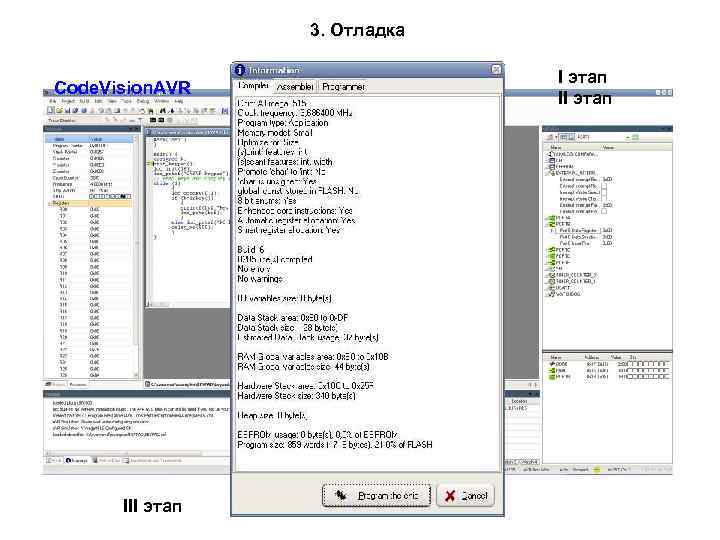

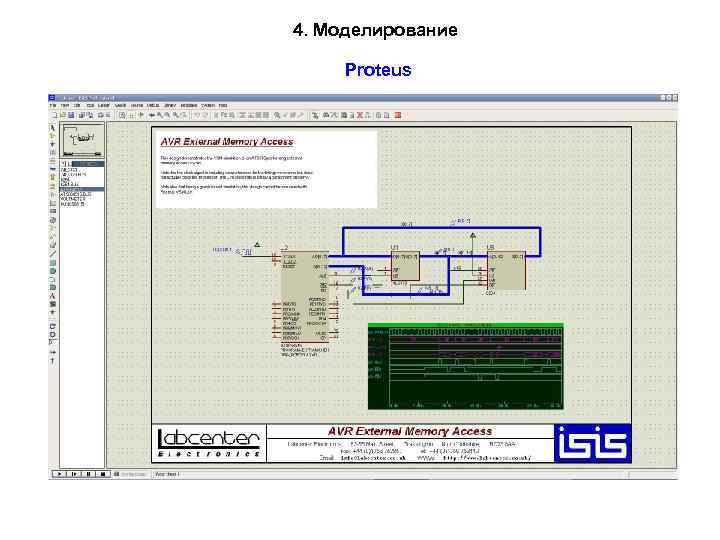

Технология разработки программного обеспечения для МК 1. Разработка алгоритма решения поставленной задачи. Уяснить суть задачи и определить способы достижения поставленной цели. Выполняется обычно в голове, на бумажке и т. д. 2. Программирование (кодирование). Текстовыё редактор → компилятор → библиотекарь → линковщик. file. c, file. pas file. obj file. lib, file. dll file. bin, file. exe Всё вместе содержит т. н. Интегрированная среда разработки IDE (англ. Integrated Development Environment). Мы будем использовать Code. Vision. 3. Отладка. I этап – синтаксическая. Выполняется при компиляции исходного файла. Задача выявить «орфографические» ошибки исходного кода программы. Результат – объектный файл. II этап – конструктивная. Выполняется при линковании (связывании) компонентов программы в единый исполняемый файл. Результат – файл годный для загрузки в программатор - file. hex, file. coff. III этап – симуляция. Использование специального ПО – Debugger. Мы будем использовать AVRStudio – file. coff (Содержит исполняемый код и символьную информацию для удобства отладки). 4. Моделирование. Мы будем использовать Proteus. 5. Испытание на отладочном стенде UNI-DS 3. Мы будем использовать программатор AVRProg.

1. Разработка алгоритма решения поставленной задачи

2. Программирование (кодирование) IDE - Code. Vision. AVR

3. Отладка I этап II этап Code. Vision. AVR III этап Debugger - AVRStudio

4. Моделирование Proteus

5. Испытание на отладочном стенде UNI-DS 3

Порты ввода-вывода

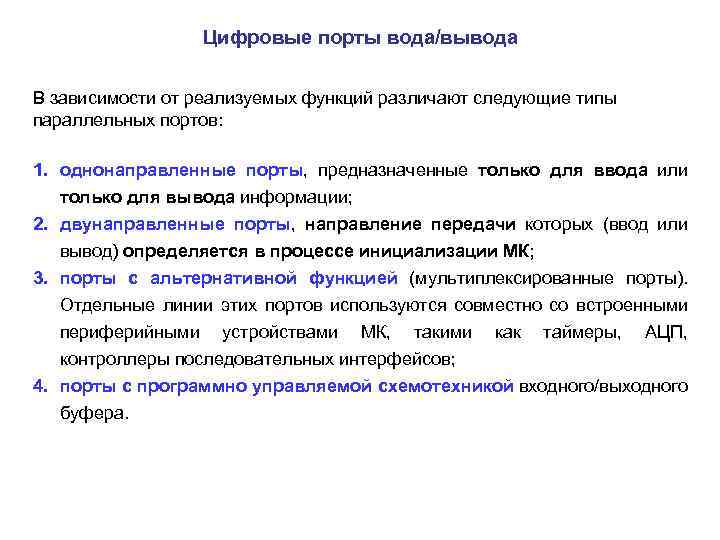

Цифровые порты вода/вывода В зависимости от реализуемых функций различают следующие типы параллельных портов: 1. однонаправленные порты, предназначенные только для ввода или только для вывода информации; 2. двунаправленные порты, направление передачи которых (ввод или вывод) определяется в процессе инициализации МК; 3. порты с альтернативной функцией (мультиплексированные порты). Отдельные линии этих портов используются совместно со встроенными периферийными устройствами МК, такими как таймеры, АЦП, контроллеры последовательных интерфейсов; 4. порты с программно управляемой схемотехникой входного/выходного буфера.

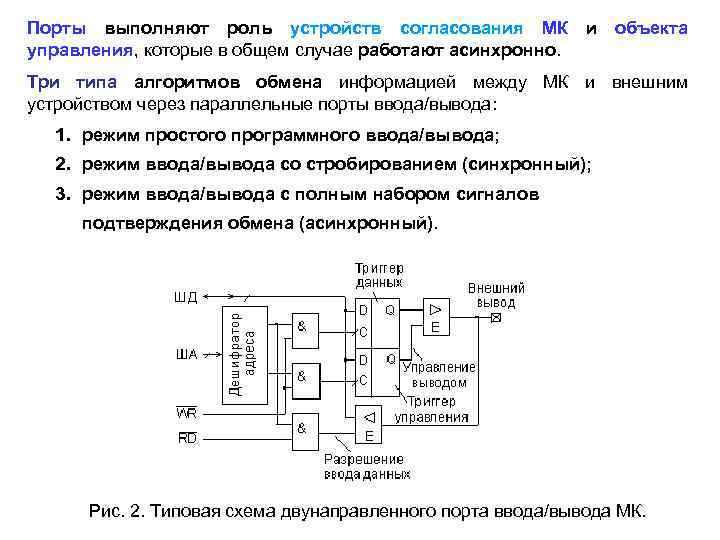

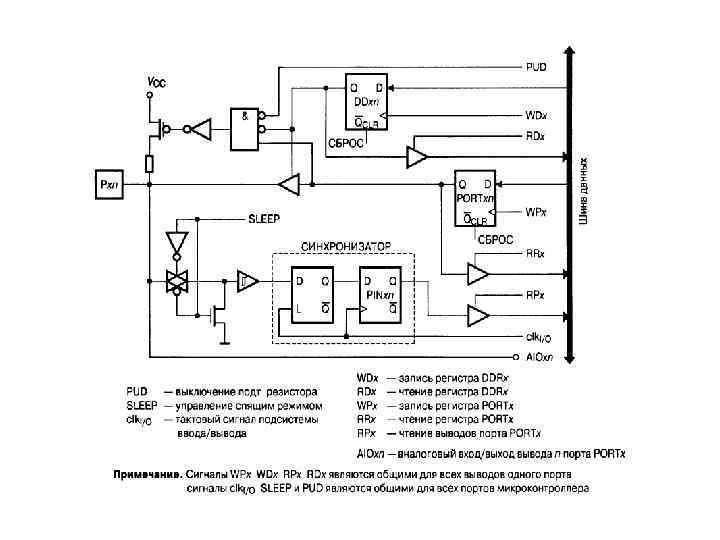

Порты выполняют роль устройств согласования МК и объекта управления, которые в общем случае работают асинхронно. Три типа алгоритмов обмена информацией между МК и внешним устройством через параллельные порты ввода/вывода: 1. режим простого программного ввода/вывода; 2. режим ввода/вывода со стробированием (синхронный); 3. режим ввода/вывода с полным набором сигналов подтверждения обмена (асинхронный). Рис. 2. Типовая схема двунаправленного порта ввода/вывода МК.

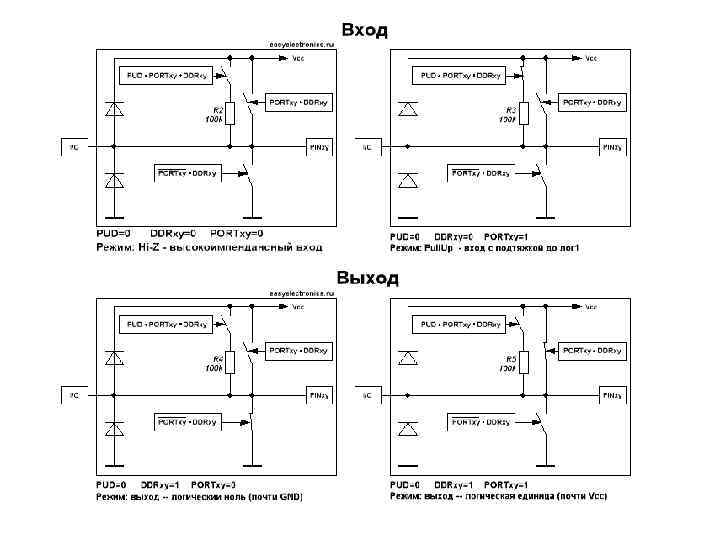

Как запомнить режимы? Для этого надо понять логику работы контроллера. Итак: • • • Самый безопасный для МК и схемы, ни на что не влияющий режим это Hi-Z. Очевидно что этот режим и должен быть по умолчанию (default). Значения большинства портов I/O при включении питания/сбросе = 0 х00, PORT и DDR не исключение. Соответственно когда DDR = 0 и PORT = 0 это High-Z – самый безопасный режим, оптимальный при старте. Hi-Z это вход, значит при DDR = 0 нога настроена на вход. Запомнили. Однако, если DDR = 0 – вход, то что будет если PORT переключить в 1? Очевидно, что будет другой режим входа. Какой? Pull. Up, другого не дано! Логично? Логично. Запомнили. Раз дефолтный режим был входом и одновременно в регистрах нуль, то для того, чтобы настроить вывод на выход надо в DDR записать 1. Ну, а состояние выхода уже соответствует регистру PORT – высокий это 1, низкий это 0. Чтение производится из регистра PIN.

Порты ввода-вывода 1. Каждый порт микроконтроллеров состоит из определенного числа выводов, через которые микроконтроллер может осуществлять прием и передачу цифровых сигналов. 2. Задание направления передачи данных через любой контакт ввода/вывода может быть произведено программно в любой момент времени. 3. Выходные буферы всех портов, имея симметричные нагрузочные характеристики, обеспечивают высокую нагрузочную способность при любом уровне сигнала. Нагрузочной способности достаточно для непосредственного управления светодиодными индикаторами. 4. Входные буферы всех выводов построены по схеме триггера Шмитта. Для всех входов имеется возможность подключения внутреннего подтягивающего резистора между входом и шиной питания Vcc. 5. Отличительной особенностью портов микроконтроллеров AVR при использовании их в качестве цифровых портов ввода/вывода общего назначения является реализация истинной функциональности «чтениемодификация-запись» . Благодаря этому можно выполнять операции над любым выводом не влияя на другие выводы порта. Это относится к изменению режима работы контакта ввода/вывода, к изменению состояния выходного буфера (для выходов) и к изменению состояния внутреннего подтягивающего резистора (для входов).

Особенности порта ввода-вывода (I/O) AVR Порты ввода/вывода AVR имеют: • • от 3 до 53 независимых линий "вход/выход". Каждая линия порта может быть запрограммирована на вход или на выход. Мощные выходные драйверы обеспечивают высокую токовую нагрузочную способность 20 м. А на линию порта (втекающий ток) при максимальном значении 40 м. А, что позволяет, например, непосредственно подключать к микроконтроллеру светодиоды и биполярные транзисторы. Общая токовая нагрузка на все линии одного порта не должна превышать 80 м. А (все значения приведены для напряжения питания 5 В). Архитектурная особенность построения портов ввода/вывода у AVR заключается в том, что для каждого физического вывода (пина) существует 3 бита контроля/управления, а не 2, как у распространенных 8 -разрядных микроконтроллеров. Это повышает скорость работы микроконтроллера при работе с внешними устройствами, особенно в условиях внешних электрических помех.

Регистры портов ввода/вывода Обращение к портам производится через регистры ввода/вывода. Под каждый порт в адресном пространстве ввода/вывода зарезервировано по 3 адреса, по которым размещены следующие регистры: • • • регистр данных порта PORTx*, регистр направления данных DDRх и регистр выводов порта PINx. * Букве «х» обозначает имя порта – A, B, C, D и т. д. в зависимости от типа контроллера Все регистры 8 -и разрядные. Регистры PORTx и DDRx доступны и для чтения, и для записи. С помощью регистров PINx осуществляется доступ к физическим значениям сигналов на выводах порта, они доступны только для чтения.

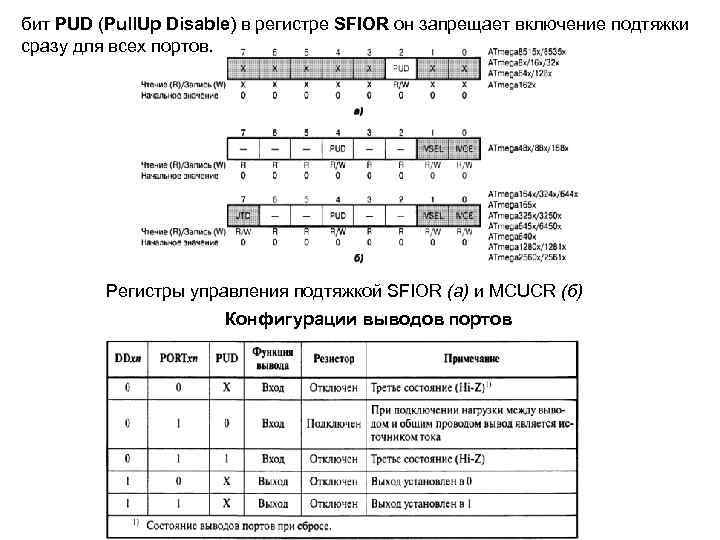

бит PUD (Pull. Up Disable) в регистре SFIOR он запрещает включение подтяжки сразу для всех портов. Регистры управления подтяжкой SFIOR (а) и MCUCR (б) Конфигурации выводов портов

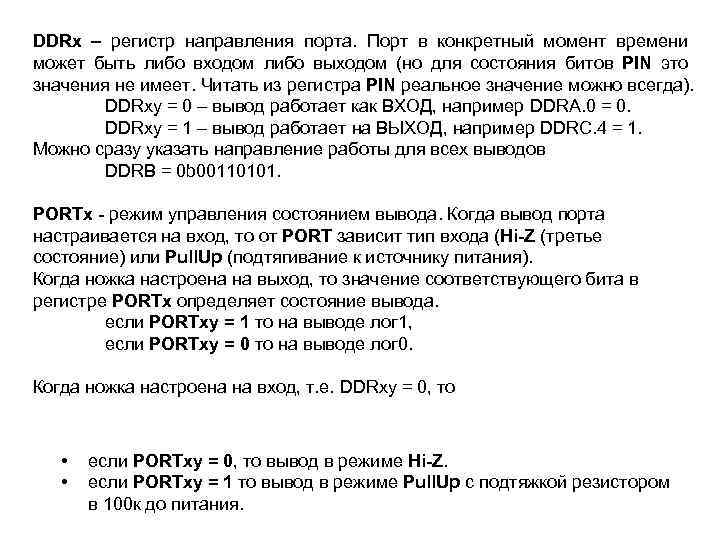

DDRx – регистр направления порта. Порт в конкретный момент времени может быть либо входом либо выходом (но для состояния битов PIN это значения не имеет. Читать из регистра PIN реальное значение можно всегда). DDRxy = 0 – вывод работает как ВХОД, например DDRA. 0 = 0. DDRxy = 1 – вывод работает на ВЫХОД, например DDRC. 4 = 1. Можно сразу указать направление работы для всех выводов DDRB = 0 b 00110101. PORTx - режим управления состоянием вывода. Когда вывод порта настраивается на вход, то от PORT зависит тип входа (Hi-Z (третье состояние) или Pull. Up (подтягивание к источнику питания). Когда ножка настроена на выход, то значение соответствующего бита в регистре PORTx определяет состояние вывода. если PORTxy = 1 то на выводе лог 1, если PORTxy = 0 то на выводе лог 0. Когда ножка настроена на вход, т. е. DDRxy = 0, то • • если PORTxy = 0, то вывод в режиме Hi-Z. если PORTxy = 1 то вывод в режиме Pull. Up с подтяжкой резистором в 100 к до питания.

Состояние вывода микроконтроллера (независимо от установок бита DDxn) может быть получено путем чтения бита PINxn регистра PINx. При этом следует помнить, что между действительным изменением сигнала на выводе и изменением бита PINxn существует задержка в 1 машинный цикл). Эта задержка вносится узлом синхронизации, состоящим, из бита PINxn и дополнительного триггера-защелки. Значение сигнала на выводе микроконтроллера фиксируется триггеромзащелкой при НИЗКОМ уровне тактового сигнала и переписывается затем в бит PINxn по нарастающему фронту тактового сигнала. Соответственно, величина задержки может составлять от 0. 5 до 1. 5 периодов системного тактового сигнала

Л1. Технология ПО и Порты ввода-вывода AVR.ppt