fd0fad6cab44ca3e63725b4a6e2da6d8.ppt

- Количество слайдов: 14

Technion – Israel Institute of Technology Faculty of Electrical Engineering NOC Seminar Error Handling in Wormhole Networks Author: Amit Berman Mentor: Prof. Idit Keidar April, 2008

Technion – Israel Institute of Technology Faculty of Electrical Engineering NOC Seminar Error Handling in Wormhole Networks Author: Amit Berman Mentor: Prof. Idit Keidar April, 2008

![Introduction – “A flit with a bad day” [8] Glitch from Aggressive Crosstalk Module Introduction – “A flit with a bad day” [8] Glitch from Aggressive Crosstalk Module](https://present5.com/presentation/fd0fad6cab44ca3e63725b4a6e2da6d8/image-2.jpg) Introduction – “A flit with a bad day” [8] Glitch from Aggressive Crosstalk Module ‘ 11100’ ‘ 11110’ Module Radiation ‘ 11000’ ‘ 10000’ Alpha particles or cosmic ‘radiation in 11100’ high integration ‘ 10000’ ‘ 00000’ 0. 7 Vcc ‘ 11110’ Module EMI ‘ 11000’ ‘ 11111’ Module Radiation Voltage Scaling Crosstalk noise Module Coupling capacitance. Interference (EMI) between wires Electro-Magnetic Signal Glitch High frequency, long interconnects Process Variations Aggressive voltage scaling Parameters Uncertainty Module Module Process Variations

Introduction – “A flit with a bad day” [8] Glitch from Aggressive Crosstalk Module ‘ 11100’ ‘ 11110’ Module Radiation ‘ 11000’ ‘ 10000’ Alpha particles or cosmic ‘radiation in 11100’ high integration ‘ 10000’ ‘ 00000’ 0. 7 Vcc ‘ 11110’ Module EMI ‘ 11000’ ‘ 11111’ Module Radiation Voltage Scaling Crosstalk noise Module Coupling capacitance. Interference (EMI) between wires Electro-Magnetic Signal Glitch High frequency, long interconnects Process Variations Aggressive voltage scaling Parameters Uncertainty Module Module Process Variations

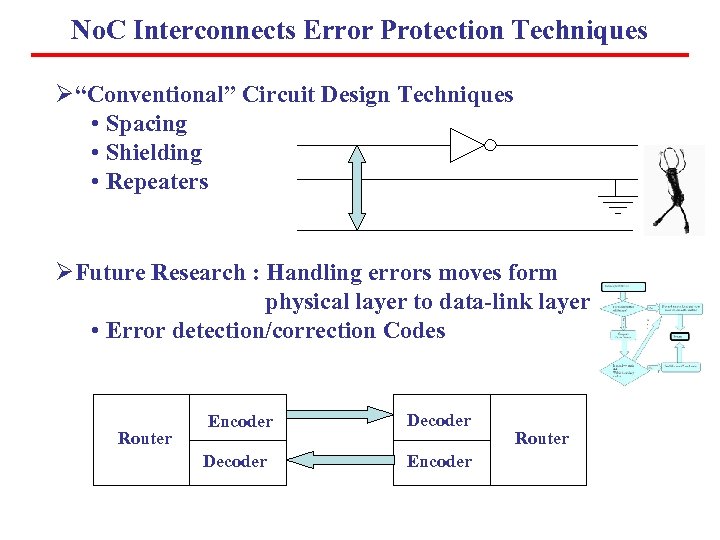

No. C Interconnects Error Protection Techniques Ø“Conventional” Circuit Design Techniques • Spacing • Shielding • Repeaters ØFuture Research : Handling errors moves form physical layer to data-link layer • Error detection/correction Codes Router Encoder Decoder Encoder Router

No. C Interconnects Error Protection Techniques Ø“Conventional” Circuit Design Techniques • Spacing • Shielding • Repeaters ØFuture Research : Handling errors moves form physical layer to data-link layer • Error detection/correction Codes Router Encoder Decoder Encoder Router

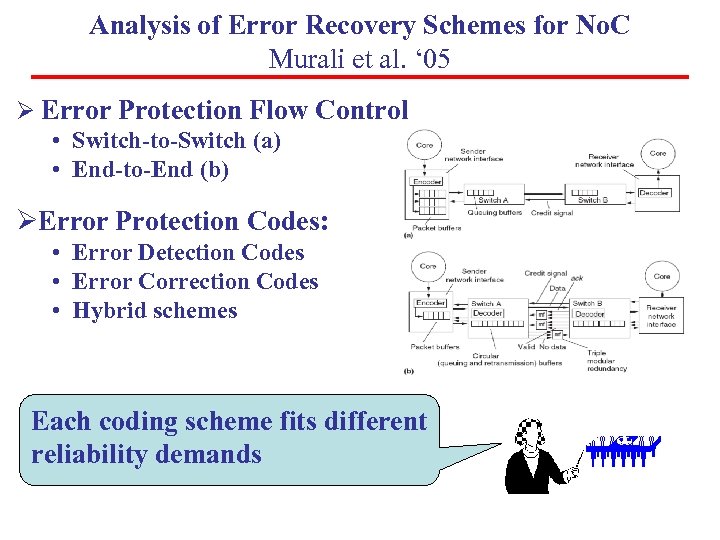

Analysis of Error Recovery Schemes for No. C Murali et al. ‘ 05 Ø Error Protection Flow Control • Switch-to-Switch (a) • End-to-End (b) ØError Protection Codes: • Error Detection Codes • Error Correction Codes • Hybrid schemes Each coding scheme fits different reliability demands

Analysis of Error Recovery Schemes for No. C Murali et al. ‘ 05 Ø Error Protection Flow Control • Switch-to-Switch (a) • End-to-End (b) ØError Protection Codes: • Error Detection Codes • Error Correction Codes • Hybrid schemes Each coding scheme fits different reliability demands

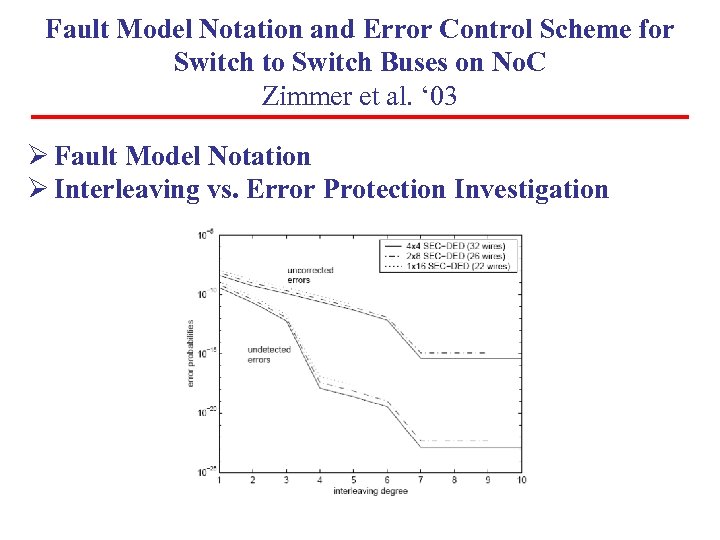

Fault Model Notation and Error Control Scheme for Switch to Switch Buses on No. C Zimmer et al. ‘ 03 Ø Fault Model Notation Ø Interleaving vs. Error Protection Investigation

Fault Model Notation and Error Control Scheme for Switch to Switch Buses on No. C Zimmer et al. ‘ 03 Ø Fault Model Notation Ø Interleaving vs. Error Protection Investigation

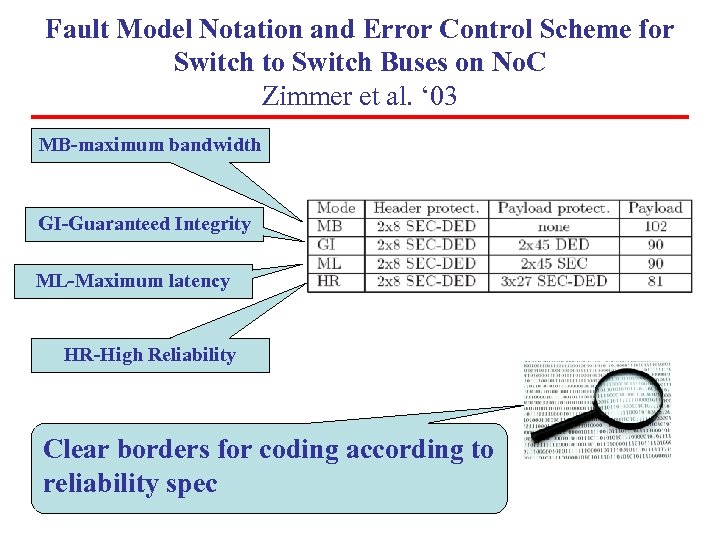

Fault Model Notation and Error Control Scheme for Switch to Switch Buses on No. C Zimmer et al. ‘ 03 MB-maximum bandwidth GI-Guaranteed Integrity ML-Maximum latency HR-High Reliability Clear borders for coding according to reliability spec

Fault Model Notation and Error Control Scheme for Switch to Switch Buses on No. C Zimmer et al. ‘ 03 MB-maximum bandwidth GI-Guaranteed Integrity ML-Maximum latency HR-High Reliability Clear borders for coding according to reliability spec

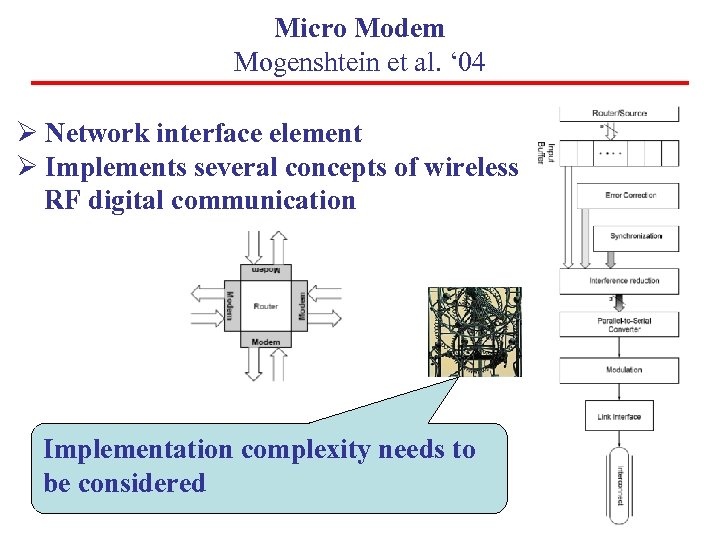

Micro Modem Mogenshtein et al. ‘ 04 Ø Network interface element Ø Implements several concepts of wireless RF digital communication Implementation complexity needs to be considered

Micro Modem Mogenshtein et al. ‘ 04 Ø Network interface element Ø Implements several concepts of wireless RF digital communication Implementation complexity needs to be considered

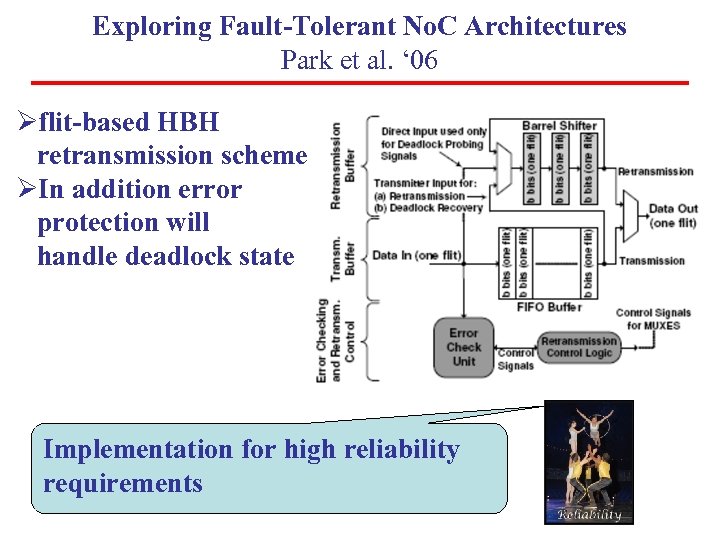

Exploring Fault-Tolerant No. C Architectures Park et al. ‘ 06 Øflit-based HBH retransmission scheme ØIn addition error protection will handle deadlock state Implementation for high reliability requirements

Exploring Fault-Tolerant No. C Architectures Park et al. ‘ 06 Øflit-based HBH retransmission scheme ØIn addition error protection will handle deadlock state Implementation for high reliability requirements

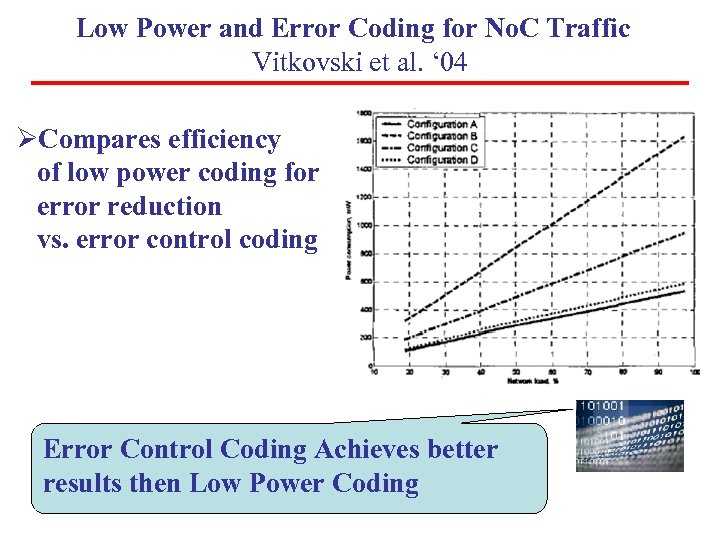

Low Power and Error Coding for No. C Traffic Vitkovski et al. ‘ 04 ØCompares efficiency of low power coding for error reduction vs. error control coding Error Control Coding Achieves better results then Low Power Coding

Low Power and Error Coding for No. C Traffic Vitkovski et al. ‘ 04 ØCompares efficiency of low power coding for error reduction vs. error control coding Error Control Coding Achieves better results then Low Power Coding

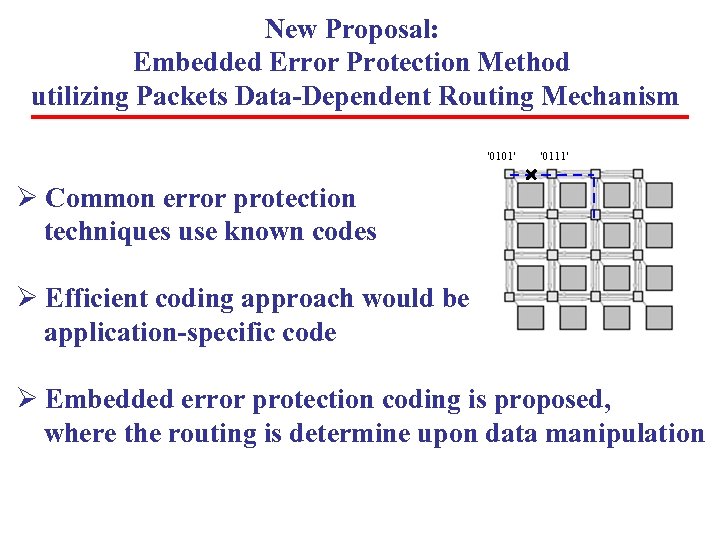

New Proposal: Embedded Error Protection Method utilizing Packets Data-Dependent Routing Mechanism '0101' '0111' Ø Common error protection techniques use known codes Ø Efficient coding approach would be application-specific code Ø Embedded error protection coding is proposed, where the routing is determine upon data manipulation

New Proposal: Embedded Error Protection Method utilizing Packets Data-Dependent Routing Mechanism '0101' '0111' Ø Common error protection techniques use known codes Ø Efficient coding approach would be application-specific code Ø Embedded error protection coding is proposed, where the routing is determine upon data manipulation

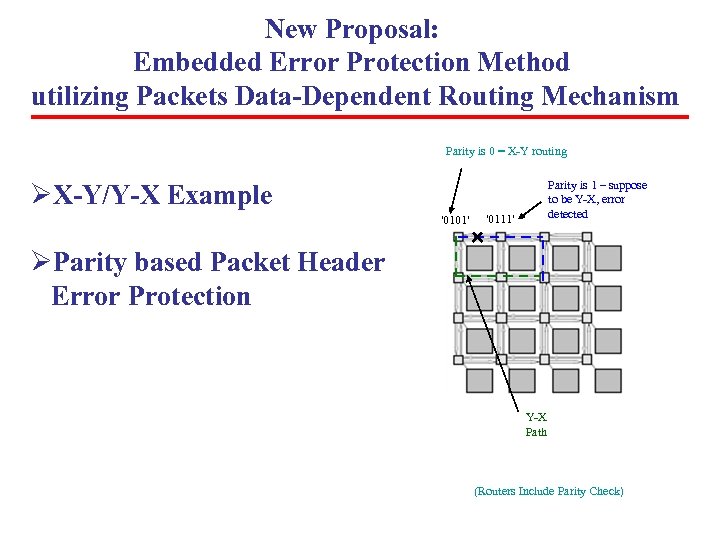

New Proposal: Embedded Error Protection Method utilizing Packets Data-Dependent Routing Mechanism Parity is 0 = X-Y routing Parity is 1 – suppose to be Y-X, error detected ØX-Y/Y-X Example '0101' '0111' ØParity based Packet Header Error Protection Y-X Path (Routers Include Parity Check)

New Proposal: Embedded Error Protection Method utilizing Packets Data-Dependent Routing Mechanism Parity is 0 = X-Y routing Parity is 1 – suppose to be Y-X, error detected ØX-Y/Y-X Example '0101' '0111' ØParity based Packet Header Error Protection Y-X Path (Routers Include Parity Check)

New Proposal: Embedded Error Protection Method utilizing Packets Data-Dependent Routing Mechanism ØFuture Research: ØApplication to various routing techniques e. g. source routing ØCost function considerations ØPower and Error Protection Efficiency comparing other Coding techniques Minimum Overhead, Balanced, Scalable Method

New Proposal: Embedded Error Protection Method utilizing Packets Data-Dependent Routing Mechanism ØFuture Research: ØApplication to various routing techniques e. g. source routing ØCost function considerations ØPower and Error Protection Efficiency comparing other Coding techniques Minimum Overhead, Balanced, Scalable Method

![References [1] H. Zimmer, A. Jantsch, References [1] H. Zimmer, A. Jantsch,](https://present5.com/presentation/fd0fad6cab44ca3e63725b4a6e2da6d8/image-13.jpg) References [1] H. Zimmer, A. Jantsch, "Fault Model Notation and Error Control Scheme for Switch to Switch buses on No. C". CODES ISSS 2003, pp. 188 -193. [2] S. Murali, T. Theocharides, N. Vijaykrishnan, M. J Irwin, L. Benini, G. Micheli, "Analysis of Error Recovery Schemes for Networks on Chips", IEEE Design&Test of Computers 2005, pp. 434 -442. [3] A. Mogenshtein, E. Bolotim, I. Cidon, A. Kolodny, R. Ginosar, "Micro Modem – Reliability Solution For No. C Communications", ICECS 2004, pp. 483 -486. [4] D. Park, C. Nicopoulos, J. Kim, N. Vijaykrishnan, C. R. Das, "Exploring Fault-Tolerant No. C Architectures", IEEE DSN 2006, pp. 93 -104. [5] A. Vitkovski, R. Haukilahti, A. Jantsch, E. Nilsson, "Low Power and Error Coding for Network-on-Chip Traffic", Norchip Conference Proc. , 2004. pp. 20 -23. [6] G. Micheli, L. Benini, "Networks on Chips – Technology and Tools", Morgan Kaufmann Publishers 2006, pp. 75 -139. [7] P. Vellanki, N. Banerjee, K. S. Chatha, "Quality-of-Service and Error Control Techniques for Mesh-Based Network-on-Chip Architectures", Integration 2005, pp. 353 -382. [8] J. Nurmi, H. Tenhunen, J. Isoaho, A. Jantsch, "Interconnect-Centric Design for Advanced SOC and NOC", Kluwer Academic Publishers 2004, pp. 155 -170. [9] R. Gindin, I. Cidon, I. Keidar, "No. C-Based FPGA: Architecture and Routing", NOCS 2007, pp. 253 -264. [10] M. Mutyam, "Selective shielding: A Crosstalk-Free Bus Encoding Technique", IEEE ICCAD 2007, pp. 618 -621. [11] International Technology Roadmap for Semiconductors, 2001.

References [1] H. Zimmer, A. Jantsch, "Fault Model Notation and Error Control Scheme for Switch to Switch buses on No. C". CODES ISSS 2003, pp. 188 -193. [2] S. Murali, T. Theocharides, N. Vijaykrishnan, M. J Irwin, L. Benini, G. Micheli, "Analysis of Error Recovery Schemes for Networks on Chips", IEEE Design&Test of Computers 2005, pp. 434 -442. [3] A. Mogenshtein, E. Bolotim, I. Cidon, A. Kolodny, R. Ginosar, "Micro Modem – Reliability Solution For No. C Communications", ICECS 2004, pp. 483 -486. [4] D. Park, C. Nicopoulos, J. Kim, N. Vijaykrishnan, C. R. Das, "Exploring Fault-Tolerant No. C Architectures", IEEE DSN 2006, pp. 93 -104. [5] A. Vitkovski, R. Haukilahti, A. Jantsch, E. Nilsson, "Low Power and Error Coding for Network-on-Chip Traffic", Norchip Conference Proc. , 2004. pp. 20 -23. [6] G. Micheli, L. Benini, "Networks on Chips – Technology and Tools", Morgan Kaufmann Publishers 2006, pp. 75 -139. [7] P. Vellanki, N. Banerjee, K. S. Chatha, "Quality-of-Service and Error Control Techniques for Mesh-Based Network-on-Chip Architectures", Integration 2005, pp. 353 -382. [8] J. Nurmi, H. Tenhunen, J. Isoaho, A. Jantsch, "Interconnect-Centric Design for Advanced SOC and NOC", Kluwer Academic Publishers 2004, pp. 155 -170. [9] R. Gindin, I. Cidon, I. Keidar, "No. C-Based FPGA: Architecture and Routing", NOCS 2007, pp. 253 -264. [10] M. Mutyam, "Selective shielding: A Crosstalk-Free Bus Encoding Technique", IEEE ICCAD 2007, pp. 618 -621. [11] International Technology Roadmap for Semiconductors, 2001.

The End Questions? Thanks for your attention

The End Questions? Thanks for your attention