СУММАТОРЫ Вычислительная техника

СУММАТОРЫ Вычислительная техника

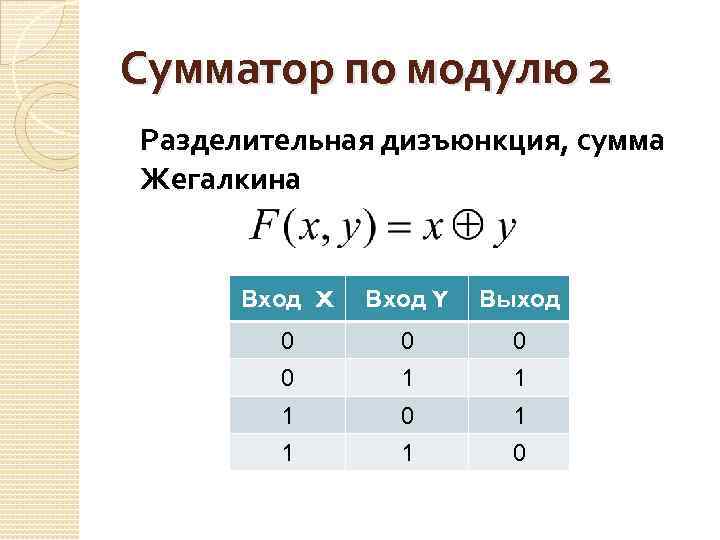

Сумматор по модулю 2 Разделительная дизъюнкция, сумма Жегалкина Вход X Вход Y Выход 0 0 1 1 1 0

Сумматор по модулю 2 Разделительная дизъюнкция, сумма Жегалкина Вход X Вход Y Выход 0 0 1 1 1 0

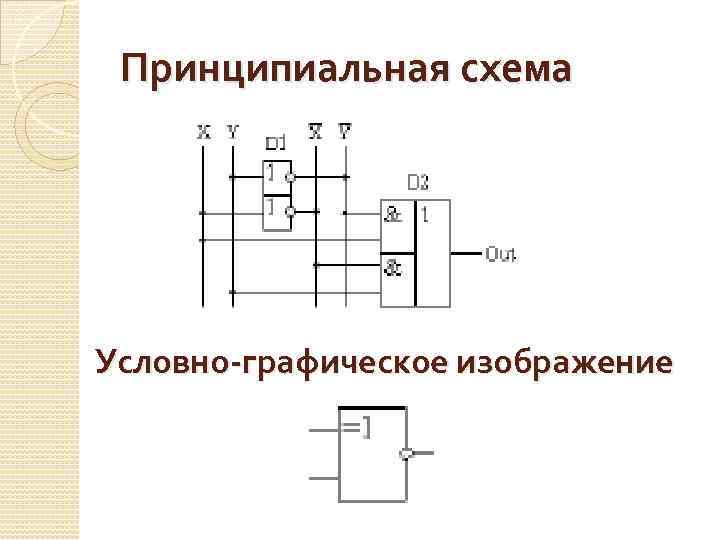

Принципиальная схема Условно-графическое изображение

Принципиальная схема Условно-графическое изображение

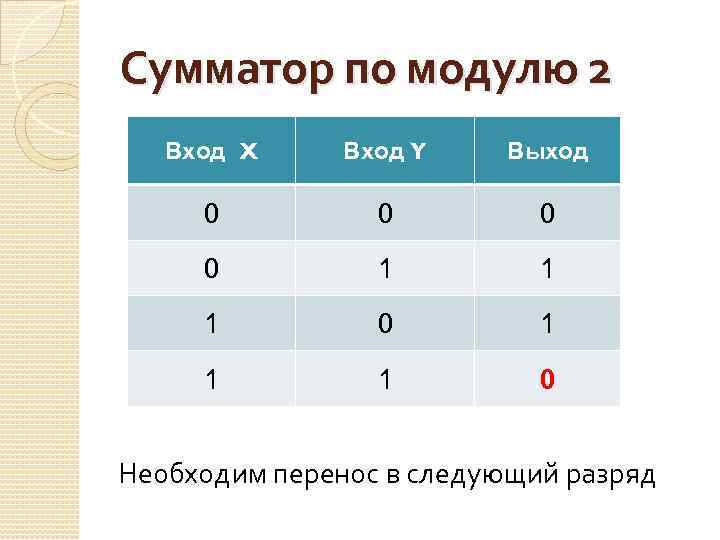

Сумматор по модулю 2 Вход X Вход Y Выход 0 0 1 1 1 0 Необходим перенос в следующий разряд

Сумматор по модулю 2 Вход X Вход Y Выход 0 0 1 1 1 0 Необходим перенос в следующий разряд

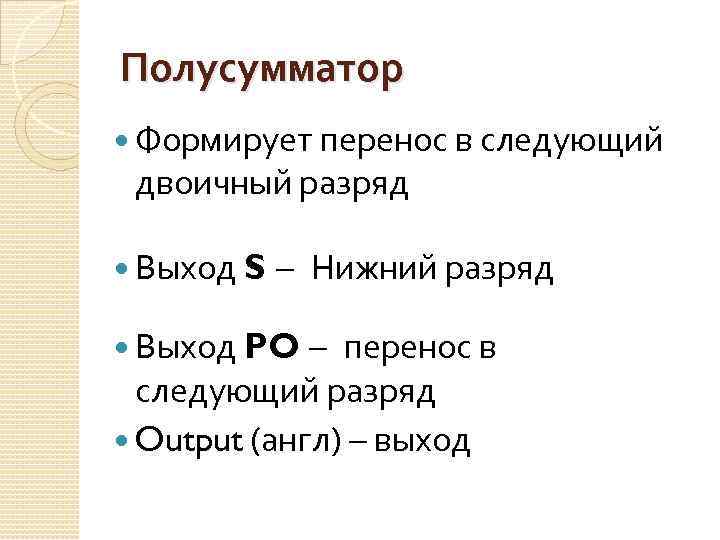

Полусумматор Формирует перенос в следующий двоичный разряд Выход S – Нижний разряд Выход PO – перенос в следующий разряд Output (англ) – выход

Полусумматор Формирует перенос в следующий двоичный разряд Выход S – Нижний разряд Выход PO – перенос в следующий разряд Output (англ) – выход

Полусумматор Вход A Вход B Выход S 0 0 1 1 1 0 Выход PO

Полусумматор Вход A Вход B Выход S 0 0 1 1 1 0 Выход PO

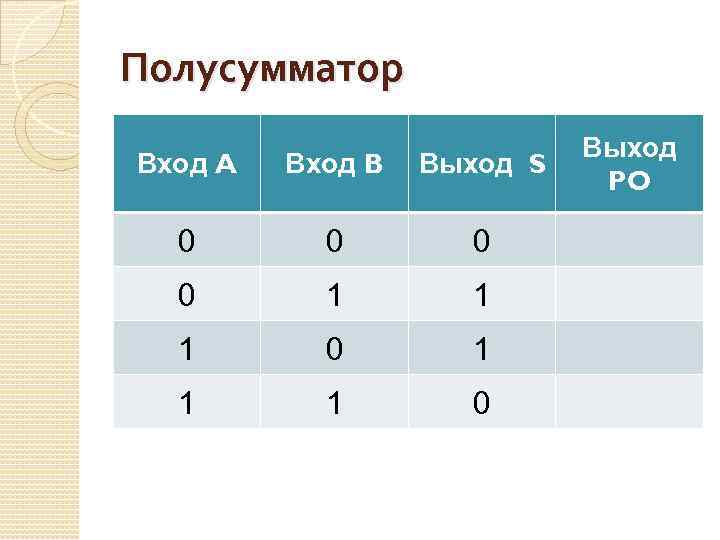

Полусумматор Вход A Вход B Выход S Выход PO 0 0 0 1 1 0 1 0 1

Полусумматор Вход A Вход B Выход S Выход PO 0 0 0 1 1 0 1 0 1

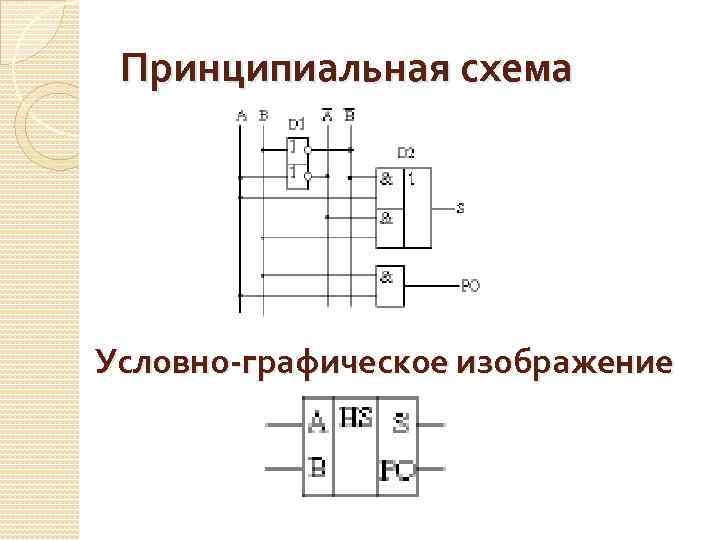

Принципиальная схема Условно-графическое изображение

Принципиальная схема Условно-графическое изображение

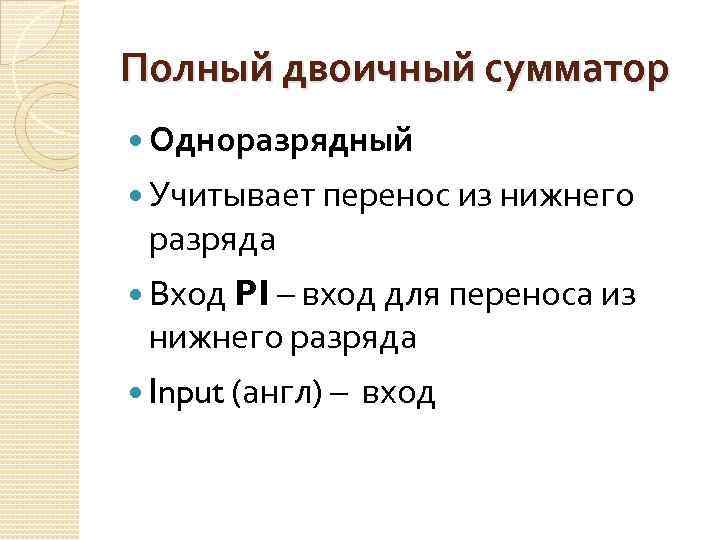

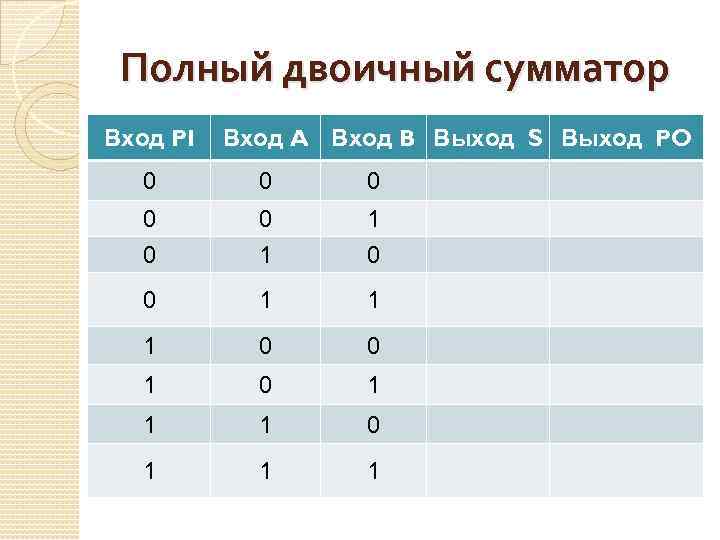

Полный двоичный сумматор Одноразрядный Учитывает перенос из нижнего разряда Вход PI – вход для переноса из нижнего разряда Input (англ) – вход

Полный двоичный сумматор Одноразрядный Учитывает перенос из нижнего разряда Вход PI – вход для переноса из нижнего разряда Input (англ) – вход

Полный двоичный сумматор Вход PI Вход A Вход B Выход S Выход PO 0 0 0 1 1 0 0 1 0 1 1 1

Полный двоичный сумматор Вход PI Вход A Вход B Выход S Выход PO 0 0 0 1 1 0 0 1 0 1 1 1

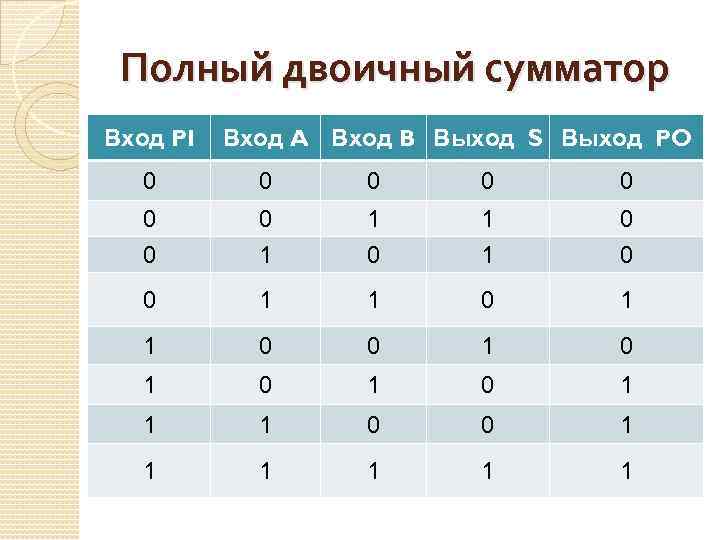

Полный двоичный сумматор Вход PI Вход A Вход B Выход S Выход PO 0 0 0 0 1 1 0 0 1 0 1 1 1 0 0 1 1 1

Полный двоичный сумматор Вход PI Вход A Вход B Выход S Выход PO 0 0 0 0 1 1 0 0 1 0 1 1 1 0 0 1 1 1

Принципиальная схема

Принципиальная схема

Условно-графическое изображение

Условно-графическое изображение

Многоразрядный сумматор

Многоразрядный сумматор

Условно-графическое изображение

Условно-графическое изображение

ДЕШИФРАТОРЫ

ДЕШИФРАТОРЫ

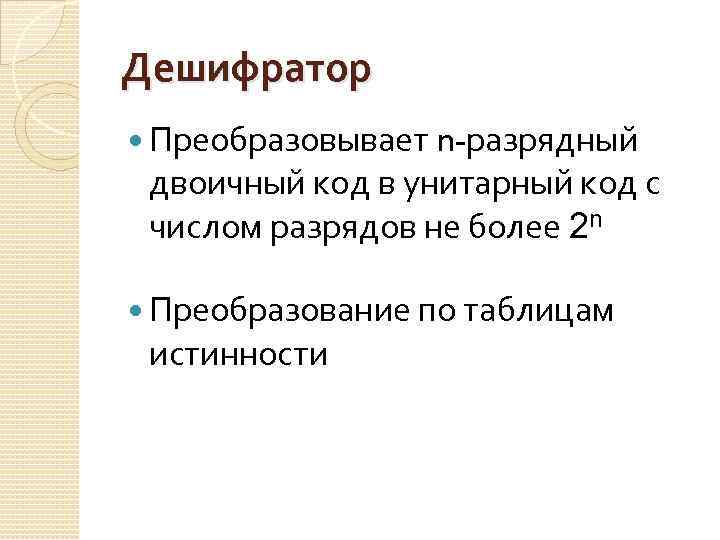

Дешифратор Преобразовывает n-разрядный двоичный код в унитарный код с числом разрядов не более 2 n Преобразование по таблицам истинности

Дешифратор Преобразовывает n-разрядный двоичный код в унитарный код с числом разрядов не более 2 n Преобразование по таблицам истинности

Дешифратор Преобразование входного 4 - разрядного двоичного кода в унитарный 10 -разрядный код Дешифратор 4× 10

Дешифратор Преобразование входного 4 - разрядного двоичного кода в унитарный 10 -разрядный код Дешифратор 4× 10

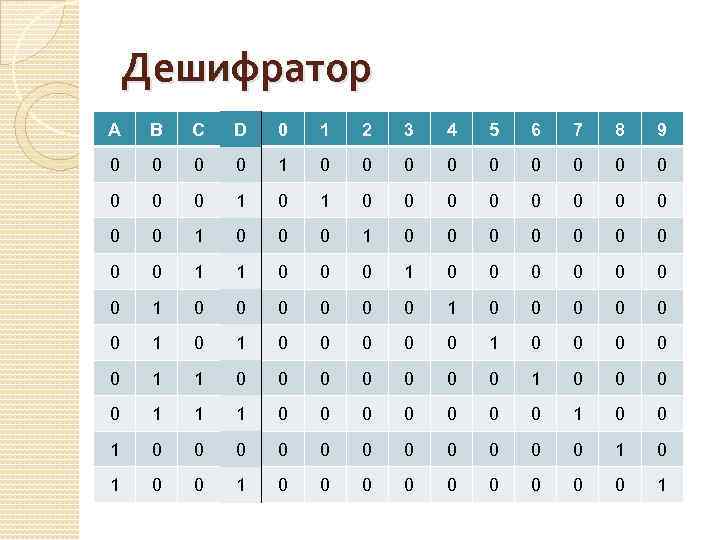

Дешифратор А B C D 0 1 2 3 4 5 6 7 8 9 0 0 1 0 0 0 0 0 0 1 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 0 1 1 1 0 0 0 0 0 0 1 0 0 0 0 0 1

Дешифратор А B C D 0 1 2 3 4 5 6 7 8 9 0 0 1 0 0 0 0 0 0 1 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 0 1 1 1 0 0 0 0 0 0 1 0 0 0 0 0 1

Условное графическое обозначение

Условное графическое обозначение

Семисегментный индикатор

Семисегментный индикатор

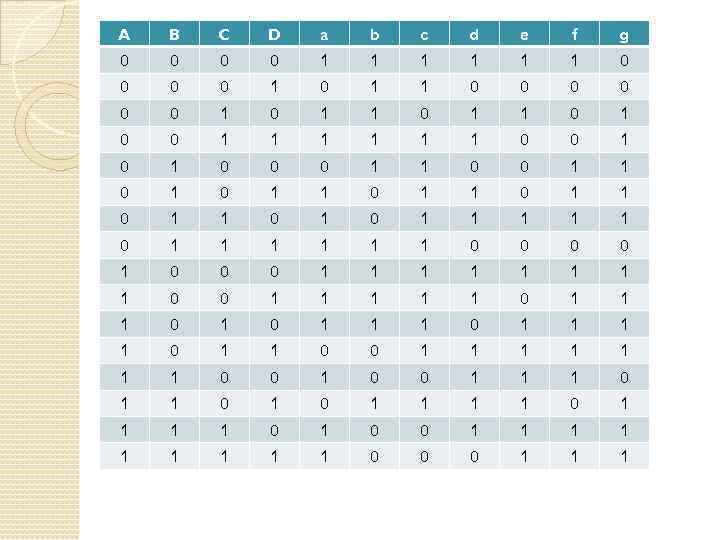

A B C D a b c d e f g 0 0 1 1 1 0 0 1 0 1 1 0 0 1 1 1 0 0 0 1 1 0 1 1 0 1 0 1 1 1 0 0 1 0 0 0 1 1 1 1 0 0 1 1 1 0 1 1 0 0 1 1 1 1 0 0 1 1 1 0 1 0 1 1 1 1 0 0 1 1 1 1 1 0 0 0 1 1 1

A B C D a b c d e f g 0 0 1 1 1 0 0 1 0 1 1 0 0 1 1 1 0 0 0 1 1 0 1 1 0 1 0 1 1 1 0 0 1 0 0 0 1 1 1 1 0 0 1 1 1 0 1 1 0 0 1 1 1 1 0 0 1 1 1 0 1 0 1 1 1 1 0 0 1 1 1 1 1 0 0 0 1 1 1

Условно-графическое изображение

Условно-графическое изображение

МУЛЬТИПЛЕКСОРЫ

МУЛЬТИПЛЕКСОРЫ

Мультиплексор Устройство, которое позволяет подавать сигнал с одного из нескольких входов на один выход

Мультиплексор Устройство, которое позволяет подавать сигнал с одного из нескольких входов на один выход

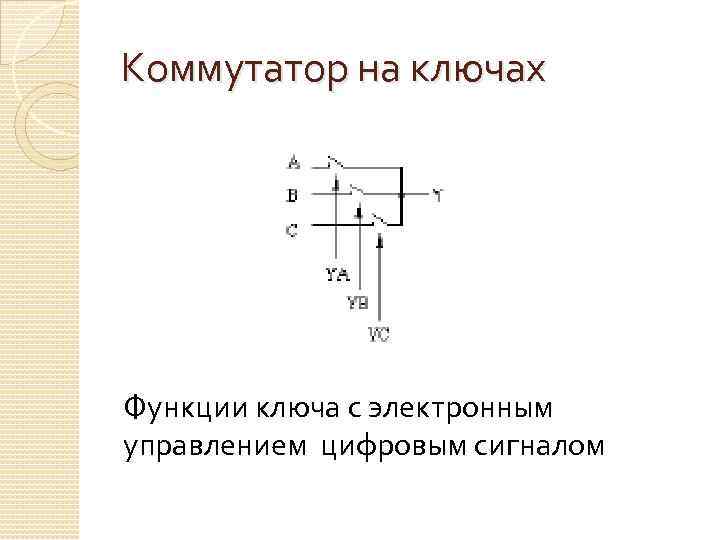

Коммутатор на ключах Функции ключа с электронным управлением цифровым сигналом

Коммутатор на ключах Функции ключа с электронным управлением цифровым сигналом

Простейший цифровой ключ управляющий информационн ый Вход X Вход Y Выход 0 0 1 1 1

Простейший цифровой ключ управляющий информационн ый Вход X Вход Y Выход 0 0 1 1 1

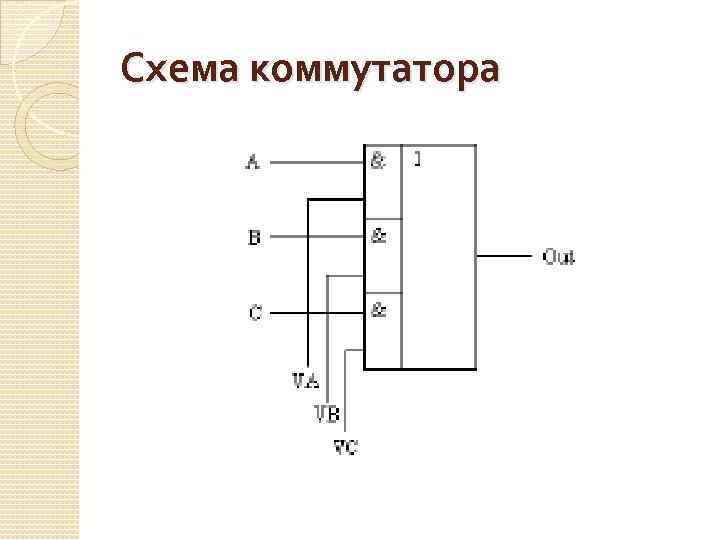

Схема коммутатора

Схема коммутатора

Принципиальная схема Информационн ые входы Адресные входы

Принципиальная схема Информационн ые входы Адресные входы

Мультиплексор

Мультиплексор

Демультиплексор Передача сигнала с одного входа микросхемы на один из нескольких выходов

Демультиплексор Передача сигнала с одного входа микросхемы на один из нескольких выходов