2f74591f05e353a59fd380add92dcdee.ppt

- Количество слайдов: 40

Status of the electronics systems of the MEG experiment PSI - Jun. 27 th, 2006 1

Status of the electronics systems of the MEG experiment PSI - Jun. 27 th, 2006 1

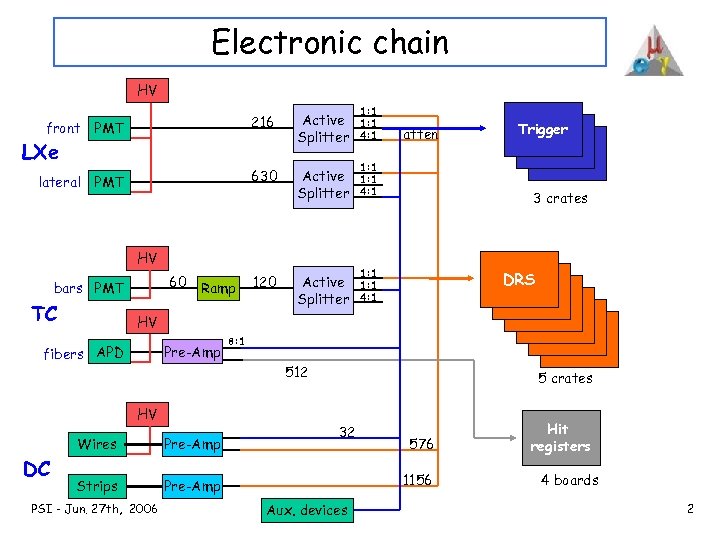

Electronic chain HV 216 1: 1 4: 1 630 front PMT Active Splitter 1: 1 4: 1 LXe lateral PMT HV 60 bars PMT TC Ramp Pre-Amp DRS DRS DRS 8: 1 512 HV Wires Pre-Amp Strips 5 crates 32 Pre-Amp PSI - Jun. 27 th, 2006 Trigger 3 crates HV fibers APD DC 120 atten 576 1156 Aux. devices Hit registers 4 boards 2

Electronic chain HV 216 1: 1 4: 1 630 front PMT Active Splitter 1: 1 4: 1 LXe lateral PMT HV 60 bars PMT TC Ramp Pre-Amp DRS DRS DRS 8: 1 512 HV Wires Pre-Amp Strips 5 crates 32 Pre-Amp PSI - Jun. 27 th, 2006 Trigger 3 crates HV fibers APD DC 120 atten 576 1156 Aux. devices Hit registers 4 boards 2

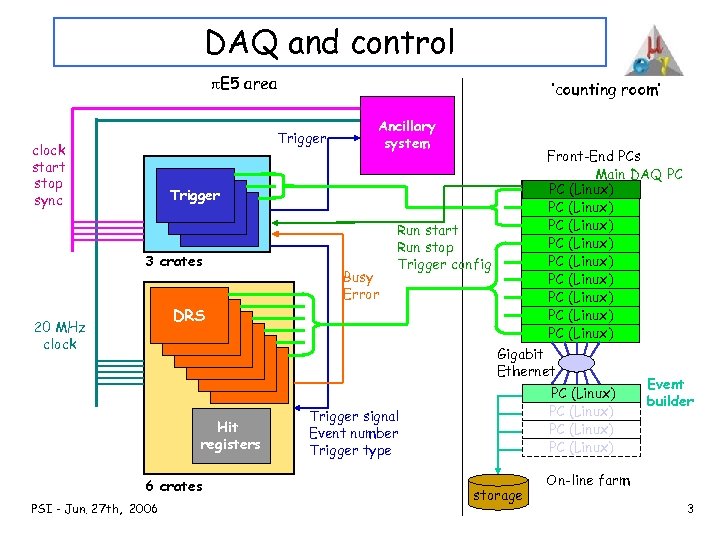

DAQ and control p. E 5 area ‘counting room’ Trigger clock start stop sync Ancillary system Trigger 3 crates Busy Error Run start Run stop Trigger config DRS DRS DRS 20 MHz clock Hit registers 6 crates PSI - Jun. 27 th, 2006 Front-End PCs Main DAQ PC PC (Linux) PC (Linux) PC (Linux) Gigabit Ethernet PC (Linux) Trigger signal Event number Trigger type storage Event builder On-line farm 3

DAQ and control p. E 5 area ‘counting room’ Trigger clock start stop sync Ancillary system Trigger 3 crates Busy Error Run start Run stop Trigger config DRS DRS DRS 20 MHz clock Hit registers 6 crates PSI - Jun. 27 th, 2006 Front-End PCs Main DAQ PC PC (Linux) PC (Linux) PC (Linux) Gigabit Ethernet PC (Linux) Trigger signal Event number Trigger type storage Event builder On-line farm 3

HV PSI - Jun. 27 th, 2006 4

HV PSI - Jun. 27 th, 2006 4

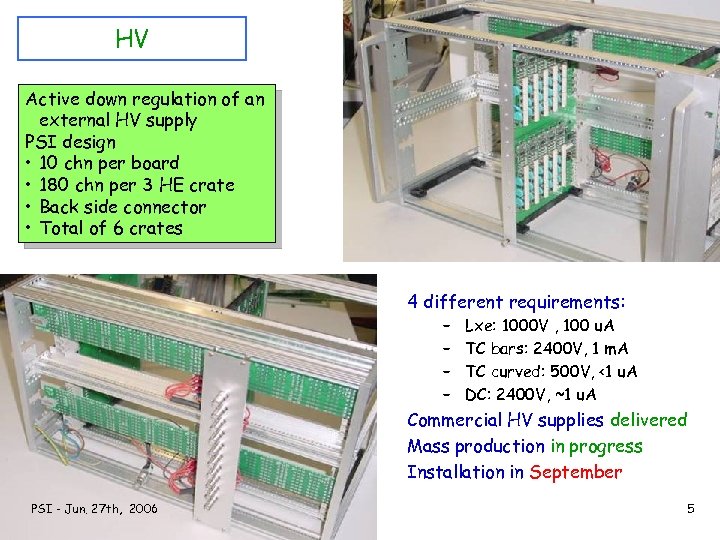

HV Active down regulation of an external HV supply PSI design • 10 chn per board • 180 chn per 3 HE crate • Back side connector • Total of 6 crates 4 different requirements: – – Lxe: 1000 V , 100 u. A TC bars: 2400 V, 1 m. A TC curved: 500 V, <1 u. A DC: 2400 V, ~1 u. A Commercial HV supplies delivered Mass production in progress Installation in September PSI - Jun. 27 th, 2006 5

HV Active down regulation of an external HV supply PSI design • 10 chn per board • 180 chn per 3 HE crate • Back side connector • Total of 6 crates 4 different requirements: – – Lxe: 1000 V , 100 u. A TC bars: 2400 V, 1 m. A TC curved: 500 V, <1 u. A DC: 2400 V, ~1 u. A Commercial HV supplies delivered Mass production in progress Installation in September PSI - Jun. 27 th, 2006 5

Splitters PSI - Jun. 27 th, 2006 6

Splitters PSI - Jun. 27 th, 2006 6

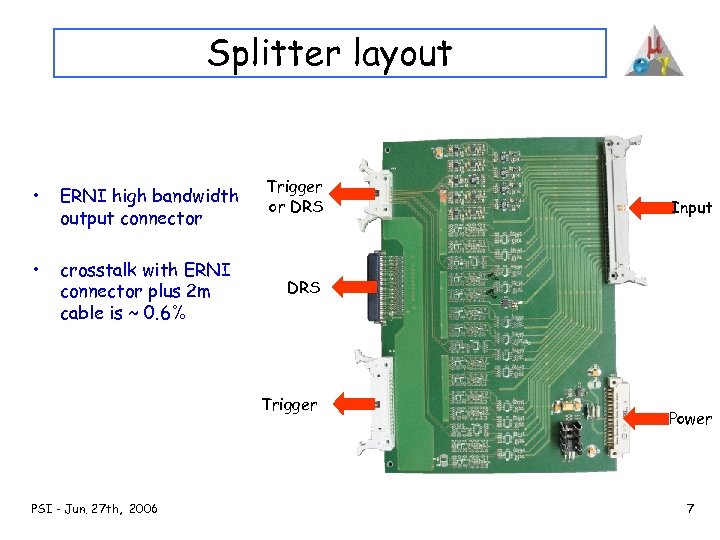

Splitter layout • ERNI high bandwidth output connector • crosstalk with ERNI connector plus 2 m cable is ~ 0. 6% Trigger or DRS Trigger PSI - Jun. 27 th, 2006 Input Power 7

Splitter layout • ERNI high bandwidth output connector • crosstalk with ERNI connector plus 2 m cable is ~ 0. 6% Trigger or DRS Trigger PSI - Jun. 27 th, 2006 Input Power 7

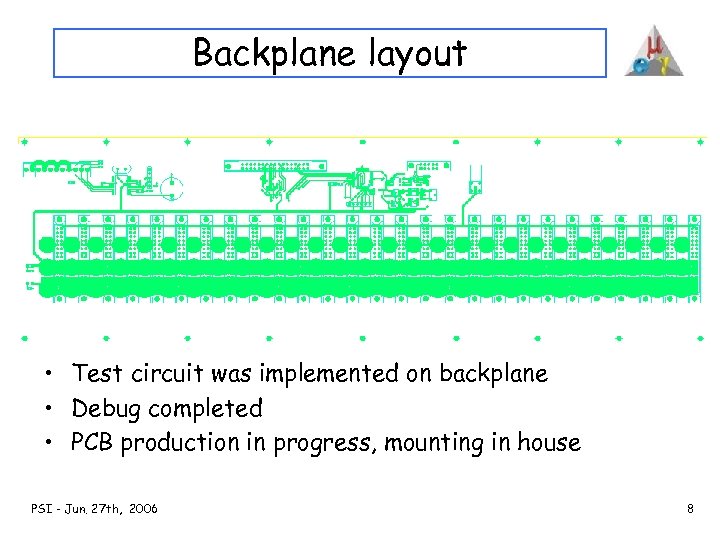

Backplane layout • Test circuit was implemented on backplane • Debug completed • PCB production in progress, mounting in house PSI - Jun. 27 th, 2006 8

Backplane layout • Test circuit was implemented on backplane • Debug completed • PCB production in progress, mounting in house PSI - Jun. 27 th, 2006 8

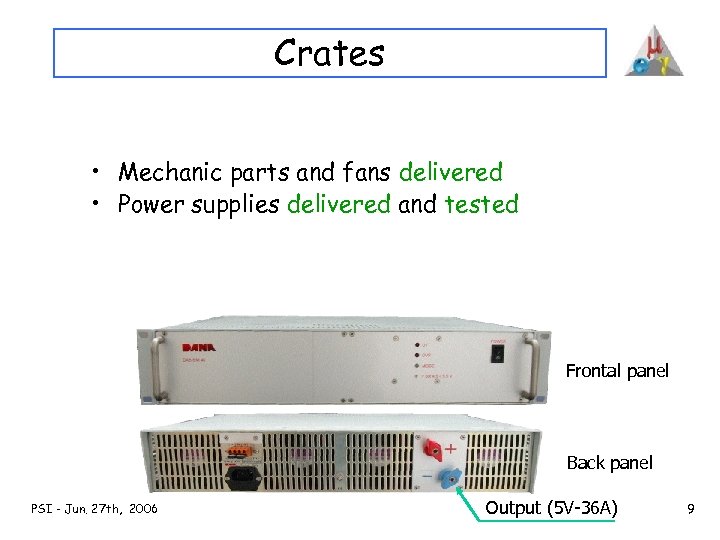

Crates • Mechanic parts and fans delivered • Power supplies delivered and tested Frontal panel Back panel PSI - Jun. 27 th, 2006 Output (5 V-36 A) 9

Crates • Mechanic parts and fans delivered • Power supplies delivered and tested Frontal panel Back panel PSI - Jun. 27 th, 2006 Output (5 V-36 A) 9

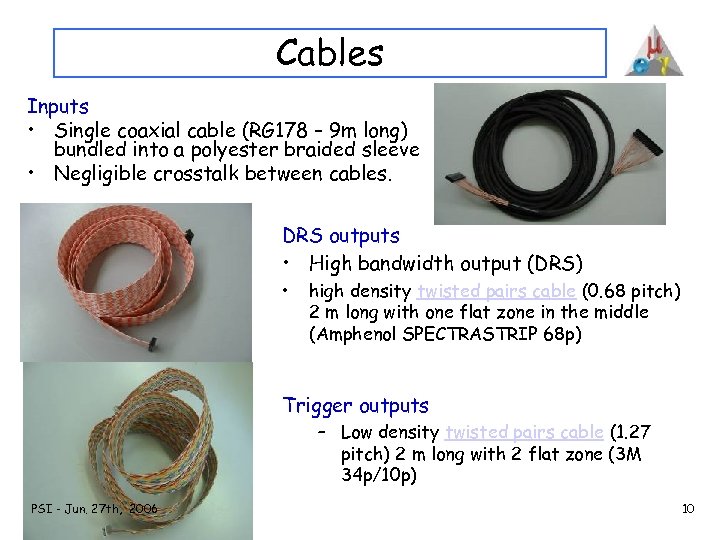

Cables Inputs • Single coaxial cable (RG 178 – 9 m long) bundled into a polyester braided sleeve • Negligible crosstalk between cables. DRS outputs • High bandwidth output (DRS) • high density twisted pairs cable (0. 68 pitch) 2 m long with one flat zone in the middle (Amphenol SPECTRASTRIP 68 p) Trigger outputs – Low density twisted pairs cable (1. 27 pitch) 2 m long with 2 flat zone (3 M 34 p/10 p) PSI - Jun. 27 th, 2006 10

Cables Inputs • Single coaxial cable (RG 178 – 9 m long) bundled into a polyester braided sleeve • Negligible crosstalk between cables. DRS outputs • High bandwidth output (DRS) • high density twisted pairs cable (0. 68 pitch) 2 m long with one flat zone in the middle (Amphenol SPECTRASTRIP 68 p) Trigger outputs – Low density twisted pairs cable (1. 27 pitch) 2 m long with 2 flat zone (3 M 34 p/10 p) PSI - Jun. 27 th, 2006 10

Splitter Summary Splitter – – – – first prototype finished in may successfully PCB production started the first of June PCB production time one month Component procurement in progress Board mounting 2 weeks end of July Board test 1 week Boards ready by the beginning of September Backplane – Crates and power supply delivered – backplane production in Lecce Cables – Trigger cables ready – LXe cables in production – DRS cables in production Installation – Foreseen between September 5 and 20 PSI - Jun. 27 th, 2006 11

Splitter Summary Splitter – – – – first prototype finished in may successfully PCB production started the first of June PCB production time one month Component procurement in progress Board mounting 2 weeks end of July Board test 1 week Boards ready by the beginning of September Backplane – Crates and power supply delivered – backplane production in Lecce Cables – Trigger cables ready – LXe cables in production – DRS cables in production Installation – Foreseen between September 5 and 20 PSI - Jun. 27 th, 2006 11

TC PSI - Jun. 27 th, 2006 12

TC PSI - Jun. 27 th, 2006 12

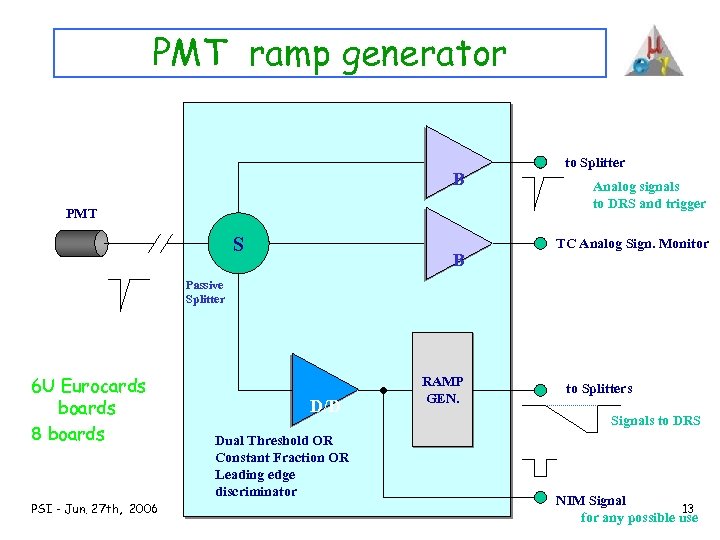

PMT ramp generator B PMT S B to Splitter Analog signals to DRS and trigger TC Analog Sign. Monitor Passive Splitter 6 U Eurocards boards 8 boards PSI - Jun. 27 th, 2006 D/D Dual Threshold OR Constant Fraction OR Leading edge discriminator RAMP GEN. to Splitters Signals to DRS NIM Signal 13 for any possible use

PMT ramp generator B PMT S B to Splitter Analog signals to DRS and trigger TC Analog Sign. Monitor Passive Splitter 6 U Eurocards boards 8 boards PSI - Jun. 27 th, 2006 D/D Dual Threshold OR Constant Fraction OR Leading edge discriminator RAMP GEN. to Splitters Signals to DRS NIM Signal 13 for any possible use

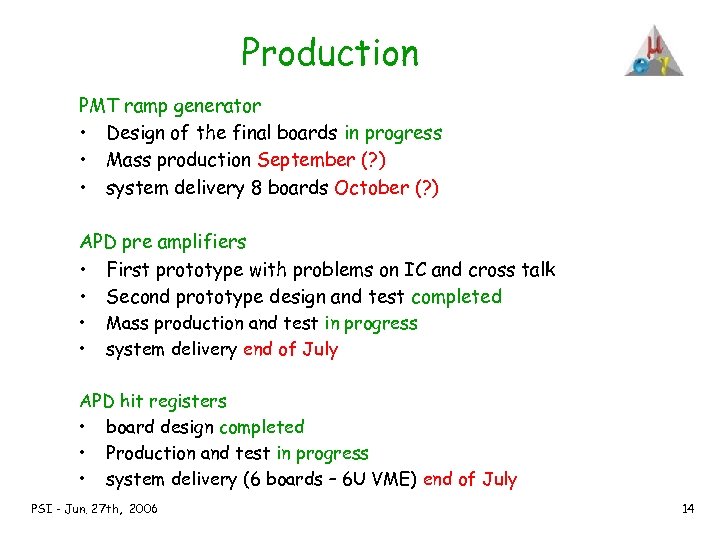

Production PMT ramp generator • Design of the final boards in progress • Mass production September (? ) • system delivery 8 boards October (? ) APD pre amplifiers • First prototype with problems on IC and cross talk • Second prototype design and test completed • Mass production and test in progress • system delivery end of July APD hit registers • board design completed • Production and test in progress • system delivery (6 boards – 6 U VME) end of July PSI - Jun. 27 th, 2006 14

Production PMT ramp generator • Design of the final boards in progress • Mass production September (? ) • system delivery 8 boards October (? ) APD pre amplifiers • First prototype with problems on IC and cross talk • Second prototype design and test completed • Mass production and test in progress • system delivery end of July APD hit registers • board design completed • Production and test in progress • system delivery (6 boards – 6 U VME) end of July PSI - Jun. 27 th, 2006 14

Trigger PSI - Jun. 27 th, 2006 15

Trigger PSI - Jun. 27 th, 2006 15

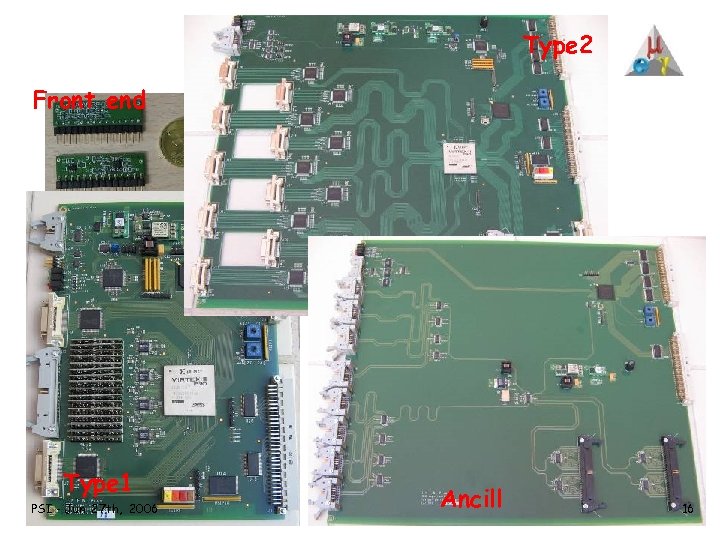

Front end Type 1 PSI - Jun. 27 th, 2006 Trigger Boards Type 2 Ancill 16

Front end Type 1 PSI - Jun. 27 th, 2006 Trigger Boards Type 2 Ancill 16

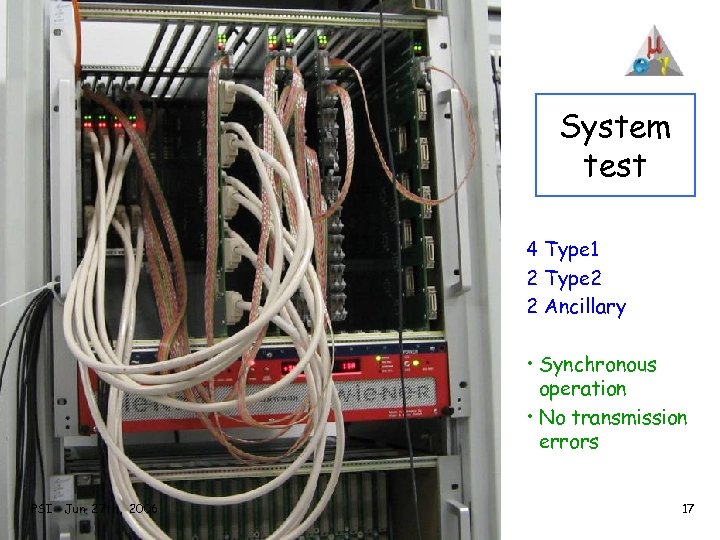

System test 4 Type 1 2 Type 2 2 Ancillary • Synchronous operation • No transmission errors PSI - Jun. 27 th, 2006 17

System test 4 Type 1 2 Type 2 2 Ancillary • Synchronous operation • No transmission errors PSI - Jun. 27 th, 2006 17

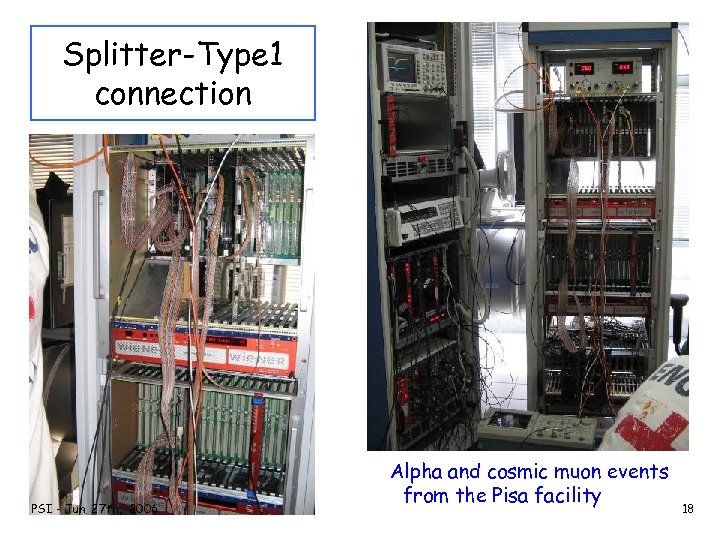

Splitter-Type 1 connection PSI - Jun. 27 th, 2006 Alpha and cosmic muon events from the Pisa facility 18

Splitter-Type 1 connection PSI - Jun. 27 th, 2006 Alpha and cosmic muon events from the Pisa facility 18

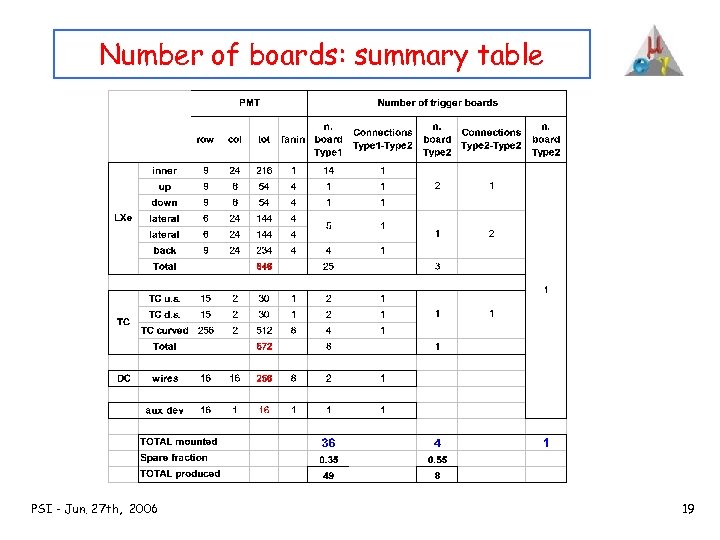

Number of boards: summary table PSI - Jun. 27 th, 2006 19

Number of boards: summary table PSI - Jun. 27 th, 2006 19

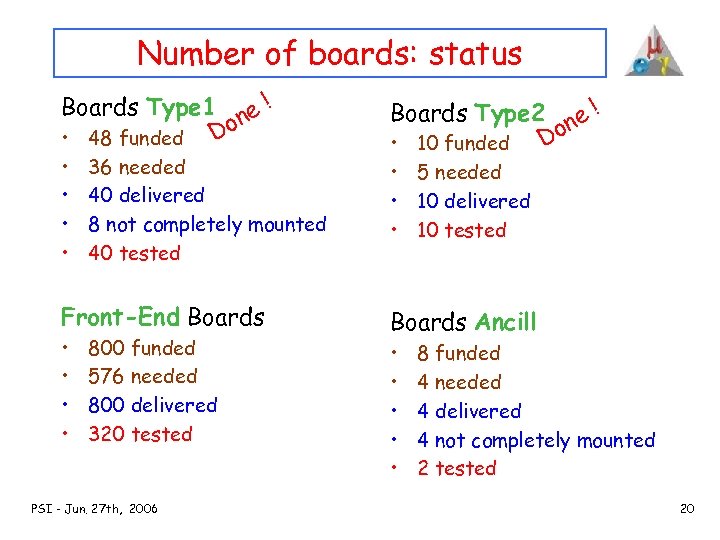

Number of boards: status Boards Type 1 ne ! o • 48 funded D • • 36 needed 40 delivered 8 not completely mounted 40 tested Front-End Boards • • 800 funded 576 needed 800 delivered 320 tested PSI - Jun. 27 th, 2006 Boards Type 2 ne ! Do • 10 funded • 5 needed • 10 delivered • 10 tested Boards Ancill • • • 8 funded 4 needed 4 delivered 4 not completely mounted 2 tested 20

Number of boards: status Boards Type 1 ne ! o • 48 funded D • • 36 needed 40 delivered 8 not completely mounted 40 tested Front-End Boards • • 800 funded 576 needed 800 delivered 320 tested PSI - Jun. 27 th, 2006 Boards Type 2 ne ! Do • 10 funded • 5 needed • 10 delivered • 10 tested Boards Ancill • • • 8 funded 4 needed 4 delivered 4 not completely mounted 2 tested 20

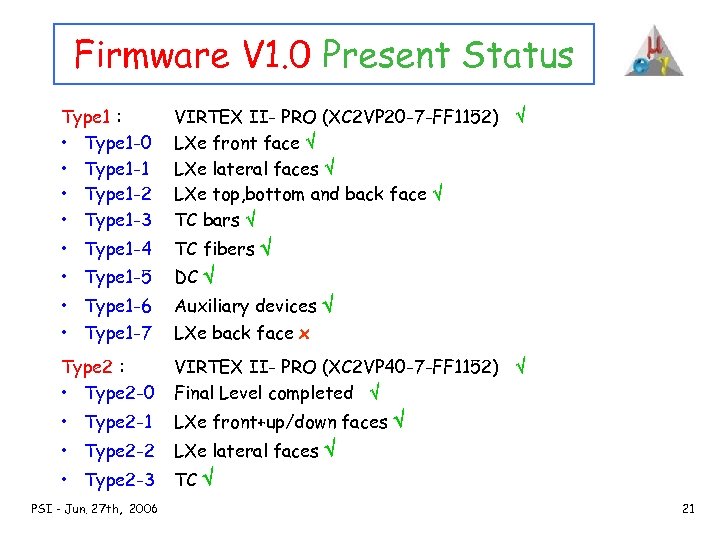

Firmware V 1. 0 Present Status Type 1 : • Type 1 -0 • Type 1 -1 • Type 1 -2 • Type 1 -3 VIRTEX II- PRO (XC 2 VP 20 -7 -FF 1152) LXe front face LXe lateral faces LXe top, bottom and back face TC bars • Type 1 -4 TC fibers • Type 1 -5 DC • Type 1 -6 • Type 1 -7 Auxiliary devices LXe back face x Type 2 : • Type 2 -0 VIRTEX II- PRO (XC 2 VP 40 -7 -FF 1152) Final Level completed • Type 2 -1 LXe front+up/down faces • Type 2 -2 LXe lateral faces • Type 2 -3 TC PSI - Jun. 27 th, 2006 21

Firmware V 1. 0 Present Status Type 1 : • Type 1 -0 • Type 1 -1 • Type 1 -2 • Type 1 -3 VIRTEX II- PRO (XC 2 VP 20 -7 -FF 1152) LXe front face LXe lateral faces LXe top, bottom and back face TC bars • Type 1 -4 TC fibers • Type 1 -5 DC • Type 1 -6 • Type 1 -7 Auxiliary devices LXe back face x Type 2 : • Type 2 -0 VIRTEX II- PRO (XC 2 VP 40 -7 -FF 1152) Final Level completed • Type 2 -1 LXe front+up/down faces • Type 2 -2 LXe lateral faces • Type 2 -3 TC PSI - Jun. 27 th, 2006 21

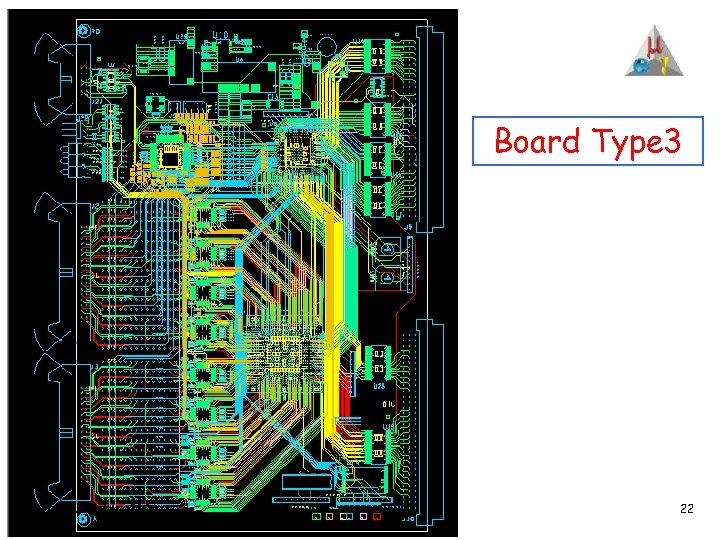

Board Type 3 PSI - Jun. 27 th, 2006 22

Board Type 3 PSI - Jun. 27 th, 2006 22

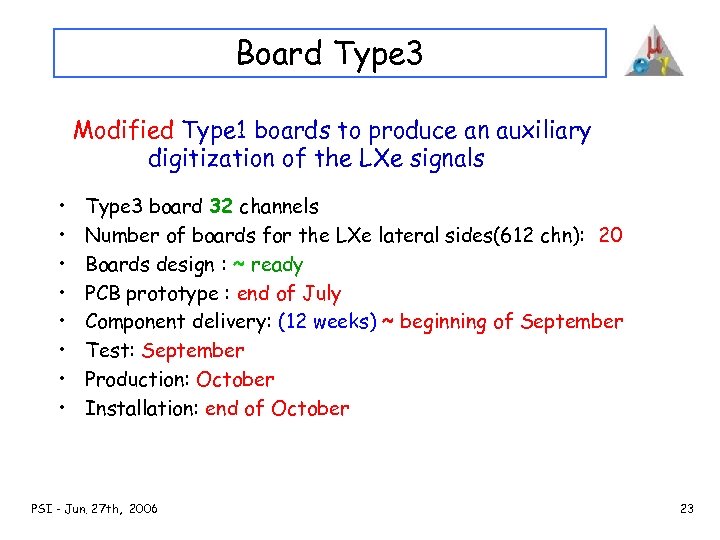

Board Type 3 Modified Type 1 boards to produce an auxiliary digitization of the LXe signals • • Type 3 board 32 channels Number of boards for the LXe lateral sides(612 chn): 20 Boards design : ~ ready PCB prototype : end of July Component delivery: (12 weeks) ~ beginning of September Test: September Production: October Installation: end of October PSI - Jun. 27 th, 2006 23

Board Type 3 Modified Type 1 boards to produce an auxiliary digitization of the LXe signals • • Type 3 board 32 channels Number of boards for the LXe lateral sides(612 chn): 20 Boards design : ~ ready PCB prototype : end of July Component delivery: (12 weeks) ~ beginning of September Test: September Production: October Installation: end of October PSI - Jun. 27 th, 2006 23

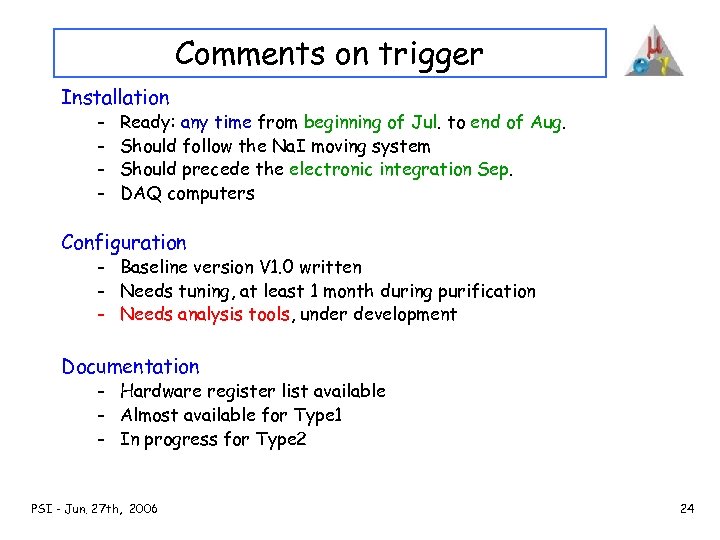

Comments on trigger Installation - Ready: any time from beginning of Jul. to end of Aug. Should follow the Na. I moving system Should precede the electronic integration Sep. DAQ computers Configuration - Baseline version V 1. 0 written - Needs tuning, at least 1 month during purification - Needs analysis tools, under development Documentation - Hardware register list available - Almost available for Type 1 - In progress for Type 2 PSI - Jun. 27 th, 2006 24

Comments on trigger Installation - Ready: any time from beginning of Jul. to end of Aug. Should follow the Na. I moving system Should precede the electronic integration Sep. DAQ computers Configuration - Baseline version V 1. 0 written - Needs tuning, at least 1 month during purification - Needs analysis tools, under development Documentation - Hardware register list available - Almost available for Type 1 - In progress for Type 2 PSI - Jun. 27 th, 2006 24

DRS PSI - Jun. 27 th, 2006 25

DRS PSI - Jun. 27 th, 2006 25

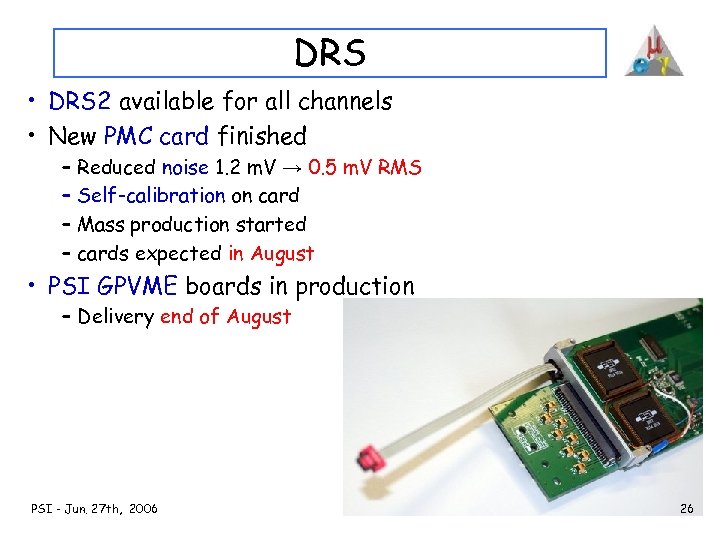

DRS • DRS 2 available for all channels • New PMC card finished – Reduced noise 1. 2 m. V → 0. 5 m. V RMS – Self-calibration on card – Mass production started – cards expected in August • PSI GPVME boards in production – Delivery end of August PSI - Jun. 27 th, 2006 26

DRS • DRS 2 available for all channels • New PMC card finished – Reduced noise 1. 2 m. V → 0. 5 m. V RMS – Self-calibration on card – Mass production started – cards expected in August • PSI GPVME boards in production – Delivery end of August PSI - Jun. 27 th, 2006 26

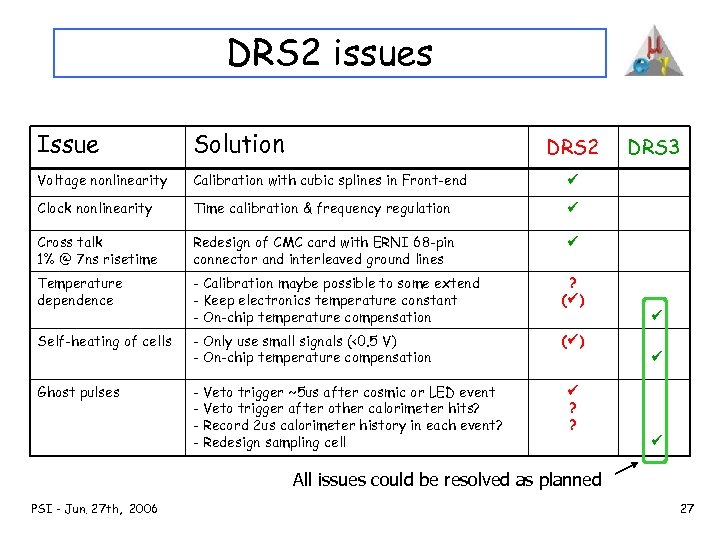

DRS 2 issues Issue Solution Voltage nonlinearity Calibration with cubic splines in Front-end Clock nonlinearity Time calibration & frequency regulation Cross talk 1% @ 7 ns risetime Redesign of CMC card with ERNI 68 -pin connector and interleaved ground lines Temperature dependence - Calibration maybe possible to some extend - Keep electronics temperature constant - On-chip temperature compensation ? ( ) - Only use small signals (<0. 5 V) - On-chip temperature compensation ( ) Self-heating of cells Ghost pulses DRS 2 - Veto trigger ~5 us after cosmic or LED event - Veto trigger after other calorimeter hits? - Record 2 us calorimeter history in each event? - Redesign sampling cell DRS 3 ? ? All issues could be resolved as planned PSI - Jun. 27 th, 2006 27

DRS 2 issues Issue Solution Voltage nonlinearity Calibration with cubic splines in Front-end Clock nonlinearity Time calibration & frequency regulation Cross talk 1% @ 7 ns risetime Redesign of CMC card with ERNI 68 -pin connector and interleaved ground lines Temperature dependence - Calibration maybe possible to some extend - Keep electronics temperature constant - On-chip temperature compensation ? ( ) - Only use small signals (<0. 5 V) - On-chip temperature compensation ( ) Self-heating of cells Ghost pulses DRS 2 - Veto trigger ~5 us after cosmic or LED event - Veto trigger after other calorimeter hits? - Record 2 us calorimeter history in each event? - Redesign sampling cell DRS 3 ? ? All issues could be resolved as planned PSI - Jun. 27 th, 2006 27

DRS 3 • DRS 3 design finished • Prototypes expected in August • Tests foreseen at the end of the year PSI - Jun. 27 th, 2006 28

DRS 3 • DRS 3 design finished • Prototypes expected in August • Tests foreseen at the end of the year PSI - Jun. 27 th, 2006 28

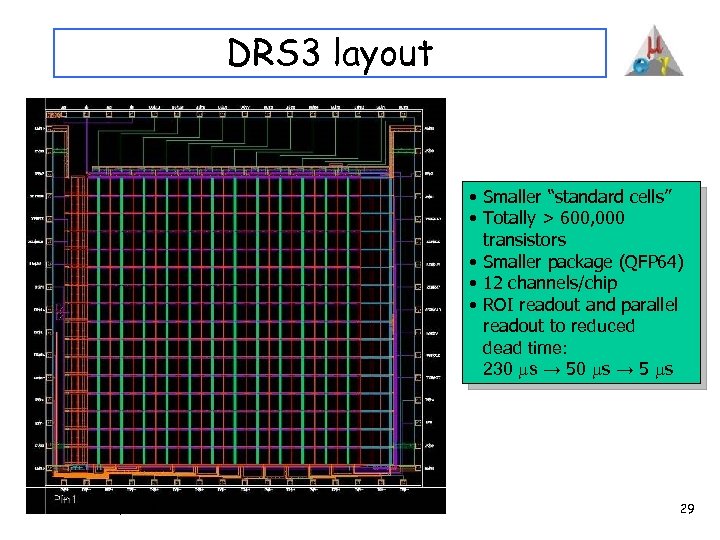

DRS 3 layout • Smaller “standard cells” • Totally > 600, 000 transistors • Smaller package (QFP 64) • 12 channels/chip • ROI readout and parallel readout to reduced dead time: 230 ms → 5 ms PSI - Jun. 27 th, 2006 29

DRS 3 layout • Smaller “standard cells” • Totally > 600, 000 transistors • Smaller package (QFP 64) • 12 channels/chip • ROI readout and parallel readout to reduced dead time: 230 ms → 5 ms PSI - Jun. 27 th, 2006 29

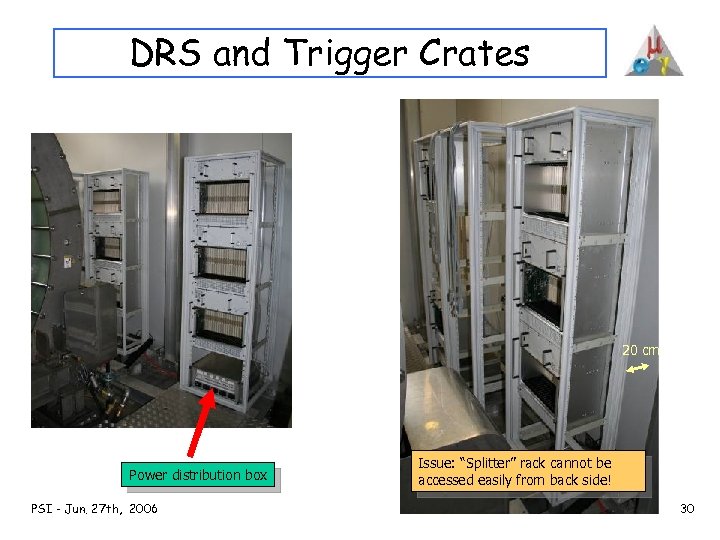

DRS and Trigger Crates 20 cm Power distribution box PSI - Jun. 27 th, 2006 Issue: “Splitter” rack cannot be accessed easily from back side! 30

DRS and Trigger Crates 20 cm Power distribution box PSI - Jun. 27 th, 2006 Issue: “Splitter” rack cannot be accessed easily from back side! 30

DAQ cluster PSI - Jun. 27 th, 2006 31

DAQ cluster PSI - Jun. 27 th, 2006 31

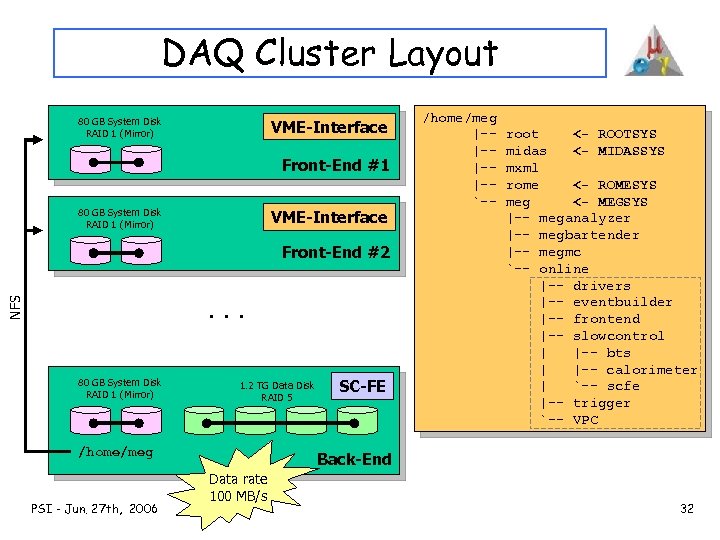

DAQ Cluster Layout 80 GB System Disk RAID 1 (Mirror) VME-Interface Front-End #1 80 GB System Disk RAID 1 (Mirror) VME-Interface Front-End #2 NFS . . . 80 GB System Disk RAID 1 (Mirror) 1. 2 TG Data Disk RAID 5 /home/meg PSI - Jun. 27 th, 2006 SC-FE /home/meg |-|-`-- root <- ROOTSYS midas <- MIDASSYS mxml rome <- ROMESYS meg <- MEGSYS |-- meganalyzer |-- megbartender |-- megmc `-- online |-- drivers |-- eventbuilder |-- frontend |-- slowcontrol | |-- bts | |-- calorimeter | `-- scfe |-- trigger `-- VPC Back-End Data rate 100 MB/s 32

DAQ Cluster Layout 80 GB System Disk RAID 1 (Mirror) VME-Interface Front-End #1 80 GB System Disk RAID 1 (Mirror) VME-Interface Front-End #2 NFS . . . 80 GB System Disk RAID 1 (Mirror) 1. 2 TG Data Disk RAID 5 /home/meg PSI - Jun. 27 th, 2006 SC-FE /home/meg |-|-`-- root <- ROOTSYS midas <- MIDASSYS mxml rome <- ROMESYS meg <- MEGSYS |-- meganalyzer |-- megbartender |-- megmc `-- online |-- drivers |-- eventbuilder |-- frontend |-- slowcontrol | |-- bts | |-- calorimeter | `-- scfe |-- trigger `-- VPC Back-End Data rate 100 MB/s 32

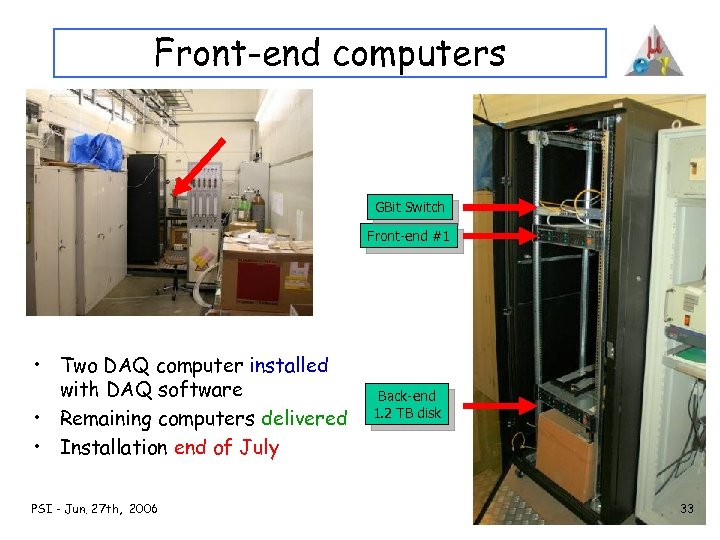

Front-end computers GBit Switch Front-end #1 • Two DAQ computer installed with DAQ software • Remaining computers delivered • Installation end of July PSI - Jun. 27 th, 2006 Back-end 1. 2 TB disk 33

Front-end computers GBit Switch Front-end #1 • Two DAQ computer installed with DAQ software • Remaining computers delivered • Installation end of July PSI - Jun. 27 th, 2006 Back-end 1. 2 TB disk 33

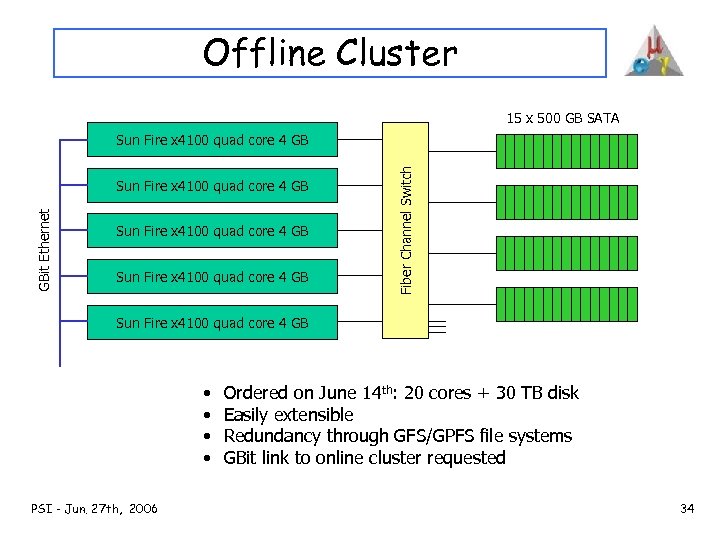

Offline Cluster 15 x 500 GB SATA GBit Ethernet Sun Fire x 4100 quad core 4 GB Fiber Channel Switch Sun Fire x 4100 quad core 4 GB • • PSI - Jun. 27 th, 2006 Ordered on June 14 th: 20 cores + 30 TB disk Easily extensible Redundancy through GFS/GPFS file systems GBit link to online cluster requested 34

Offline Cluster 15 x 500 GB SATA GBit Ethernet Sun Fire x 4100 quad core 4 GB Fiber Channel Switch Sun Fire x 4100 quad core 4 GB • • PSI - Jun. 27 th, 2006 Ordered on June 14 th: 20 cores + 30 TB disk Easily extensible Redundancy through GFS/GPFS file systems GBit link to online cluster requested 34

Slow control PSI - Jun. 27 th, 2006 35

Slow control PSI - Jun. 27 th, 2006 35

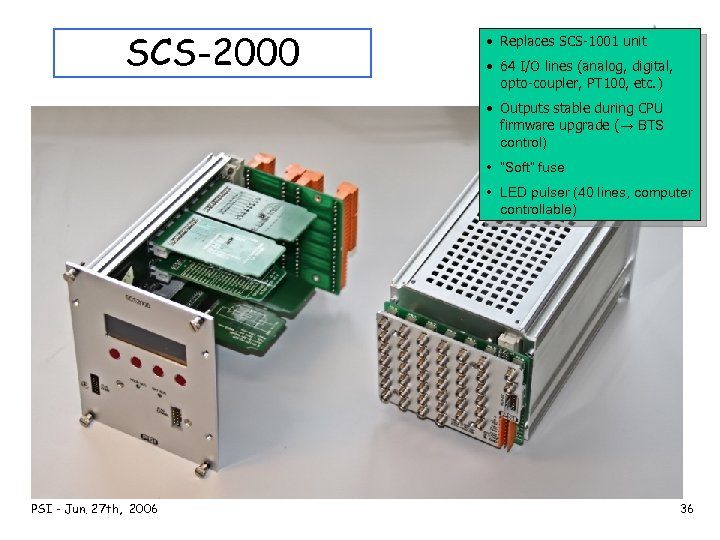

SCS-2000 • Replaces SCS-1001 unit • 64 I/O lines (analog, digital, opto-coupler, PT 100, etc. ) • Outputs stable during CPU firmware upgrade (→ BTS control) • “Soft” fuse • LED pulser (40 lines, computer controllable) PSI - Jun. 27 th, 2006 36

SCS-2000 • Replaces SCS-1001 unit • 64 I/O lines (analog, digital, opto-coupler, PT 100, etc. ) • Outputs stable during CPU firmware upgrade (→ BTS control) • “Soft” fuse • LED pulser (40 lines, computer controllable) PSI - Jun. 27 th, 2006 36

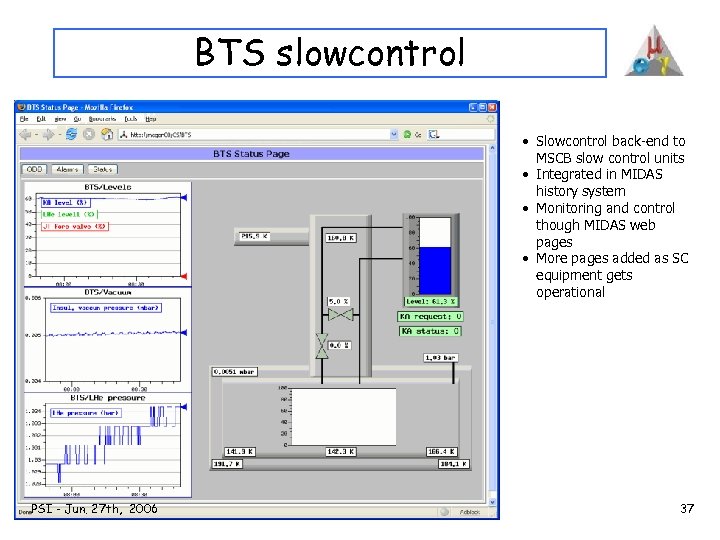

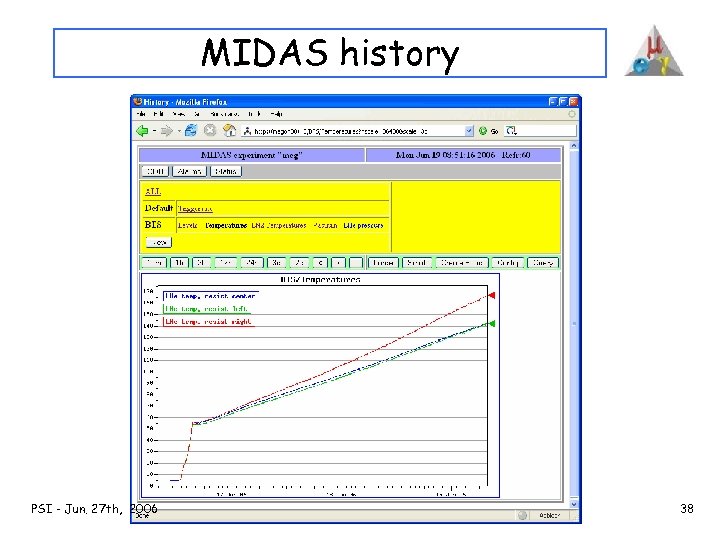

BTS slowcontrol • Slowcontrol back-end to MSCB slow control units • Integrated in MIDAS history system • Monitoring and control though MIDAS web pages • More pages added as SC equipment gets operational PSI - Jun. 27 th, 2006 37

BTS slowcontrol • Slowcontrol back-end to MSCB slow control units • Integrated in MIDAS history system • Monitoring and control though MIDAS web pages • More pages added as SC equipment gets operational PSI - Jun. 27 th, 2006 37

MIDAS history PSI - Jun. 27 th, 2006 38

MIDAS history PSI - Jun. 27 th, 2006 38

Conclusions • All the key elements of the electronic system are available for integration in September • Some parts will arrive with ~1 month delay PSI - Jun. 27 th, 2006 39

Conclusions • All the key elements of the electronic system are available for integration in September • Some parts will arrive with ~1 month delay PSI - Jun. 27 th, 2006 39

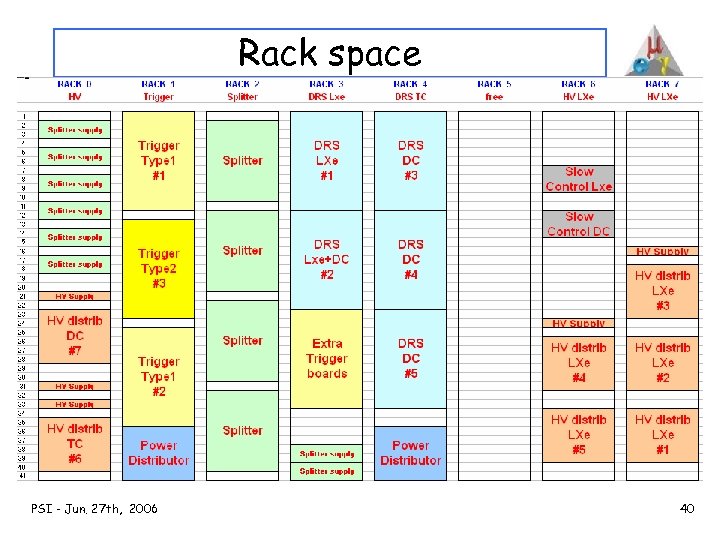

Rack space PSI - Jun. 27 th, 2006 40

Rack space PSI - Jun. 27 th, 2006 40