9ec1858610f345ea327d0f61264330ab.ppt

- Количество слайдов: 16

STAR Pixel Detector readout prototyping status

STAR Pixel Detector readout prototyping status

Talk Outline • Quick review of requirements and system design • Status at last meeting at IPHC • RDO hardware status • RDO firmware and software status • Future development path LBNL-IPHC-06/2009 - LG 2

Talk Outline • Quick review of requirements and system design • Status at last meeting at IPHC • RDO hardware status • RDO firmware and software status • Future development path LBNL-IPHC-06/2009 - LG 2

RDO Requirements and Design In addition to the detailed requirements imposed by the interface to the sensors, the RDO system shall: • Triggered detector system fitting into existing STAR infrastructure (Trigger, DAQ, etc. ) • Deliver full frame events to STAR DAQ for event building at approximately the same rate as the TPC (1 k. Hz for DAQ 1000). • Have live time characteristics such that the Pixel detector is live whenever the TPC is live. • Reduce the total data rate of the detector to a manageable level (< TPC rate of ~1 MB / event). • Reliable, robust, cost effective, etc. Furthermore, this RDO system will be the basis of the future sensor testing including production probe testing so additional functionality will be included to enable this system to have the needed additional capabilities. LBNL-IPHC-06/2009 - LG 3

RDO Requirements and Design In addition to the detailed requirements imposed by the interface to the sensors, the RDO system shall: • Triggered detector system fitting into existing STAR infrastructure (Trigger, DAQ, etc. ) • Deliver full frame events to STAR DAQ for event building at approximately the same rate as the TPC (1 k. Hz for DAQ 1000). • Have live time characteristics such that the Pixel detector is live whenever the TPC is live. • Reduce the total data rate of the detector to a manageable level (< TPC rate of ~1 MB / event). • Reliable, robust, cost effective, etc. Furthermore, this RDO system will be the basis of the future sensor testing including production probe testing so additional functionality will be included to enable this system to have the needed additional capabilities. LBNL-IPHC-06/2009 - LG 3

Pixel Detector Design Cabling and cooling infrastructure New beryllium beam pipe (800 µm thick, r = 2 cm) Mechanical support with kinematic mounts Detector extraction at one end of the cone 2 layers 10 modules 4 ladders/module Ladder with 10 MAPS sensors (~ 2× 2 cm each) LBNL-IPHC-06/2009 - LG 4

Pixel Detector Design Cabling and cooling infrastructure New beryllium beam pipe (800 µm thick, r = 2 cm) Mechanical support with kinematic mounts Detector extraction at one end of the cone 2 layers 10 modules 4 ladders/module Ladder with 10 MAPS sensors (~ 2× 2 cm each) LBNL-IPHC-06/2009 - LG 4

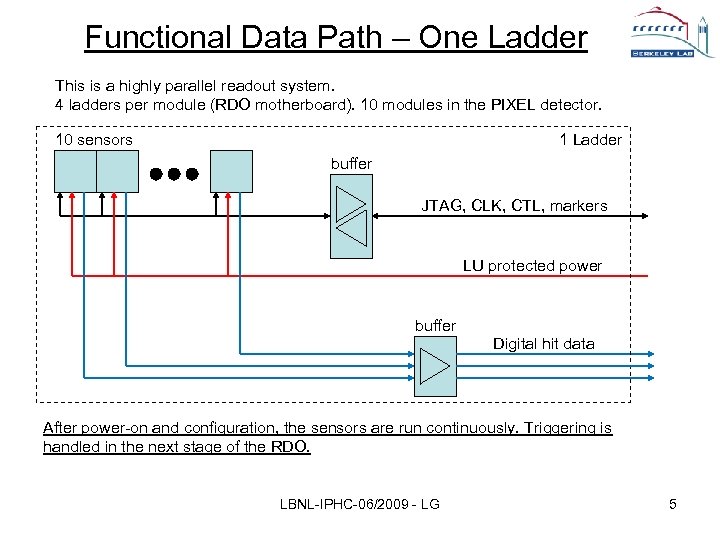

Functional Data Path – One Ladder This is a highly parallel readout system. 4 ladders per module (RDO motherboard). 10 modules in the PIXEL detector. 10 sensors 1 Ladder buffer JTAG, CLK, CTL, markers LU protected power buffer Digital hit data After power-on and configuration, the sensors are run continuously. Triggering is handled in the next stage of the RDO. LBNL-IPHC-06/2009 - LG 5

Functional Data Path – One Ladder This is a highly parallel readout system. 4 ladders per module (RDO motherboard). 10 modules in the PIXEL detector. 10 sensors 1 Ladder buffer JTAG, CLK, CTL, markers LU protected power buffer Digital hit data After power-on and configuration, the sensors are run continuously. Triggering is handled in the next stage of the RDO. LBNL-IPHC-06/2009 - LG 5

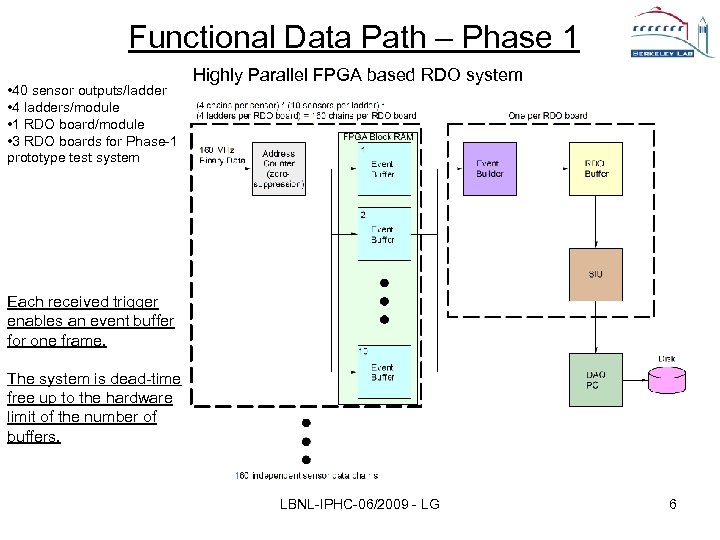

Functional Data Path – Phase 1 • 40 sensor outputs/ladder • 4 ladders/module • 1 RDO board/module • 3 RDO boards for Phase-1 prototype test system Highly Parallel FPGA based RDO system Each received trigger enables an event buffer for one frame. The system is dead-time free up to the hardware limit of the number of buffers. LBNL-IPHC-06/2009 - LG 6

Functional Data Path – Phase 1 • 40 sensor outputs/ladder • 4 ladders/module • 1 RDO board/module • 3 RDO boards for Phase-1 prototype test system Highly Parallel FPGA based RDO system Each received trigger enables an event buffer for one frame. The system is dead-time free up to the hardware limit of the number of buffers. LBNL-IPHC-06/2009 - LG 6

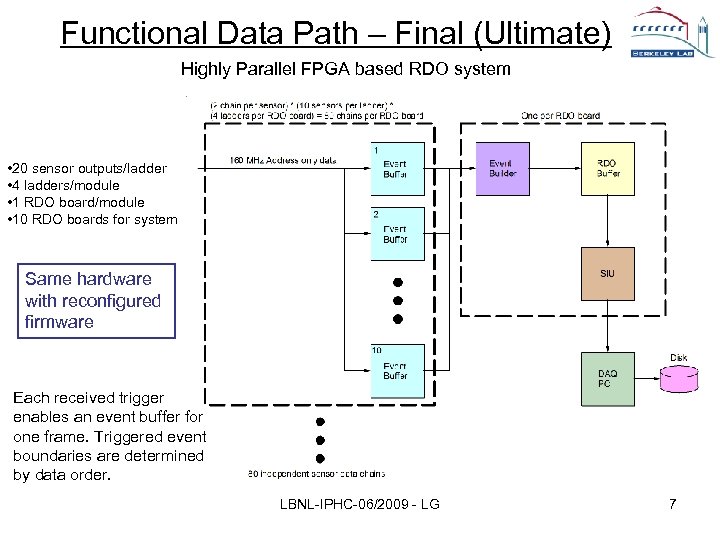

Functional Data Path – Final (Ultimate) Highly Parallel FPGA based RDO system • 20 sensor outputs/ladder • 4 ladders/module • 1 RDO board/module • 10 RDO boards for system Same hardware with reconfigured firmware Each received trigger enables an event buffer for one frame. Triggered event boundaries are determined by data order. LBNL-IPHC-06/2009 - LG 7

Functional Data Path – Final (Ultimate) Highly Parallel FPGA based RDO system • 20 sensor outputs/ladder • 4 ladders/module • 1 RDO board/module • 10 RDO boards for system Same hardware with reconfigured firmware Each received trigger enables an event buffer for one frame. Triggered event boundaries are determined by data order. LBNL-IPHC-06/2009 - LG 7

RDO System Design – Physical Layout Sensors, Ladders, Modules (interaction point) 1 -2 m Low mass twisted pair LU Protected Regulators, Mass cable termination 6 m - twisted pair RDO Boards (Low Rad Area) Platform 30 m Power Supplies 30 m DAQ Room 100 m - Fiber optic Platform DAQ PCs Control PCs 30 m LBNL-IPHC-06/2009 - LG 8

RDO System Design – Physical Layout Sensors, Ladders, Modules (interaction point) 1 -2 m Low mass twisted pair LU Protected Regulators, Mass cable termination 6 m - twisted pair RDO Boards (Low Rad Area) Platform 30 m Power Supplies 30 m DAQ Room 100 m - Fiber optic Platform DAQ PCs Control PCs 30 m LBNL-IPHC-06/2009 - LG 8

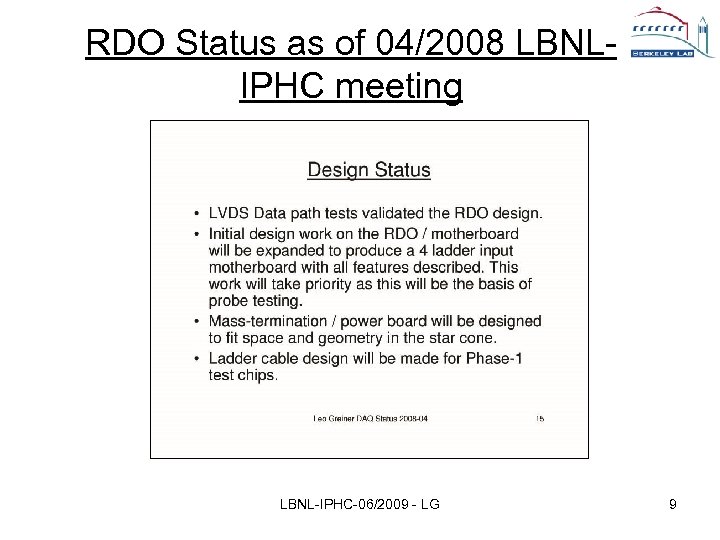

RDO Status as of 04/2008 LBNLIPHC meeting LBNL-IPHC-06/2009 - LG 9

RDO Status as of 04/2008 LBNLIPHC meeting LBNL-IPHC-06/2009 - LG 9

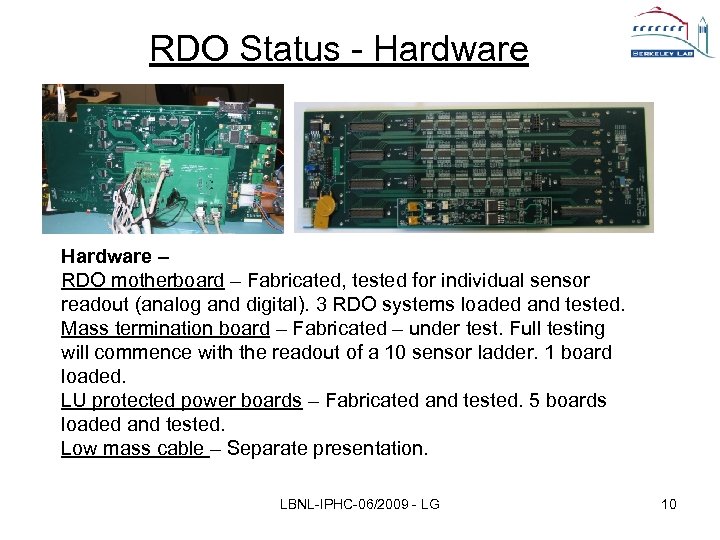

RDO Status - Hardware – RDO motherboard – Fabricated, tested for individual sensor readout (analog and digital). 3 RDO systems loaded and tested. Mass termination board – Fabricated – under test. Full testing will commence with the readout of a 10 sensor ladder. 1 board loaded. LU protected power boards – Fabricated and tested. 5 boards loaded and tested. Low mass cable – Separate presentation. LBNL-IPHC-06/2009 - LG 10

RDO Status - Hardware – RDO motherboard – Fabricated, tested for individual sensor readout (analog and digital). 3 RDO systems loaded and tested. Mass termination board – Fabricated – under test. Full testing will commence with the readout of a 10 sensor ladder. 1 board loaded. LU protected power boards – Fabricated and tested. 5 boards loaded and tested. Low mass cable – Separate presentation. LBNL-IPHC-06/2009 - LG 10

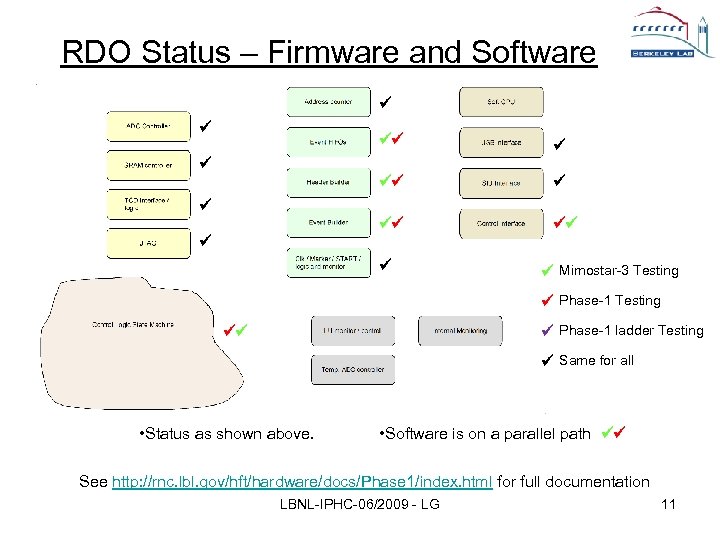

RDO Status – Firmware and Software Mimostar-3 Testing Phase-1 ladder Testing Same for all • Status as shown above. • Software is on a parallel path See http: //rnc. lbl. gov/hft/hardware/docs/Phase 1/index. html for full documentation LBNL-IPHC-06/2009 - LG 11

RDO Status – Firmware and Software Mimostar-3 Testing Phase-1 ladder Testing Same for all • Status as shown above. • Software is on a parallel path See http: //rnc. lbl. gov/hft/hardware/docs/Phase 1/index. html for full documentation LBNL-IPHC-06/2009 - LG 11

RDO Status – Firmware and Software • Phase-1 readout firmware and software complete and working for analog and digital data for individual sensor testing. • DDL optical link and USB based data paths are both functional. • Analysis software for Phase-1 data is mostly complete. We are using both Root and Labview based analysis paths. • Scripting needed for automated testing of sensors is complete and working. • The analysis path for 10 sensor ladders is expected to be a simple extension of the existing framework. LBNL-IPHC-06/2009 - LG 12

RDO Status – Firmware and Software • Phase-1 readout firmware and software complete and working for analog and digital data for individual sensor testing. • DDL optical link and USB based data paths are both functional. • Analysis software for Phase-1 data is mostly complete. We are using both Root and Labview based analysis paths. • Scripting needed for automated testing of sensors is complete and working. • The analysis path for 10 sensor ladders is expected to be a simple extension of the existing framework. LBNL-IPHC-06/2009 - LG 12

RDO Status – Future Development • Adaptation of the existing individual testing system for use in automated probe testing. • Development of the 10 sensor ladder readout firmware and software. • Design and implementation of a slow control system for the detector. • Extension of the system into multi-ladder / multisector readout. LBNL-IPHC-06/2009 - LG 13

RDO Status – Future Development • Adaptation of the existing individual testing system for use in automated probe testing. • Development of the 10 sensor ladder readout firmware and software. • Design and implementation of a slow control system for the detector. • Extension of the system into multi-ladder / multisector readout. LBNL-IPHC-06/2009 - LG 13

end LBNL-IPHC-06/2009 - LG 14

end LBNL-IPHC-06/2009 - LG 14

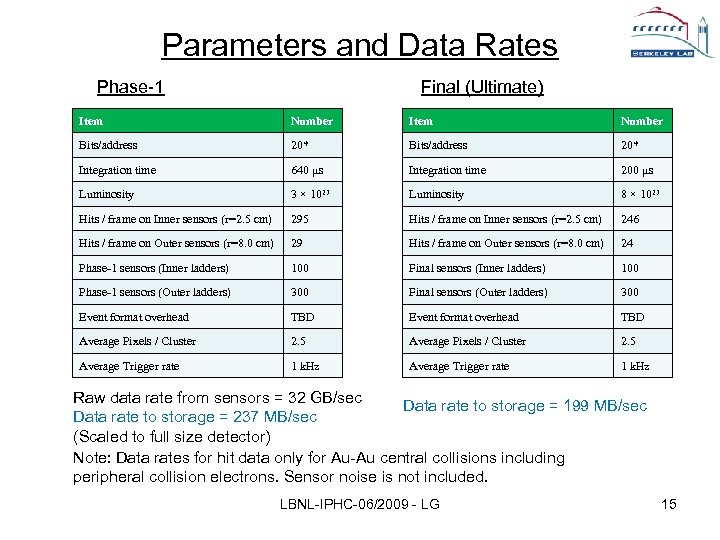

Parameters and Data Rates Phase-1 Item Final (Ultimate) Number Item Number Bits/address 20 20* Bits/address Integration time 640 µs Luminosity 3 × 1027 Hits / frame on Inner sensors 295 Hits / frame on Inner sensors (r=2. 5 cm) Bits/address 20 20* Bits/address Integration time 200 µs Luminosity 8 × 1027 Hits / frame on Inner sensors 246 Hits / frame oncm) sensors (r=2. 5 cm) (r=2. 5 Inner Hits / frame on Outer sensors cm) 29 / frame on Outer sensors (r=8. 0 29 (r=8. 0 cm) Phase-1 sensors (Inner ladders) 100 Phase-1 sensors (Outer ladders) 300 Event format overhead TBD Hits / frame on Outer sensors (r=8. 0 cm) 24 (r=8. 0 cm) Final sensors (Inner ladders) 100 Final sensors (Outer ladders) 300 Event format overhead TBD 24 Average Pixels / Cluster 2. 5 Average Trigger rate 1 k. Hz 100 300 TBD Raw data rate from sensors = 32 GB/sec Data rate to storage = 199 MB/sec Data rate to storage = 237 MB/sec (Scaled to full size detector) Note: Data rates for hit data only for Au-Au central collisions including peripheral collision electrons. Sensor noise is not included. LBNL-IPHC-06/2009 - LG 15

Parameters and Data Rates Phase-1 Item Final (Ultimate) Number Item Number Bits/address 20 20* Bits/address Integration time 640 µs Luminosity 3 × 1027 Hits / frame on Inner sensors 295 Hits / frame on Inner sensors (r=2. 5 cm) Bits/address 20 20* Bits/address Integration time 200 µs Luminosity 8 × 1027 Hits / frame on Inner sensors 246 Hits / frame oncm) sensors (r=2. 5 cm) (r=2. 5 Inner Hits / frame on Outer sensors cm) 29 / frame on Outer sensors (r=8. 0 29 (r=8. 0 cm) Phase-1 sensors (Inner ladders) 100 Phase-1 sensors (Outer ladders) 300 Event format overhead TBD Hits / frame on Outer sensors (r=8. 0 cm) 24 (r=8. 0 cm) Final sensors (Inner ladders) 100 Final sensors (Outer ladders) 300 Event format overhead TBD 24 Average Pixels / Cluster 2. 5 Average Trigger rate 1 k. Hz 100 300 TBD Raw data rate from sensors = 32 GB/sec Data rate to storage = 199 MB/sec Data rate to storage = 237 MB/sec (Scaled to full size detector) Note: Data rates for hit data only for Au-Au central collisions including peripheral collision electrons. Sensor noise is not included. LBNL-IPHC-06/2009 - LG 15

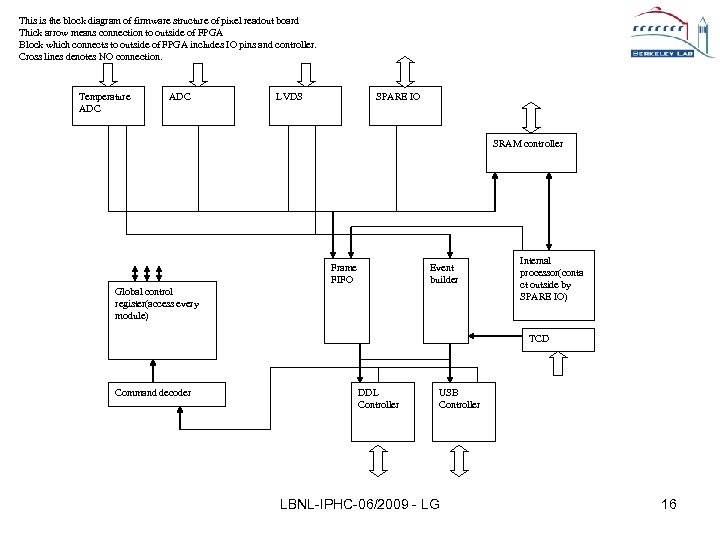

This is the block diagram of firmware structure of pixel readout board Thick arrow means connection to outside of FPGA Block which connects to outside of FPGA includes IO pins and controller. Cross lines denotes NO connection. Temperature ADC LVDS SPARE IO SRAM controller Frame FIFO Event builder Global control register(access every module) Internal processor(conta ct outside by SPARE IO) TCD Command decoder DDL Controller USB Controller LBNL-IPHC-06/2009 - LG 16

This is the block diagram of firmware structure of pixel readout board Thick arrow means connection to outside of FPGA Block which connects to outside of FPGA includes IO pins and controller. Cross lines denotes NO connection. Temperature ADC LVDS SPARE IO SRAM controller Frame FIFO Event builder Global control register(access every module) Internal processor(conta ct outside by SPARE IO) TCD Command decoder DDL Controller USB Controller LBNL-IPHC-06/2009 - LG 16