926e0bc68f3b2c9b036bab4305673e80.ppt

- Количество слайдов: 24

Standards in Design Automation: Influencing Design and Verification Methodologies Yatin Trivedi Standards Education Committee, IEEE-SA Director of Standards, Synopsys February 11, 2011

Standards in Design Automation: Influencing Design and Verification Methodologies Yatin Trivedi Standards Education Committee, IEEE-SA Director of Standards, Synopsys February 11, 2011

Contents Standards in Design Automation Benefits of EDA standards Successful Standards 2

Contents Standards in Design Automation Benefits of EDA standards Successful Standards 2

EDA: Where Electronics Begins Software “tools” for chip design – Architecture design – Functional design and verification – Physical design and verification – Various electrical analyses Standards improve productivity – Tool interoperability – Data exchange, sharing, and consistency

EDA: Where Electronics Begins Software “tools” for chip design – Architecture design – Functional design and verification – Physical design and verification – Various electrical analyses Standards improve productivity – Tool interoperability – Data exchange, sharing, and consistency

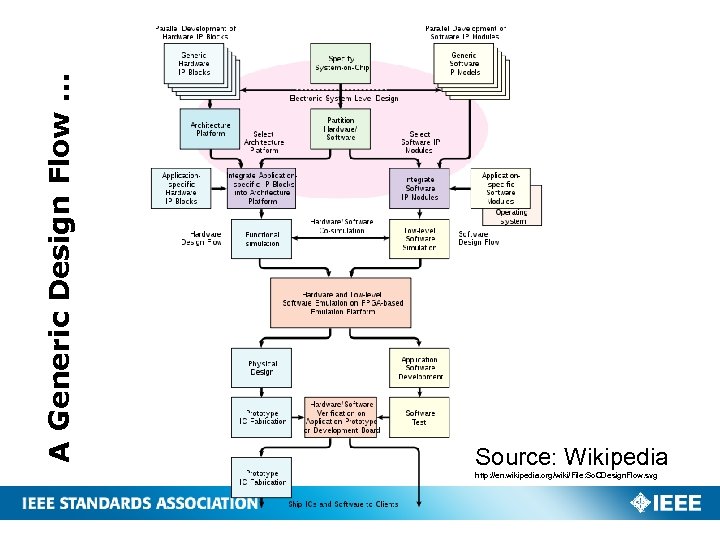

A Generic Design Flow … Source: Wikipedia http: //en. wikipedia. org/wiki/File: So. CDesign. Flow. svg

A Generic Design Flow … Source: Wikipedia http: //en. wikipedia. org/wiki/File: So. CDesign. Flow. svg

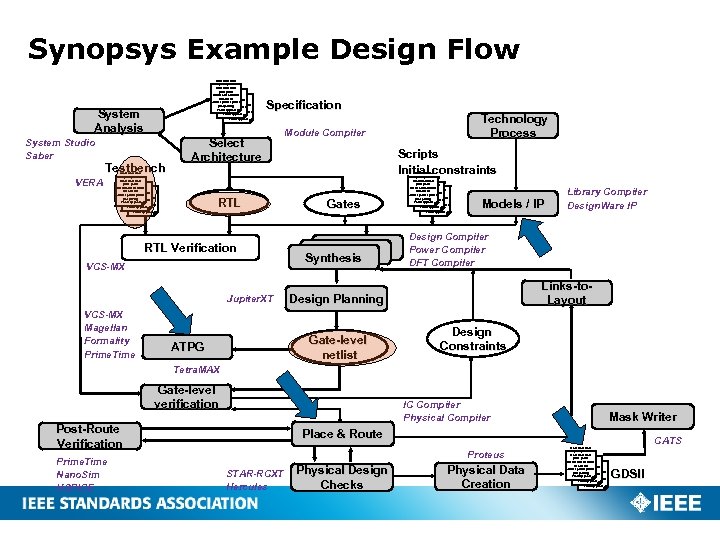

Synopsys Example Design Flow Blah blah yada blah Blah blah yada Blah yidie yadie blah Blah blah So on and soyada forth yidie yadie blah Blah blah on and on so forth So on and Jibber jabberyidie yadie jibber on on So and on just jawing and so forth Jibber jabber jibber on Yackety yackand on just jawing jibber Jibber jabber Ya'll com back Yackety yack just jawing Ya'll com back Yackety yack System Analysis System Studio Saber Testbench VERA Specification Select Architecture Blah blah yada blah Blah blah yada Blah yidie yadie blah Blah blah So on and soyada forth yidie yadie on on Blah blah So and on so forth and Jibber jabberyidie yadie jibber on on So and on just jawing and so forth Jibber jabber jibber on Yackety yackand on just jawing Jibber jabber jibber Ya'll com back Yackety yack just jawing Ya'll com back Yackety yack RTL Module Compiler Scripts Initial constraints Gates Ya'll com back Blah blah yada blah Blah blah yada Blah yidie yadie blah Blah blah So on and soyada forth yidie yadie on on Blah blah So and on so forth and Jibber jabberyidie yadie jibber on on So and on just jawing and so forth Jibber jabber jibber on Yackety yackand on just jawing Jibber jabber jibber Ya'll com back Yackety yack just jawing Ya'll com back Yackety yack Models / IP Library Compiler Design. Ware IP Ya'll com back RTL Verification VCS-MX Jupiter. XT VCS-MX Magellan Formality Prime. Time Technology Process Ya'll com back Synthesis Links-to. Layout Design Planning Gate-level netlist ATPG Design Compiler Power Compiler DFT Compiler Design Constraints Tetra. MAX Gate-level verification IC Compiler Physical Compiler Post-Route Verification Prime. Time Nano. Sim HSPICE Mask Writer Place & Route CATS Proteus STAR-RCXT Hercules Physical Design Checks Physical Data Creation Blah blah yada blah Blah blah yada Blah yidie yadie blah Blah blah So on and soyada forth yidie yadie on on Blah blah So and on so yadie and forth Jibber jabberyidie jibber on and on so forth So on just jawing and Jibber jabber jibber on Yackety yackand on just jawing Jibber jabber jibber Ya'll com back Yackety yack just jawing Ya'll com back Yackety yack Ya'll com back GDSII

Synopsys Example Design Flow Blah blah yada blah Blah blah yada Blah yidie yadie blah Blah blah So on and soyada forth yidie yadie blah Blah blah on and on so forth So on and Jibber jabberyidie yadie jibber on on So and on just jawing and so forth Jibber jabber jibber on Yackety yackand on just jawing jibber Jibber jabber Ya'll com back Yackety yack just jawing Ya'll com back Yackety yack System Analysis System Studio Saber Testbench VERA Specification Select Architecture Blah blah yada blah Blah blah yada Blah yidie yadie blah Blah blah So on and soyada forth yidie yadie on on Blah blah So and on so forth and Jibber jabberyidie yadie jibber on on So and on just jawing and so forth Jibber jabber jibber on Yackety yackand on just jawing Jibber jabber jibber Ya'll com back Yackety yack just jawing Ya'll com back Yackety yack RTL Module Compiler Scripts Initial constraints Gates Ya'll com back Blah blah yada blah Blah blah yada Blah yidie yadie blah Blah blah So on and soyada forth yidie yadie on on Blah blah So and on so forth and Jibber jabberyidie yadie jibber on on So and on just jawing and so forth Jibber jabber jibber on Yackety yackand on just jawing Jibber jabber jibber Ya'll com back Yackety yack just jawing Ya'll com back Yackety yack Models / IP Library Compiler Design. Ware IP Ya'll com back RTL Verification VCS-MX Jupiter. XT VCS-MX Magellan Formality Prime. Time Technology Process Ya'll com back Synthesis Links-to. Layout Design Planning Gate-level netlist ATPG Design Compiler Power Compiler DFT Compiler Design Constraints Tetra. MAX Gate-level verification IC Compiler Physical Compiler Post-Route Verification Prime. Time Nano. Sim HSPICE Mask Writer Place & Route CATS Proteus STAR-RCXT Hercules Physical Design Checks Physical Data Creation Blah blah yada blah Blah blah yada Blah yidie yadie blah Blah blah So on and soyada forth yidie yadie on on Blah blah So and on so yadie and forth Jibber jabberyidie jibber on and on so forth So on just jawing and Jibber jabber jibber on Yackety yackand on just jawing Jibber jabber jibber Ya'll com back Yackety yack just jawing Ya'll com back Yackety yack Ya'll com back GDSII

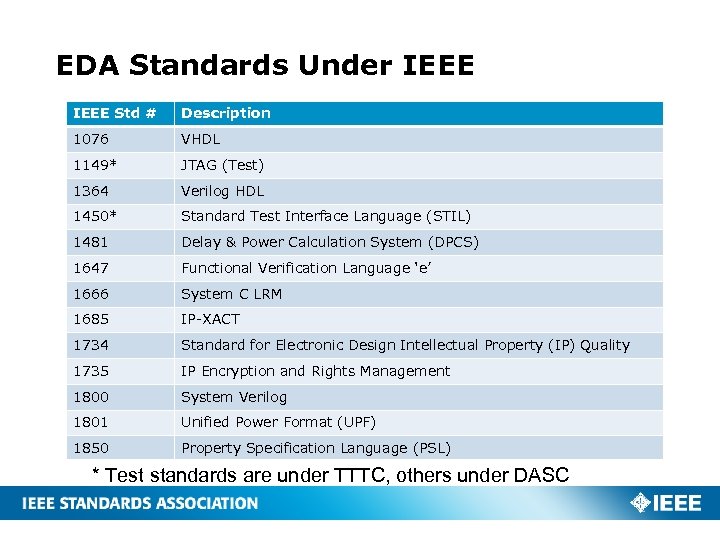

EDA Standards Under IEEE Std # Description 1076 VHDL 1149* JTAG (Test) 1364 Verilog HDL 1450* Standard Test Interface Language (STIL) 1481 Delay & Power Calculation System (DPCS) 1647 Functional Verification Language ‘e’ 1666 System C LRM 1685 IP-XACT 1734 Standard for Electronic Design Intellectual Property (IP) Quality 1735 IP Encryption and Rights Management 1800 System Verilog 1801 Unified Power Format (UPF) 1850 Property Specification Language (PSL) * Test standards are under TTTC, others under DASC

EDA Standards Under IEEE Std # Description 1076 VHDL 1149* JTAG (Test) 1364 Verilog HDL 1450* Standard Test Interface Language (STIL) 1481 Delay & Power Calculation System (DPCS) 1647 Functional Verification Language ‘e’ 1666 System C LRM 1685 IP-XACT 1734 Standard for Electronic Design Intellectual Property (IP) Quality 1735 IP Encryption and Rights Management 1800 System Verilog 1801 Unified Power Format (UPF) 1850 Property Specification Language (PSL) * Test standards are under TTTC, others under DASC

Contents Standards in Design Automation Benefits of EDA standards Successful Standards 7

Contents Standards in Design Automation Benefits of EDA standards Successful Standards 7

Benefits to EDA Tool Developers Don’t have to address entire design flow – Too complex for small EDA companies Focus on core strengths – Standards help partition the problem Integrate tools in design team’s flow – Interoperability means new business opportunities Ability to promote own technology for widespread usage as a standard

Benefits to EDA Tool Developers Don’t have to address entire design flow – Too complex for small EDA companies Focus on core strengths – Standards help partition the problem Integrate tools in design team’s flow – Interoperability means new business opportunities Ability to promote own technology for widespread usage as a standard

Benefits to EDA Tool Users Portability of design data across multiple tools Users’ in-house special-purpose tools integrate easily with commercial tools Reuse of design data – Among different projects – Among different design teams Faster learning curve Build customized design flow to suit specific requirements Better management over tool purchases

Benefits to EDA Tool Users Portability of design data across multiple tools Users’ in-house special-purpose tools integrate easily with commercial tools Reuse of design data – Among different projects – Among different design teams Faster learning curve Build customized design flow to suit specific requirements Better management over tool purchases

EDA Standards Collaboration with Industry Availability of the standard is synchronized with many marketing/promotional activities – Several product rollouts – Launching of web site • (e. g. , www. systemverilog. org) – – Consultants doing tutorials Seminar series by vendors User groups Papers, articles, blogs, … Wide adoption by user community – When the standard solves REAL problems, it is quickly adopted – Marketing the standard helps to accelerate its adoption rate – Wider community adoption accelerates tool maturity, use models, and entirely new methodologies – Leads to continued enhancement of the standard

EDA Standards Collaboration with Industry Availability of the standard is synchronized with many marketing/promotional activities – Several product rollouts – Launching of web site • (e. g. , www. systemverilog. org) – – Consultants doing tutorials Seminar series by vendors User groups Papers, articles, blogs, … Wide adoption by user community – When the standard solves REAL problems, it is quickly adopted – Marketing the standard helps to accelerate its adoption rate – Wider community adoption accelerates tool maturity, use models, and entirely new methodologies – Leads to continued enhancement of the standard

EDA Standards Collaboration with Industry (cont. ) EDA standards-setting organizations bridge to IEEE – Accellera, SPIRIT, OSCI/System. C – Incubate standards, then transfer to IEEE EDA’s IEEE standards are sponsored by – Design Automation Standards Committee (DASC) – Test Technology Council (TTTC)

EDA Standards Collaboration with Industry (cont. ) EDA standards-setting organizations bridge to IEEE – Accellera, SPIRIT, OSCI/System. C – Incubate standards, then transfer to IEEE EDA’s IEEE standards are sponsored by – Design Automation Standards Committee (DASC) – Test Technology Council (TTTC)

Case Study: System. Verilog – A Success from Concept to Standard Computer language for IC design An industry-wide collaborative effort that started in 2001 – Co-Design, Inc. “invented” Superlog, a derivative/enhancement of Verilog HDL (IEEE 1364) – Company acquired by Synopsys in 2001 – Superlog, with many other internal technologies, proposed as extensions to Verilog for system-level modeling, design, and verification – Called “System. Verilog”, created by Accellera – Six technology donations and many enhancements – New entity-based IEEE WG (P 1800) formed after Accellera approved its System. Verilog standard

Case Study: System. Verilog – A Success from Concept to Standard Computer language for IC design An industry-wide collaborative effort that started in 2001 – Co-Design, Inc. “invented” Superlog, a derivative/enhancement of Verilog HDL (IEEE 1364) – Company acquired by Synopsys in 2001 – Superlog, with many other internal technologies, proposed as extensions to Verilog for system-level modeling, design, and verification – Called “System. Verilog”, created by Accellera – Six technology donations and many enhancements – New entity-based IEEE WG (P 1800) formed after Accellera approved its System. Verilog standard

System. Verilog Journey Ratified as IEEE Std. 1800 -2005 – Started with System. Verilog 3. 1 a from Accellera – Less than one year from transfer to ratification – More than 200 products support the standard – Rapid adoption across design and verification community Ratified as IEEE Std. 1800 -2009 – Verilog IEEE 1364 completely integrated – Large user community looking for design and verification productivity improvement Free tutorial on IEEE Standards Education website

System. Verilog Journey Ratified as IEEE Std. 1800 -2005 – Started with System. Verilog 3. 1 a from Accellera – Less than one year from transfer to ratification – More than 200 products support the standard – Rapid adoption across design and verification community Ratified as IEEE Std. 1800 -2009 – Verilog IEEE 1364 completely integrated – Large user community looking for design and verification productivity improvement Free tutorial on IEEE Standards Education website

System. Verilog Spawned an Entirely New Business Segment Enabled/accelerated IP (design blocks) market segment – One language to write complex design blocks – Same language to verify design blocks – Make IP once, sell many times Many IP providers for design and verification reuse – Networking, wireless, and consumer applications Verification IPs as much in demand as design IPs – New methodologies invented • Assertion based verification, testbench automation – Clear inflection point in the industry to deal with large System -on-Chips

System. Verilog Spawned an Entirely New Business Segment Enabled/accelerated IP (design blocks) market segment – One language to write complex design blocks – Same language to verify design blocks – Make IP once, sell many times Many IP providers for design and verification reuse – Networking, wireless, and consumer applications Verification IPs as much in demand as design IPs – New methodologies invented • Assertion based verification, testbench automation – Clear inflection point in the industry to deal with large System -on-Chips

Contents Standards in Design Automation Benefits of EDA standards Successful Standards 15

Contents Standards in Design Automation Benefits of EDA standards Successful Standards 15

Case Study: IEEE 1801/UPF A Low-Power IC Standard Ever-growing need for low-power ICs in mobile/portable devices and data centers Industry recognized need for low-power IC standard – Common way for design and verification engineers to describe IC’s low-power properties EDA users and vendors came together to develop a format and methodology – Effort started in 2006 under Accellera – Merged 6 technology donations for multi-faceted requirements – Unified Power Format (UPF) created in 6 months Ratified as IEEE Std. 1801 -2009 – Less than 18 months under entity process

Case Study: IEEE 1801/UPF A Low-Power IC Standard Ever-growing need for low-power ICs in mobile/portable devices and data centers Industry recognized need for low-power IC standard – Common way for design and verification engineers to describe IC’s low-power properties EDA users and vendors came together to develop a format and methodology – Effort started in 2006 under Accellera – Merged 6 technology donations for multi-faceted requirements – Unified Power Format (UPF) created in 6 months Ratified as IEEE Std. 1801 -2009 – Less than 18 months under entity process

Case Study: IEEE 1685 IP-XACT Meta-data about semiconductor IP Composing systems using/reusing IP – consistent, complete Originally developed under The SPIRIT Consortium Ratified as SPIRIT standard in 2007 (version 1. 0, 1. 5) XML Schemas published IP-XACT 1. 5 donated to IEEE P 1685 Ratified as IEEE Std. 1685 -2010

Case Study: IEEE 1685 IP-XACT Meta-data about semiconductor IP Composing systems using/reusing IP – consistent, complete Originally developed under The SPIRIT Consortium Ratified as SPIRIT standard in 2007 (version 1. 0, 1. 5) XML Schemas published IP-XACT 1. 5 donated to IEEE P 1685 Ratified as IEEE Std. 1685 -2010

Why Standards Education Is Important Standards education recognizes the key role standards play within the engineering, technology and computing fields. Knowledge of standards can help facilitate the transition from classroom to professional practice by aligning educational concepts with real-world applications. Incorporating standards into the curriculum … Benefits students and faculty mentors as they face challenging design processes Provides tools for use in learning about standards and their impact on design and development 18

Why Standards Education Is Important Standards education recognizes the key role standards play within the engineering, technology and computing fields. Knowledge of standards can help facilitate the transition from classroom to professional practice by aligning educational concepts with real-world applications. Incorporating standards into the curriculum … Benefits students and faculty mentors as they face challenging design processes Provides tools for use in learning about standards and their impact on design and development 18

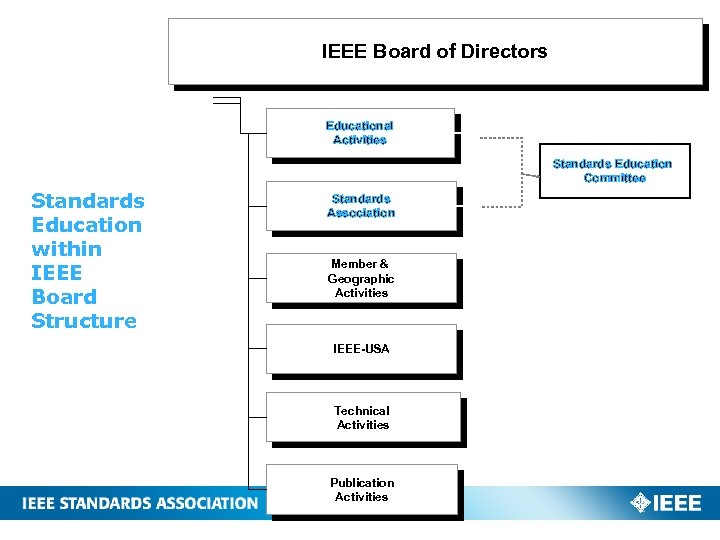

IEEE Board of Directors Educational Activities Standards Education Committee Standards Education within IEEE Board Structure Standards Association Member & Geographic Activities IEEE-USA Technical Activities Publication Activities

IEEE Board of Directors Educational Activities Standards Education Committee Standards Education within IEEE Board Structure Standards Association Member & Geographic Activities IEEE-USA Technical Activities Publication Activities

Mission of the Standards Education Committee Promote the importance of standards in meeting technical, economic, environmental, and societal challenges. Secure and disseminate learning materials on the application of standards in the design and development aspects of educational programs. Secure and provide short courses about standards needed in the design and development phases of professional practice. Actively promote the integration of standards into academic programs. Lead other education initiatives planned jointly by the IEEE Educational Activities Board and the Standards Association. 20

Mission of the Standards Education Committee Promote the importance of standards in meeting technical, economic, environmental, and societal challenges. Secure and disseminate learning materials on the application of standards in the design and development aspects of educational programs. Secure and provide short courses about standards needed in the design and development phases of professional practice. Actively promote the integration of standards into academic programs. Lead other education initiatives planned jointly by the IEEE Educational Activities Board and the Standards Association. 20

Who Benefits? Students • Undergraduate and graduate Technology professionals • Engineers and other technologists • Experienced professionals • Standards developers • Product developers • Standards managers Business leaders Marketing professionals 21

Who Benefits? Students • Undergraduate and graduate Technology professionals • Engineers and other technologists • Experienced professionals • Standards developers • Product developers • Standards managers Business leaders Marketing professionals 21

Ten Commandments of Effective Standards 3/18/2018 22

Ten Commandments of Effective Standards 3/18/2018 22

Conclusion EDA users and vendors have embraced IEEE standards for three decades Large user community active in development of standards along with vendors Standards help broaden infrastructure for the entire industry and academia

Conclusion EDA users and vendors have embraced IEEE standards for three decades Large user community active in development of standards along with vendors Standards help broaden infrastructure for the entire industry and academia

Thank you! 24

Thank you! 24