2ffee8798ed79d58c79cfb68d9db0f88.ppt

- Количество слайдов: 17

Special Manpower Development Programme in VLSI – Phase II 7 th ZOPP Workshop February 10 -11, 2012 Indian Institute of Technology – Kanpur IMPLEMENTATION STATUS OF SMDP-II at RC Name of the Institute : IIT Madras *Coordinator : Vinita Vasudevan *Co-coordinator : Nagendra Krishnapura (*as approved by Institute Director, in case of sabbatical leave , alternate Coordinator /Co-coordinator as approved by Institute Director)

Special Manpower Development Programme in VLSI – Phase II 7 th ZOPP Workshop February 10 -11, 2012 Indian Institute of Technology – Kanpur IMPLEMENTATION STATUS OF SMDP-II at RC Name of the Institute : IIT Madras *Coordinator : Vinita Vasudevan *Co-coordinator : Nagendra Krishnapura (*as approved by Institute Director, in case of sabbatical leave , alternate Coordinator /Co-coordinator as approved by Institute Director)

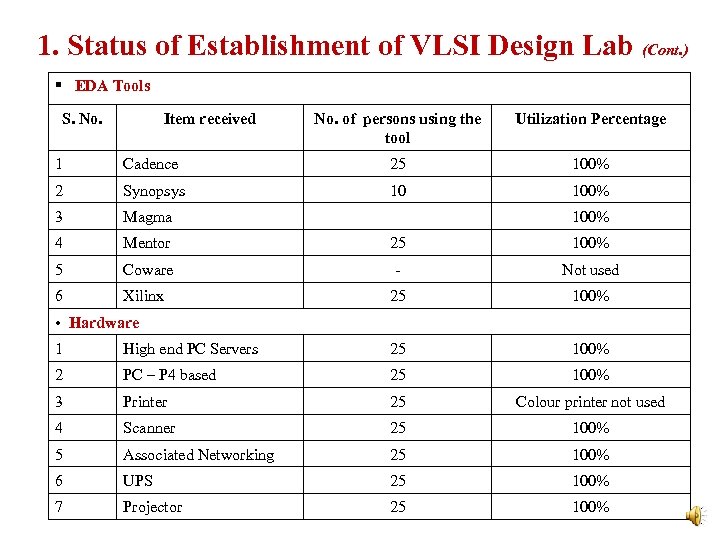

1. Status of Establishment of VLSI Design Lab (Cont. ) § EDA Tools S. No. Item received No. of persons using the tool Utilization Percentage 1 Cadence 25 100% 2 Synopsys 10 100% 3 Magma 4 Mentor 25 100% 5 Coware - Not used 6 Xilinx 25 100% • Hardware 1 High end PC Servers 25 100% 2 PC – P 4 based 25 100% 3 Printer 25 Colour printer not used 4 Scanner 25 100% 5 Associated Networking 25 100% 6 UPS 25 100% 7 Projector 25 100%

1. Status of Establishment of VLSI Design Lab (Cont. ) § EDA Tools S. No. Item received No. of persons using the tool Utilization Percentage 1 Cadence 25 100% 2 Synopsys 10 100% 3 Magma 4 Mentor 25 100% 5 Coware - Not used 6 Xilinx 25 100% • Hardware 1 High end PC Servers 25 100% 2 PC – P 4 based 25 100% 3 Printer 25 Colour printer not used 4 Scanner 25 100% 5 Associated Networking 25 100% 6 UPS 25 100% 7 Projector 25 100%

2. Instruction Enhancement Program-None in 2011 -12 Conducted 1. Topic Date/Duration No. of Participants Attended IEP contents uploaded on RCs / SMDP-II website 2. Topic Date/Duration No. of Participants Attended IEP contents uploaded on RCs / SMDP-II website

2. Instruction Enhancement Program-None in 2011 -12 Conducted 1. Topic Date/Duration No. of Participants Attended IEP contents uploaded on RCs / SMDP-II website 2. Topic Date/Duration No. of Participants Attended IEP contents uploaded on RCs / SMDP-II website

3. Vendor Trainings Conducted During 2011 -12 -None 1. Name of the Institute conducting vendor training : 2. EDA Tool : 3. Date and duration : 4. Name of the specific tool covered in training : 5. No. of Participants attended : 4

3. Vendor Trainings Conducted During 2011 -12 -None 1. Name of the Institute conducting vendor training : 2. EDA Tool : 3. Date and duration : 4. Name of the specific tool covered in training : 5. No. of Participants attended : 4

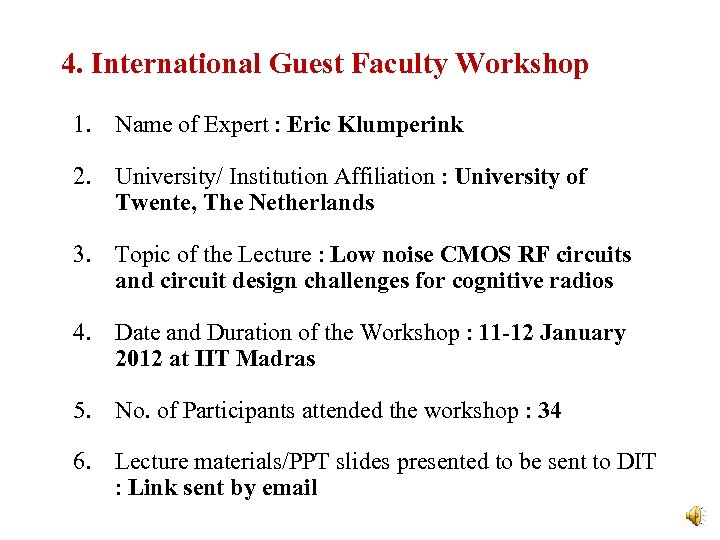

4. International Guest Faculty Workshop 1. Name of Expert : Eric Klumperink 2. University/ Institution Affiliation : University of Twente, The Netherlands 3. Topic of the Lecture : Low noise CMOS RF circuits and circuit design challenges for cognitive radios 4. Date and Duration of the Workshop : 11 -12 January 2012 at IIT Madras 5. No. of Participants attended the workshop : 34 6. Lecture materials/PPT slides presented to be sent to DIT : Link sent by email 5

4. International Guest Faculty Workshop 1. Name of Expert : Eric Klumperink 2. University/ Institution Affiliation : University of Twente, The Netherlands 3. Topic of the Lecture : Low noise CMOS RF circuits and circuit design challenges for cognitive radios 4. Date and Duration of the Workshop : 11 -12 January 2012 at IIT Madras 5. No. of Participants attended the workshop : 34 6. Lecture materials/PPT slides presented to be sent to DIT : Link sent by email 5

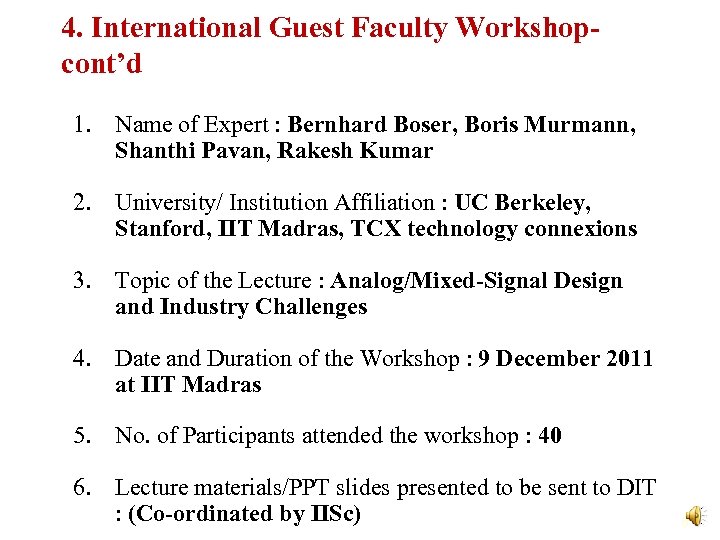

4. International Guest Faculty Workshopcont’d 1. Name of Expert : Bernhard Boser, Boris Murmann, Shanthi Pavan, Rakesh Kumar 2. University/ Institution Affiliation : UC Berkeley, Stanford, IIT Madras, TCX technology connexions 3. Topic of the Lecture : Analog/Mixed-Signal Design and Industry Challenges 4. Date and Duration of the Workshop : 9 December 2011 at IIT Madras 5. No. of Participants attended the workshop : 40 6. Lecture materials/PPT slides presented to be sent to DIT : (Co-ordinated by IISc) 6

4. International Guest Faculty Workshopcont’d 1. Name of Expert : Bernhard Boser, Boris Murmann, Shanthi Pavan, Rakesh Kumar 2. University/ Institution Affiliation : UC Berkeley, Stanford, IIT Madras, TCX technology connexions 3. Topic of the Lecture : Analog/Mixed-Signal Design and Industry Challenges 4. Date and Duration of the Workshop : 9 December 2011 at IIT Madras 5. No. of Participants attended the workshop : 40 6. Lecture materials/PPT slides presented to be sent to DIT : (Co-ordinated by IISc) 6

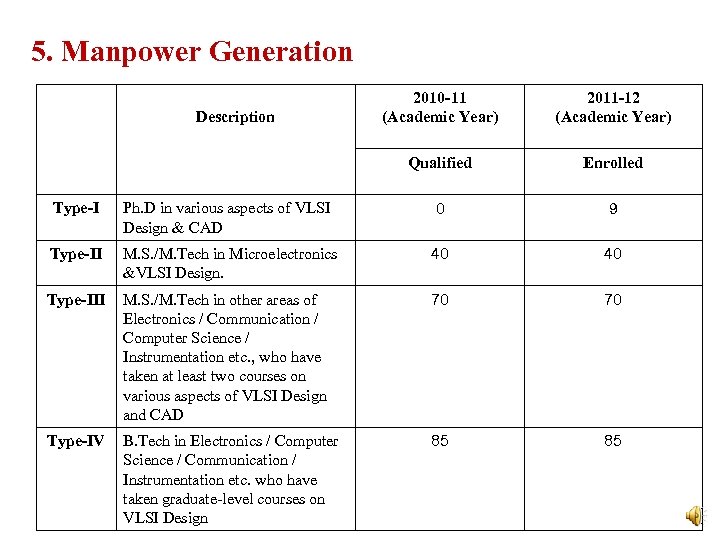

5. Manpower Generation 2011 -12 (Academic Year) Qualified Description 2010 -11 (Academic Year) Enrolled Type-I Ph. D in various aspects of VLSI Design & CAD 0 9 Type-II M. S. /M. Tech in Microelectronics &VLSI Design. 40 40 Type-III M. S. /M. Tech in other areas of Electronics / Communication / Computer Science / Instrumentation etc. , who have taken at least two courses on various aspects of VLSI Design and CAD 70 70 Type-IV B. Tech in Electronics / Computer Science / Communication / Instrumentation etc. who have taken graduate-level courses on VLSI Design 85 85

5. Manpower Generation 2011 -12 (Academic Year) Qualified Description 2010 -11 (Academic Year) Enrolled Type-I Ph. D in various aspects of VLSI Design & CAD 0 9 Type-II M. S. /M. Tech in Microelectronics &VLSI Design. 40 40 Type-III M. S. /M. Tech in other areas of Electronics / Communication / Computer Science / Instrumentation etc. , who have taken at least two courses on various aspects of VLSI Design and CAD 70 70 Type-IV B. Tech in Electronics / Computer Science / Communication / Instrumentation etc. who have taken graduate-level courses on VLSI Design 85 85

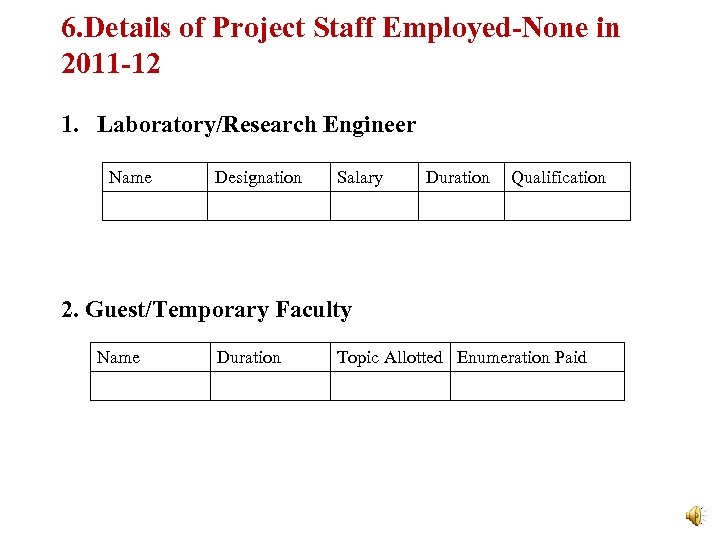

6. Details of Project Staff Employed-None in 2011 -12 1. Laboratory/Research Engineer Name Designation Salary Duration Qualification 2. Guest/Temporary Faculty Name Duration Topic Allotted Enumeration Paid

6. Details of Project Staff Employed-None in 2011 -12 1. Laboratory/Research Engineer Name Designation Salary Duration Qualification 2. Guest/Temporary Faculty Name Duration Topic Allotted Enumeration Paid

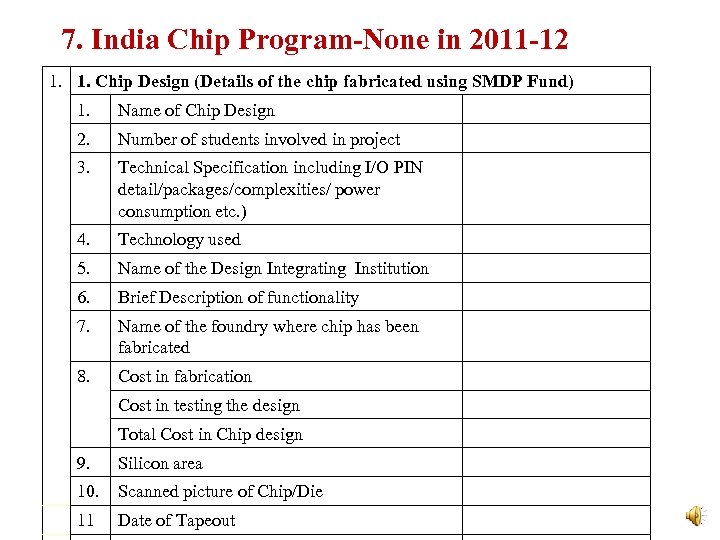

7. India Chip Program-None in 2011 -12 1. 1. Chip Design (Details of the chip fabricated using SMDP Fund) 1. Name of Chip Design 2. Number of students involved in project 3. Technical Specification including I/O PIN detail/packages/complexities/ power consumption etc. ) 4. Technology used 5. Name of the Design Integrating Institution 6. Brief Description of functionality 7. Name of the foundry where chip has been fabricated 8. Cost in fabrication Cost in testing the design Total Cost in Chip design 9. Silicon area 10. Scanned picture of Chip/Die 11 Date of Tapeout

7. India Chip Program-None in 2011 -12 1. 1. Chip Design (Details of the chip fabricated using SMDP Fund) 1. Name of Chip Design 2. Number of students involved in project 3. Technical Specification including I/O PIN detail/packages/complexities/ power consumption etc. ) 4. Technology used 5. Name of the Design Integrating Institution 6. Brief Description of functionality 7. Name of the foundry where chip has been fabricated 8. Cost in fabrication Cost in testing the design Total Cost in Chip design 9. Silicon area 10. Scanned picture of Chip/Die 11 Date of Tapeout

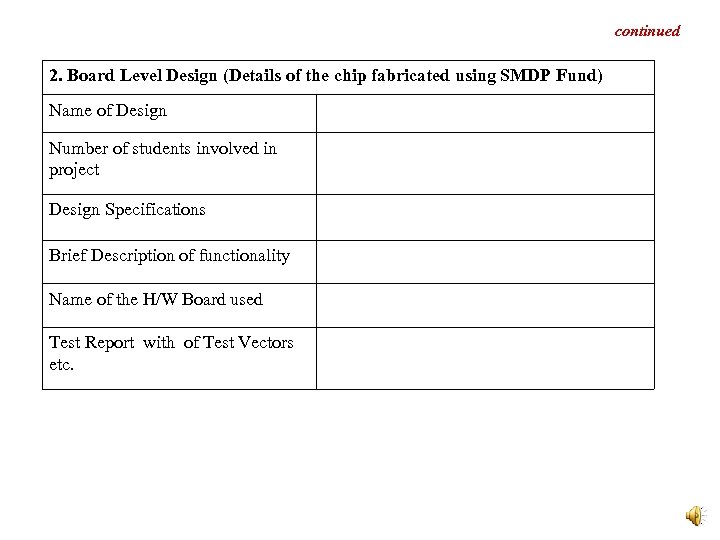

continued 2. Board Level Design (Details of the chip fabricated using SMDP Fund) Name of Design Number of students involved in project Design Specifications Brief Description of functionality Name of the H/W Board used Test Report with of Test Vectors etc.

continued 2. Board Level Design (Details of the chip fabricated using SMDP Fund) Name of Design Number of students involved in project Design Specifications Brief Description of functionality Name of the H/W Board used Test Report with of Test Vectors etc.

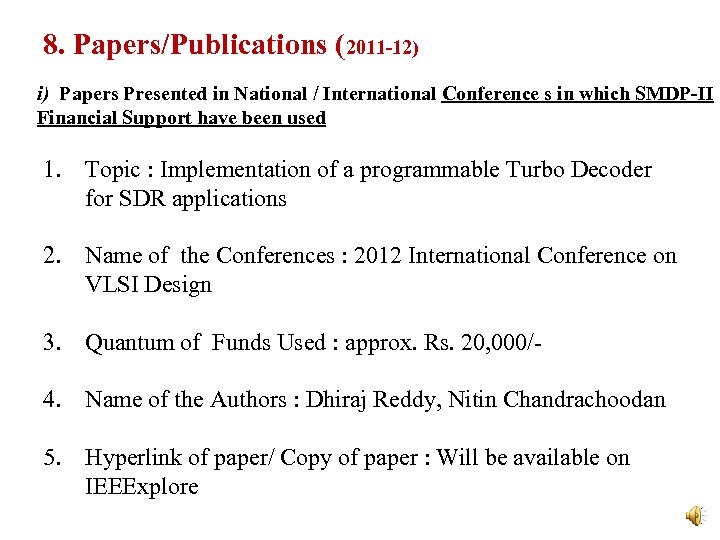

8. Papers/Publications (2011 -12) i) Papers Presented in National / International Conference s in which SMDP-II Financial Support have been used 1. Topic : Implementation of a programmable Turbo Decoder for SDR applications 2. Name of the Conferences : 2012 International Conference on VLSI Design 3. Quantum of Funds Used : approx. Rs. 20, 000/4. Name of the Authors : Dhiraj Reddy, Nitin Chandrachoodan 5. Hyperlink of paper/ Copy of paper : Will be available on IEEExplore

8. Papers/Publications (2011 -12) i) Papers Presented in National / International Conference s in which SMDP-II Financial Support have been used 1. Topic : Implementation of a programmable Turbo Decoder for SDR applications 2. Name of the Conferences : 2012 International Conference on VLSI Design 3. Quantum of Funds Used : approx. Rs. 20, 000/4. Name of the Authors : Dhiraj Reddy, Nitin Chandrachoodan 5. Hyperlink of paper/ Copy of paper : Will be available on IEEExplore

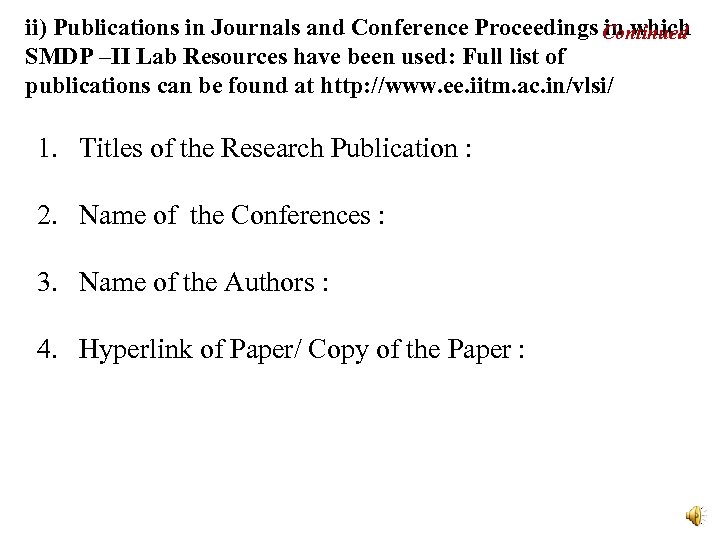

ii) Publications in Journals and Conference Proceedings Continued in which SMDP –II Lab Resources have been used: Full list of publications can be found at http: //www. ee. iitm. ac. in/vlsi/ 1. Titles of the Research Publication : 2. Name of the Conferences : 3. Name of the Authors : 4. Hyperlink of Paper/ Copy of the Paper :

ii) Publications in Journals and Conference Proceedings Continued in which SMDP –II Lab Resources have been used: Full list of publications can be found at http: //www. ee. iitm. ac. in/vlsi/ 1. Titles of the Research Publication : 2. Name of the Conferences : 3. Name of the Authors : 4. Hyperlink of Paper/ Copy of the Paper :

9. Best M. Tech Thesis Award-None in 2011 -12 Nomination for the best thesis for the academic year 2010 -11 M. Tech. Thesis Title Name of Student Name of Supervisor • Has thesis being sent to the respective RCs or DIT. • In case of RCs the best thesis from the respective RCs has to be send directly to DIT. • In case of PIs the best thesis from the respective PIs has to be send to the associated RCs , who in turn would forward the best thesis received from the amongst its PIs and forward the one selected nomination to DIT.

9. Best M. Tech Thesis Award-None in 2011 -12 Nomination for the best thesis for the academic year 2010 -11 M. Tech. Thesis Title Name of Student Name of Supervisor • Has thesis being sent to the respective RCs or DIT. • In case of RCs the best thesis from the respective RCs has to be send directly to DIT. • In case of PIs the best thesis from the respective PIs has to be send to the associated RCs , who in turn would forward the best thesis received from the amongst its PIs and forward the one selected nomination to DIT.

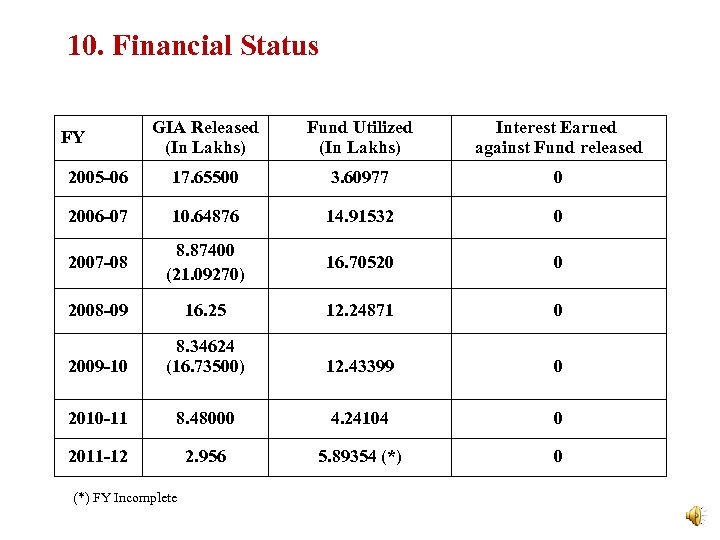

10. Financial Status GIA Released (In Lakhs) Fund Utilized (In Lakhs) Interest Earned against Fund released 2005 -06 17. 65500 3. 60977 0 2006 -07 10. 64876 14. 91532 0 2007 -08 8. 87400 (21. 09270) 16. 70520 0 2008 -09 16. 25 12. 24871 0 2009 -10 8. 34624 (16. 73500) 12. 43399 0 2010 -11 8. 48000 4. 24104 0 2011 -12 2. 956 5. 89354 (*) 0 FY (*) FY Incomplete

10. Financial Status GIA Released (In Lakhs) Fund Utilized (In Lakhs) Interest Earned against Fund released 2005 -06 17. 65500 3. 60977 0 2006 -07 10. 64876 14. 91532 0 2007 -08 8. 87400 (21. 09270) 16. 70520 0 2008 -09 16. 25 12. 24871 0 2009 -10 8. 34624 (16. 73500) 12. 43399 0 2010 -11 8. 48000 4. 24104 0 2011 -12 2. 956 5. 89354 (*) 0 FY (*) FY Incomplete

11. VLSI Placements § No. of B. Tech students placed through the campus recruitment to VLSI/EDA companies: 2 § No. of M. Tech/MS students placed through the campus recruitment to VLSI/EDA companies: 8 § Names of the Companies hiring the B. Tech and the M. Tech students: Aura, Cosmic, Intel, National Instruments, NVidia, Texas Instruments

11. VLSI Placements § No. of B. Tech students placed through the campus recruitment to VLSI/EDA companies: 2 § No. of M. Tech/MS students placed through the campus recruitment to VLSI/EDA companies: 8 § Names of the Companies hiring the B. Tech and the M. Tech students: Aura, Cosmic, Intel, National Instruments, NVidia, Texas Instruments

12. Miscellaneous Information 1. Achievement of SMDP-II in your institution if any which would justify the continuation of Programme in its present form or modified form. 2. Chips to Systems Initiative (C 2 S) : How does your institute propose to participate in the programme being evolved by DIT. Please see the next slide for furnishing details

12. Miscellaneous Information 1. Achievement of SMDP-II in your institution if any which would justify the continuation of Programme in its present form or modified form. 2. Chips to Systems Initiative (C 2 S) : How does your institute propose to participate in the programme being evolved by DIT. Please see the next slide for furnishing details

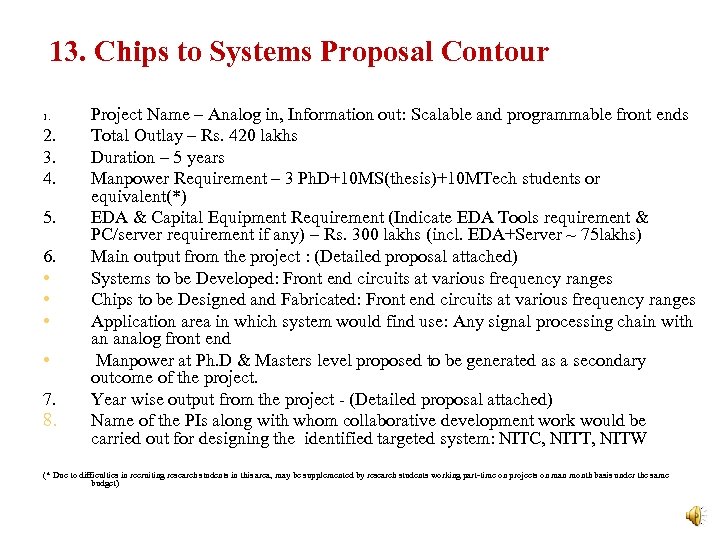

13. Chips to Systems Proposal Contour 1. 2. 3. 4. 5. 6. • • 7. 8. Project Name – Analog in, Information out: Scalable and programmable front ends Total Outlay – Rs. 420 lakhs Duration – 5 years Manpower Requirement – 3 Ph. D+10 MS(thesis)+10 MTech students or equivalent(*) EDA & Capital Equipment Requirement (Indicate EDA Tools requirement & PC/server requirement if any) – Rs. 300 lakhs (incl. EDA+Server ~ 75 lakhs) Main output from the project : (Detailed proposal attached) Systems to be Developed: Front end circuits at various frequency ranges Chips to be Designed and Fabricated: Front end circuits at various frequency ranges Application area in which system would find use: Any signal processing chain with an analog front end Manpower at Ph. D & Masters level proposed to be generated as a secondary outcome of the project. Year wise output from the project - (Detailed proposal attached) Name of the PIs along with whom collaborative development work would be carried out for designing the identified targeted system: NITC, NITT, NITW (* Due to difficulties in recruiting research students in this area, may be supplemented by research students working part-time on projects on man month basis under the same budget)

13. Chips to Systems Proposal Contour 1. 2. 3. 4. 5. 6. • • 7. 8. Project Name – Analog in, Information out: Scalable and programmable front ends Total Outlay – Rs. 420 lakhs Duration – 5 years Manpower Requirement – 3 Ph. D+10 MS(thesis)+10 MTech students or equivalent(*) EDA & Capital Equipment Requirement (Indicate EDA Tools requirement & PC/server requirement if any) – Rs. 300 lakhs (incl. EDA+Server ~ 75 lakhs) Main output from the project : (Detailed proposal attached) Systems to be Developed: Front end circuits at various frequency ranges Chips to be Designed and Fabricated: Front end circuits at various frequency ranges Application area in which system would find use: Any signal processing chain with an analog front end Manpower at Ph. D & Masters level proposed to be generated as a secondary outcome of the project. Year wise output from the project - (Detailed proposal attached) Name of the PIs along with whom collaborative development work would be carried out for designing the identified targeted system: NITC, NITT, NITW (* Due to difficulties in recruiting research students in this area, may be supplemented by research students working part-time on projects on man month basis under the same budget)