Современные микропроцессоры.ppt

- Количество слайдов: 15

Современные микропроцессоры Цель: рассмотреть особенности структуры МП с явным параллелизмом команд.

Ведущие фирмы производители универсальных МП INTEL pentium SUN Sparc DEC Alpha AMD K 5 -K 6 Motorola PC 604, 620 Cyrix IBM Power 6 Hewlett. Packard PA 8000 VIA M 1 -M 2 Atmel AVR Silicon Graphics MIPS R-x

Этапы развития структур универсальных МП Внешние команды CISC ядро RISC компилятор VLIW EPIC Аппаратная оптимизация процесса Программная и аппаратная оптимизация процесса Причина перехода к многоядерности Исчерпана возможность повышения быстродействия за счет повышения частоты. Общая шина - до 32 процессоров. При большем количестве ядер система снижает производительность

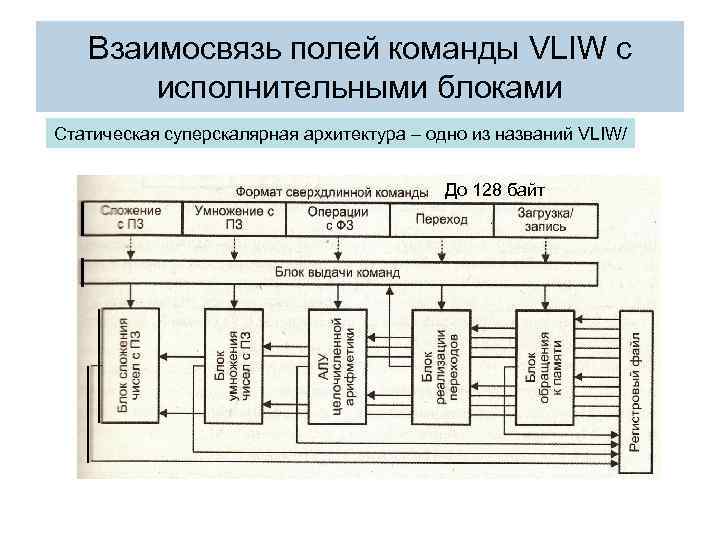

Процессоры VLIW Задача эффективного планирования параллельных вычислений команд возлагается на «разумный» компилятор. Анализ программы Выявление команд RISC, которые могут быть выполнены одновременно и без конфликтов Объединение связок команд в одну длинную команду Исполнение VLIW Правила формирование команды VLIW 1. Количество простых команд равно числу исполнительных блоков процессора 2. Простые команды должны загружать все исполнительные блоки процессора

Взаимосвязь полей команды VLIW с исполнительными блоками Статическая суперскалярная архитектура – одно из названий VLIW/ До 128 байт

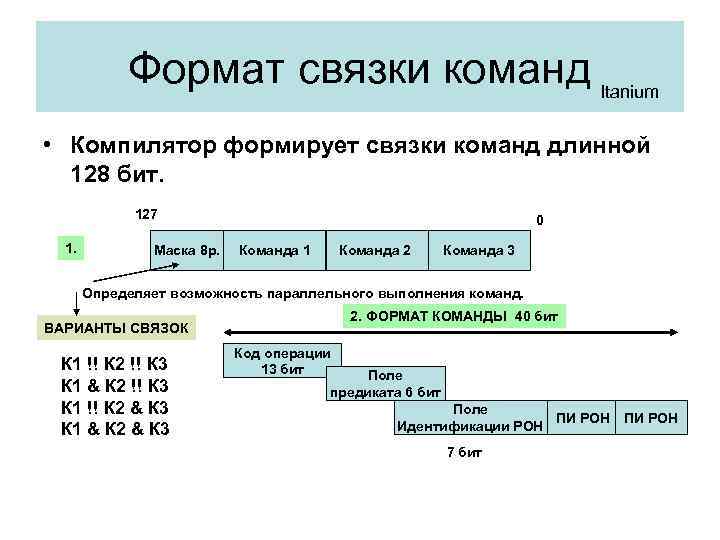

Микропроцессоры с архитектурой Itanium EPIC IA-64, 2001 год Основные отличия архитектур IA-32 и IA-64 IA-32 IA-64 Использование сложных команд переменной длины, обрабатываемых последовательно Использование простых команд одинаковой длины, сгруппированных по 3 Переупорядочивание и оптимизация команд в процессе выполнения Переупорядочивание и оптимизация в процессе компиляции Попытки предсказания переходов аппаратно Параллельное выполнение последовательностей команд без предсказания переходов Загрузка данных по мере необходимости, первым проверяя кэш Загрузка данных прежде, чем они потребуются. IA-64 первый компромисс между CISC и RISC. 2 режима декодирования команд WLIV и CISC c автоматическим переключением.

Формат связки команд Itanium • Компилятор формирует связки команд длинной 128 бит. 127 1. Маска 8 р. 0 Команда 1 Команда 2 Команда 3 Определяет возможность параллельного выполнения команд. 2. ФОРМАТ КОМАНДЫ 40 бит ВАРИАНТЫ СВЯЗОК К 1 !! К 2 !! К 3 К 1 & К 2 !! К 3 К 1 !! К 2 & К 3 К 1 & К 2 & К 3 Код операции 13 бит Поле предиката 6 бит Поле ПИ РОН Идентификации РОН 7 бит

Микропроцессоры с архитектурой IA-64, 2001 год Itanium Кэш L 3 Технология 0. 18 Мкм, частота 660, 733, 800 Мгц. 220 млн. транзисторов

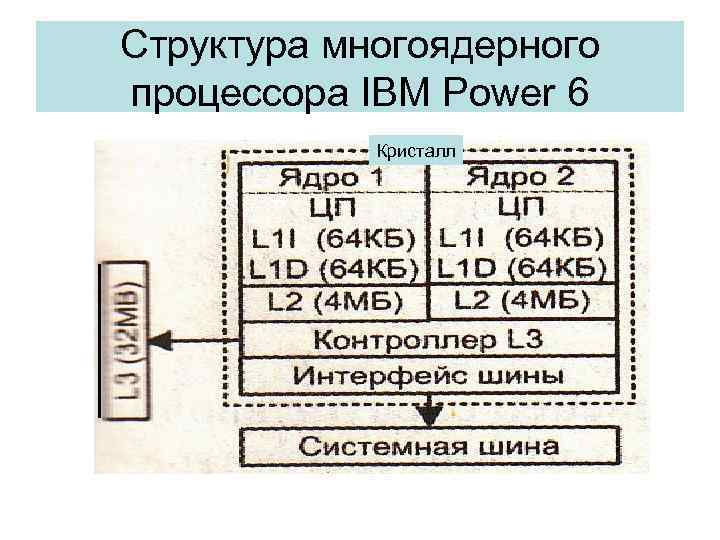

Структура многоядерного процессора IBM Power 6 Кристалл

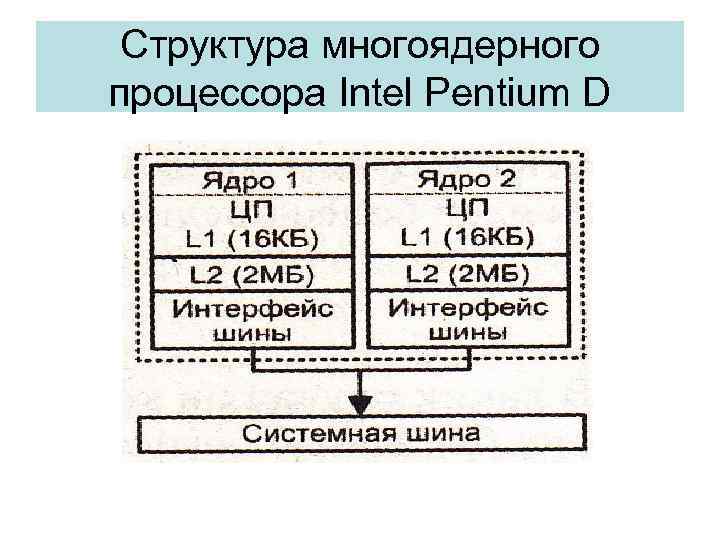

Структура многоядерного процессора Intel Pentium D

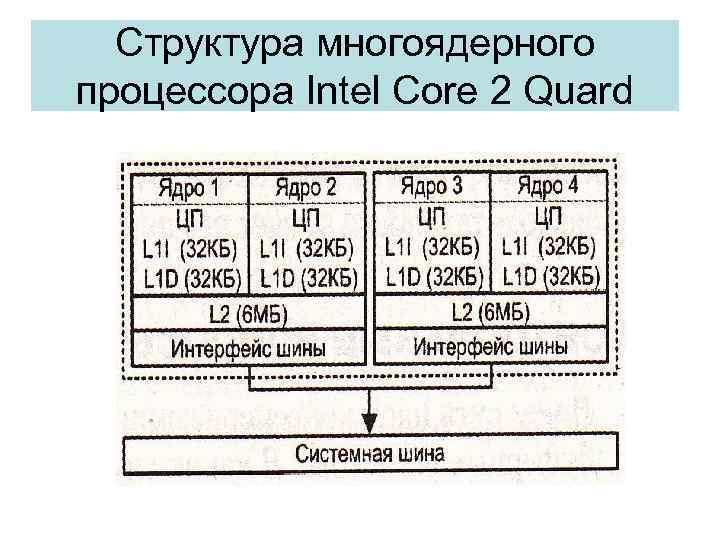

Структура многоядерного процессора Intel Core 2 Quard

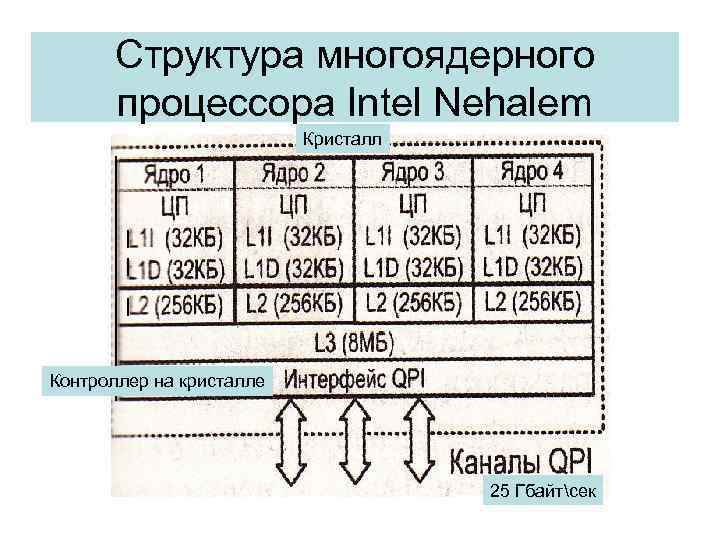

Структура многоядерного процессора Intel Nehalem Кристалл Контроллер на кристалле 25 Гбайтсек

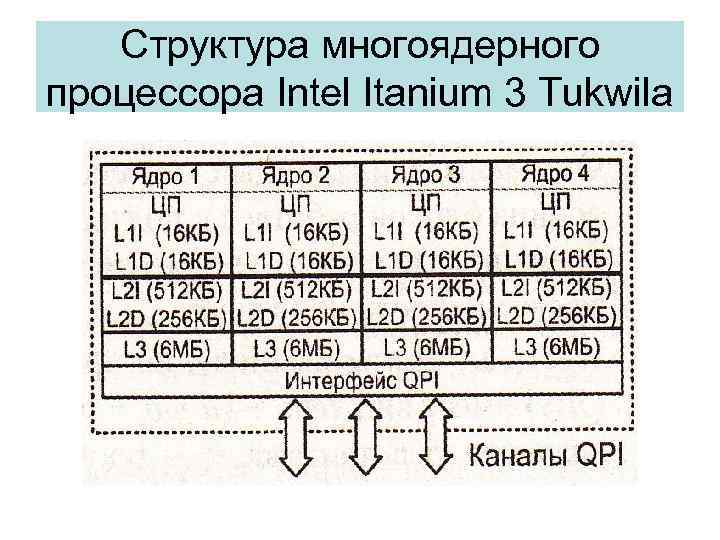

Структура многоядерного процессора Intel Itanium 3 Tukwila

Структура многоядерного процессора AMD Phenom X 4

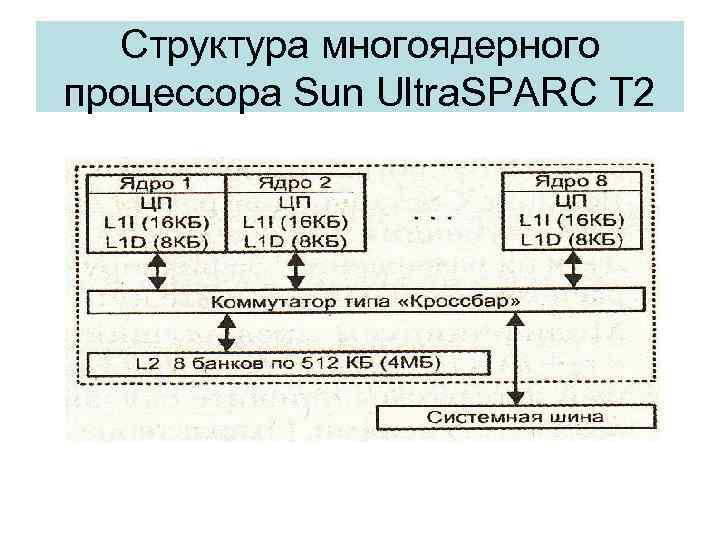

Структура многоядерного процессора Sun Ultra. SPARC T 2

Современные микропроцессоры.ppt