289976f13a1320c07c9f28d695dd9f97.ppt

- Количество слайдов: 55

Software Engineering Methodology for Reconfigurable Platforms Damien Picard and Loic Lagadec Architectures et Systèmes, Lab-STICC Université de Bretagne Occidentale, France ESUG’ 09 Brest, France, 2009

Introduction Increasing complexity of modern System-on-Chip ¨ Difficulty to program and to validate applications ¨ Shrinking time-to-market Common techniques for hardware validation ¨ Testing/debugging at a very low abstraction level Time-consuming and burdensome Need for productive methodologies with an higher level approach ¨ Software development benefits from very efficient techniques ¨ Our approach: applying software engineering methodologies to hardware design D. Picard, L. Lagadec ESUG’ 09 - Brest 2

Aim of this talk This talk focuses on a key issue: validation of hardware application targeting RA An HL synthesis flow for reconfigurable architectures based on MADEO [ESUG 08] ¨ Multi-level simulation: from behavioral to hardware ¨ Interfacing with third-party tools through code generation ¨ Software-like debugging features embedded in hardware Advocates for the use of software engineering techniques ¨ Short development cycles, use of OO models, code generation, etc. D. Picard, L. Lagadec ESUG’ 09 - Brest 3

Outline 1. Overview of Reconfigurable Architectures 2. OO methodology for synthesis on RA 3. Simulation and testing methodology 4. Software-like debugging for RA 5. Conclusion D. Picard, L. Lagadec ESUG’ 09 - Brest 4

Outline 1. Overview of Reconfigurable Architectures 2. OO methodology for synthesis on RA 3. Simulation and testing methodology 4. Software-like debugging for RA 5. Conclusion D. Picard, L. Lagadec ESUG’ 09 - Brest 5

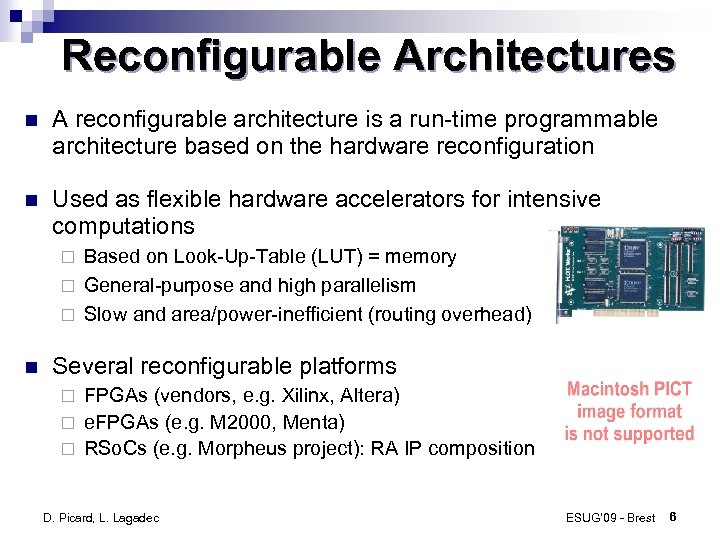

Reconfigurable Architectures A reconfigurable architecture is a run-time programmable architecture based on the hardware reconfiguration Used as flexible hardware accelerators for intensive computations Based on Look-Up-Table (LUT) = memory ¨ General-purpose and high parallelism ¨ Slow and area/power-inefficient (routing overhead) ¨ Several reconfigurable platforms FPGAs (vendors, e. g. Xilinx, Altera) ¨ e. FPGAs (e. g. M 2000, Menta) ¨ RSo. Cs (e. g. Morpheus project): RA IP composition ¨ D. Picard, L. Lagadec ESUG’ 09 - Brest 6

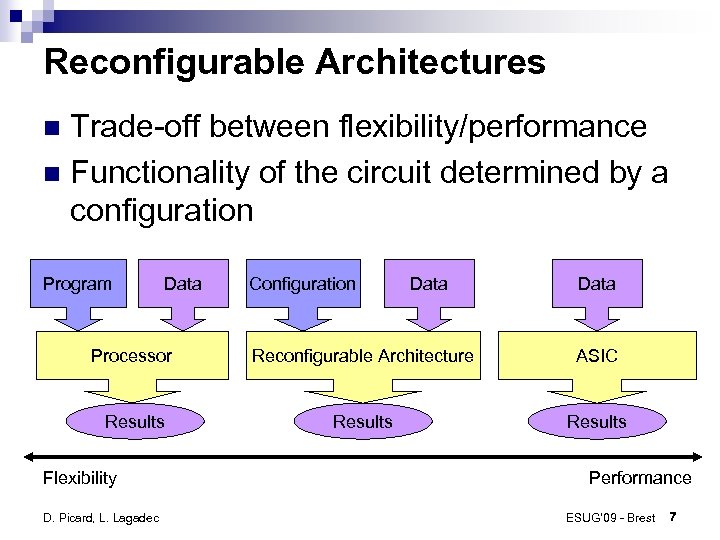

Reconfigurable Architectures Trade-off between flexibility/performance Functionality of the circuit determined by a configuration Program Data Configuration Data Processor Reconfigurable Architecture ASIC Results Flexibility D. Picard, L. Lagadec Performance ESUG’ 09 - Brest 7

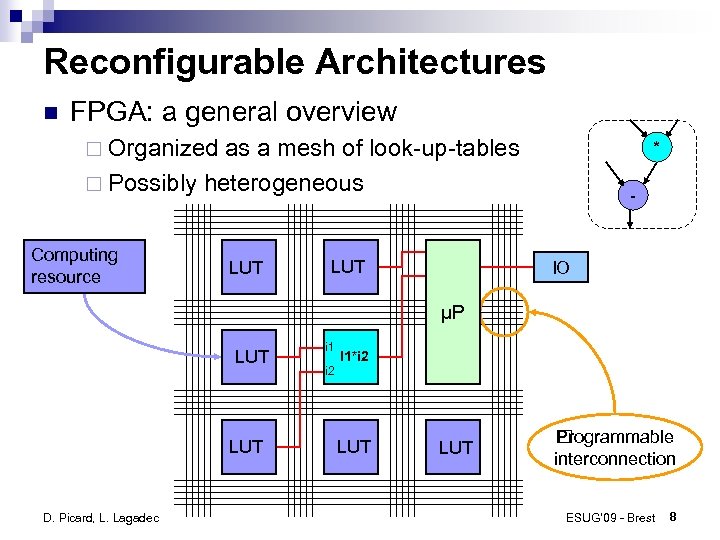

Reconfigurable Architectures FPGA: a general overview ¨ Organized as a mesh of look-up-tables ¨ Possibly heterogeneous Computing resource LUT i 1 I 1 -i 2 i 2 LUT + * - IO µP LUT D. Picard, L. Lagadec i 1 I 1*i 2 I 1+i 2 LUT LUT i 2 Programmable interconnection ESUG’ 09 - Brest 8

Outline 1. Overview of Reconfigurable Architectures 2. OO methodology for synthesis on RA 3. Simulation and testing methodology 4. Software-like debugging for RA 5. Conclusion D. Picard, L. Lagadec ESUG’ 09 - Brest 9

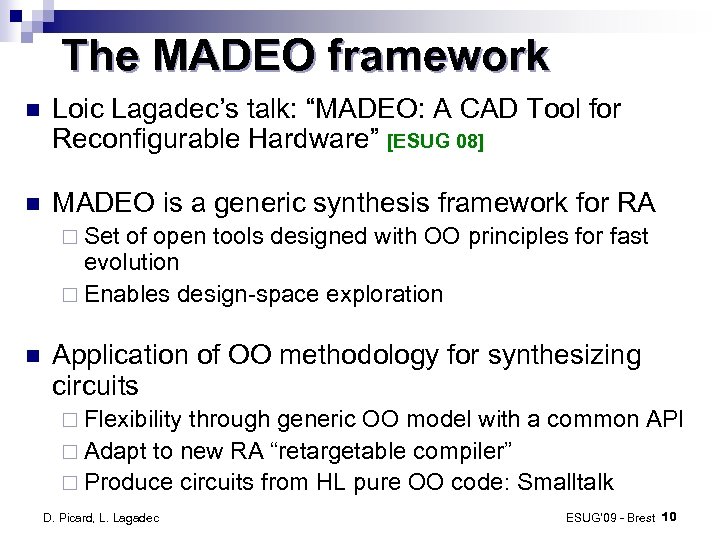

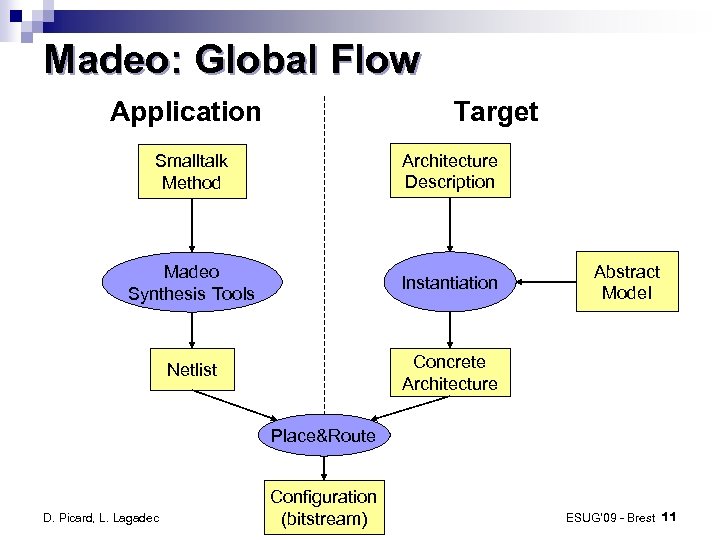

The MADEO framework Loic Lagadec’s talk: “MADEO: A CAD Tool for Reconfigurable Hardware” [ESUG 08] MADEO is a generic synthesis framework for RA ¨ Set of open tools designed with OO principles for fast evolution ¨ Enables design-space exploration Application of OO methodology for synthesizing circuits ¨ Flexibility through generic OO model with a common API ¨ Adapt to new RA “retargetable compiler” ¨ Produce circuits from HL pure OO code: Smalltalk D. Picard, L. Lagadec ESUG’ 09 - Brest 10

Madeo: Global Flow Application Target Smalltalk Method Architecture Description Madeo Synthesis Tools Instantiation Netlist Concrete Architecture Abstract Model Place&Route D. Picard, L. Lagadec Configuration (bitstream) ESUG’ 09 - Brest 11

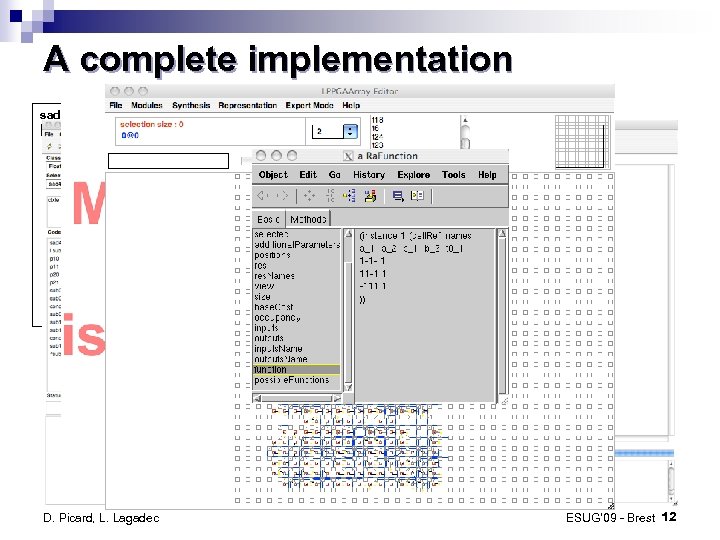

A complete implementation sad 4 p 1: p 1 p 2: p 2 | sub 0 a sub 1 a sub 0 b sub 1 b sub 0 sub 1 cond 0 cond 1 p 10 p 11 p 20 p 21 | p 10 : = p 11 : = p 1 bit. Shift: 8. p 20 : = p 21 : = p 2 bit. Shift: 8. sub 0 a : = p 10 -p 20. sub 0 b : = p 20 -p 10. cond 0 : = sub 0 a<0. sub 0 : = cond 0 if. True: [sub 0 b] if. False: [sub 0 a]. sub 1 a : = p 11 -p 21. sub 1 b : = p 21 -p 11. cond 1 : = sub 1 a<0. sub 1 : = cond 1 if. True: [sub 1 b] if. False: [sub 1 a]. ^sub 0+sub 1. D. Picard, L. Lagadec ESUG’ 09 - Brest 12

The MADEO framework Software-engineering concepts applied to logic synthesis on reconfigurable architectures MADEO: extensive use of OO methodology ¨ Modeling, generic tools through polymorphism An HL synthesis flow for RSo. C based on the MADEO approach with validation methodology ¨ Multi-level simulation: from behavioral to hardware ¨ Target modeling ¨ Interfacing with third-party tools through code generation ¨ Software-like debugging features embedded in hardware D. Picard, L. Lagadec ESUG’ 09 - Brest 13

Outline 1. Overview of Reconfigurable Architectures 2. OO methodology for synthesis on RA 3. Simulation and testing methodology 4. Software-like debugging for RA 5. Conclusion D. Picard, L. Lagadec ESUG’ 09 - Brest 14

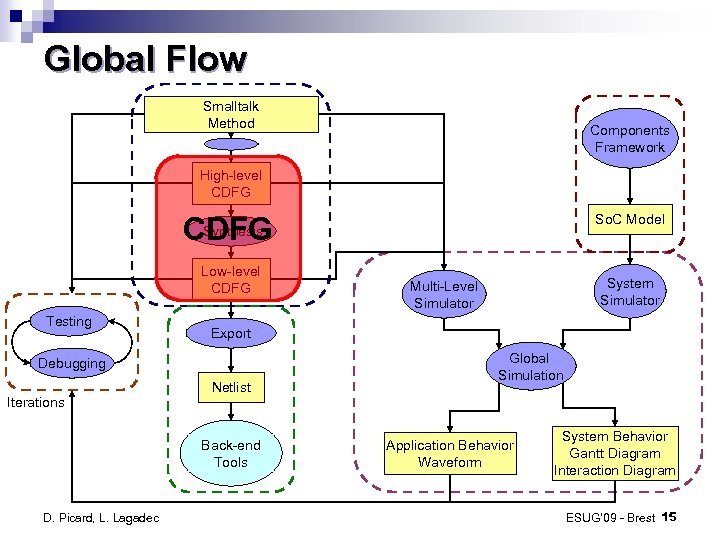

Global Flow Smalltalk Method Components Framework High-level CDFG Synthesis CDFG Low-level CDFG Testing Netlist Back-end Tools D. Picard, L. Lagadec System Simulator Multi-Level Simulator Export Debugging Iterations So. C Model Global Simulation Application Behavior Waveform System Behavior Gantt Diagram Interaction Diagram ESUG’ 09 - Brest 15

![APPLICATION [Lagadec, ESUG 08] CDFG Use Tool X Tool Y HLL CDFG API (Java) APPLICATION [Lagadec, ESUG 08] CDFG Use Tool X Tool Y HLL CDFG API (Java)](https://present5.com/presentation/289976f13a1320c07c9f28d695dd9f97/image-16.jpg)

APPLICATION [Lagadec, ESUG 08] CDFG Use Tool X Tool Y HLL CDFG API (Java) CDFG instances (STEP files) Target architecture description Madeo+ synthesis tool HLL CDFG API (Smalltalk) CDFG Checker Target 1 EDIF D. Picard, L. Lagadec Target 2 Target 3 C like code Specific Assembly code CDFG design Platypus tool CDFG EXPRESS model ENTITY Hierarchical. Node SUBTYPE OF (Node); local. Variables : LIST OF Abstract. Data; sub. Operators : LIST [1 : ? ] OF Node; END_ENTITY; ENTITY Accumulator. Node SUBTYPE OF (Hierarchical. Node); init : Abstract. Data; -”Accumulator. Node. init” the initial value we start accumulating from. to. Be. Accumulated: Abstract. Data; DERIVE cumulated. Arguments : LIST OF Abstract. Data : = sub. Operators [ SIZEOF (sub. Operators)]. outputs; WHERE to. Be. Accumulated. Source: SIZEOF ( cumulated. Arguments )=1; type. Compat: cumulated. Arguments[1]. type = init. type; END_ENTITY; 16 ESUG’ 09 - Brest 16

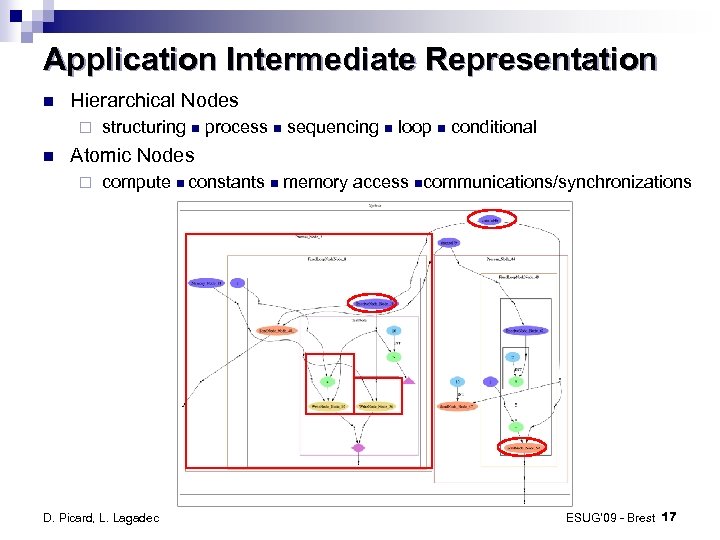

Application Intermediate Representation Hierarchical Nodes ¨ structuring process sequencing loop conditional Atomic Nodes ¨ compute constants memory access communications/synchronizations D. Picard, L. Lagadec ESUG’ 09 - Brest 17

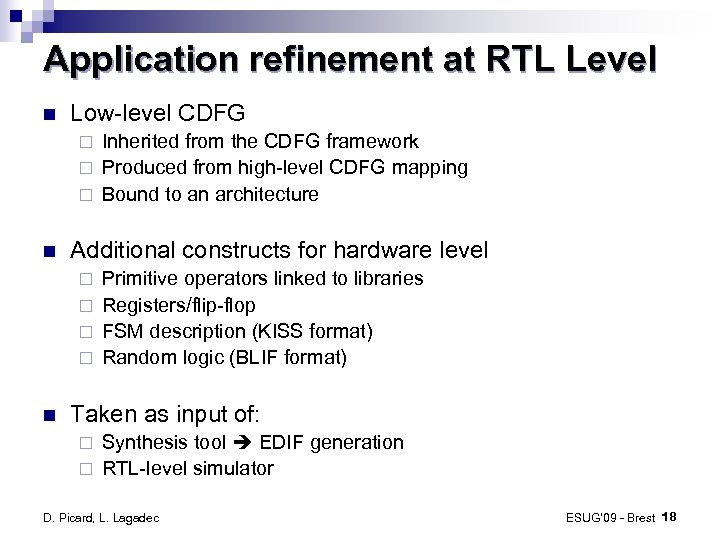

Application refinement at RTL Level Low-level CDFG Inherited from the CDFG framework ¨ Produced from high-level CDFG mapping ¨ Bound to an architecture ¨ Additional constructs for hardware level Primitive operators linked to libraries ¨ Registers/flip-flop ¨ FSM description (KISS format) ¨ Random logic (BLIF format) ¨ Taken as input of: Synthesis tool EDIF generation ¨ RTL-level simulator ¨ D. Picard, L. Lagadec ESUG’ 09 - Brest 18

Link between abstraction-levels How keeping the link between HL-CDFG variables and LL-CDFG signals? Software abstraction D. Picard, L. Lagadec ? Synthesis Implementation in hardware ESUG’ 09 - Brest 19

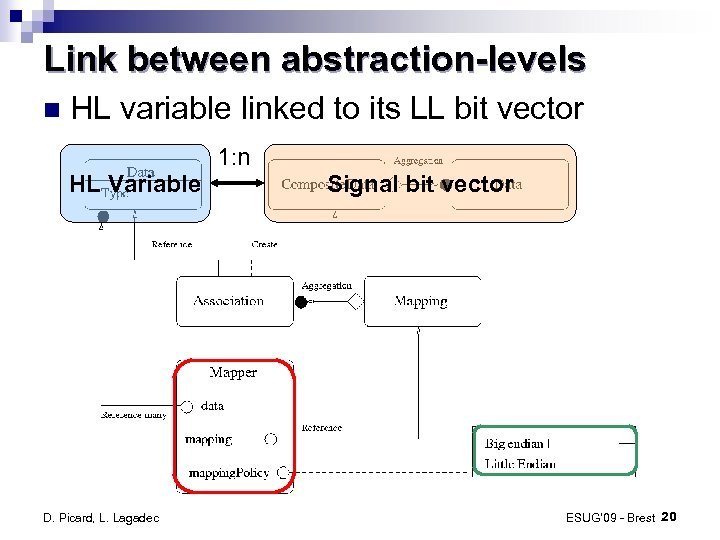

Link between abstraction-levels HL variable linked to its LL bit vector 1: n HL Variable D. Picard, L. Lagadec Signal bit vector ESUG’ 09 - Brest 20

Multi-Level Simulation Engines Behavioral specification of the application: Smalltalk Direct execution by ST virtual machine environment ¨ Use of system-level simulator API in code ¨ High-level CDFG produced from Smalltalk code Each node is simulated in function of sequencing nodes ¨ CDFG API for design pattern: Visitor, Composite ¨ Low-Level CDFG RTL-Level simulator takes as input a low-level CDFG ¨ Link between HL and LL CDFG ¨ ¨ For example loop indices Tracing signals Waveforms generation D. Picard, L. Lagadec ESUG’ 09 - Brest 21

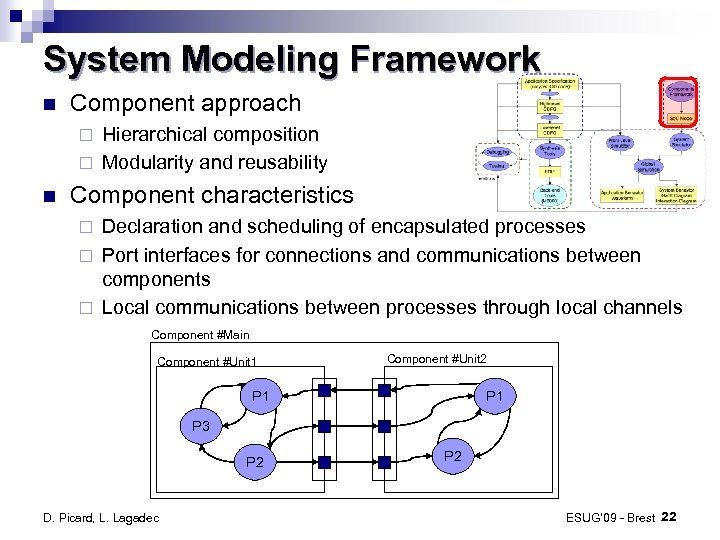

System Modeling Framework Component approach Hierarchical composition ¨ Modularity and reusability ¨ Component characteristics Declaration and scheduling of encapsulated processes ¨ Port interfaces for connections and communications between components ¨ Local communications between processes through local channels ¨ Component #Main Component #Unit 1 Component #Unit 2 P 1 P 3 P 2 D. Picard, L. Lagadec P 2 ESUG’ 09 - Brest 22

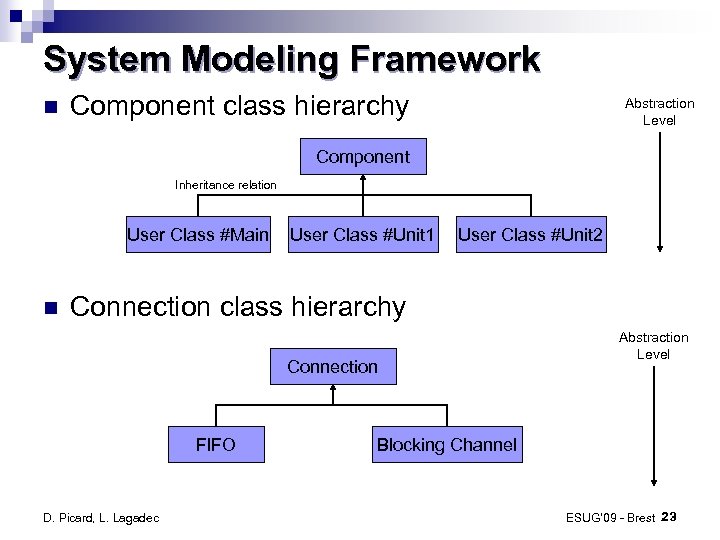

System Modeling Framework Component class hierarchy Abstraction Level Component Inheritance relation User Class #Main User Class #Unit 1 User Class #Unit 2 Connection class hierarchy Connection FIFO D. Picard, L. Lagadec Abstraction Level Blocking Channel ESUG’ 09 - Brest 23

![System-Level Simulation Framework of classes ¨ Based on an event-driven simulation kernel [Blue Book] System-Level Simulation Framework of classes ¨ Based on an event-driven simulation kernel [Blue Book]](https://present5.com/presentation/289976f13a1320c07c9f28d695dd9f97/image-24.jpg)

System-Level Simulation Framework of classes ¨ Based on an event-driven simulation kernel [Blue Book] ¨ Defines an API for simulating operator latencies, scheduling, stopping activities ¨ System modeling framework inherits from the simulator Simulator + modeling class hierarchy Simulation. Object Component Simulation Connection User Model D. Picard, L. Lagadec ESUG’ 09 - Brest 24

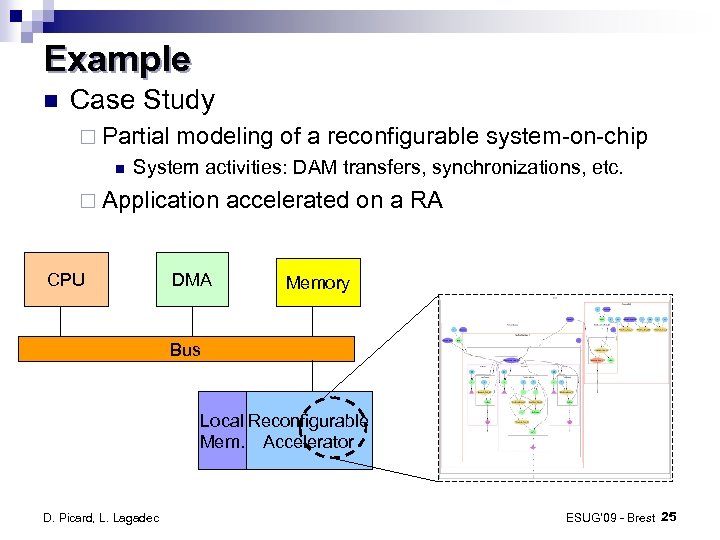

Example Case Study ¨ Partial modeling of a reconfigurable system-on-chip System activities: DAM transfers, synchronizations, etc. ¨ Application CPU DMA accelerated on a RA Memory Bus Local Reconfigurable Mem. Accelerator D. Picard, L. Lagadec ESUG’ 09 - Brest 25

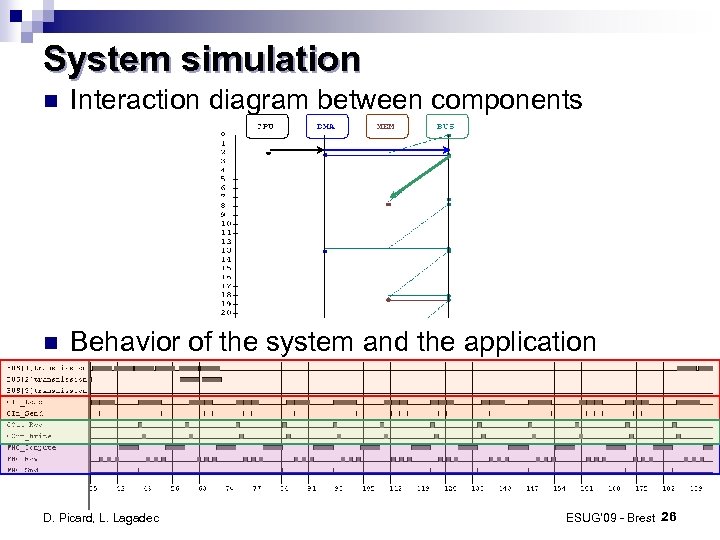

System simulation Interaction diagram between components Behavior of the system and the application D. Picard, L. Lagadec ESUG’ 09 - Brest 26

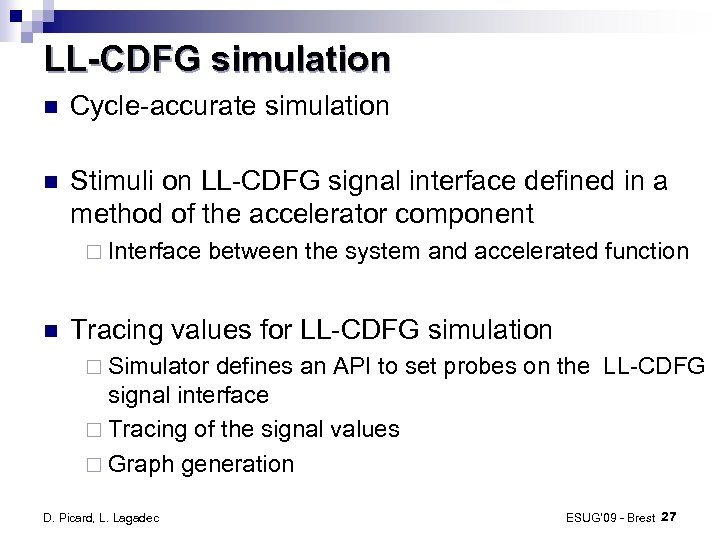

LL-CDFG simulation Cycle-accurate simulation Stimuli on LL-CDFG signal interface defined in a method of the accelerator component ¨ Interface between the system and accelerated function Tracing values for LL-CDFG simulation ¨ Simulator defines an API to set probes on the LL-CDFG signal interface ¨ Tracing of the signal values ¨ Graph generation D. Picard, L. Lagadec ESUG’ 09 - Brest 27

Tracing signals Traced signals and stimuli set through a GUI D. Picard, L. Lagadec ESUG’ 09 - Brest 28

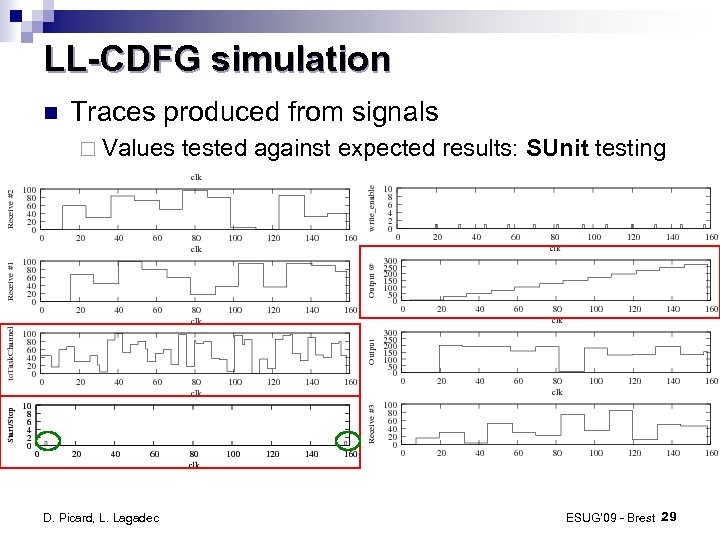

LL-CDFG simulation Traces produced from signals ¨ Values D. Picard, L. Lagadec tested against expected results: SUnit testing ESUG’ 09 - Brest 29

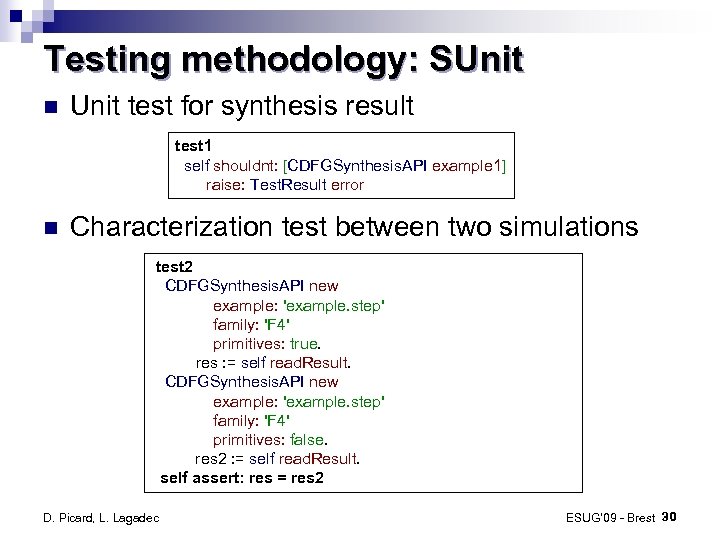

Testing methodology: SUnit test for synthesis result test 1 self shouldnt: [CDFGSynthesis. API example 1] raise: Test. Result error Characterization test between two simulations test 2 CDFGSynthesis. API new example: 'example. step' family: 'F 4' primitives: true. res : = self read. Result. CDFGSynthesis. API new example: 'example. step' family: 'F 4' primitives: false. res 2 : = self read. Result. self assert: res = res 2 D. Picard, L. Lagadec ESUG’ 09 - Brest 30

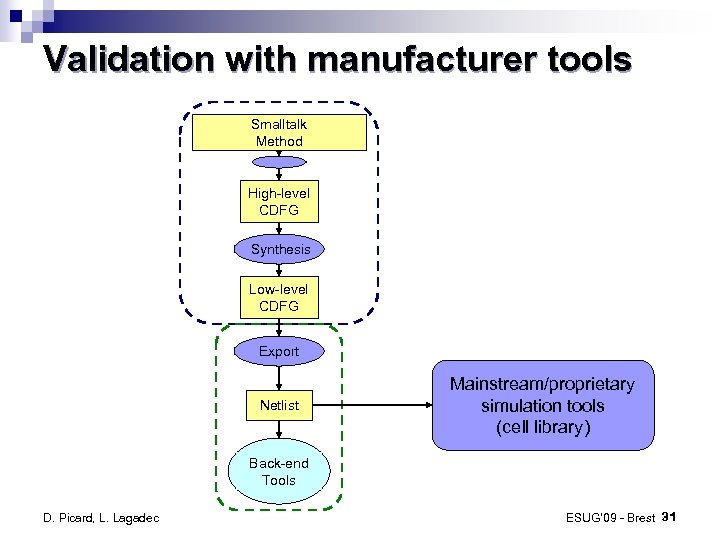

Validation with manufacturer tools Smalltalk Method High-level CDFG Synthesis Low-level CDFG Export Netlist Mainstream/proprietary simulation tools (cell library) Back-end Tools D. Picard, L. Lagadec ESUG’ 09 - Brest 31

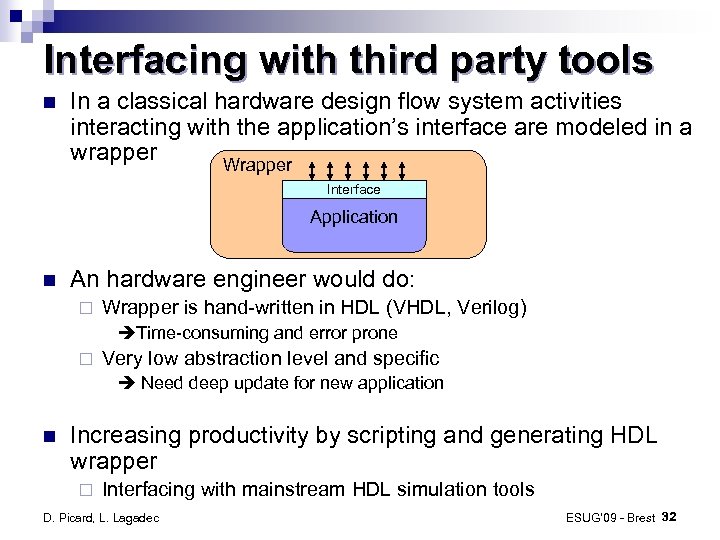

Interfacing with third party tools In a classical hardware design flow system activities interacting with the application’s interface are modeled in a wrapper Wrapper Interface Application An hardware engineer would do: ¨ Wrapper is hand-written in HDL (VHDL, Verilog) Time-consuming and error prone ¨ Very low abstraction level and specific Need deep update for new application Increasing productivity by scripting and generating HDL wrapper ¨ Interfacing with mainstream HDL simulation tools D. Picard, L. Lagadec ESUG’ 09 - Brest 32

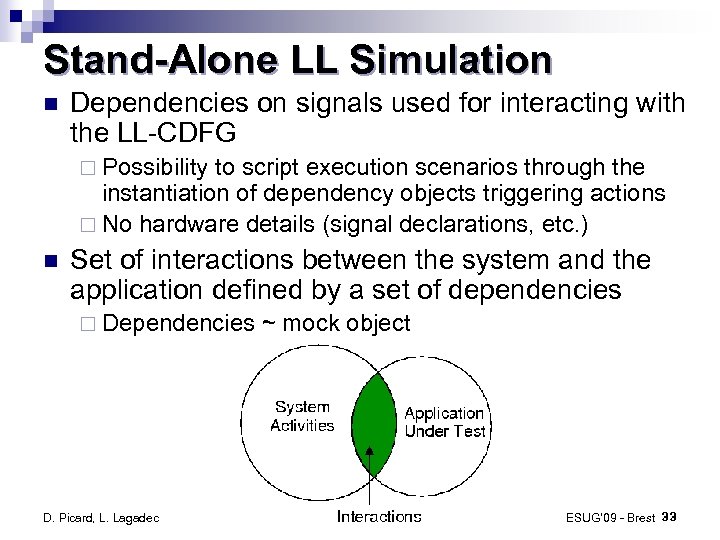

Stand-Alone LL Simulation Dependencies on signals used for interacting with the LL-CDFG ¨ Possibility to script execution scenarios through the instantiation of dependency objects triggering actions ¨ No hardware details (signal declarations, etc. ) Set of interactions between the system and the application defined by a set of dependencies ¨ Dependencies D. Picard, L. Lagadec ~ mock object ESUG’ 09 - Brest 33

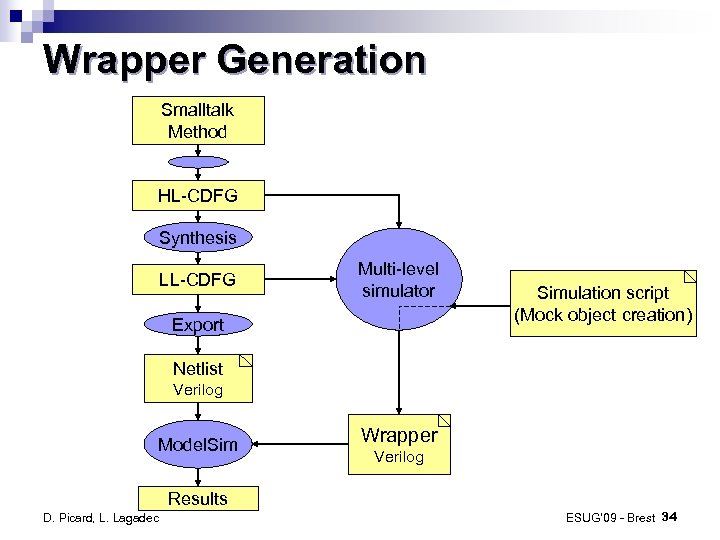

Wrapper Generation Smalltalk Method HL-CDFG Synthesis LL-CDFG Multi-level simulator Export Simulation script (Mock object creation) Netlist Verilog Model. Sim Results D. Picard, L. Lagadec Wrapper Verilog ESUG’ 09 - Brest 34

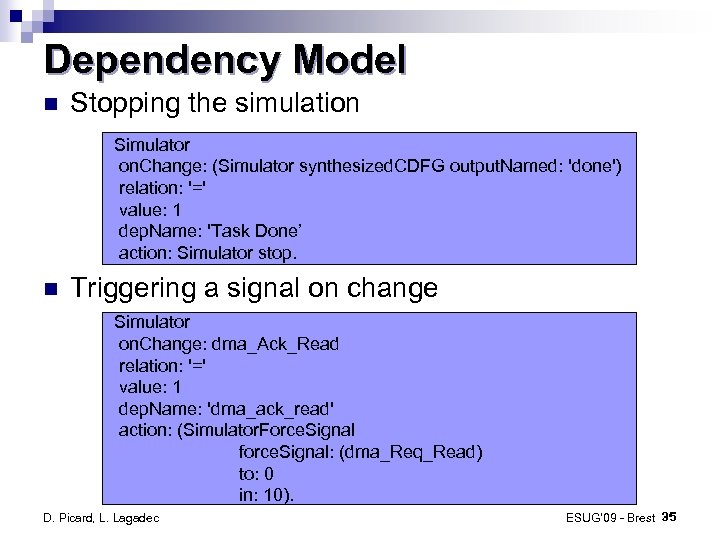

Dependency Model Stopping the simulation Simulator on. Change: (Simulator synthesized. CDFG output. Named: 'done') relation: '=' value: 1 dep. Name: 'Task Done’ action: Simulator stop. Triggering a signal on change Simulator on. Change: dma_Ack_Read relation: '=' value: 1 dep. Name: 'dma_ack_read' action: (Simulator. Force. Signal force. Signal: (dma_Req_Read) to: 0 in: 10). D. Picard, L. Lagadec ESUG’ 09 - Brest 35

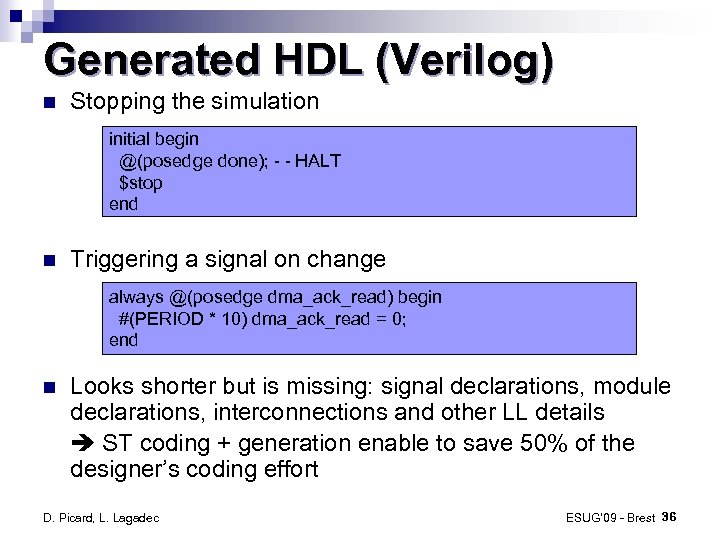

Generated HDL (Verilog) Stopping the simulation initial begin @(posedge done); - - HALT $stop end Triggering a signal on change always @(posedge dma_ack_read) begin #(PERIOD * 10) dma_ack_read = 0; end Looks shorter but is missing: signal declarations, module declarations, interconnections and other LL details ST coding + generation enable to save 50% of the designer’s coding effort D. Picard, L. Lagadec ESUG’ 09 - Brest 36

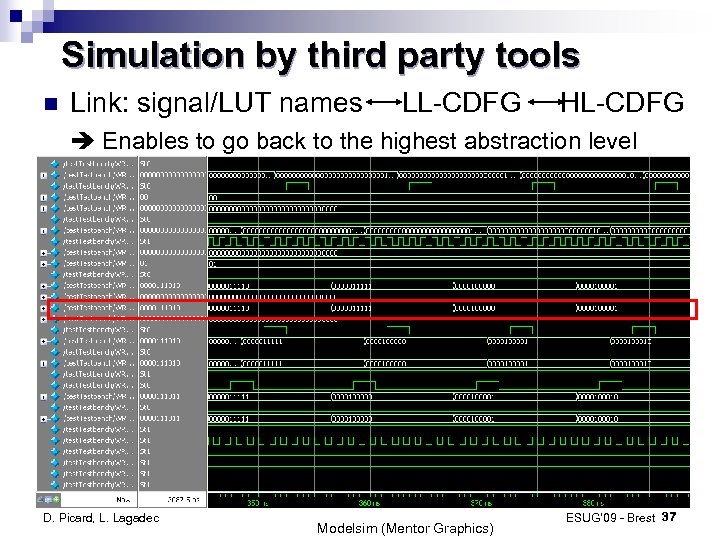

Simulation by third party tools Link: signal/LUT names LL-CDFG HL-CDFG Enables to go back to the highest abstraction level D. Picard, L. Lagadec Modelsim (Mentor Graphics) ESUG’ 09 - Brest 37

Outline 1. Overview of Reconfigurable Architectures 2. OO methodology for synthesis on RA 3. Simulation and testing methodology 4. Software-like debugging for RA 5. Conclusion D. Picard, L. Lagadec ESUG’ 09 - Brest 38

After Testing Failed Multi-level simulation enables to test the application at any flow stage Use software engineering techniques ¨ Testing at all level with SUnit ¨ Modeling approach with generic models Platform , application, interactions ¨ Interfacing with third-party tools Automated code generation If validation failed… ¨ …Time D. Picard, L. Lagadec Testing Debugging for debugging ESUG’ 09 - Brest 39

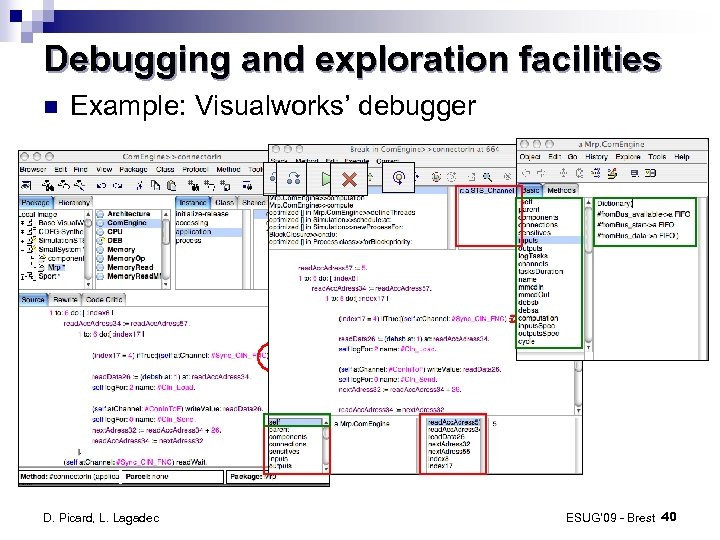

Debugging and exploration facilities Example: Visualworks’ debugger D. Picard, L. Lagadec ESUG’ 09 - Brest 40

Methods and Tools for Software Debugging facilities in Smalltalk environment ¨ Conditional breakpoint and watchpoint inserted/modified dynamically ¨ Hot-code replacement ¨ Deep exploration of the execution context ¨ Message stack control Short iterative cycles: edit-compile-run-debug ¨ Fast development These software features do not exist in hardware ¨ No symbolic debugging, no execution stack, etc. D. Picard, L. Lagadec ESUG’ 09 - Brest 41

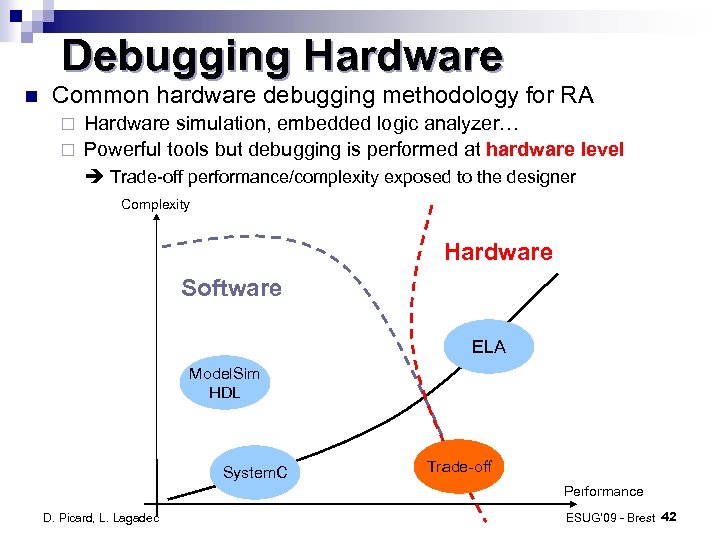

Debugging Hardware Common hardware debugging methodology for RA Hardware simulation, embedded logic analyzer… ¨ Powerful tools but debugging is performed at hardware level Trade-off performance/complexity exposed to the designer ¨ Complexity Hardware Software ELA Model. Sim HDL System. C Trade-off Performance D. Picard, L. Lagadec ESUG’ 09 - Brest 42

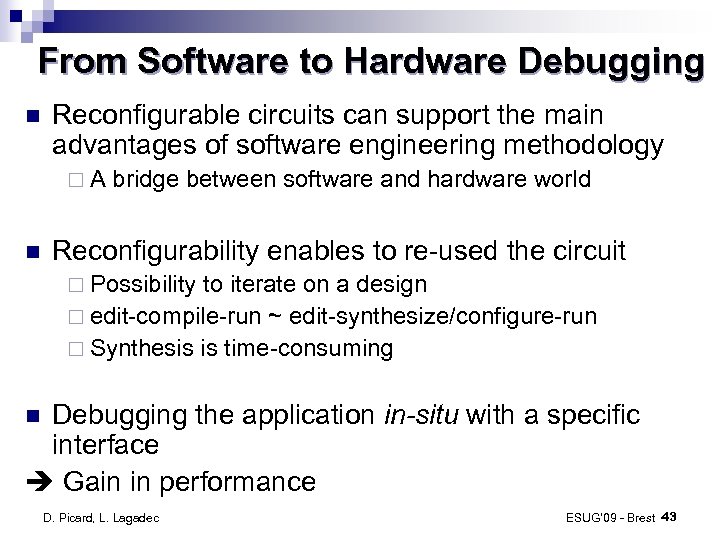

From Software to Hardware Debugging Reconfigurable circuits can support the main advantages of software engineering methodology ¨A bridge between software and hardware world Reconfigurability enables to re-used the circuit ¨ Possibility to iterate on a design ¨ edit-compile-run ~ edit-synthesize/configure-run ¨ Synthesis is time-consuming Debugging the application in-situ with a specific interface Gain in performance D. Picard, L. Lagadec ESUG’ 09 - Brest 43

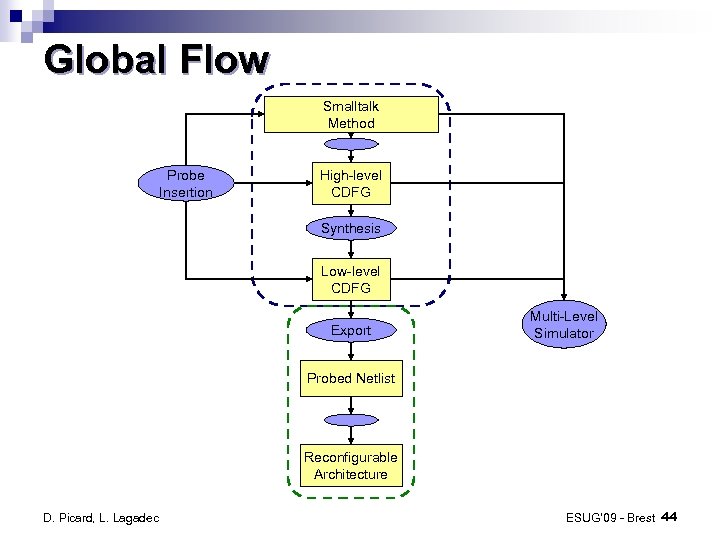

Global Flow Smalltalk Method Probe Insertion High-level CDFG Synthesis Low-level CDFG Export Multi-Level Simulator Probed Netlist Reconfigurable Architecture D. Picard, L. Lagadec ESUG’ 09 - Brest 44

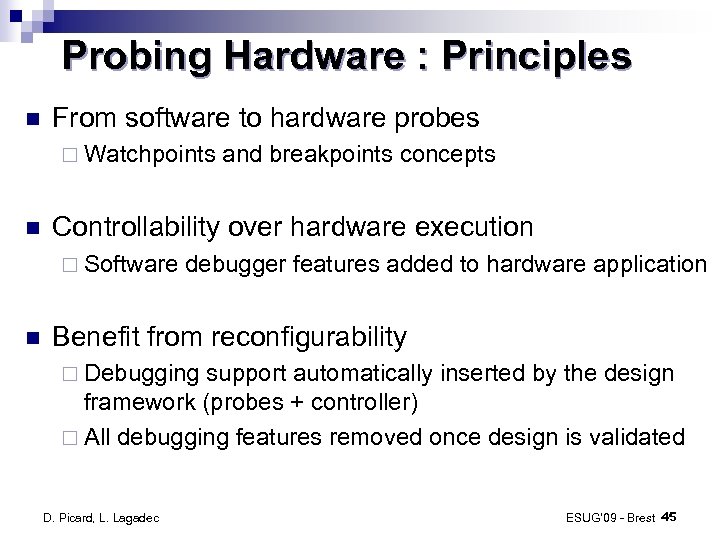

Probing Hardware : Principles From software to hardware probes ¨ Watchpoints Controllability over hardware execution ¨ Software and breakpoints concepts debugger features added to hardware application Benefit from reconfigurability ¨ Debugging support automatically inserted by the design framework (probes + controller) ¨ All debugging features removed once design is validated D. Picard, L. Lagadec ESUG’ 09 - Brest 45

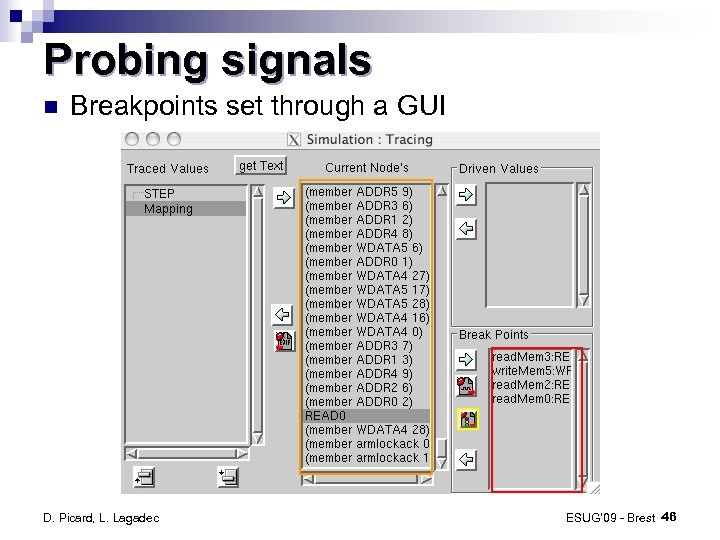

Probing signals Breakpoints set through a GUI D. Picard, L. Lagadec ESUG’ 09 - Brest 46

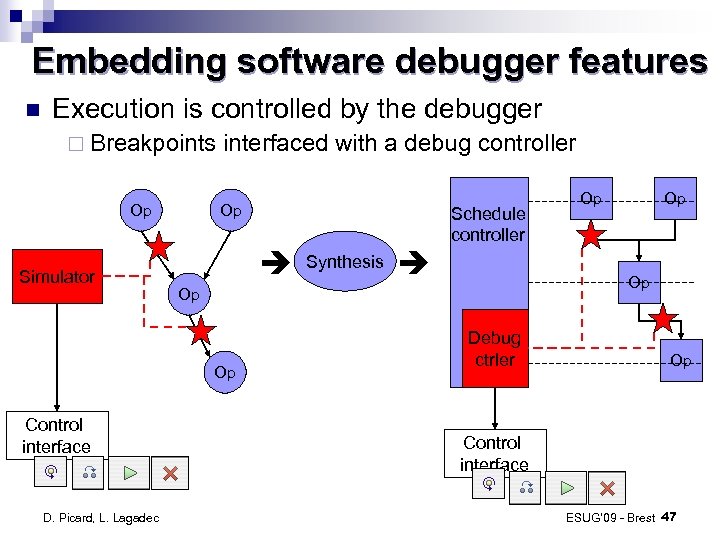

Embedding software debugger features Execution is controlled by the debugger ¨ Breakpoints Op Simulator interfaced with a debug controller Op D. Picard, L. Lagadec Synthesis Op Op Control interface Schedule controller Op Debug ctrler Op Control interface ESUG’ 09 - Brest 47

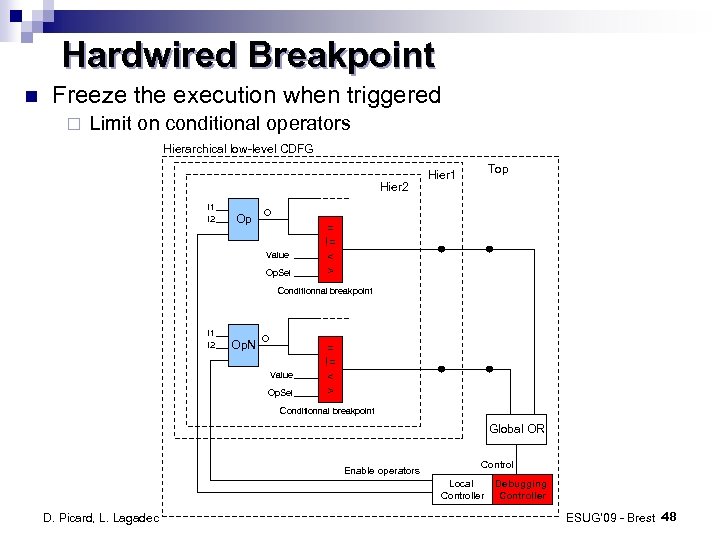

Hardwired Breakpoint Freeze the execution when triggered ¨ Limit on conditional operators Hierarchical low-level CDFG Hier 2 i 1 i 2 Op Top Hier 1 O Value Op. Sel = != < > Conditionnal breakpoint i 1 i 2 Op. N O Value Op. Sel = != < > Conditionnal breakpoint Global OR Enable operators Control Local Controller D. Picard, L. Lagadec Debugging Controller ESUG’ 09 - Brest 48

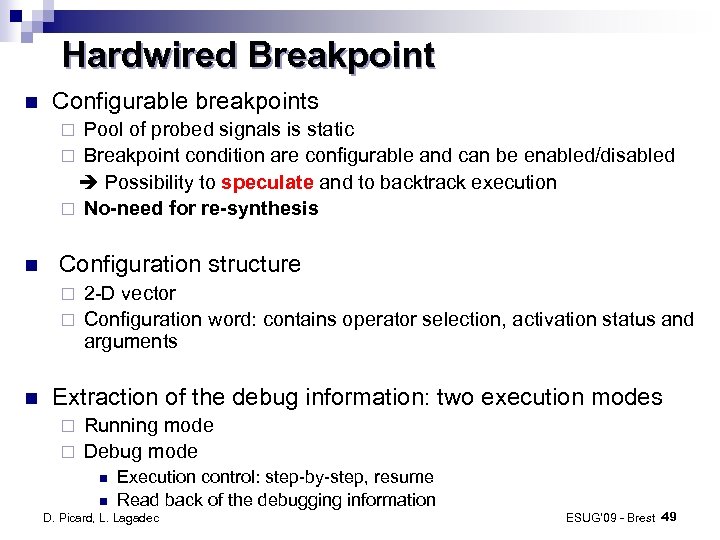

Hardwired Breakpoint Configurable breakpoints Pool of probed signals is static ¨ Breakpoint condition are configurable and can be enabled/disabled Possibility to speculate and to backtrack execution ¨ No-need for re-synthesis ¨ Configuration structure 2 -D vector ¨ Configuration word: contains operator selection, activation status and arguments ¨ Extraction of the debug information: two execution modes Running mode ¨ Debug mode ¨ Execution control: step-by-step, resume Read back of the debugging information D. Picard, L. Lagadec ESUG’ 09 - Brest 49

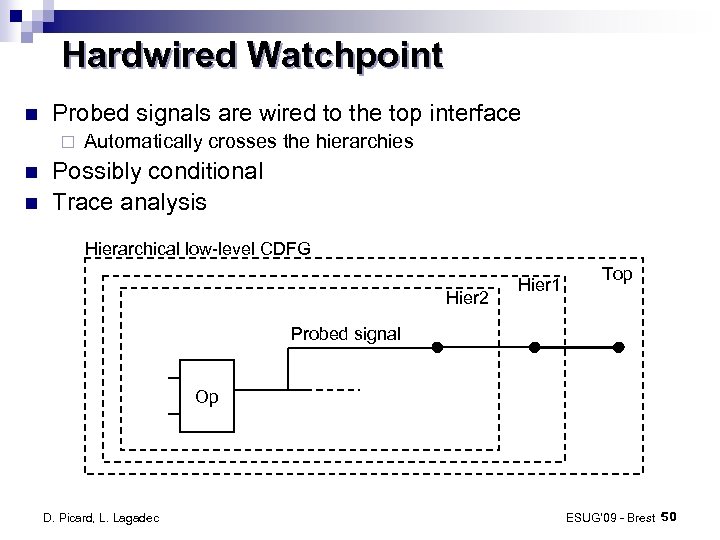

Hardwired Watchpoint Probed signals are wired to the top interface ¨ Automatically crosses the hierarchies Possibly conditional Trace analysis Hierarchical low-level CDFG Hier 2 Hier 1 Top Probed signal Op D. Picard, L. Lagadec ESUG’ 09 - Brest 50

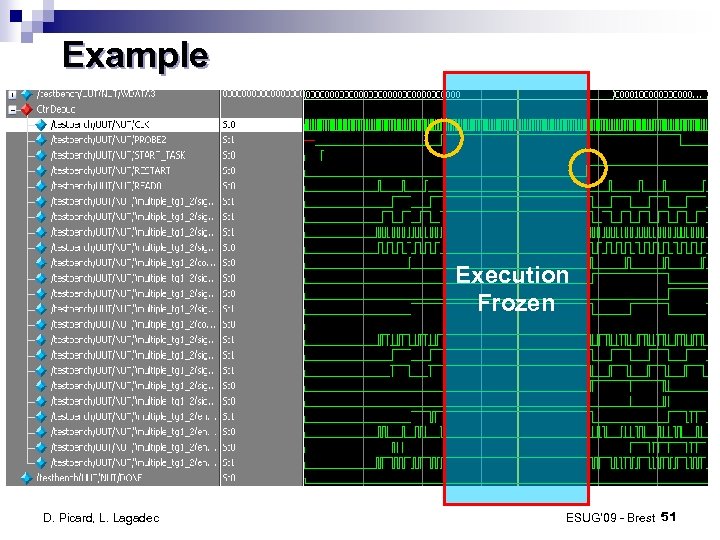

Example Execution Frozen D. Picard, L. Lagadec ESUG’ 09 - Brest 51

Outline 1. Overview of Reconfigurable Architectures 2. OO methodology for synthesis on RA 3. Simulation and testing methodology 4. Software-like debugging for RA 5. Conclusion D. Picard, L. Lagadec ESUG’ 09 - Brest 52

Conclusion Methodology for validating an application running on a RSo. C Multi-level simulation of the application specified as CDFG ¨ High-level modeling of platform by a component-based approach ¨ Benefit from software expertise for hardware design Taking advantage of the Smalltalk dynamic language and environment ¨ Debugging techniques from software to hardware ¨ Short cycle and iterative developments ¨ Software engineering techniques increase productivity D. Picard, L. Lagadec ESUG’ 09 - Brest 53

Future work Dynamic insertion of HW breakpoints into the application ¨ Synthesizing SUnit embedded in hardware ¨ Synthesizing probes on demand / partial reconfiguration assertions in the netlist Interfacing the synthesized application with highlevel software tools ¨ Inspector utility on the circuit ¨ Collecting state values of the HW application at high-level D. Picard, L. Lagadec ESUG’ 09 - Brest 54

Thank you ! D. Picard, L. Lagadec ESUG’ 09 - Brest 55

289976f13a1320c07c9f28d695dd9f97.ppt