83266db3f850f0b6e65a3c953cc362d7.ppt

- Количество слайдов: 38

So. C 설계 기초 성균관대 조준동 교수

목차 가. So. C Design Flow 나. HW/SW Co-design 다. platform-based design 라. Network-on-chip 마. 저전력 설계

가. So. C Design Flow 성균관대 조준동 교수

목차 z. So. C 설계 동향 z 3 G를 위한 설계 방법 z설계 플로루 z 지적재산을 이용한 설계 방법 z 다양한 설계 방법 형태

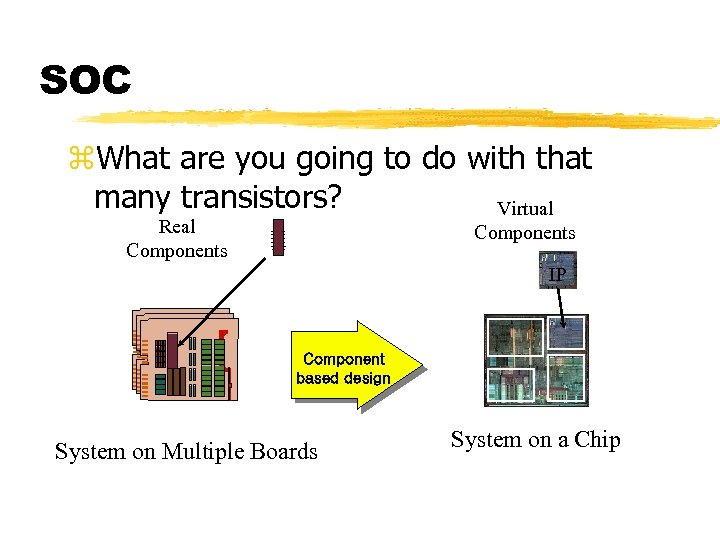

SOC z. What are you going to do with that many transistors? Virtual Real Components IP Component based design System on Multiple Boards System on a Chip

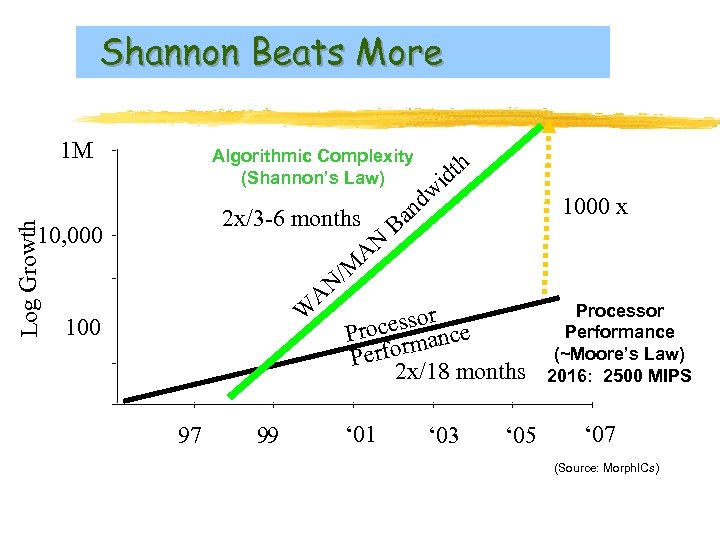

Shannon Beats More Log Growth 1 M Algorithmic Complexity (Shannon’s Law) 2 x/3 -6 months 10, 000 AN h dt wi d an B 1000 x /M AN W cessor nce Pro ma Perfor 2 x/18 months 100 97 99 ‘ 01 ‘ 03 ‘ 05 Processor Performance (~Moore’s Law) 2016: 2500 MIPS ‘ 07 (Source: Morph. ICs)

Technology Roadmap 시장전망 (단말기) 3. 5 G 2 GHz 밴드폭 100 Mbps 10 MB/200 sec 다운로드 Image Bit Rate 385 kbps Contents 100 MB/10 sec 24 Mbps. X 2 175 W 15 Mbytes 800 Mhz 2001 - 2003 2005 개인화: 고속화: 저전력화: 재사용화: 200, 000 150, 000 0 2001 2002 2003 2007 2004 2005 2006 Year 5 -10 GHz 200 M gates 집적도 250, 000 2000 700 kbytes CPU 300, 000 100, 000 30 -50 W 에너지 소모량 1999 3 -6 Ghz 14. 4 Mbps 속도 350, 000 4 G Revenue(million $) 3 G 1 B gates 2010 Context-aware Sensor Networks No. C 기술 ACM, PSM, DVS, GC, LCC Hardware/Software Co-design *출처 ETRI, 2000

Radio systems z Wi. Fi – 10 -100 Mbits/sec unlicensed band y. OFDM, M-ary coding z 3 G –. 1 -2 Mbits/sec wide area cellular y. CDMA, GMSK z Bluetooth –. 8 Mbit/sec cable replacement y. Frequency hop z Zig. Bee –. 02 -. 2 Kbits/sec low power, low cost y. QPSK z UWB – Recently allowed by FCC y. Short pulses (no carrier), bi-phase or PPM

Power Dissipation 10 W 3 G 1 W 100 m. W 802. 11 bg Bluetooth 10 m. W Zig. Bee UWB Zig. Bee 802. 11 a UWB 1 m. W 0 GHz 1 GHz 2 GHz 3 GHz 4 GHz 5 GHz 6 GHz

Cost (projections) $1000 $100 3 G 802. 11 b, g $10 $1 Zig. Bee UWB Bluetooth Zig. Bee 802. 11 a UWB $. 10 0 GHz 1 GHz 2 GHz 3 GHz 4 GHz 5 GHz 6 GHz

Data rate 100 Mbit/sec 100 kbits/sec UWB 802. 11 g 802. 11 b 3 G 802. 11 a Bluetooth Zig. Bee 10 kbits/sec UWB 0 GHz 1 GHz 2 GHz 3 GHz 4 GHz 5 GHz 6 GHz

Integration on SOC on CMOS Process

‘Top Ten Obstacles to 3 G Wireless Technology’ from: Carl Panasik “Overcoming Obstacles to 3 G Wireless Technology”, Communications System Design, January, 2001, pp. 11 -12. . Reused with permission. Carl Panasik is in the Wireless Unit of TI. z. Stable Standards z. Increased DSP Performance z. Software Sophistication z. Lower Power Consumption z. Advanced Power Management z. Increased Battery Capacity z 3 G OSes z. Enhanced Radio Technology z. Cost Concerns z. Innovative Applications

Multimedia Cell phone Challenges z 3 G WCDMA communications channel y. Complexity 5 x to 6 x greater than GSM y. Higher throughput with lower power y. Wider bandwidth with increased linearity y. Multi-standard capability z. Combined challenges of wireless video y. Managing BER impacts on video quality y. FEC -- forward error correction y. Managing bandwidth and video quality y. Higher power efficiency y. Higher integration -- digital logic, memory, mixed-signal, & RF y. Lower cost

· SOC Design Trends § Expected to integrate more and more complex • Web-browsing, real-time video processing, speech recognition and synthesis § Average operating power at or below 100 m. W and standby power levels at or below 2 m. W § Performance levels must increase from 300 million operations per second (MOPS) today to 2500 MOPS in 2016

Four main applications z. Set-top box: Mobile multimedia system, base station for the home local-area network. z. Digital PCTV: concurrent use of TV, 3 D graphics, and Internet services z. Set-top box LAN service: Wireless homenetworks, multi-user wireless LAN z. Navigation system: steer and control traffic and/or goods-transportation

Achieving functionality while maximizing battery life and minimizing size Cochlear implant GPS Cellular phone Noise cancellation headphones Medical watch Digital still camera Hearing aid Portable audio Digital radio

Implementation Choices for a 3 G Device Cadence What functions How do I reuse What information is do I my own IP? required to integrate IP? integrate? What is my IP supplier chain process? What IP do I build, what IP do I buy? What do I reuse? Image processing RISC/DSP/ASIC Sensor A/D How can I use IP standards? Amp I/O Channels Does the IP integrate throughout the flow? USB Node Blue Tooth Pixel Defect Masking Demosaic, Gamma 1394/Fire. Wire RGB-YUV, JPEG I/O & Network Stack SRAM/DRAM/Flash MEMORY Mic If I change architecture, what happens to performance? RISC/DSP/ASIC G. 723. 1/ADPCM A/D Audio Compression MEMORY V. 90 Modem ETHERNET I/O Will this platform meet cost targets? PCI Video/Ch 3 RF 3 G WCDMA Photo MEMORY BATTERY RF WIRELESS Flash Multilevel Flash CHARGER/PWR MGMT Ir. DA Disk, DVD UNTETHERED CAMERA View Finder LCD Display

So. C Design Flow

Structured So. C Designs z. Hierarchy: Subdivide the design into many levels of sub-modules z. Regularity: Subdivide to max number of similar sub-modules at each level z. Modularity: Define sub-modules unambiguously & well defined interfaces z. Locality: Max local connections, keeping critical paths within module boundaries

![The So. C platform application software hardware platform for (I=0; I<N; I++) a[I] = The So. C platform application software hardware platform for (I=0; I<N; I++) a[I] =](https://present5.com/presentation/83266db3f850f0b6e65a3c953cc362d7/image-21.jpg)

The So. C platform application software hardware platform for (I=0; I<N; I++) a[I] = b[I]*c[I]; . . .

System-on on-Chip components

Common Fabric for IP Blocks z Soft IP blocks are portable, but not as predictable as hard IP. z Hard IP blocks are very predictable since a specific physical implementation can be characterized, but are hard to port since are often tied to a specific process. z Common fabric is required for both portability and predictability. z Wide availability: Cell Based Array, metal programmable architecture that provides the performance of a standard cell and is optimized for synthesis.

Why SOC? • SOC specs are coming from ICT system engineers than RTL descriptions rather • SOC will bridge the gap b/w s/w and their implementation in novel, energy-efficient silicon architecture. • In SOC design, chips are assembled at IP block level (design reusable) and IP interfaces rather than gate level

Types of System-on-a-Chip Designs

Energy-Flexibility Gap 에너지 효율 (MOPS/m. W) 1000 100 신호처리 ASIC 200 MOPS/m. W 재구성 구조 10 1 신호처리 프로세서 ASIPs, DSPs 10 -80 MOPS/m. W 3 MOPS/m. W 임베디드 프로세서(ARM) 0. 5 MOPS/m. W 0. 1 가용성 6

Physical gap z Timing closure problem: layout-driven logic and RT-level synthesis z Energy efficiency requires locality of computation and storage: match for stream-based data processing of speech, images, and multimedia-system packets. z Next generation SOC designers must bridge the architectural gap b/w system specification and energyefficient IP-based architectures, while CAE vendors and IP providers will bridge the physical gap.

Circular Y-Chart

Implementing Digital Systems

The 100 Million Transistor Question HOW BEST CAN WE USE THEM TO SOLVE OUR COMPUTING PROBLEMS ?

Answer I: Multiprocessor on a chip Requirement: Efficient, parallelizing compiler Problems: Enough parallelism in programs? Does not go fast enough for video applications, for instance.

Answer II: Giant FPGA Requirement: CAD system for FPGAs Problems: May work well for bit- level video computations, but in general FPGAs are inefficient.

Answer III: H/W and S/W Codesign

ASIP Design z Given a set of applications, determine micro architecture of ASIP (i. e. , configuration of functional units in datapaths, instruction set) z To accurately evaluate performance of processor on a given application need to compile the application program onto the processor datapath and simulate object code. z The micro architecture of the processor is a design parameter!

ASIP Design Flow

Alternatives for Semiconductor z. Quantum Computing z. DNA Computing z. Optical Computing z. Molecular Computing

83266db3f850f0b6e65a3c953cc362d7.ppt