72613a934d400099894f98e49cc18b04.ppt

- Количество слайдов: 19

Smart Dust: Unique Low Power Flexible Sensor Network Neil Goldsman, Haralabos (Babis) Papadopoulos and Shuvra Bhattacharyya Dept. of Electrical and Computer Engineering University of Maryland College Park

Lead Personnel All UMD ECE Faculty • Prof. Neil Goldsman –Director of ECE Mixed Signal VLSI Lab –Director of ECE Semiconductor Simulation Lab –Introduced RF VLSI Circuit Design to UMD –Other Areas: 3 D Integration • Prof. Haralabos (Babis) Papadopoulos –Institute for Systems Research –Communications and Signal Processing Laboratory –Center for Satellite Communications –Other Areas: Power Efficient Private Comm. Networks • Prof. Shuvra Bhattacharyya –Institute for Advanced Computer Studies –Digital VLSI Design Automation Laboratory –Embedded Systems Research Laboratory, –Communications and Signal Processing Laboratory –Other Areas: Embedded Software; Low Power Design

Outline • • Smart Dust Overview Electronics (Neil) – • Communications (Babis) – • RF VLSI, Hardware, Sensors and 3 D Integration Algorithms and Signal Processing Microcontrol (Shuvra) – Digital Hardware and Software for Data Flow and Processing

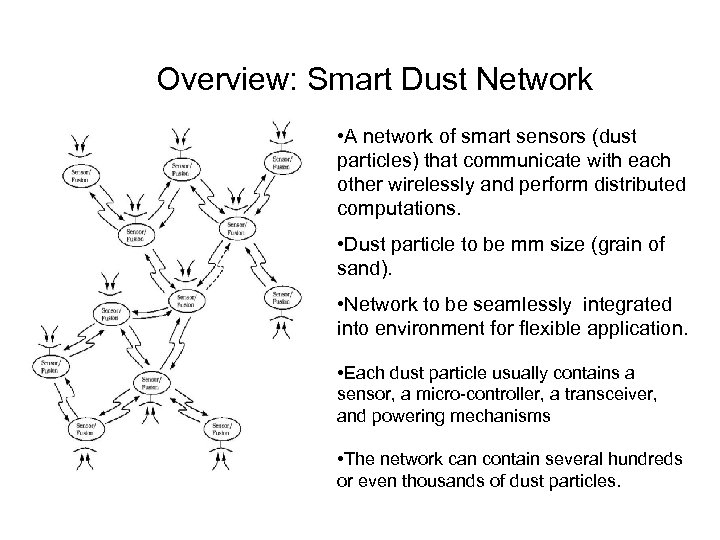

Overview: Smart Dust Network • A network of smart sensors (dust particles) that communicate with each other wirelessly and perform distributed computations. • Dust particle to be mm size (grain of sand). • Network to be seamlessly integrated into environment for flexible application. • Each dust particle usually contains a sensor, a micro-controller, a transceiver, and powering mechanisms • The network can contain several hundreds or even thousands of dust particles.

Overview: What is a Smart Dust Network? • The dust particles sense physical attributes of the environment, and then wirelessly communicate these attributes to other dust particles. • Using a distributed computing algorithms, the dust particles fuse their data, and make decisions based on the cumulative information of the overall network. • Applications: – – Motion and Distance tracking Biological and Chemical Environmental Factors Distributed Image Recognition and Optical Sensing Acoustic and Vibrational Sensing

Overview: The Challenges • Dust particles are small size but must still house RF and computational circuitry. • Low Power: Dust particles are either to be powered externally or by a power source that is commensurately sized with respect to the dust particle. We must perform RF communication, computations and sensing which minimize power use, but still overcome noise limitations and bit errors. • How to physically produce dust particles that allow for sensing, communication and computation on a system that is millimeter scale? • What special computational codes and hardware do we need, and what special communication algorithms do we need?

Overview: Overcoming the Challenges To develop a state-of-the-art smart dust system we have divided the project into three major tasks. 1. Design of Physical Smart Dust Particles (Neil). 2. Development of Network Communication Protocols and Fusion of Data (Babis). 3. Computation for Data Analysis and Network control (Shuvra).

Design of Analog Smart Dust Particle Components Neil Goldsman

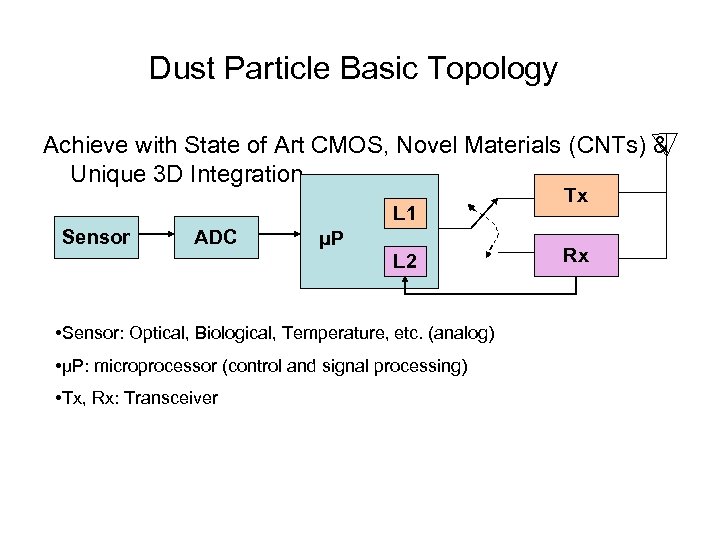

Dust Particle Basic Topology Achieve with State of Art CMOS, Novel Materials (CNTs) & Unique 3 D Integration L 1 Sensor ADC μP L 2 • Sensor: Optical, Biological, Temperature, etc. (analog) • μP: microprocessor (control and signal processing) • Tx, Rx: Transceiver Tx Rx

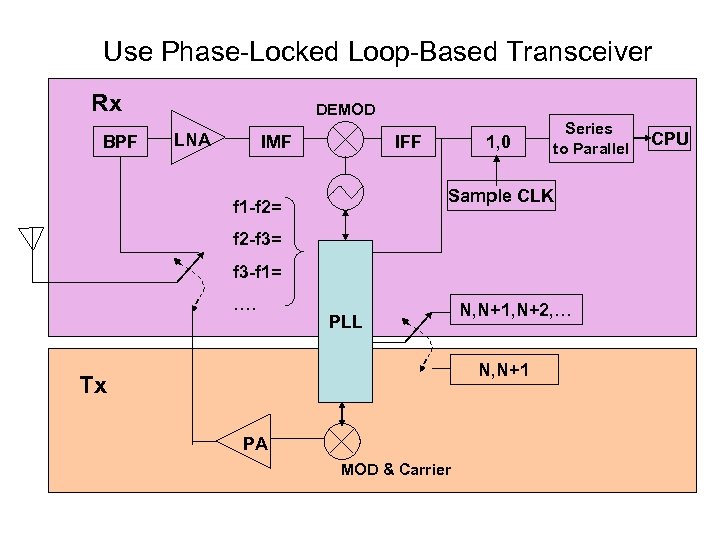

Use Phase-Locked Loop-Based Transceiver Rx BPF DEMOD LNA IMF IFF 1, 0 Series to Parallel Sample CLK f 1 -f 2= f 2 -f 3= f 3 -f 1= …. PLL N, N+1, N+2, … N, N+1 Tx PA MOD & Carrier CPU

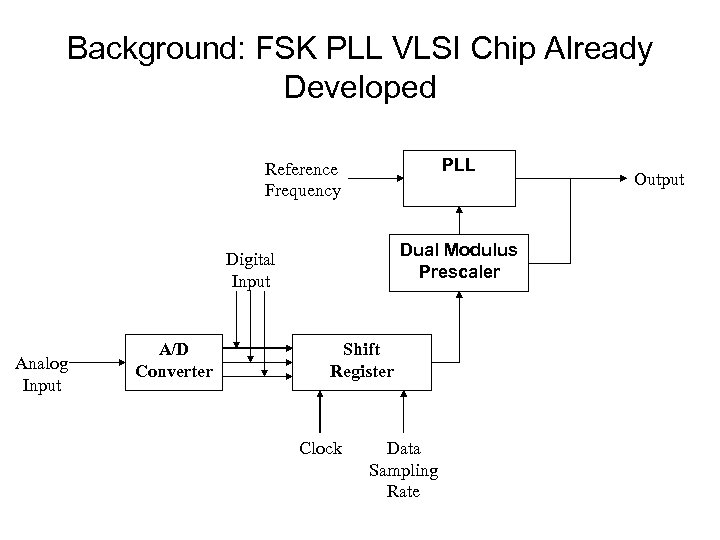

Background: FSK PLL VLSI Chip Already Developed PLL Reference Frequency Dual Modulus Prescaler Digital Input Analog Input A/D Converter Shift Register Clock Data Sampling Rate Output

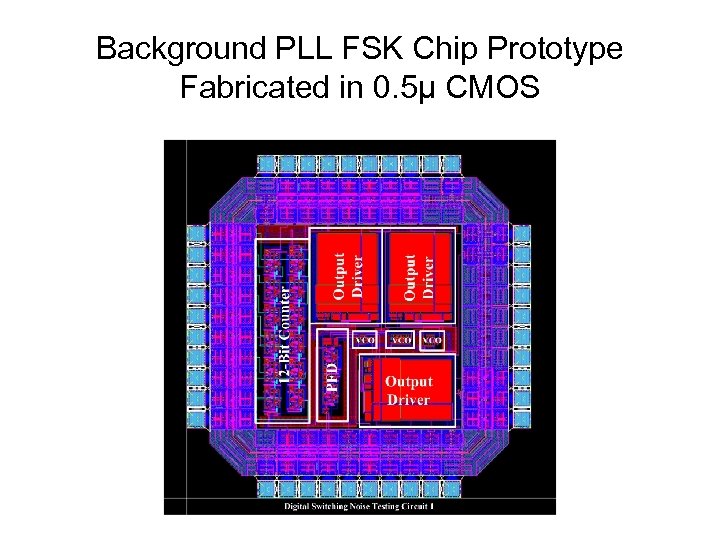

Background PLL FSK Chip Prototype Fabricated in 0. 5μ CMOS

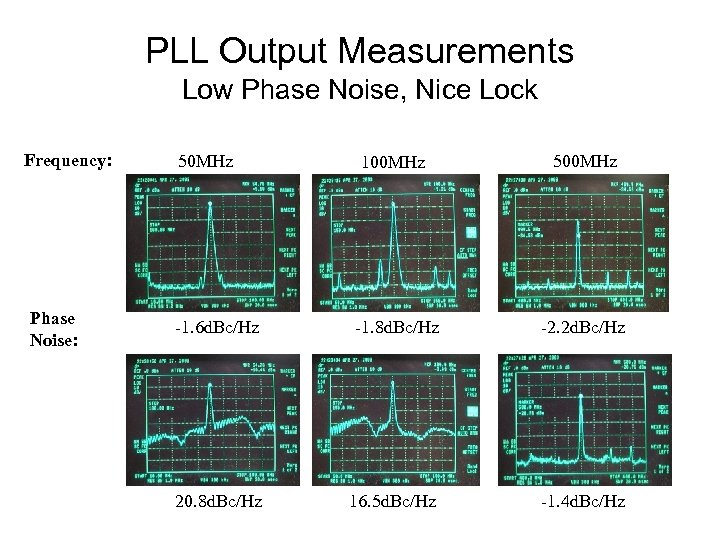

PLL Output Measurements Low Phase Noise, Nice Lock Frequency: Phase Noise: 50 MHz 100 MHz 500 MHz -1. 6 d. Bc/Hz -1. 8 d. Bc/Hz -2. 2 d. Bc/Hz 20. 8 d. Bc/Hz 16. 5 d. Bc/Hz -1. 4 d. Bc/Hz

Analog Structures for Meeting Low Power, Small Size Dust Design Constraints • Operating frequency high GHz for small dimensions • On-Chip antenna tuned to high GHz • Transceivers rely heavily on tuned circuits – Need State of Art Inductors for Max Q and Min Area. – 3 D inductor and Antenna design – Carbon Nanotube Kinetic Inductor (2 nd generation) • Sensors – On chip temperature sensor array – Optical diode array (visible and infrared) – MEMS accelerometer, microphone (2 nd generation) • On-chip microwave power harvester – Antenna and Schottky diode form power supply Assemble into Single Dust Particle with Novel 3 D Integration Methods

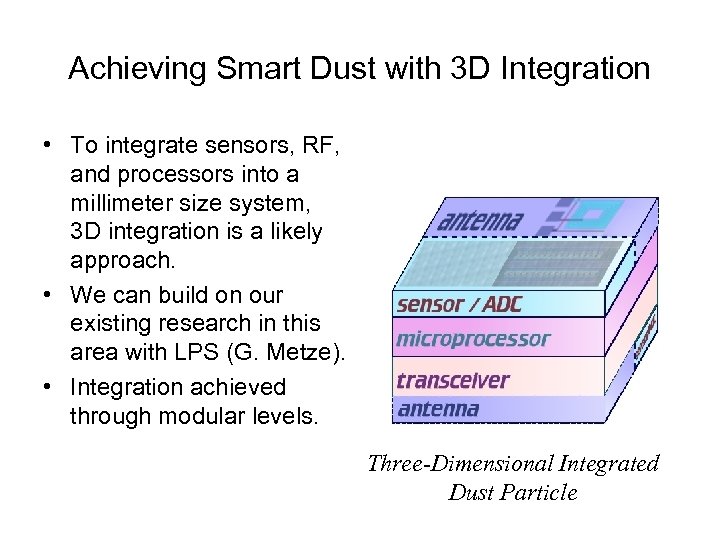

Achieving Smart Dust with 3 D Integration • To integrate sensors, RF, and processors into a millimeter size system, 3 D integration is a likely approach. • We can build on our existing research in this area with LPS (G. Metze). • Integration achieved through modular levels. Three-Dimensional Integrated Dust Particle

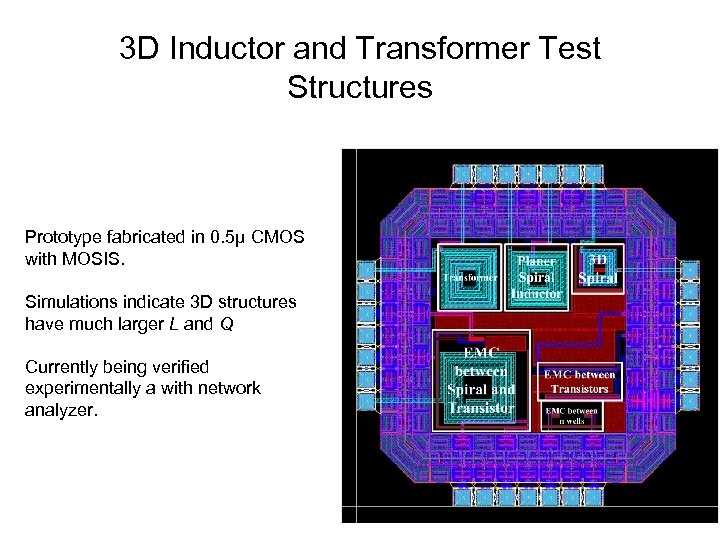

3 D Inductor and Transformer Test Structures Prototype fabricated in 0. 5μ CMOS with MOSIS. Simulations indicate 3 D structures have much larger L and Q Currently being verified experimentally a with network analyzer.

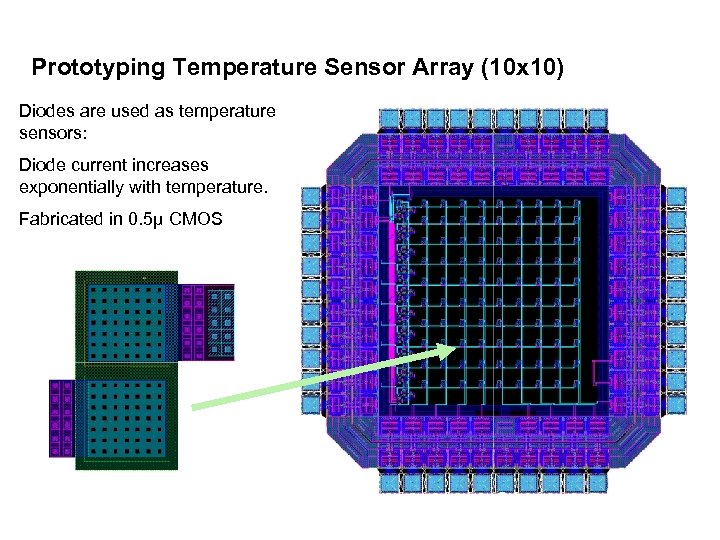

Prototyping Temperature Sensor Array (10 x 10) Diodes are used as temperature sensors: Diode current increases exponentially with temperature. Fabricated in 0. 5μ CMOS

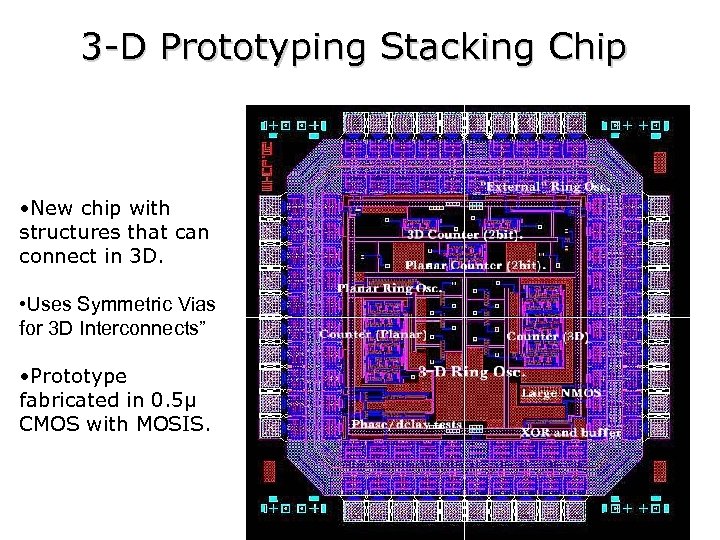

3 -D Prototyping Stacking Chip • New chip with structures that can connect in 3 D. • Uses Symmetric Vias for 3 D Interconnects” • Prototype fabricated in 0. 5μ CMOS with MOSIS.

Proof of Principle Prototype • Develop Temperature Sensor Smart Dust Network • Use aforementioned RF and Temperature Systems • Employ State of the Art Dust with 3 D Integration • Power – First with batteries – Second by harvesting the environment (RF, Heat) • Communication and Microcontrolling schemes to be used are described next.

72613a934d400099894f98e49cc18b04.ppt