Lect6_Commands.ppt

- Количество слайдов: 20

Системы команд процессоров

Системы команд процессоров

Логический состав процессора Адрес команда коп Упр. регистры РОН АЛУ IP сумматор Рег. ком И, или, не F сдвиги SP RAM операнды

Логический состав процессора Адрес команда коп Упр. регистры РОН АЛУ IP сумматор Рег. ком И, или, не F сдвиги SP RAM операнды

Логика функционирования процессора 1. Из оперативной памяти по адресу, записанному в РС, выбирается команда и записывается в регистр команд. 2. Команда дешифруется, т. е. из нее выделяются поля операции и операндов. Одновременно модифицируется РС, так, чтобы он указывал на следующую команду 3. Производится выборка операндов из оперативной памяти и/или регистров общего назначения; код операции и операнды подаются в АЛУ. 4. Выполняется операция, причем если операция арифметическая или логическая, то результат получается в регистрах АЛУ, при этом в зависимости от результата операции (положительный, отрицательный, нулевой, переполнение разрядной сетки и др. ) устанавливается признак результата в регистре признаков. 5. Результат записывается в соответствующее место оперативной памяти или регистр общего назначения. 6. Происходит возврат к П. 1.

Логика функционирования процессора 1. Из оперативной памяти по адресу, записанному в РС, выбирается команда и записывается в регистр команд. 2. Команда дешифруется, т. е. из нее выделяются поля операции и операндов. Одновременно модифицируется РС, так, чтобы он указывал на следующую команду 3. Производится выборка операндов из оперативной памяти и/или регистров общего назначения; код операции и операнды подаются в АЛУ. 4. Выполняется операция, причем если операция арифметическая или логическая, то результат получается в регистрах АЛУ, при этом в зависимости от результата операции (положительный, отрицательный, нулевой, переполнение разрядной сетки и др. ) устанавливается признак результата в регистре признаков. 5. Результат записывается в соответствующее место оперативной памяти или регистр общего назначения. 6. Происходит возврат к П. 1.

Функциональные группы команд процессоров 1. Команды пересылки (включая команды обмена с портами (ввода/вывода)) 2. Арифметико-логические команды а) Арифметические инструкции ( «+» , «-» , «*» , «/» ) б) Логические инструкции (И, ИЛИ, НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ) в) Арифметические и логические сдвиги 3. Команды переходов а) Безусловные переходы б) Условные переходы в) Циклы г) Организация подпрограмм д) Обработка прерываний 4. Команды управления состоянием процессора

Функциональные группы команд процессоров 1. Команды пересылки (включая команды обмена с портами (ввода/вывода)) 2. Арифметико-логические команды а) Арифметические инструкции ( «+» , «-» , «*» , «/» ) б) Логические инструкции (И, ИЛИ, НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ) в) Арифметические и логические сдвиги 3. Команды переходов а) Безусловные переходы б) Условные переходы в) Циклы г) Организация подпрограмм д) Обработка прерываний 4. Команды управления состоянием процессора

Команды пересылки Stor r, mem (mov mem, r) Load r, mem (mov r, mem) РОН RAM mov r 1, r 2 pop r push r Stack in r, port out r, port I/O Ports 1. В подавляющем большинстве случаев имеет Место копирование информации из источника в приемник 2. в подавляющем большинстве случаев не влияют на состояние регистра флагов

Команды пересылки Stor r, mem (mov mem, r) Load r, mem (mov r, mem) РОН RAM mov r 1, r 2 pop r push r Stack in r, port out r, port I/O Ports 1. В подавляющем большинстве случаев имеет Место копирование информации из источника в приемник 2. в подавляющем большинстве случаев не влияют на состояние регистра флагов

Арифметические инструкции 1. используют блоки АЛУ 2. устанавливают признак результата 3. операции сложения и вычитания могут дополнительно устанавливать признак переноса/заёма (carry/borrow flag — C) 4. операции умножения могут дополнительно устанавливать флаг переполнения (overflow — V) 5. операции умножения и деления используют регистр двойной Длины (результат операции умножения, делимое и результат Деления — частное и остаток ) делимое 1 -й сомножитель / Х 2 -й сомножитель = делитель = результат остаток частное результат

Арифметические инструкции 1. используют блоки АЛУ 2. устанавливают признак результата 3. операции сложения и вычитания могут дополнительно устанавливать признак переноса/заёма (carry/borrow flag — C) 4. операции умножения могут дополнительно устанавливать флаг переполнения (overflow — V) 5. операции умножения и деления используют регистр двойной Длины (результат операции умножения, делимое и результат Деления — частное и остаток ) делимое 1 -й сомножитель / Х 2 -й сомножитель = делитель = результат остаток частное результат

Логические инструкции Логическая операция И (AND) операнд 1 операнд 2 Результат 0 0 0 1 0 1 1 1 Логическая операция ИСКЛЮЧАЮЩЕЕ ИЛИ(XOR) операнд 1 операнд 2 результат 0 0 0 1 0 1 1 1 Логическая операция НЕ(NOT) 0 1 Логическая операция ИЛИ (OR) операнд результа т 1 0 1 0

Логические инструкции Логическая операция И (AND) операнд 1 операнд 2 Результат 0 0 0 1 0 1 1 1 Логическая операция ИСКЛЮЧАЮЩЕЕ ИЛИ(XOR) операнд 1 операнд 2 результат 0 0 0 1 0 1 1 1 Логическая операция НЕ(NOT) 0 1 Логическая операция ИЛИ (OR) операнд результа т 1 0 1 0

Инструкции сдвигов Арифметический и логический Сдвиг влево 1 1 0 0 1 Логический сдвиг вправо 1 0 0 0 1 0 1 CF 0 CF Арифметический сдвиг вправо Устанавливают регистр флагов и флаг переноса Дополнительно бывают циклические сдвиги(вращения) и циклические сдвиги через флаг переноса 1 0 1 1 1 0 Код знака 0 1 1 0 0 1 0 CF

Инструкции сдвигов Арифметический и логический Сдвиг влево 1 1 0 0 1 Логический сдвиг вправо 1 0 0 0 1 0 1 CF 0 CF Арифметический сдвиг вправо Устанавливают регистр флагов и флаг переноса Дополнительно бывают циклические сдвиги(вращения) и циклические сдвиги через флаг переноса 1 0 1 1 1 0 Код знака 0 1 1 0 0 1 0 CF

Инструкции переходов Безусловный переход — значение адреса перехода записывается в программный счетчик (значение адреса перехода может быть как абсолютным, так и вычисляемым) КОП Адрес перехода IP Условный переход: 1. проверяется состояние регистра флагов 2. если флаги, соотвествующие условиям перехода, выставлены, то в программный счетчик записывается адрес перехода, Иначе содержимое IP не меняется Условия перехода Переход по 0 (переход по равно) Переход по + (переход по больше) Переход по - (переход по меньне) Переход по 0 или + (больше или равно) флаги Z=1 P=1 N=1 Z=1 или P=1

Инструкции переходов Безусловный переход — значение адреса перехода записывается в программный счетчик (значение адреса перехода может быть как абсолютным, так и вычисляемым) КОП Адрес перехода IP Условный переход: 1. проверяется состояние регистра флагов 2. если флаги, соотвествующие условиям перехода, выставлены, то в программный счетчик записывается адрес перехода, Иначе содержимое IP не меняется Условия перехода Переход по 0 (переход по равно) Переход по + (переход по больше) Переход по - (переход по меньне) Переход по 0 или + (больше или равно) флаги Z=1 P=1 N=1 Z=1 или P=1

Применение инструкций переходов. . . T F A>B Действия 1 Действия 2 M 1: M 2: CMP A, B JP M 1 Выполнение Действий 1 JMP M 2 Выполнение Действий 2. . .

Применение инструкций переходов. . . T F A>B Действия 1 Действия 2 M 1: M 2: CMP A, B JP M 1 Выполнение Действий 1 JMP M 2 Выполнение Действий 2. . .

Организация циклов с применением инструкций переходов F A<0 T Cycl: Тело цикла Out: CMP A, 0 x 00 JN Out тело цикла JMP Cycl. . .

Организация циклов с применением инструкций переходов F A<0 T Cycl: Тело цикла Out: CMP A, 0 x 00 JN Out тело цикла JMP Cycl. . .

Организация цикла со счетчиком Команда организации цикла со счетчиком LOOP Перед началом выполнения цикла в регистр-счетчик заносится количество повторений тела цикла; При каждом выполнении команды LOOP выполняется два действия: 1. из содержимого регистра-счетчика вычитается единица, и результат заносится в Регистр-счетчик; 2. выполняется команда условного перехода по ненулевому результату Цикл с предусловием Cycl: Body: Out: Загрузить в Rсч N Loop Body JMP Out Тело Цикла JMP Cycl …. . . Цикл с постусловием Cycl: Загрузить в Rсч N Тело цикла loop Cycl …. . . .

Организация цикла со счетчиком Команда организации цикла со счетчиком LOOP Перед началом выполнения цикла в регистр-счетчик заносится количество повторений тела цикла; При каждом выполнении команды LOOP выполняется два действия: 1. из содержимого регистра-счетчика вычитается единица, и результат заносится в Регистр-счетчик; 2. выполняется команда условного перехода по ненулевому результату Цикл с предусловием Cycl: Body: Out: Загрузить в Rсч N Loop Body JMP Out Тело Цикла JMP Cycl …. . . Цикл с постусловием Cycl: Загрузить в Rсч N Тело цикла loop Cycl …. . . .

Команды управления состоянием процессора Команды, обеспечивающие управление состоянием процессора, режимами его работы и состоянием вычислительного процесса (Wait, Halt) Перевод процессора в состояние ожидания внешнего события или останова Установка и сброс отдельных флажков В регистре флажков (clc, stc, cli, sti и др. )

Команды управления состоянием процессора Команды, обеспечивающие управление состоянием процессора, режимами его работы и состоянием вычислительного процесса (Wait, Halt) Перевод процессора в состояние ожидания внешнего события или останова Установка и сброс отдельных флажков В регистре флажков (clc, stc, cli, sti и др. )

Методы адресации При доступе к операндам, размещенным в регистрах, памяти и портах ввода/вывода выделяются следующие методы адресации: прямая (абсолютная адресация); относительная адресация; индексная адресация; непосредственная адресация; косвенная адресация; неявная адресация; Кроме того, в современных компьютерах

Методы адресации При доступе к операндам, размещенным в регистрах, памяти и портах ввода/вывода выделяются следующие методы адресации: прямая (абсолютная адресация); относительная адресация; индексная адресация; непосредственная адресация; косвенная адресация; неявная адресация; Кроме того, в современных компьютерах

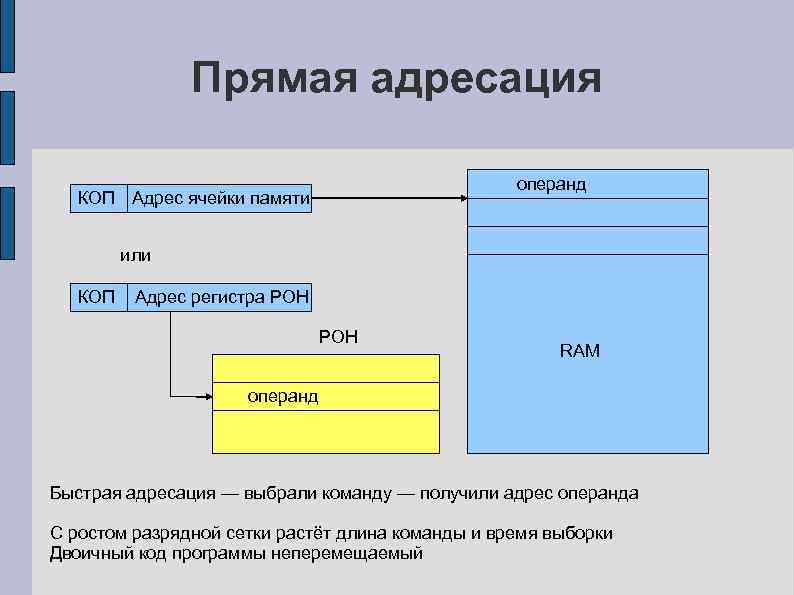

Прямая адресация операнд КОП Адрес ячейки памяти или КОП Адрес регистра РОН RAM операнд Быстрая адресация — выбрали команду — получили адрес операнда С ростом разрядной сетки растёт длина команды и время выборки Двоичный код программы неперемещаемый

Прямая адресация операнд КОП Адрес ячейки памяти или КОП Адрес регистра РОН RAM операнд Быстрая адресация — выбрали команду — получили адрес операнда С ростом разрядной сетки растёт длина команды и время выборки Двоичный код программы неперемещаемый

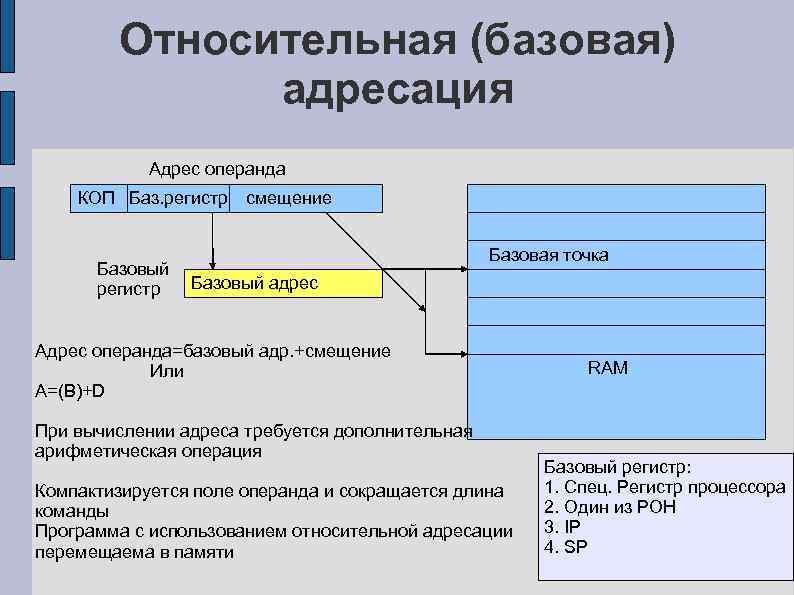

Относительная (базовая) адресация Адрес операнда КОП Баз. регистр Базовый регистр смещение Базовая точка Базовый адрес Адрес операнда=базовый адр. +смещение Или A=(B)+D При вычислении адреса требуется дополнительная арифметическая операция Компактизируется поле операнда и сокращается длина команды Программа с использованием относительной адресации перемещаема в памяти RAM Базовый регистр: 1. Спец. Регистр процессора 2. Один из РОН 3. IP 4. SP

Относительная (базовая) адресация Адрес операнда КОП Баз. регистр Базовый регистр смещение Базовая точка Базовый адрес Адрес операнда=базовый адр. +смещение Или A=(B)+D При вычислении адреса требуется дополнительная арифметическая операция Компактизируется поле операнда и сокращается длина команды Программа с использованием относительной адресации перемещаема в памяти RAM Базовый регистр: 1. Спец. Регистр процессора 2. Один из РОН 3. IP 4. SP

Индексная адресация КОП Инд. регистр RAM(длина слова — 2 байта) Адрес нач. мас Элемент мас. 0 — инд. см. 0 Индексный Регистр Х Индексное смещение Элемент мас. 1 — инд. см. 2 Элемент мас. 2 — инд. см. 4 Адр. =Адрес_нач_мас+индексное смещение A=An+(X) Элемент мас. 3 — инд. см. 6 X=(i - 1) * Lэл – для одномерного массива Х = ((i - 1) * Jmax + j - 1) * Lэл – для двумерного Х = ((i - 1) * Jmax * Kmax + (j - 1) * Kmax + k-1) * Lэл - для трехмерного Общий случай — индексно-относительная адресация КОП Баз. регистр Инд. регистр смещение A=(B)+(X)+D

Индексная адресация КОП Инд. регистр RAM(длина слова — 2 байта) Адрес нач. мас Элемент мас. 0 — инд. см. 0 Индексный Регистр Х Индексное смещение Элемент мас. 1 — инд. см. 2 Элемент мас. 2 — инд. см. 4 Адр. =Адрес_нач_мас+индексное смещение A=An+(X) Элемент мас. 3 — инд. см. 6 X=(i - 1) * Lэл – для одномерного массива Х = ((i - 1) * Jmax + j - 1) * Lэл – для двумерного Х = ((i - 1) * Jmax * Kmax + (j - 1) * Kmax + k-1) * Lэл - для трехмерного Общий случай — индексно-относительная адресация КОП Баз. регистр Инд. регистр смещение A=(B)+(X)+D

Непосредственная адресация КОП Непосредственный операнд Самая быстрая форма адресации — операнд выбирается вместе с командой

Непосредственная адресация КОП Непосредственный операнд Самая быстрая форма адресации — операнд выбирается вместе с командой

Косвенная адресация КОП Адрес указателя косвенно-регистровая КОП Адрес регистра косв. адр. Адрес операнда Операнд Рег. косв. адресации или РОН Адрес операнда RAM Количество указателей в цепочке — кратность косвенной адресации Работает медленно — чем больше кратность — тем больше выборок из памяти Является удобным механизмом для работы с динамическими структурами данных, память под которые выделяется в процессе работы программы

Косвенная адресация КОП Адрес указателя косвенно-регистровая КОП Адрес регистра косв. адр. Адрес операнда Операнд Рег. косв. адресации или РОН Адрес операнда RAM Количество указателей в цепочке — кратность косвенной адресации Работает медленно — чем больше кратность — тем больше выборок из памяти Является удобным механизмом для работы с динамическими структурами данных, память под которые выделяется в процессе работы программы

Неявная адресация и безадресная память Неявная адресация — операнд в поле операндов не указывается, определяется типом команды и архитектурой процессора Безадресная память — стек — реализуется областью Обычной оперативной памяти и регистром-указателем стека RAM Указатель стека Стек традиционно растет от старших адресов к младшим, при аппаратной и программно-аппаратной организации стека указатель стека при стековых операциях Изменяется автоматически Вершина стека Дно стека

Неявная адресация и безадресная память Неявная адресация — операнд в поле операндов не указывается, определяется типом команды и архитектурой процессора Безадресная память — стек — реализуется областью Обычной оперативной памяти и регистром-указателем стека RAM Указатель стека Стек традиционно растет от старших адресов к младшим, при аппаратной и программно-аппаратной организации стека указатель стека при стековых операциях Изменяется автоматически Вершина стека Дно стека