Аттестация.ppt

- Количество слайдов: 21

Системотехника ЭВС, комплексы и сети 1

Системотехника ЭВС, комплексы и сети 1

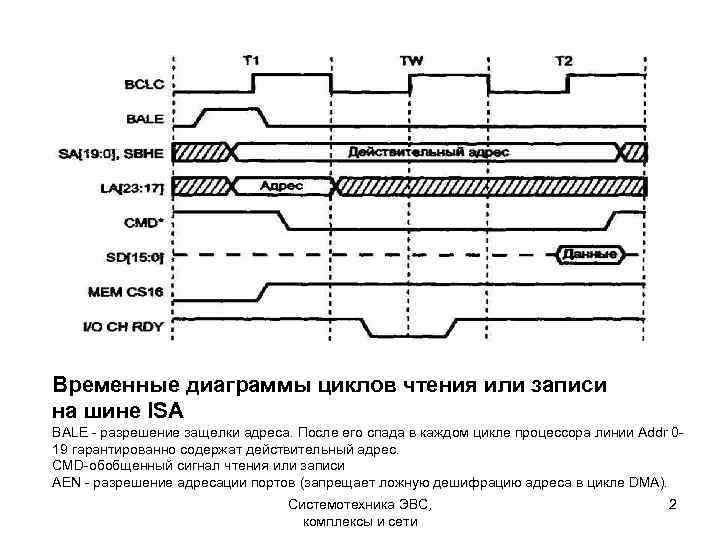

Временные диаграммы циклов чтения или записи на шине ISA BALE - разрешение защелки адреса. После его спада в каждом цикле процессора линии Addr 019 гарантированно содержат действительный адрес. CMD-обобщенный сигнал чтения или записи AEN - разрешение адресации портов (запрещает ложную дешифрацию адреса в цикле DMA). Системотехника ЭВС, комплексы и сети 2

Временные диаграммы циклов чтения или записи на шине ISA BALE - разрешение защелки адреса. После его спада в каждом цикле процессора линии Addr 019 гарантированно содержат действительный адрес. CMD-обобщенный сигнал чтения или записи AEN - разрешение адресации портов (запрещает ложную дешифрацию адреса в цикле DMA). Системотехника ЭВС, комплексы и сети 2

Временные диаграммы шины PCI • • CLK • • _______ FRAME |_________________| • • • AD C/BE ___ ___| |___| |___ _______ ______ -------<______><______><______>--Адрес Данные 1 Данные 2 Данные 3 Данные 4 ___________________ -------<______><________________>--Команда Сигнал разрешения передачи байта • • IRDY • • _______ TRDY |________________| • • _______ ___ DEVSEL |________________| ______ ___ |________________| Системотехника ЭВС, комплексы и сети ___ 3

Временные диаграммы шины PCI • • CLK • • _______ FRAME |_________________| • • • AD C/BE ___ ___| |___| |___ _______ ______ -------<______><______><______>--Адрес Данные 1 Данные 2 Данные 3 Данные 4 ___________________ -------<______><________________>--Команда Сигнал разрешения передачи байта • • IRDY • • _______ TRDY |________________| • • _______ ___ DEVSEL |________________| ______ ___ |________________| Системотехника ЭВС, комплексы и сети ___ 3

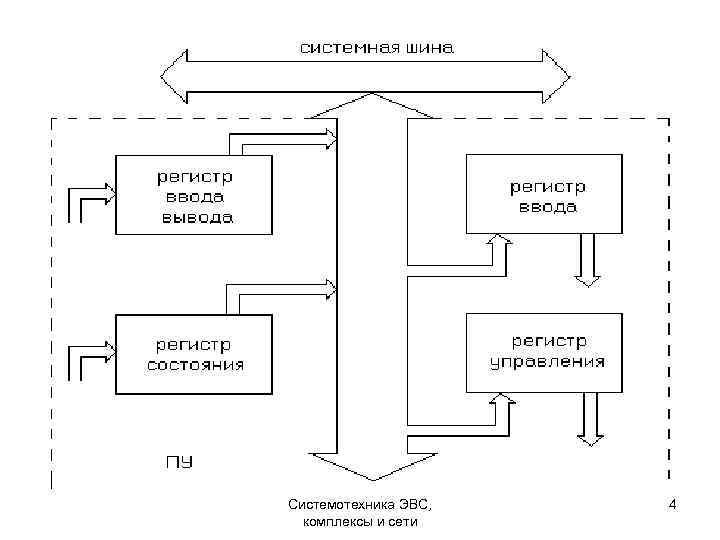

Системотехника ЭВС, комплексы и сети 4

Системотехника ЭВС, комплексы и сети 4

Блок схема контроллера прерываний Системотехника ЭВС, комплексы и сети 5

Блок схема контроллера прерываний Системотехника ЭВС, комплексы и сети 5

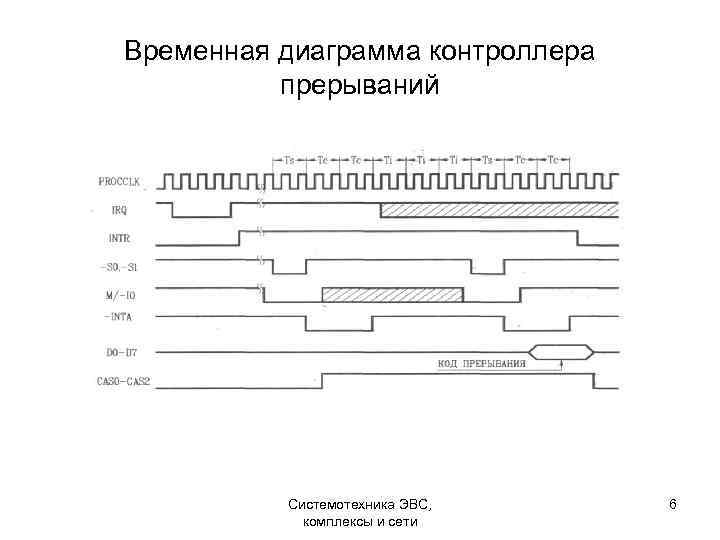

Временная диаграмма контроллера прерываний Системотехника ЭВС, комплексы и сети 6

Временная диаграмма контроллера прерываний Системотехника ЭВС, комплексы и сети 6

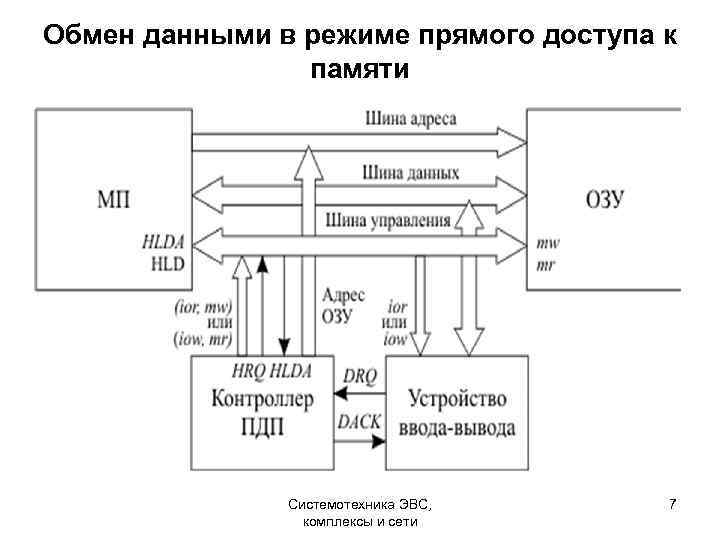

Обмен данными в режиме прямого доступа к памяти Системотехника ЭВС, комплексы и сети 7

Обмен данными в режиме прямого доступа к памяти Системотехника ЭВС, комплексы и сети 7

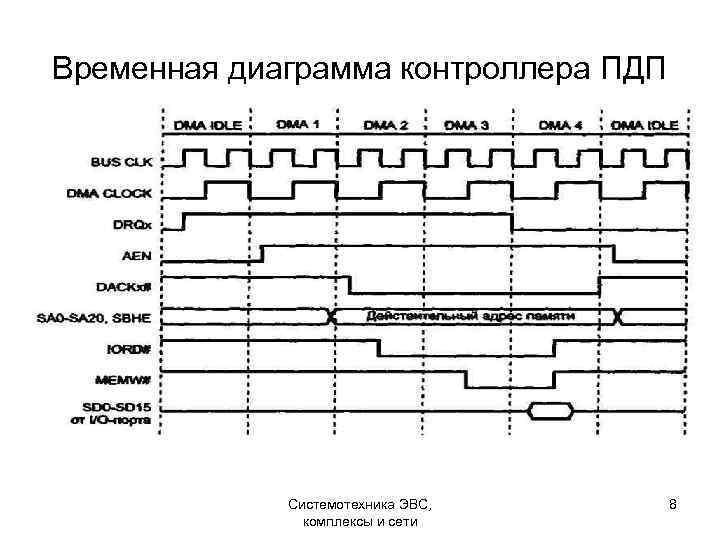

Временная диаграмма контроллера ПДП Системотехника ЭВС, комплексы и сети 8

Временная диаграмма контроллера ПДП Системотехника ЭВС, комплексы и сети 8

Элементы памяти Системотехника ЭВС, комплексы и сети 9

Элементы памяти Системотехника ЭВС, комплексы и сети 9

Блок схема видеоконтроллера Системотехника ЭВС, комплексы и сети 10

Блок схема видеоконтроллера Системотехника ЭВС, комплексы и сети 10

Программируемый периферийный адаптер Системотехника ЭВС, комплексы и сети 11

Программируемый периферийный адаптер Системотехника ЭВС, комплексы и сети 11

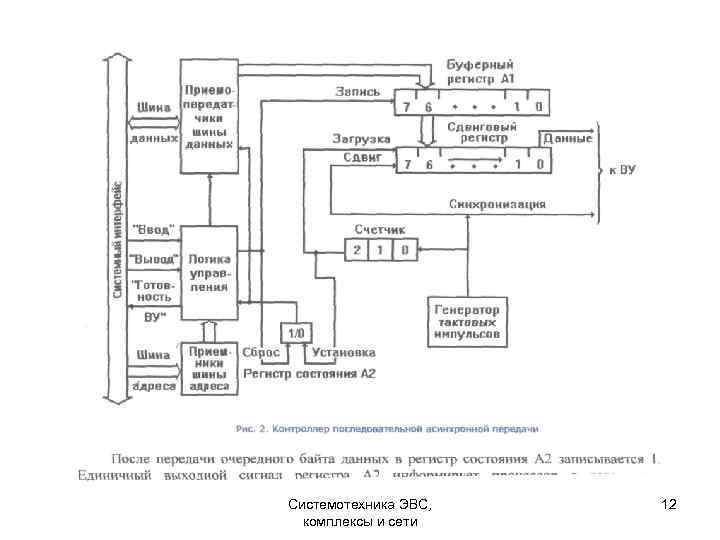

Системотехника ЭВС, комплексы и сети 12

Системотехника ЭВС, комплексы и сети 12

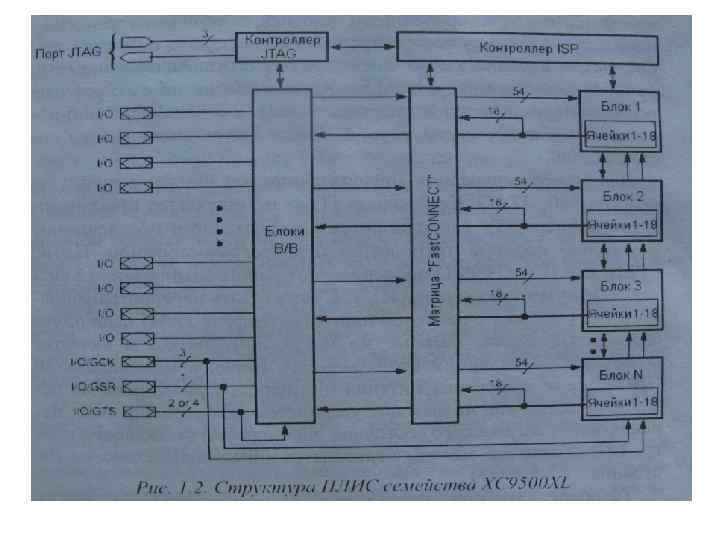

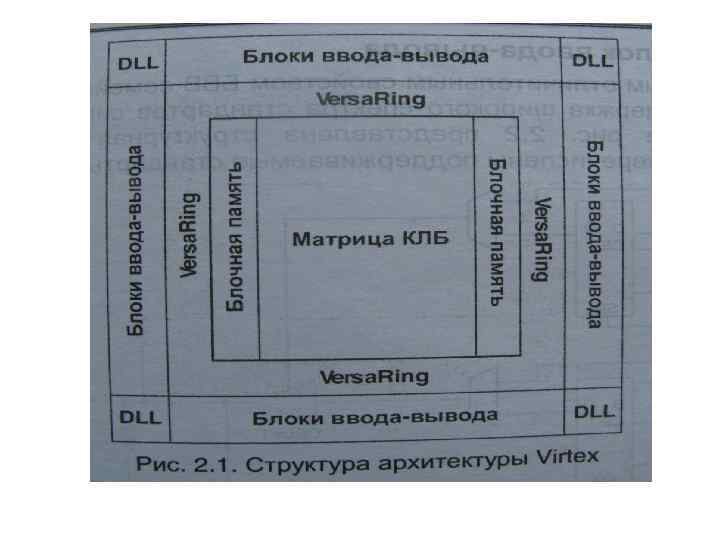

Структура интегральных схем

Структура интегральных схем

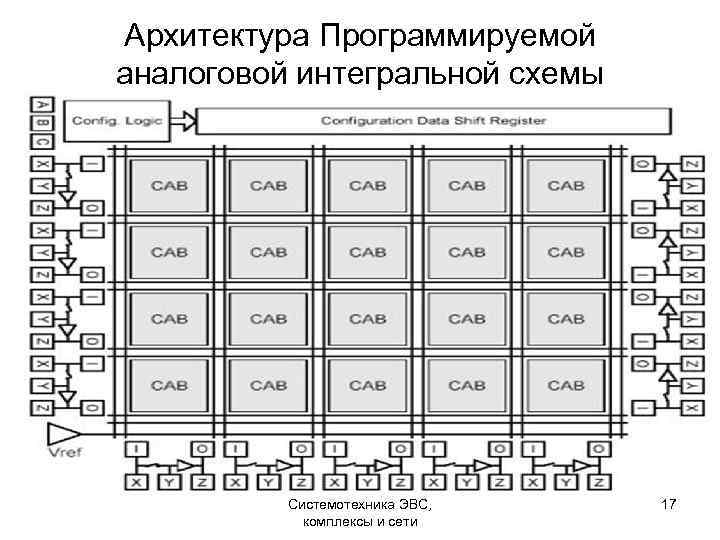

Архитектура Программируемой аналоговой интегральной схемы Системотехника ЭВС, комплексы и сети 17

Архитектура Программируемой аналоговой интегральной схемы Системотехника ЭВС, комплексы и сети 17

Области применения ПАИС • ПАИС предназначены для создания аналоговых устройств в частотном диапазоне от постоянного тока до 2 МГц, однако в ряде случаев верхняя частота ограничивается 400 к. ГЦ. • Обработка сигналов от датчиков, • Аналоговые схемы управления, • Комплексная фильтрация, • Интерфейсы и усилители сигналов фотодиодов, • Преобразователи напряжение/ток и ток/напряжение, обработка и фильтрация аудио сигналов, • Частотные модуляторы, • аналоговые умножители, • Тональные генераторы и многое другое Системотехника ЭВС, комплексы и сети 18

Области применения ПАИС • ПАИС предназначены для создания аналоговых устройств в частотном диапазоне от постоянного тока до 2 МГц, однако в ряде случаев верхняя частота ограничивается 400 к. ГЦ. • Обработка сигналов от датчиков, • Аналоговые схемы управления, • Комплексная фильтрация, • Интерфейсы и усилители сигналов фотодиодов, • Преобразователи напряжение/ток и ток/напряжение, обработка и фильтрация аудио сигналов, • Частотные модуляторы, • аналоговые умножители, • Тональные генераторы и многое другое Системотехника ЭВС, комплексы и сети 18

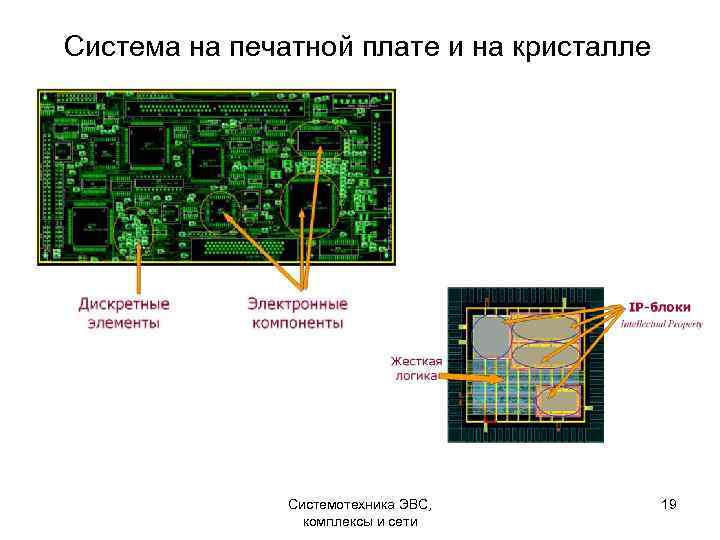

Система на печатной плате и на кристалле Системотехника ЭВС, комплексы и сети 19

Система на печатной плате и на кристалле Системотехника ЭВС, комплексы и сети 19

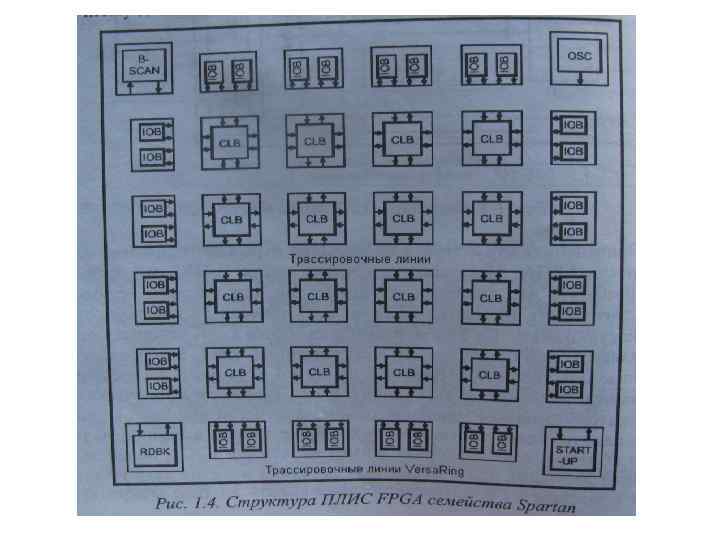

Структурная схема модуля Spartan-3 Starter Kit Системотехника ЭВС, комплексы и сети 20

Структурная схема модуля Spartan-3 Starter Kit Системотехника ЭВС, комплексы и сети 20

• • Этапы проектирования ПЛИС создание проекта: выбор тира ПЛИС, подключение необходимых ресурсов и библиотек, выбор средств синтеза; подготовка описания RTL-модели устройства в схемотехническом или алгоритмическом виде; синтез RTL-описания в список связей элементов из стандартной библиотеки фирмы Xilinx; функциональное моделирование и верификация логики работы устройства (осуществляется в системе моделирования Model. Sim); трансляция списка связей в схему соединений узлов данной архитектуры ПЛИС (этот этап относится к логическому уровню, на котором рассматриваются реальные элементы, но связи между ними считаются идеальными, ибо не определены); размещение проекта в кристалле и конфигурация трассировочных ресурсов (теперь определены задержки линий связи между узлами ПЛИС, что соответствует физическому уровню); полное временное моделирование, основанное на имеющейся информации о всех задержках при данной конфигурации ПЛИС (осуществляется в системе моделирования Model. Sim); загрузка проекта в энергонезависимую память CPLD или внешнюю память конфигурации FPGA. Системотехника ЭВС, комплексы и сети 21

• • Этапы проектирования ПЛИС создание проекта: выбор тира ПЛИС, подключение необходимых ресурсов и библиотек, выбор средств синтеза; подготовка описания RTL-модели устройства в схемотехническом или алгоритмическом виде; синтез RTL-описания в список связей элементов из стандартной библиотеки фирмы Xilinx; функциональное моделирование и верификация логики работы устройства (осуществляется в системе моделирования Model. Sim); трансляция списка связей в схему соединений узлов данной архитектуры ПЛИС (этот этап относится к логическому уровню, на котором рассматриваются реальные элементы, но связи между ними считаются идеальными, ибо не определены); размещение проекта в кристалле и конфигурация трассировочных ресурсов (теперь определены задержки линий связи между узлами ПЛИС, что соответствует физическому уровню); полное временное моделирование, основанное на имеющейся информации о всех задержках при данной конфигурации ПЛИС (осуществляется в системе моделирования Model. Sim); загрузка проекта в энергонезависимую память CPLD или внешнюю память конфигурации FPGA. Системотехника ЭВС, комплексы и сети 21