46057d7e9c894559096783d1d6a0529b.ppt

- Количество слайдов: 12

SISSA Trieste AMD and SUN Trieste, 22 Novembre 2004 Roberto Dognini Business Development Enterprise Manager

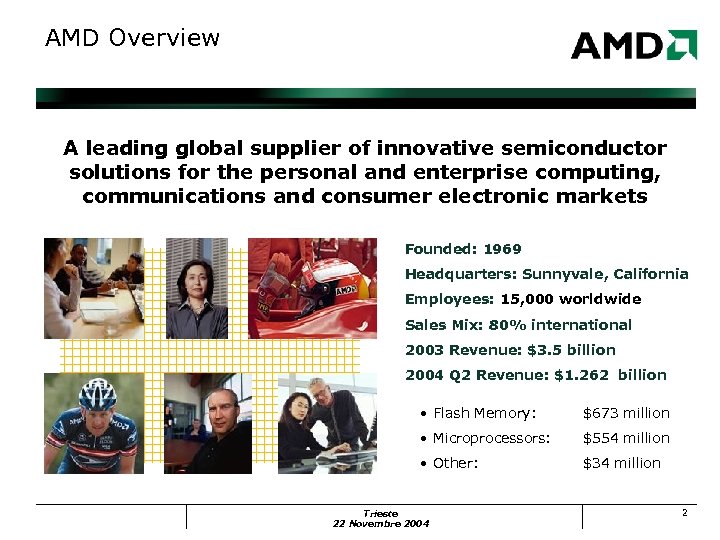

AMD Overview A leading global supplier of innovative semiconductor solutions for the personal and enterprise computing, communications and consumer electronic markets Founded: 1969 Headquarters: Sunnyvale, California Employees: 15, 000 worldwide Sales Mix: 80% international 2003 Revenue: $3. 5 billion 2004 Q 2 Revenue: $1. 262 billion • Flash Memory: $673 million • Microprocessors: $554 million • Other: $34 million Trieste 22 Novembre 2004 2

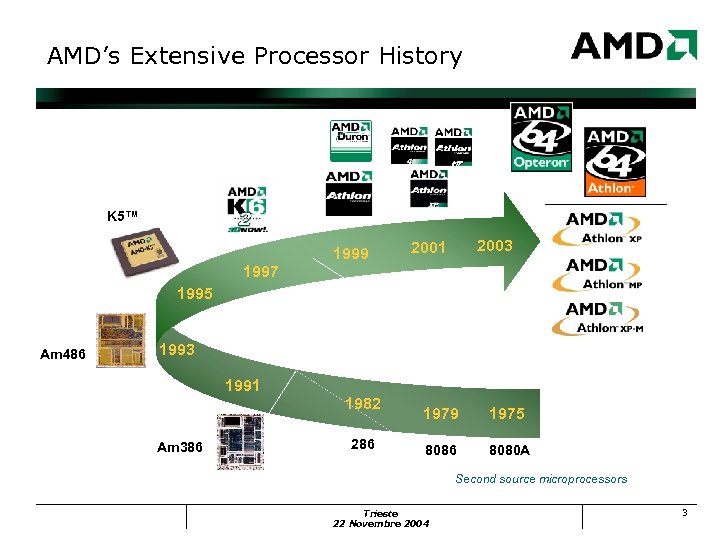

AMD’s Extensive Processor History K 5™ 1999 2003 2001 1997 1995 Am 486 1993 1991 1982 Am 386 286 1979 1975 8086 8080 A Second source microprocessors Trieste 22 Novembre 2004 3

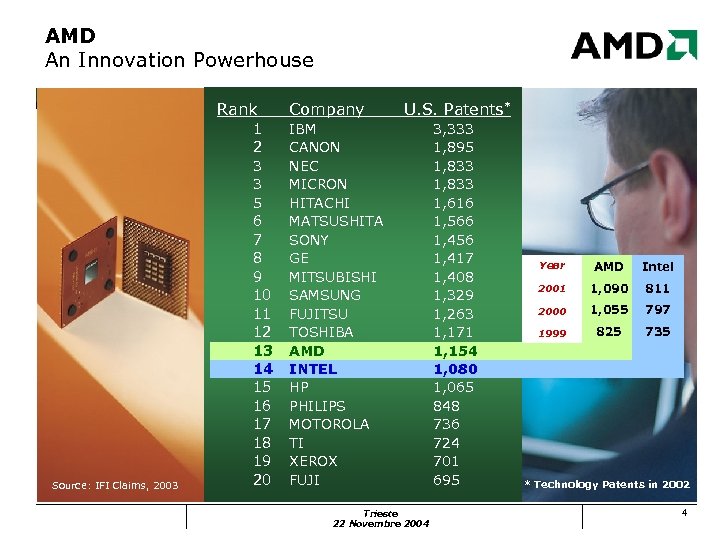

AMD An Innovation Powerhouse Rank Source: IFI Claims, 2003 1 2 3 3 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 Company U. S. Patents* IBM CANON NEC MICRON HITACHI MATSUSHITA SONY GE MITSUBISHI SAMSUNG FUJITSU TOSHIBA AMD INTEL HP PHILIPS MOTOROLA TI XEROX FUJI Trieste 22 Novembre 2004 3, 333 1, 895 1, 833 1, 616 1, 566 1, 456 1, 417 1, 408 1, 329 1, 263 1, 171 1, 154 1, 080 1, 065 848 736 724 701 695 Year AMD Intel 2001 1, 090 811 2000 1, 055 797 1999 825 735 * Technology Patents in 2002 4

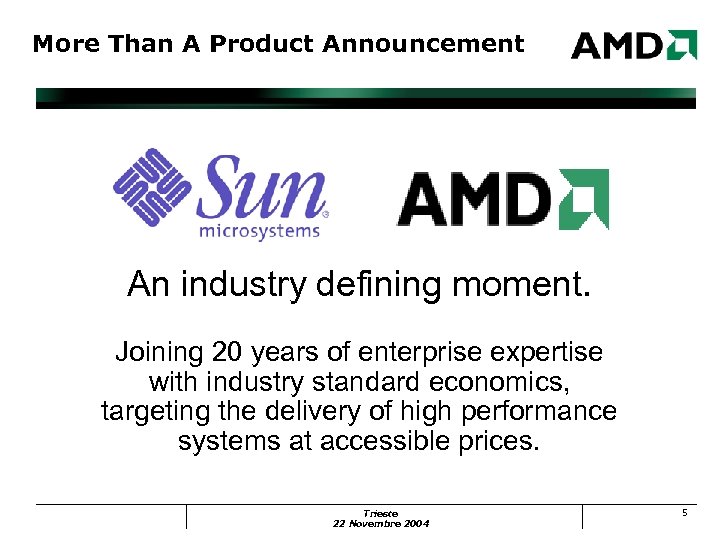

More Than A Product Announcement An industry defining moment. Joining 20 years of enterprise expertise with industry standard economics, targeting the delivery of high performance systems at accessible prices. Trieste 22 Novembre 2004 5

Building the AMD 64 Ecosystem AMD and SUN Key independent software vendors are already embracing the Sun and AMD Opteron processor-based offering as the standard in network computing: BEA Systems, Cadence Design Systems, Inc. , Computer Associates, Documentum, Matrix. One Inc. , Oracle, Synopsys, Inc. , and SAP AG. http: //www. amd. com/us-en/assets/content_type/Downloadable. Assets/AMD 64_ecosystem_final. pdf Trieste 22 Novembre 2004 6

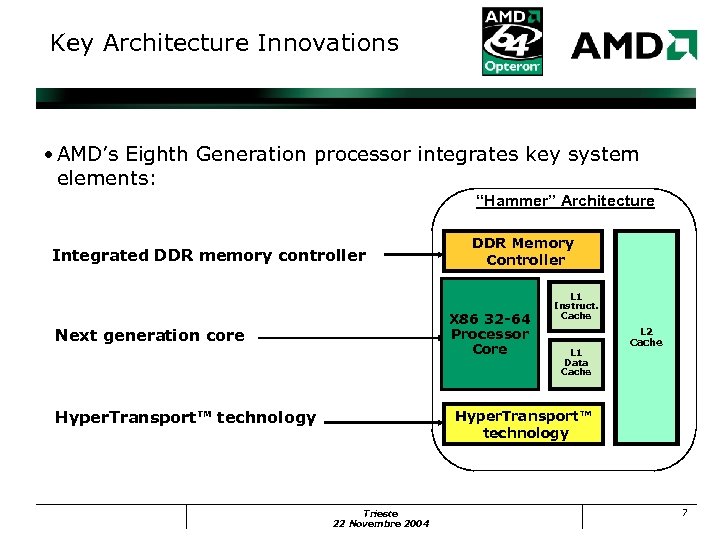

Key Architecture Innovations • AMD’s Eighth Generation processor integrates key system elements: “Hammer” Architecture Integrated DDR memory controller DDR Memory Controller X 86 32 -64 Processor Core Next generation core Hyper. Transport™ technology L 1 Instruct. Cache L 1 Data Cache L 2 Cache Hyper. Transport™ technology Trieste 22 Novembre 2004 7

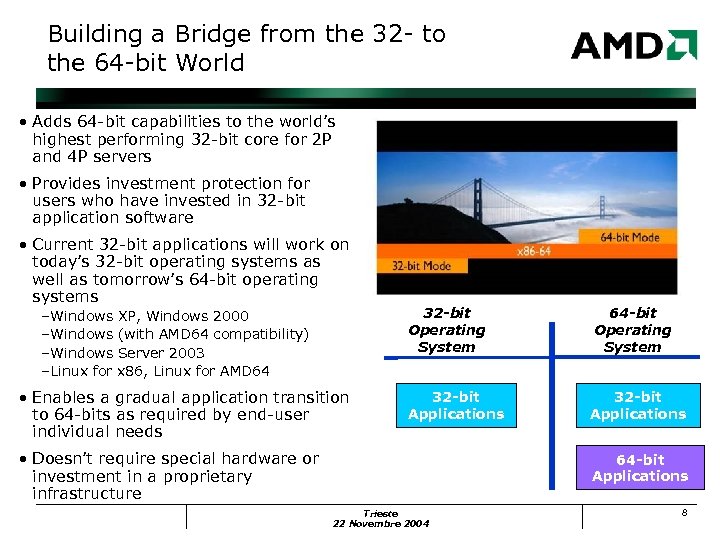

Building a Bridge from the 32 - to the 64 -bit World • Adds 64 -bit capabilities to the world’s highest performing 32 -bit core for 2 P and 4 P servers • Provides investment protection for users who have invested in 32 -bit application software • Current 32 -bit applications will work on today’s 32 -bit operating systems as well as tomorrow’s 64 -bit operating systems –Windows XP, Windows 2000 –Windows (with AMD 64 compatibility) –Windows Server 2003 –Linux for x 86, Linux for AMD 64 • Enables a gradual application transition to 64 -bits as required by end-user individual needs 32 -bit Operating System 64 -bit Operating System 32 -bit Applications • Doesn’t require special hardware or investment in a proprietary infrastructure 64 -bit Applications Trieste 22 Novembre 2004 8

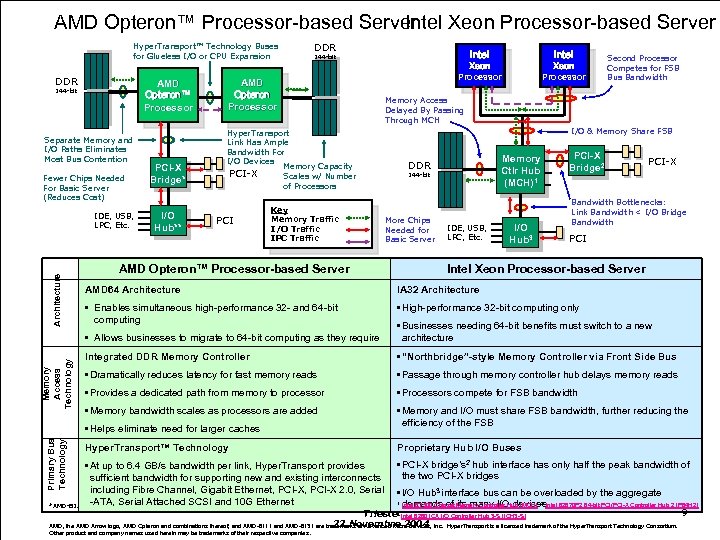

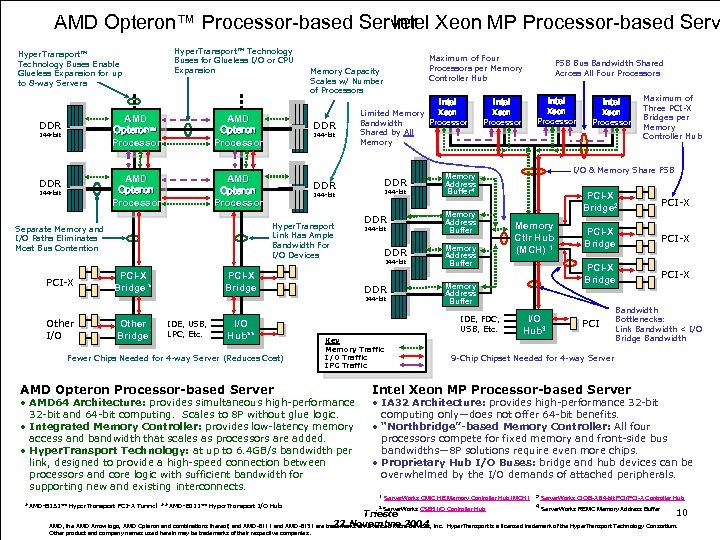

AMD Opteron™ Processor-based Server Intel Xeon Processor-based Server Hyper. Transport™ Technology Buses for Glueless I/O or CPU Expansion DDR AMD Opteron™ Processor 144 -bit Separate Memory and I/O Paths Eliminates Most Bus Contention Fewer Chips Needed For Basic Server (Reduces Cost) Architecture IDE, USB, LPC, Etc. PCI-X Bridge* I/O Hub** DDR Intel 144 -bit AMD Opteron Processor Xeon Processor Second Processor Competes for FSB Bus Bandwidth Memory Access Delayed By Passing Through MCH I/O & Memory Share FSB Hyper. Transport Link Has Ample Bandwidth For I/O Devices Memory Capacity PCI-X Scales w/ Number of Processors PCI Intel Xeon Processor Memory Ctlr Hub (MCH)1 DDR 144 -bit Key Memory Traffic I/O Traffic IPC Traffic More Chips Needed for Basic Server AMD Opteron™ Processor-based Server IDE, USB, LPC, Etc. I/O Hub 3 PCI-X Bridge 2 PCI-X Bandwidth Bottlenecks: Link Bandwidth < I/O Bridge Bandwidth PCI Intel Xeon Processor-based Server AMD 64 Architecture IA 32 Architecture • Enables simultaneous high-performance 32 - and 64 -bit computing • High-performance 32 -bit computing only Memory Access Technology • Allows businesses to migrate to 64 -bit computing as they require • Businesses needing 64 -bit benefits must switch to a new architecture Integrated DDR Memory Controller • “Northbridge”-style Memory Controller via Front Side Bus • Dramatically reduces latency for fast memory reads • Passage through memory controller hub delays memory reads • Provides a dedicated path from memory to processor • Processors compete for FSB bandwidth • Memory bandwidth scales as processors are added • Memory and I/O must share FSB bandwidth, further reducing the efficiency of the FSB Primary Bus Technology • Helps eliminate need for larger caches Hyper. Transport™ Technology Proprietary Hub I/O Buses • At up to 6. 4 GB/s bandwidth per link, Hyper. Transport provides sufficient bandwidth for supporting new and existing interconnects including Fibre Channel, Gigabit Ethernet, PCI-X 2. 0, Serial *AMD-8131™-ATA, Serial Attached**AMD-8111™ Hyper. Transport I/O Hub Hyper. Transport PCI-X Tunnel SCSI and 10 G Ethernet • PCI-X bridge’s 2 hub interface has only half the peak bandwidth of the two PCI-X bridges • I/O Hub 3 interface bus can be overloaded by the aggregate 1 demands of Memory Controller Hub (MCH) 2 Intel 82870 P 2 64 -bit PCI/PCI-X Controller Hub 2 (P 64 H 2) Intel E 7500 Chipset its many I/O devices Trieste 3 Intel 82801 CA I/O Controller Hub 3 -S (ICH 3 -S) 22 Novembre 2004 AMD, the AMD Arrow logo, AMD Opteron and combinations thereof, and AMD-8111 and AMD-8131 are trademarks of Advanced Micro Devices, Inc. Hyper. Transport is a licensed trademark of the Hyper. Transport Technology Consortium. Other product and company names used herein may be trademarks of their respective companies. 9

AMD Opteron™ Processor-based Server Xeon MP Processor-based Serv Intel Hyper. Transport™ Technology Buses Enable Glueless Expansion for up to 8 -way Servers Hyper. Transport™ Technology Buses for Glueless I/O or CPU Expansion Maximum of Four Processors per Memory Controller Hub Memory Capacity Scales w/ Number of Processors Intel AMD Opteron™ Processor 144 -bit DDR 144 -bit AMD Opteron Processor DDR AMD Opteron Processor 144 -bit PCI-X Bridge * DDR Hyper. Transport Link Has Ample Bandwidth For I/O Devices Separate Memory and I/O Paths Eliminates Most Bus Contention PCI-X DDR Xeon Limited Memory Processor Bandwidth Shared by All Memory DDR 144 -bit Other I/O Other Bridge IDE, USB, LPC, Etc. I/O Hub** Fewer Chips Needed for 4 -way Server (Reduces Cost) AMD Opteron Processor-based Server • AMD 64 Architecture: provides simultaneous high-performance 32 -bit and 64 -bit computing. Scales to 8 P without glue logic. • Integrated Memory Controller: provides low-latency memory access and bandwidth that scales as processors are added. • Hyper. Transport Technology: at up to 6. 4 GB/s bandwidth per link, designed to provide a high-speed connection between processors and core logic with sufficient bandwidth for supporting new and existing interconnects. Intel Xeon Processor Memory Address Buffer Maximum of Three PCI-X Bridges per Memory Controller Hub PCI-X Bridge 2 Memory Address Buffer I/O Hub 3 PCI-X Bridge Memory Ctlr Hub (MCH) 1 PCI-X PCI Bandwidth Bottlenecks: Link Bandwidth < I/O Bridge Bandwidth 9 -Chipset Needed for 4 -way Server Intel Xeon MP Processor-based Server • IA 32 Architecture: provides high-performance 32 -bit computing only—does not offer 64 -bit benefits. • “Northbridge”-based Memory Controller: All four processors compete for fixed memory and front-side bus bandwidths— 8 P solutions require even more chips. • Proprietary Hub I/O Buses: bridge and hub devices can be overwhelmed by the I/O demands of attached peripherals. 1 *AMD-8131™ Hyper. Transport PCI-X Tunnel **AMD-8111™ Hyper. Transport I/O Hub Intel Xeon Processor I/O & Memory Share FSB Memory Address Buffer 4 IDE, FDC, USB, Etc. Key Memory Traffic I/O Traffic IPC Traffic FSB Bus Bandwidth Shared Across All Four Processors Server. Works CMIC HE Memory Controller Hub (MCH) 3 Server. Works CSB 5 I/O Controller Hub Trieste 2 Server. Works CIOB-X 64 -bit PCI/PCI-X Controller Hub 4 Server. Works REMC Memory Address Buffer 10 22 Novembre 2004 AMD, the AMD Arrow logo, AMD Opteron and combinations thereof, and AMD-8111 and AMD-8131 are trademarks of Advanced Micro Devices, Inc. Hyper. Transport is a licensed trademark of the Hyper. Transport Technology Consortium. Other product and company names used herein may be trademarks of their respective companies.

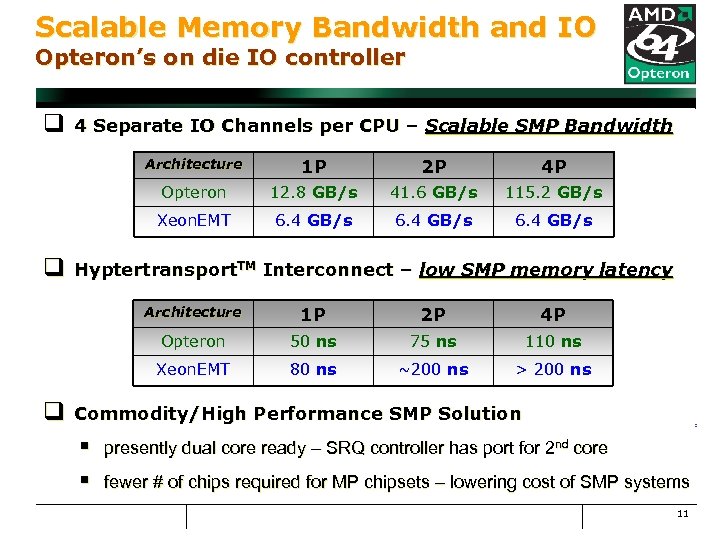

Scalable Memory Bandwidth and IO Opteron’s on die IO controller q 4 Separate IO Channels per CPU – Scalable SMP Bandwidth AMD Opteron™ Processor Server Intel Xeon MP Processor Server Hyper. Transport™ Technology Buses Enable Glueless Expansion for up to 8 -way Servers CPU 1 Hyper. Transport™ Technology Buses for Glueless I/O or CPU Expansion 12. 8 Xeon. EMT DDR 144 -bit q AMD Opteron Processor 6. 4 GB/s DDR 144 -bit 2 P 4 P 41. 6 GB/s 115. 2 GB/s Maximum of Four Processors per Memory Controller Hub Intel Xeon Limited Memory Processor Intel Xeon Processor 6. 4 GB/s FSB Bus Bandwidth Shared Across All Four Processors Intel Xeon Processor 6. 4 GB/s Maximum of Three PCI-X Bridges per Memory Controller Hub Bandwidth Shared by All Memory 25. 6 – 28. 8 Hyptertransport. TM Interconnect – low SMP memory latency GB/s DDR 144 -bit 6. 4 GB/s Separate Memory and I/O Paths Eliminates Most Bus Contention AMD Opteron DDR Processor Memory. Processor Architecture Dual channels Opteron to DDR Memory Xeon. EMT PCI-X Bridge * PCI-X q System GB/s Request Queue Memory Capacity Scales w/ Number of Processors Opteron AMD Opteron™ Processor CPU 0 1 P Architecture PCI-X Bridge DDR 144 -bit 1 P 50 ns Hyper. Transport Link Has Ample Bandwidth For I/O Devices DDR 144 -bit 2 P I/O & Memory Share FSB Memory Address Buffer CPU-CPU HT Link Memory Address Buffer 75 ns Memory Address Buffer 4 P PCI-X 110 ns Bridge Memory Ctlr Hub (MCH) DDR 1. 6 – 2. 0 GT/s ns 80 ns > 200 PCI-X 144 -bit Crossbar ~200 ns coherent DDR 144 -bit Bridge I/O § § IDE, USB, Other IO LPC, Etc. Bridge HT Link 1. 6 GT/s ready –Key SRQ controller non-coherent I/O Hub** presently dual core 6. 4 – 8. 0 PCI-X GB/s PCI-X Memory Address Buffer Commodity/High Performance SMP Solution Other 6. 4 GB/s PCI-X Bridge 2 I/O PCI Hub 3 Link CPU-CPU HT IDE, FDC, USB, Etc. has port for 2 nd Bandwidth Bottlenecks: Link Bandwidth < I/O Bridge Bandwidth 6. 4 – 8. 0 core GB/s Memory Traffic I/O Traffic IPC Traffic fewer # of chips required for MP chipsets – lowering cost of SMP systems 11

Speed up Opteron Architecture ACML – AMD’s superior equivalent of MKL Compilers – PGI performance enhancements 12

46057d7e9c894559096783d1d6a0529b.ppt