8f62d04d16fab12a41ea525fcfa18dba.ppt

- Количество слайдов: 40

SIMULAÇÃO DE CIRCUITOS Modelos de Simulações - SPICE E BSIM Leandro Manera e Jacobus W. Swart

SIMULAÇÃO DE CIRCUITOS Modelos de Simulações - SPICE E BSIM Leandro Manera e Jacobus W. Swart

APRESENTAÇÃO DOS MODELOS SPICE DE SIMULAÇÃO DE CIRCUITOS 1 - Tipos de modelos usados em simulações de circuitos 2 - Equações dos modelos e seus respectivos parâmetros 3 - Simulações de circuitos utilizando os modelos descritos 4 - Porta lógicas

APRESENTAÇÃO DOS MODELOS SPICE DE SIMULAÇÃO DE CIRCUITOS 1 - Tipos de modelos usados em simulações de circuitos 2 - Equações dos modelos e seus respectivos parâmetros 3 - Simulações de circuitos utilizando os modelos descritos 4 - Porta lógicas

1 - Nomes dos modelos Existem sete* tipos de modelos de dispositivos MOSFET. Portanto, dependendo da precisão desejada, temos: Level 1 - Shichman-Hodges model ou MOS 1 Level 2 - Geometry based - analytic model ou MOS 2 Level 3 - Semi-empirical, short channel model ou MOS 3 Level 4 - BSIM model Level 5 - EKV model (version 2. 6) Level 6 - BSIM 3 model (version 2) Level 7 - BSIM 3 model (version 3. 1) *Convém dizer que existem muitos outros tipos de modelos de dispositivos MOSFET, como exemplo podemos citar os modelos do simulador Hspice( Avant!), Spectre (Cadence) Eldo (Mentor Graphics) e outros. Esses modelos por sua vez são muito parecidos, alguma mudança pode ser notada apenas nomes dos parâmetros utilizado pelos modelos.

1 - Nomes dos modelos Existem sete* tipos de modelos de dispositivos MOSFET. Portanto, dependendo da precisão desejada, temos: Level 1 - Shichman-Hodges model ou MOS 1 Level 2 - Geometry based - analytic model ou MOS 2 Level 3 - Semi-empirical, short channel model ou MOS 3 Level 4 - BSIM model Level 5 - EKV model (version 2. 6) Level 6 - BSIM 3 model (version 2) Level 7 - BSIM 3 model (version 3. 1) *Convém dizer que existem muitos outros tipos de modelos de dispositivos MOSFET, como exemplo podemos citar os modelos do simulador Hspice( Avant!), Spectre (Cadence) Eldo (Mentor Graphics) e outros. Esses modelos por sua vez são muito parecidos, alguma mudança pode ser notada apenas nomes dos parâmetros utilizado pelos modelos.

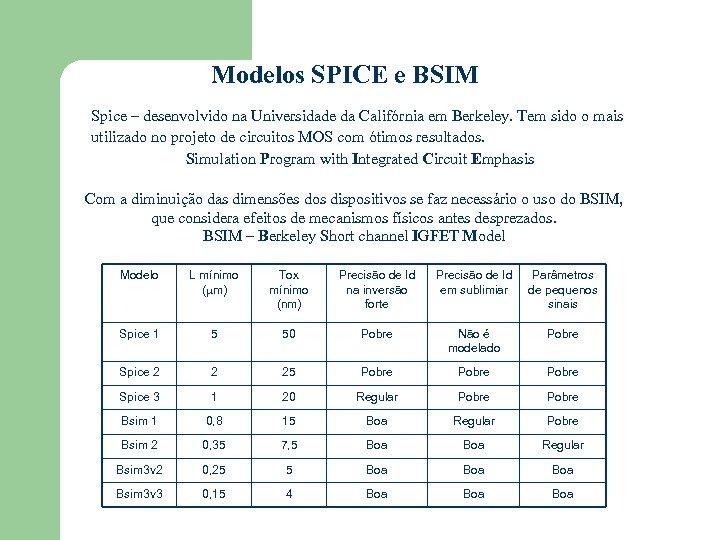

Modelos SPICE e BSIM Spice – desenvolvido na Universidade da Califórnia em Berkeley. Tem sido o mais utilizado no projeto de circuitos MOS com ótimos resultados. Simulation Program with Integrated Circuit Emphasis Com a diminuição das dimensões dos dispositivos se faz necessário o uso do BSIM, que considera efeitos de mecanismos físicos antes desprezados. BSIM – Berkeley Short channel IGFET Modelo L mínimo ( m) Tox mínimo (nm) Precisão de Id na inversão forte Precisão de Id em sublimiar Parâmetros de pequenos sinais Spice 1 5 50 Pobre Não é modelado Pobre Spice 2 2 25 Pobre Spice 3 1 20 Regular Pobre Bsim 1 0, 8 15 Boa Regular Pobre Bsim 2 0, 35 7, 5 Boa Regular Bsim 3 v 2 0, 25 5 Boa Boa Bsim 3 v 3 0, 15 4 Boa Boa

Modelos SPICE e BSIM Spice – desenvolvido na Universidade da Califórnia em Berkeley. Tem sido o mais utilizado no projeto de circuitos MOS com ótimos resultados. Simulation Program with Integrated Circuit Emphasis Com a diminuição das dimensões dos dispositivos se faz necessário o uso do BSIM, que considera efeitos de mecanismos físicos antes desprezados. BSIM – Berkeley Short channel IGFET Modelo L mínimo ( m) Tox mínimo (nm) Precisão de Id na inversão forte Precisão de Id em sublimiar Parâmetros de pequenos sinais Spice 1 5 50 Pobre Não é modelado Pobre Spice 2 2 25 Pobre Spice 3 1 20 Regular Pobre Bsim 1 0, 8 15 Boa Regular Pobre Bsim 2 0, 35 7, 5 Boa Regular Bsim 3 v 2 0, 25 5 Boa Boa Bsim 3 v 3 0, 15 4 Boa Boa

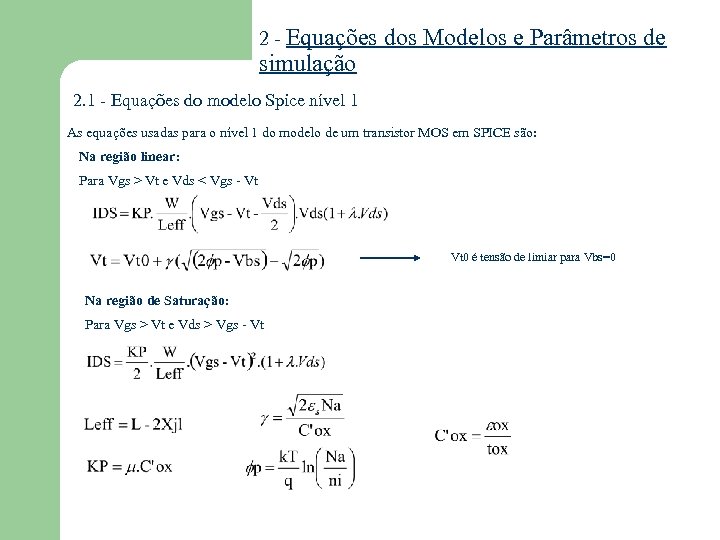

2 - Equações simulação dos Modelos e Parâmetros de 2. 1 - Equações do modelo Spice nível 1 As equações usadas para o nível 1 do modelo de um transistor MOS em SPICE são: Na região linear: Para Vgs > Vt e Vds < Vgs - Vt Vt 0 é tensão de limiar para Vbs=0 Na região de Saturação: Para Vgs > Vt e Vds > Vgs - Vt

2 - Equações simulação dos Modelos e Parâmetros de 2. 1 - Equações do modelo Spice nível 1 As equações usadas para o nível 1 do modelo de um transistor MOS em SPICE são: Na região linear: Para Vgs > Vt e Vds < Vgs - Vt Vt 0 é tensão de limiar para Vbs=0 Na região de Saturação: Para Vgs > Vt e Vds > Vgs - Vt

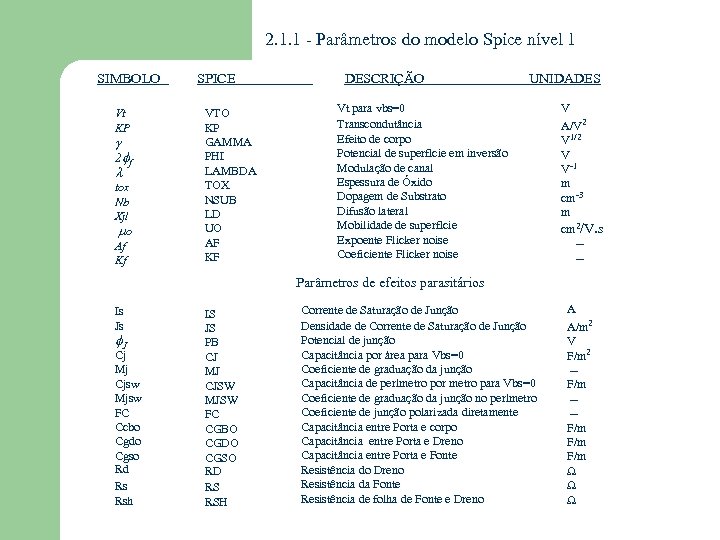

2. 1. 1 - Parâmetros do modelo Spice nível 1 SIMBOLO Vt KP 2 f tox Nb Xjl o Af Kf SPICE VTO KP GAMMA PHI LAMBDA TOX NSUB LD UO AF KF DESCRIÇÃO UNIDADES Vt para vbs=0 Transcondutância Efeito de corpo Potencial de superfície em inversão Modulação de canal Espessura de Óxido Dopagem de Substrato Difusão lateral Mobilidade de superfície Expoente Flicker noise Coeficiente Flicker noise V A/V 2 V 1/2 V V-1 m cm-3 m cm 2/V. s --- Parâmetros de efeitos parasitários Is Js J Cj Mj Cjsw Mjsw FC Ccbo Cgdo Cgso Rd Rs Rsh IS JS PB CJ MJ CJSW MJSW FC CGBO CGDO CGSO RD RS RSH Corrente de Saturação de Junção Densidade de Corrente de Saturação de Junção Potencial de junção Capacitância por área para Vbs=0 Coeficiente de graduação da junção Capacitância de perímetro por metro para Vbs=0 Coeficiente de graduação da junção no perímetro Coeficiente de junção polarizada diretamente Capacitância entre Porta e corpo Capacitância entre Porta e Dreno Capacitância entre Porta e Fonte Resistência do Dreno Resistência da Fonte Resistência de folha de Fonte e Dreno A A/m 2 V F/m 2 -F/m --F/m F/m

2. 1. 1 - Parâmetros do modelo Spice nível 1 SIMBOLO Vt KP 2 f tox Nb Xjl o Af Kf SPICE VTO KP GAMMA PHI LAMBDA TOX NSUB LD UO AF KF DESCRIÇÃO UNIDADES Vt para vbs=0 Transcondutância Efeito de corpo Potencial de superfície em inversão Modulação de canal Espessura de Óxido Dopagem de Substrato Difusão lateral Mobilidade de superfície Expoente Flicker noise Coeficiente Flicker noise V A/V 2 V 1/2 V V-1 m cm-3 m cm 2/V. s --- Parâmetros de efeitos parasitários Is Js J Cj Mj Cjsw Mjsw FC Ccbo Cgdo Cgso Rd Rs Rsh IS JS PB CJ MJ CJSW MJSW FC CGBO CGDO CGSO RD RS RSH Corrente de Saturação de Junção Densidade de Corrente de Saturação de Junção Potencial de junção Capacitância por área para Vbs=0 Coeficiente de graduação da junção Capacitância de perímetro por metro para Vbs=0 Coeficiente de graduação da junção no perímetro Coeficiente de junção polarizada diretamente Capacitância entre Porta e corpo Capacitância entre Porta e Dreno Capacitância entre Porta e Fonte Resistência do Dreno Resistência da Fonte Resistência de folha de Fonte e Dreno A A/m 2 V F/m 2 -F/m --F/m F/m

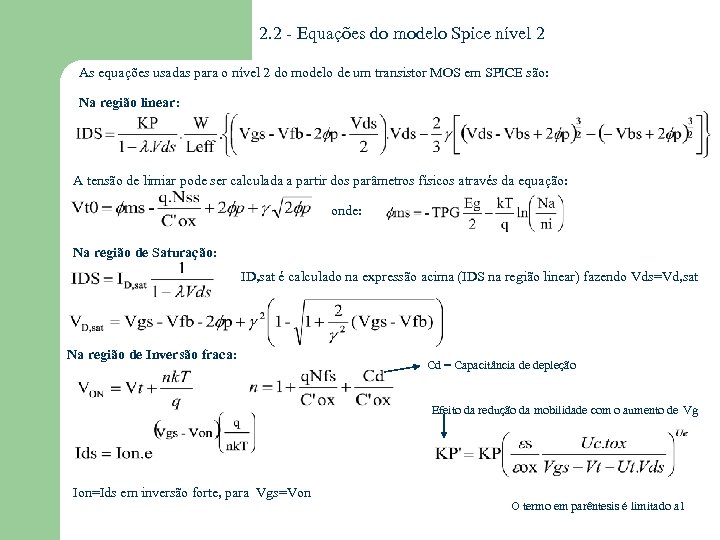

2. 2 - Equações do modelo Spice nível 2 As equações usadas para o nível 2 do modelo de um transistor MOS em SPICE são: Na região linear: A tensão de limiar pode ser calculada a partir dos parâmetros físicos através da equação: onde: Na região de Saturação: ID, sat é calculado na expressão acima (IDS na região linear) fazendo Vds=Vd, sat Na região de Inversão fraca: Cd = Capacitância de depleção Efeito da redução da mobilidade com o aumento de Vg Ion=Ids em inversão forte, para Vgs=Von O termo em parêntesis é limitado a 1

2. 2 - Equações do modelo Spice nível 2 As equações usadas para o nível 2 do modelo de um transistor MOS em SPICE são: Na região linear: A tensão de limiar pode ser calculada a partir dos parâmetros físicos através da equação: onde: Na região de Saturação: ID, sat é calculado na expressão acima (IDS na região linear) fazendo Vds=Vd, sat Na região de Inversão fraca: Cd = Capacitância de depleção Efeito da redução da mobilidade com o aumento de Vg Ion=Ids em inversão forte, para Vgs=Von O termo em parêntesis é limitado a 1

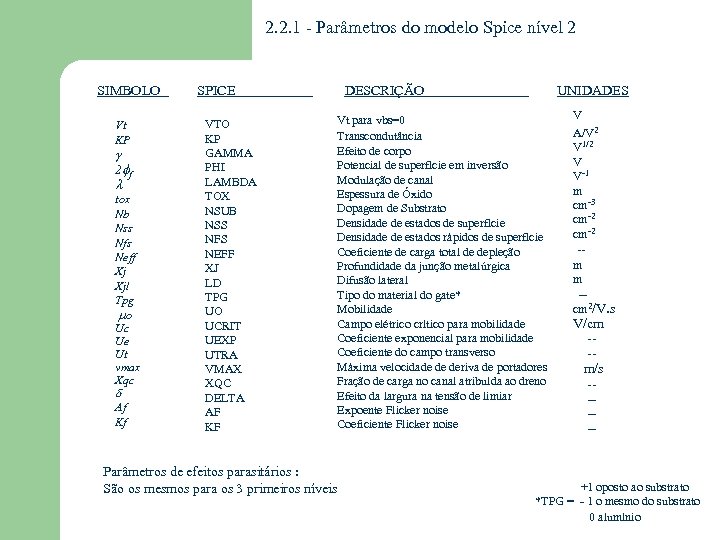

2. 2. 1 - Parâmetros do modelo Spice nível 2 SIMBOLO Vt KP 2 f tox Nb Nss Nfs Neff Xj Xjl Tpg o Uc Ue Ut vmax Xqc Af Kf SPICE VTO KP GAMMA PHI LAMBDA TOX NSUB NSS NFS NEFF XJ LD TPG UO UCRIT UEXP UTRA VMAX XQC DELTA AF KF DESCRIÇÃO UNIDADES Vt para vbs=0 Transcondutância Efeito de corpo Potencial de superfície em inversão Modulação de canal Espessura de Óxido Dopagem de Substrato Densidade de estados de superfície Densidade de estados rápidos de superfície Coeficiente de carga total de depleção Profundidade da junção metalúrgica Difusão lateral Tipo do material do gate* Mobilidade Campo elétrico crítico para mobilidade Coeficiente exponencial para mobilidade Coeficiente do campo transverso Máxima velocidade de deriva de portadores Fração de carga no canal atribuída ao dreno Efeito da largura na tensão de limiar Expoente Flicker noise Coeficiente Flicker noise Parâmetros de efeitos parasitários : São os mesmos para os 3 primeiros níveis V A/V 2 V 1/2 V V-1 m cm-3 cm-2 -m m -cm 2/V. s V/cm --m/s ----- +1 oposto ao substrato *TPG = - 1 o mesmo do substrato 0 alumínio

2. 2. 1 - Parâmetros do modelo Spice nível 2 SIMBOLO Vt KP 2 f tox Nb Nss Nfs Neff Xj Xjl Tpg o Uc Ue Ut vmax Xqc Af Kf SPICE VTO KP GAMMA PHI LAMBDA TOX NSUB NSS NFS NEFF XJ LD TPG UO UCRIT UEXP UTRA VMAX XQC DELTA AF KF DESCRIÇÃO UNIDADES Vt para vbs=0 Transcondutância Efeito de corpo Potencial de superfície em inversão Modulação de canal Espessura de Óxido Dopagem de Substrato Densidade de estados de superfície Densidade de estados rápidos de superfície Coeficiente de carga total de depleção Profundidade da junção metalúrgica Difusão lateral Tipo do material do gate* Mobilidade Campo elétrico crítico para mobilidade Coeficiente exponencial para mobilidade Coeficiente do campo transverso Máxima velocidade de deriva de portadores Fração de carga no canal atribuída ao dreno Efeito da largura na tensão de limiar Expoente Flicker noise Coeficiente Flicker noise Parâmetros de efeitos parasitários : São os mesmos para os 3 primeiros níveis V A/V 2 V 1/2 V V-1 m cm-3 cm-2 -m m -cm 2/V. s V/cm --m/s ----- +1 oposto ao substrato *TPG = - 1 o mesmo do substrato 0 alumínio

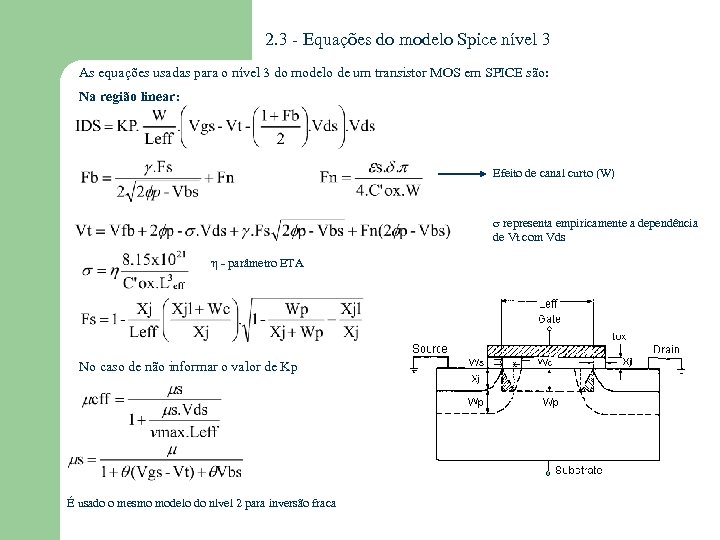

2. 3 - Equações do modelo Spice nível 3 As equações usadas para o nível 3 do modelo de um transistor MOS em SPICE são: Na região linear: Efeito de canal curto (W) representa empiricamente a dependência de Vt com Vds - parâmetro ETA No caso de não informar o valor de Kp É usado o mesmo modelo do nível 2 para inversão fraca

2. 3 - Equações do modelo Spice nível 3 As equações usadas para o nível 3 do modelo de um transistor MOS em SPICE são: Na região linear: Efeito de canal curto (W) representa empiricamente a dependência de Vt com Vds - parâmetro ETA No caso de não informar o valor de Kp É usado o mesmo modelo do nível 2 para inversão fraca

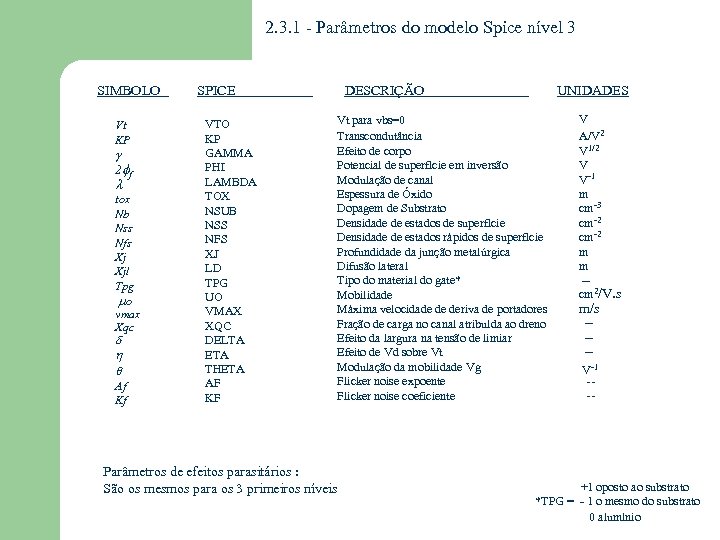

2. 3. 1 - Parâmetros do modelo Spice nível 3 SIMBOLO Vt KP 2 f tox Nb Nss Nfs Xj Xjl Tpg o vmax Xqc Af Kf SPICE VTO KP GAMMA PHI LAMBDA TOX NSUB NSS NFS XJ LD TPG UO VMAX XQC DELTA ETA THETA AF KF DESCRIÇÃO UNIDADES Vt para vbs=0 Transcondutância Efeito de corpo Potencial de superfície em inversão Modulação de canal Espessura de Óxido Dopagem de Substrato Densidade de estados de superfície Densidade de estados rápidos de superfície Profundidade da junção metalúrgica Difusão lateral Tipo do material do gate* Mobilidade Máxima velocidade de deriva de portadores Fração de carga no canal atribuída ao dreno Efeito da largura na tensão de limiar Efeito de Vd sobre Vt Modulação da mobilidade Vg Flicker noise expoente Flicker noise coeficiente Parâmetros de efeitos parasitários : São os mesmos para os 3 primeiros níveis V A/V 2 V 1/2 V V-1 m cm-3 cm-2 m m -cm 2/V. s m/s ---- V-1 --- +1 oposto ao substrato *TPG = - 1 o mesmo do substrato 0 alumínio

2. 3. 1 - Parâmetros do modelo Spice nível 3 SIMBOLO Vt KP 2 f tox Nb Nss Nfs Xj Xjl Tpg o vmax Xqc Af Kf SPICE VTO KP GAMMA PHI LAMBDA TOX NSUB NSS NFS XJ LD TPG UO VMAX XQC DELTA ETA THETA AF KF DESCRIÇÃO UNIDADES Vt para vbs=0 Transcondutância Efeito de corpo Potencial de superfície em inversão Modulação de canal Espessura de Óxido Dopagem de Substrato Densidade de estados de superfície Densidade de estados rápidos de superfície Profundidade da junção metalúrgica Difusão lateral Tipo do material do gate* Mobilidade Máxima velocidade de deriva de portadores Fração de carga no canal atribuída ao dreno Efeito da largura na tensão de limiar Efeito de Vd sobre Vt Modulação da mobilidade Vg Flicker noise expoente Flicker noise coeficiente Parâmetros de efeitos parasitários : São os mesmos para os 3 primeiros níveis V A/V 2 V 1/2 V V-1 m cm-3 cm-2 m m -cm 2/V. s m/s ---- V-1 --- +1 oposto ao substrato *TPG = - 1 o mesmo do substrato 0 alumínio

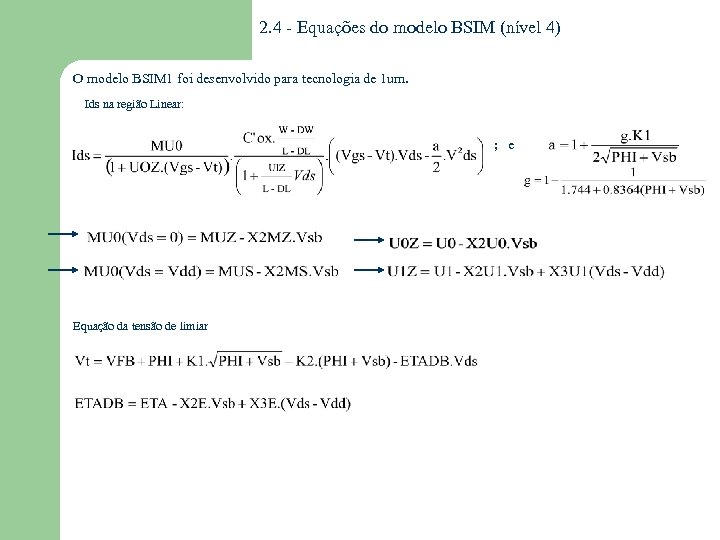

2. 4 - Equações do modelo BSIM (nível 4) O modelo BSIM 1 foi desenvolvido para tecnologia de 1 um. Ids na região Linear: ; e Equação da tensão de limiar

2. 4 - Equações do modelo BSIM (nível 4) O modelo BSIM 1 foi desenvolvido para tecnologia de 1 um. Ids na região Linear: ; e Equação da tensão de limiar

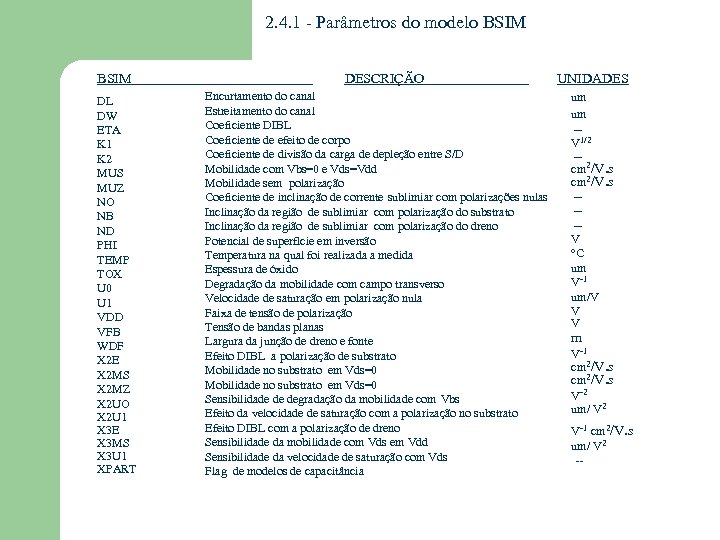

2. 4. 1 - Parâmetros do modelo BSIM DL DW ETA K 1 K 2 MUS MUZ NO NB ND PHI TEMP TOX U 0 U 1 VDD VFB WDF X 2 E X 2 MS X 2 MZ X 2 UO X 2 U 1 X 3 E X 3 MS X 3 U 1 XPART DESCRIÇÃO Encurtamento do canal Estreitamento do canal Coeficiente DIBL Coeficiente de efeito de corpo Coeficiente de divisão da carga de depleção entre S/D Mobilidade com Vbs=0 e Vds=Vdd Mobilidade sem polarização Coeficiente de inclinação de corrente sublimiar com polarizações nulas Inclinação da região de sublimiar com polarização do substrato Inclinação da região de sublimiar com polarização do dreno Potencial de superfície em inversão Temperatura na qual foi realizada a medida Espessura de óxido Degradação da mobilidade com campo transverso Velocidade de saturação em polarização nula Faixa de tensão de polarização Tensão de bandas planas Largura da junção de dreno e fonte Efeito DIBL a polarização de substrato Mobilidade no substrato em Vds=0 Sensibilidade de degradação da mobilidade com Vbs Efeito da velocidade de saturação com a polarização no substrato Efeito DIBL com a polarização de dreno Sensibilidade da mobilidade com Vds em Vdd Sensibilidade da velocidade de saturação com Vds Flag de modelos de capacitância UNIDADES um um -V 1/2 -cm 2/V. s ---V C um V-1 um/V V V m V-1 cm 2/V. s V-2 um/ V 2 V-1 cm 2/V. s um/ V 2 --

2. 4. 1 - Parâmetros do modelo BSIM DL DW ETA K 1 K 2 MUS MUZ NO NB ND PHI TEMP TOX U 0 U 1 VDD VFB WDF X 2 E X 2 MS X 2 MZ X 2 UO X 2 U 1 X 3 E X 3 MS X 3 U 1 XPART DESCRIÇÃO Encurtamento do canal Estreitamento do canal Coeficiente DIBL Coeficiente de efeito de corpo Coeficiente de divisão da carga de depleção entre S/D Mobilidade com Vbs=0 e Vds=Vdd Mobilidade sem polarização Coeficiente de inclinação de corrente sublimiar com polarizações nulas Inclinação da região de sublimiar com polarização do substrato Inclinação da região de sublimiar com polarização do dreno Potencial de superfície em inversão Temperatura na qual foi realizada a medida Espessura de óxido Degradação da mobilidade com campo transverso Velocidade de saturação em polarização nula Faixa de tensão de polarização Tensão de bandas planas Largura da junção de dreno e fonte Efeito DIBL a polarização de substrato Mobilidade no substrato em Vds=0 Sensibilidade de degradação da mobilidade com Vbs Efeito da velocidade de saturação com a polarização no substrato Efeito DIBL com a polarização de dreno Sensibilidade da mobilidade com Vds em Vdd Sensibilidade da velocidade de saturação com Vds Flag de modelos de capacitância UNIDADES um um -V 1/2 -cm 2/V. s ---V C um V-1 um/V V V m V-1 cm 2/V. s V-2 um/ V 2 V-1 cm 2/V. s um/ V 2 --

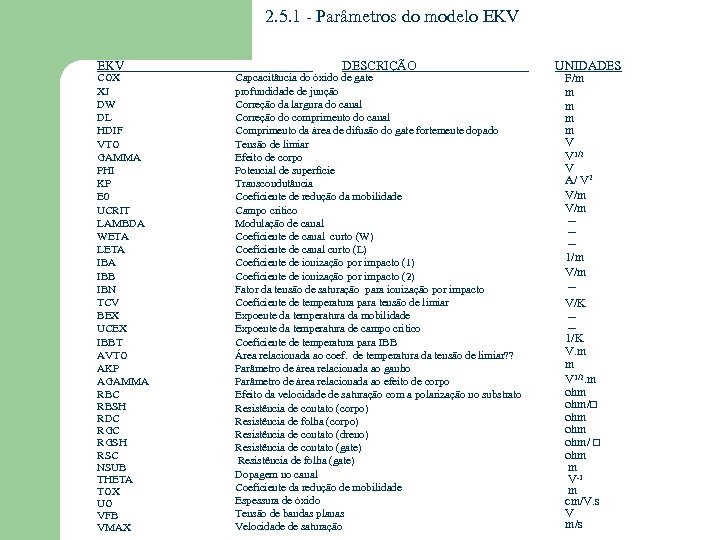

2. 5. 1 - Parâmetros do modelo EKV COX XJ DW DL HDIF VTO GAMMA PHI KP E 0 UCRIT LAMBDA WETA LETA IBB IBN TCV BEX UCEX IBBT AVTO AKP AGAMMA RBC RBSH RDC RGSH RSC NSUB THETA TOX UO VFB VMAX DESCRIÇÃO Capcacitância do óxido de gate profundidade de junção Correção da largura do canal Correção do comprimento do canal Comprimento da área de difusão do gate fortemente dopado Tensão de limiar Efeito de corpo Potencial de superfície Transcondutância Coeficiente de redução da mobilidade Campo critico Modulação de canal Coeficiente de canal curto (W) Coeficiente de canal curto (L) Coeficiente de ionização por impacto (1) Coeficiente de ionização por impacto (2) Fator da tensão de saturação para ionização por impacto Coeficiente de temperatura para tensão de limiar Expoente da temperatura da mobilidade Expoente da temperatura de campo critico Coeficiente de temperatura para IBB Área relacionada ao coef. de temperatura da tensão de limiar? ? Parâmetro de área relacionada ao ganho Parâmetro de área relacionada ao efeito de corpo Efeito da velocidade de saturação com a polarização no substrato Resistência de contato (corpo) Resistência de folha (corpo) Resistência de contato (dreno) Resistência de contato (gate) Resistência de folha (gate) Dopagem no canal Coeficiente da redução de mobilidade Espessura de óxido Tensão de bandas planas Velocidade de saturação UNIDADES F/m m m V V 1/2 V A/ V 2 V/m ---1/m V/m -V/K --1/K V. m m V 1/2. m ohm/ ohm ohm/ ohm m V-1 m cm/V. s V m/s

2. 5. 1 - Parâmetros do modelo EKV COX XJ DW DL HDIF VTO GAMMA PHI KP E 0 UCRIT LAMBDA WETA LETA IBB IBN TCV BEX UCEX IBBT AVTO AKP AGAMMA RBC RBSH RDC RGSH RSC NSUB THETA TOX UO VFB VMAX DESCRIÇÃO Capcacitância do óxido de gate profundidade de junção Correção da largura do canal Correção do comprimento do canal Comprimento da área de difusão do gate fortemente dopado Tensão de limiar Efeito de corpo Potencial de superfície Transcondutância Coeficiente de redução da mobilidade Campo critico Modulação de canal Coeficiente de canal curto (W) Coeficiente de canal curto (L) Coeficiente de ionização por impacto (1) Coeficiente de ionização por impacto (2) Fator da tensão de saturação para ionização por impacto Coeficiente de temperatura para tensão de limiar Expoente da temperatura da mobilidade Expoente da temperatura de campo critico Coeficiente de temperatura para IBB Área relacionada ao coef. de temperatura da tensão de limiar? ? Parâmetro de área relacionada ao ganho Parâmetro de área relacionada ao efeito de corpo Efeito da velocidade de saturação com a polarização no substrato Resistência de contato (corpo) Resistência de folha (corpo) Resistência de contato (dreno) Resistência de contato (gate) Resistência de folha (gate) Dopagem no canal Coeficiente da redução de mobilidade Espessura de óxido Tensão de bandas planas Velocidade de saturação UNIDADES F/m m m V V 1/2 V A/ V 2 V/m ---1/m V/m -V/K --1/K V. m m V 1/2. m ohm/ ohm ohm/ ohm m V-1 m cm/V. s V m/s

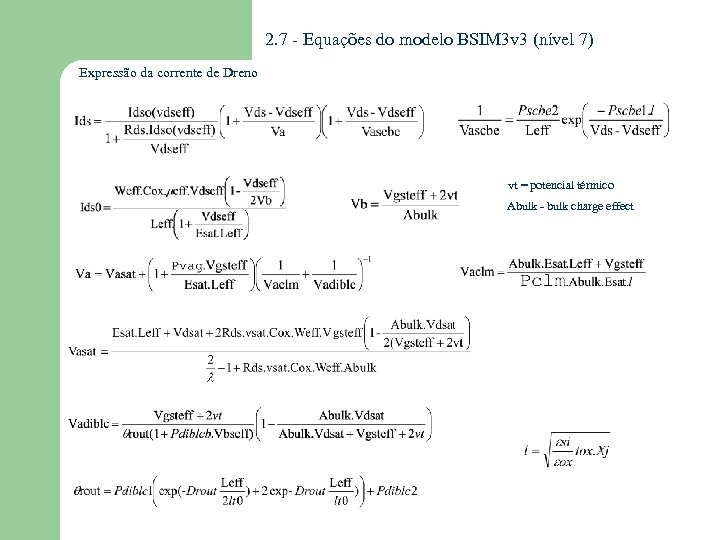

2. 7 - Equações do modelo BSIM 3 v 3 (nível 7) Expressão da corrente de Dreno vt = potencial térmico Abulk - bulk charge effect

2. 7 - Equações do modelo BSIM 3 v 3 (nível 7) Expressão da corrente de Dreno vt = potencial térmico Abulk - bulk charge effect

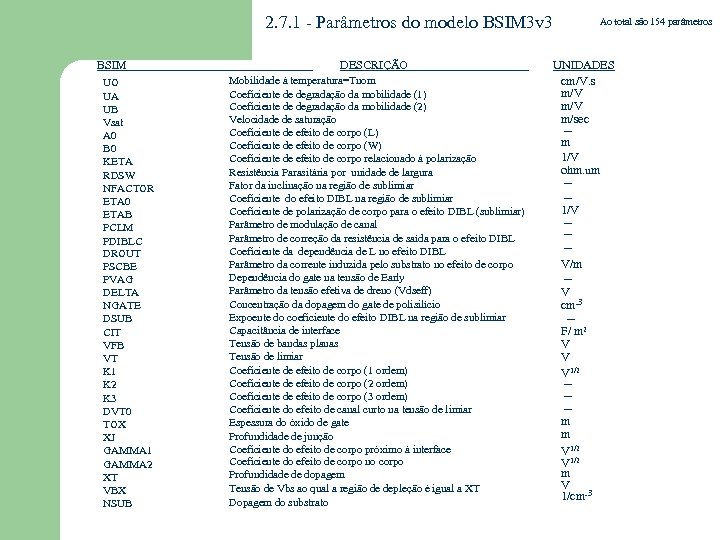

2. 7. 1 - Parâmetros do modelo BSIM 3 v 3 BSIM UO UA UB Vsat A 0 B 0 KETA RDSW NFACTOR ETA 0 ETAB PCLM PDIBLC DROUT PSCBE PVAG DELTA NGATE DSUB CIT VFB VT K 1 K 2 K 3 DVT 0 TOX XJ GAMMA 1 GAMMA 2 XT VBX NSUB DESCRIÇÃO Mobilidade à temperatura=Tnom Coeficiente de degradação da mobilidade (1) Coeficiente de degradação da mobilidade (2) Velocidade de saturação Coeficiente de efeito de corpo (L) Coeficiente de efeito de corpo (W) Coeficiente de efeito de corpo relacionado à polarização Resistência Parasitária por unidade de largura Fator da inclinação na região de sublimiar Coeficiente do efeito DIBL na região de sublimiar Coeficiente de polarização de corpo para o efeito DIBL (sublimiar) Parâmetro de modulação de canal Parâmetro de correção da resistência de saída para o efeito DIBL Coeficiente da dependência de L no efeito DIBL Parâmetro da corrente induzida pelo substrato no efeito de corpo Dependência do gate na tensão de Early Parâmetro da tensão efetiva de dreno (Vdseff) Concentração da dopagem do gate de polisilício Expoente do coeficiente do efeito DIBL na região de sublimiar Capacitância de interface Tensão de bandas planas Tensão de limiar Coeficiente de efeito de corpo (1 ordem) Coeficiente de efeito de corpo (2 ordem) Coeficiente de efeito de corpo (3 ordem) Coeficiente do efeito de canal curto na tensão de limiar Espessura do óxido de gate Profundidade de junção Coeficiente do efeito de corpo próximo à interface Coeficiente do efeito de corpo no corpo Profundidade de dopagem Tensão de Vbs ao qual a região de depleção é igual a XT Dopagem do substrato Ao total são 154 parâmetros UNIDADES cm/V. s m/V m/sec -m 1/V ohm. um --1/V ---V/m -V cm-3 -F/ m 2 V V V 1/2 ---m m V 1/2 m V 1/cm-3

2. 7. 1 - Parâmetros do modelo BSIM 3 v 3 BSIM UO UA UB Vsat A 0 B 0 KETA RDSW NFACTOR ETA 0 ETAB PCLM PDIBLC DROUT PSCBE PVAG DELTA NGATE DSUB CIT VFB VT K 1 K 2 K 3 DVT 0 TOX XJ GAMMA 1 GAMMA 2 XT VBX NSUB DESCRIÇÃO Mobilidade à temperatura=Tnom Coeficiente de degradação da mobilidade (1) Coeficiente de degradação da mobilidade (2) Velocidade de saturação Coeficiente de efeito de corpo (L) Coeficiente de efeito de corpo (W) Coeficiente de efeito de corpo relacionado à polarização Resistência Parasitária por unidade de largura Fator da inclinação na região de sublimiar Coeficiente do efeito DIBL na região de sublimiar Coeficiente de polarização de corpo para o efeito DIBL (sublimiar) Parâmetro de modulação de canal Parâmetro de correção da resistência de saída para o efeito DIBL Coeficiente da dependência de L no efeito DIBL Parâmetro da corrente induzida pelo substrato no efeito de corpo Dependência do gate na tensão de Early Parâmetro da tensão efetiva de dreno (Vdseff) Concentração da dopagem do gate de polisilício Expoente do coeficiente do efeito DIBL na região de sublimiar Capacitância de interface Tensão de bandas planas Tensão de limiar Coeficiente de efeito de corpo (1 ordem) Coeficiente de efeito de corpo (2 ordem) Coeficiente de efeito de corpo (3 ordem) Coeficiente do efeito de canal curto na tensão de limiar Espessura do óxido de gate Profundidade de junção Coeficiente do efeito de corpo próximo à interface Coeficiente do efeito de corpo no corpo Profundidade de dopagem Tensão de Vbs ao qual a região de depleção é igual a XT Dopagem do substrato Ao total são 154 parâmetros UNIDADES cm/V. s m/V m/sec -m 1/V ohm. um --1/V ---V/m -V cm-3 -F/ m 2 V V V 1/2 ---m m V 1/2 m V 1/cm-3

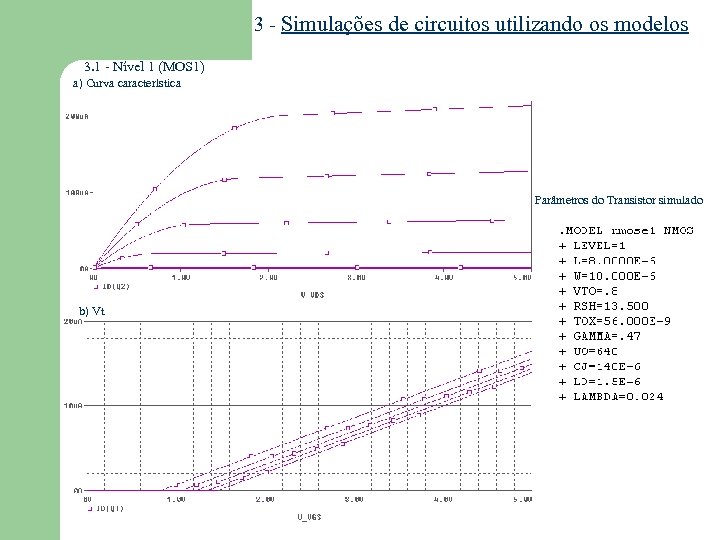

3 - Simulações de circuitos utilizando os modelos 3. 1 - Nível 1 (MOS 1) a) Curva característica Parâmetros do Transistor simulado b) Vt

3 - Simulações de circuitos utilizando os modelos 3. 1 - Nível 1 (MOS 1) a) Curva característica Parâmetros do Transistor simulado b) Vt

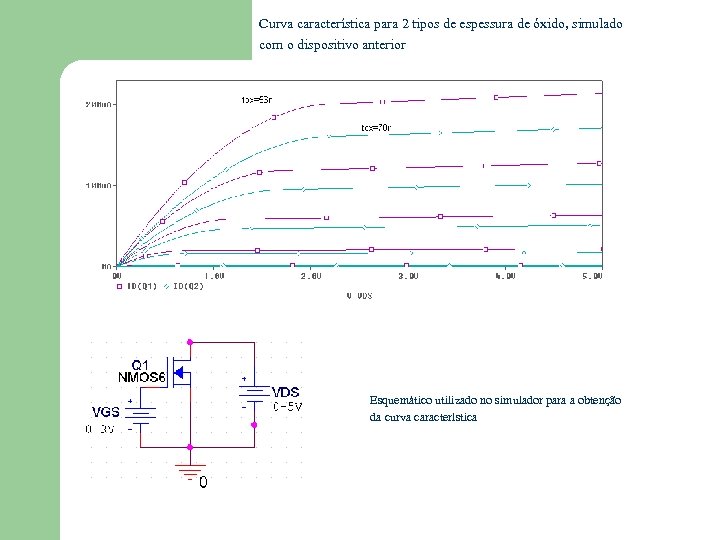

Curva característica para 2 tipos de espessura de óxido, simulado com o dispositivo anterior Esquemático utilizado no simulador para a obtenção da curva característica

Curva característica para 2 tipos de espessura de óxido, simulado com o dispositivo anterior Esquemático utilizado no simulador para a obtenção da curva característica

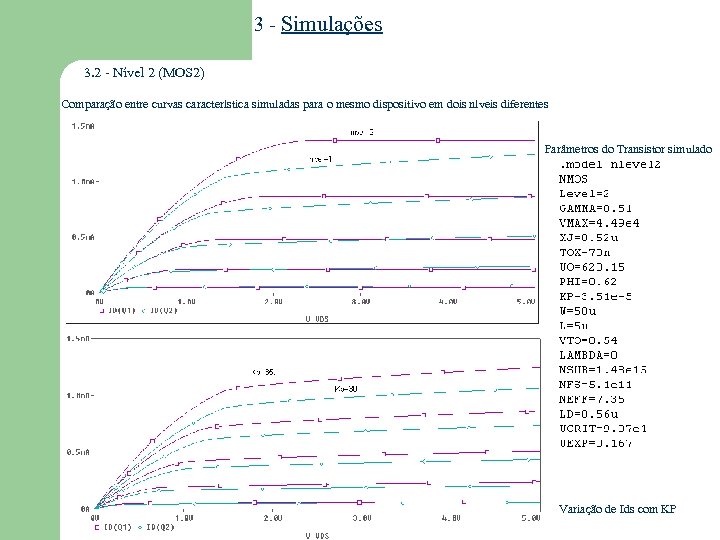

3 - Simulações 3. 2 - Nível 2 (MOS 2) Comparação entre curvas característica simuladas para o mesmo dispositivo em dois níveis diferentes Parâmetros do Transistor simulado Variação de Ids com KP

3 - Simulações 3. 2 - Nível 2 (MOS 2) Comparação entre curvas característica simuladas para o mesmo dispositivo em dois níveis diferentes Parâmetros do Transistor simulado Variação de Ids com KP

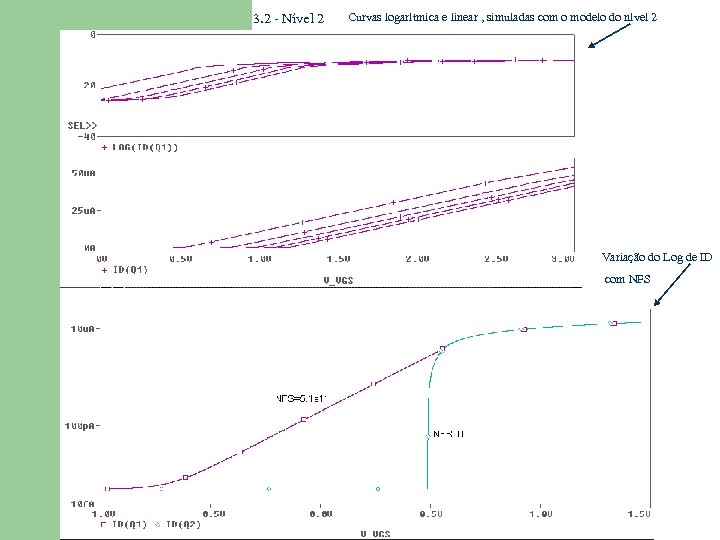

3. 2 - Nível 2 Curvas logarítmica e linear , simuladas com o modelo do nível 2 Variação do Log de ID com NFS

3. 2 - Nível 2 Curvas logarítmica e linear , simuladas com o modelo do nível 2 Variação do Log de ID com NFS

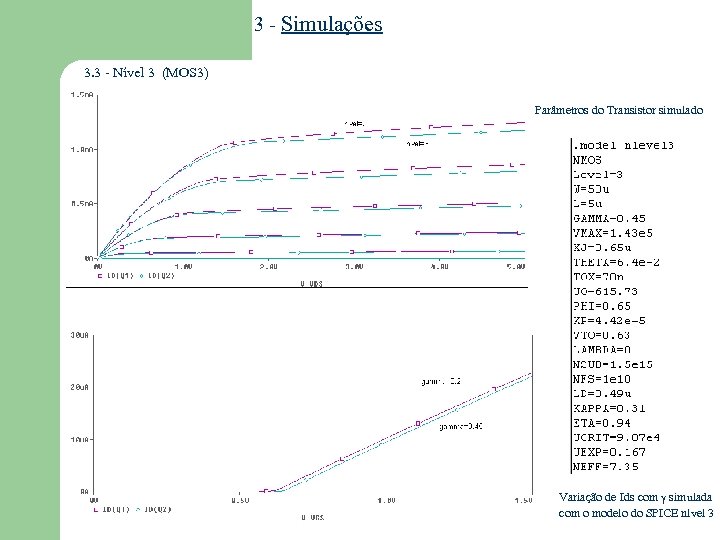

3 - Simulações 3. 3 - Nível 3 (MOS 3) Parâmetros do Transistor simulado Variação de Ids com simulada com o modelo do SPICE nível 3

3 - Simulações 3. 3 - Nível 3 (MOS 3) Parâmetros do Transistor simulado Variação de Ids com simulada com o modelo do SPICE nível 3

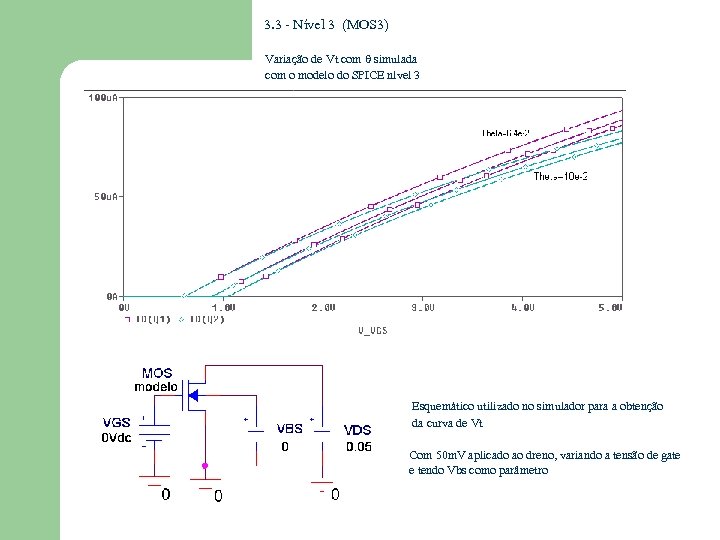

3. 3 - Nível 3 (MOS 3) Variação de Vt com simulada com o modelo do SPICE nível 3 Esquemático utilizado no simulador para a obtenção da curva de Vt Com 50 m. V aplicado ao dreno, variando a tensão de gate e tendo Vbs como parâmetro

3. 3 - Nível 3 (MOS 3) Variação de Vt com simulada com o modelo do SPICE nível 3 Esquemático utilizado no simulador para a obtenção da curva de Vt Com 50 m. V aplicado ao dreno, variando a tensão de gate e tendo Vbs como parâmetro

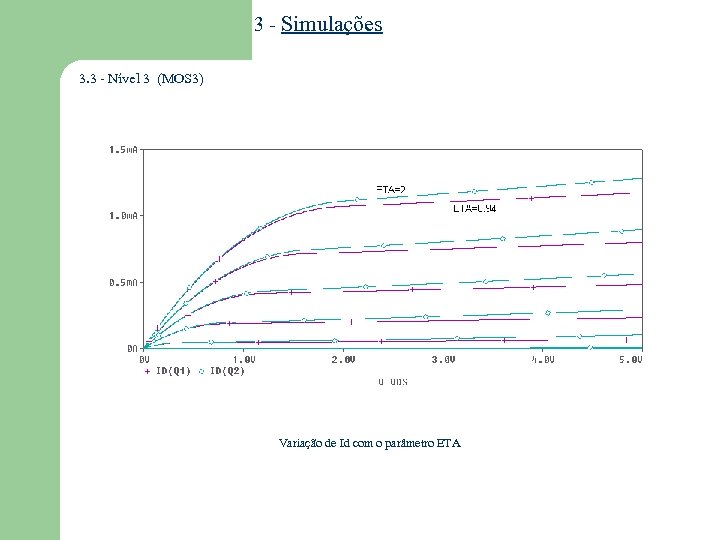

3 - Simulações 3. 3 - Nível 3 (MOS 3) Variação de Id com o parâmetro ETA

3 - Simulações 3. 3 - Nível 3 (MOS 3) Variação de Id com o parâmetro ETA

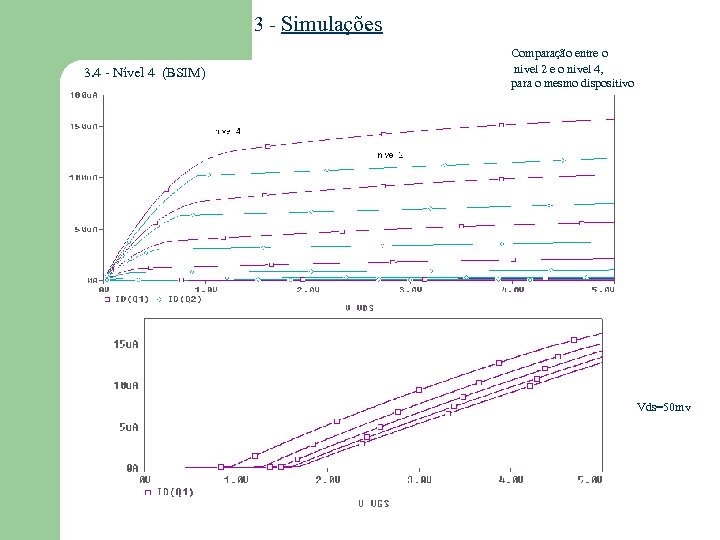

3 - Simulações 3. 4 - Nível 4 (BSIM) Comparação entre o nivel 2 e o nivel 4, para o mesmo dispositivo Vds=50 mv

3 - Simulações 3. 4 - Nível 4 (BSIM) Comparação entre o nivel 2 e o nivel 4, para o mesmo dispositivo Vds=50 mv

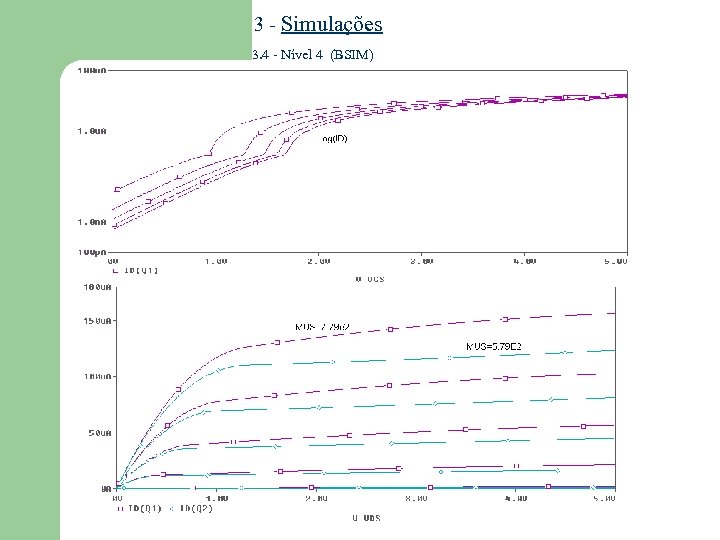

3 - Simulações 3. 4 - Nível 4 (BSIM)

3 - Simulações 3. 4 - Nível 4 (BSIM)

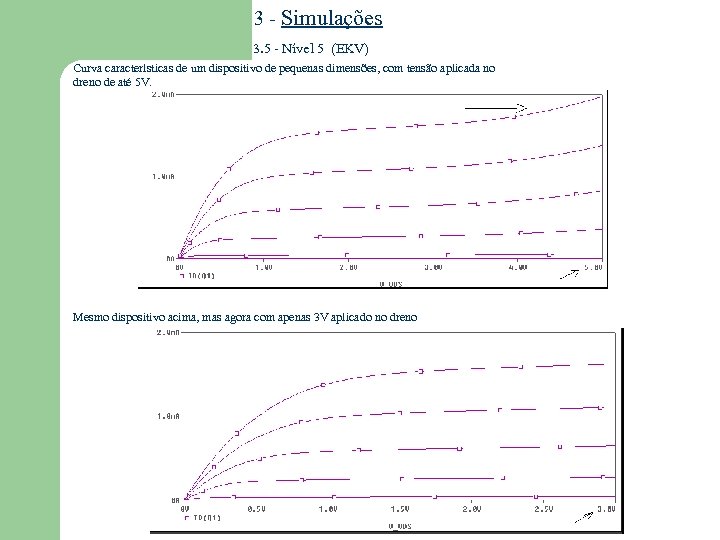

3 - Simulações 3. 5 - Nível 5 (EKV) Curva características de um dispositivo de pequenas dimensões, com tensão aplicada no dreno de até 5 V. Mesmo dispositivo acima, mas agora com apenas 3 V aplicado no dreno

3 - Simulações 3. 5 - Nível 5 (EKV) Curva características de um dispositivo de pequenas dimensões, com tensão aplicada no dreno de até 5 V. Mesmo dispositivo acima, mas agora com apenas 3 V aplicado no dreno

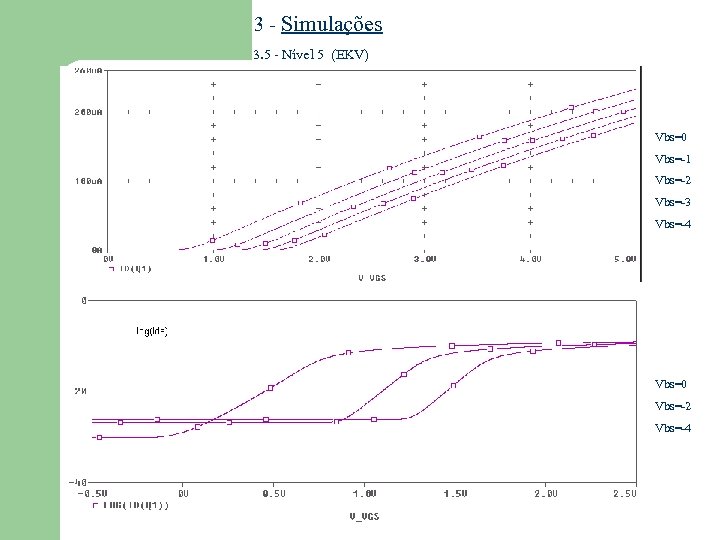

3 - Simulações 3. 5 - Nível 5 (EKV) Vbs=0 Vbs=-1 Vbs=-2 Vbs=-3 Vbs=-4 Vbs=0 Vbs=-2 Vbs=-4

3 - Simulações 3. 5 - Nível 5 (EKV) Vbs=0 Vbs=-1 Vbs=-2 Vbs=-3 Vbs=-4 Vbs=0 Vbs=-2 Vbs=-4

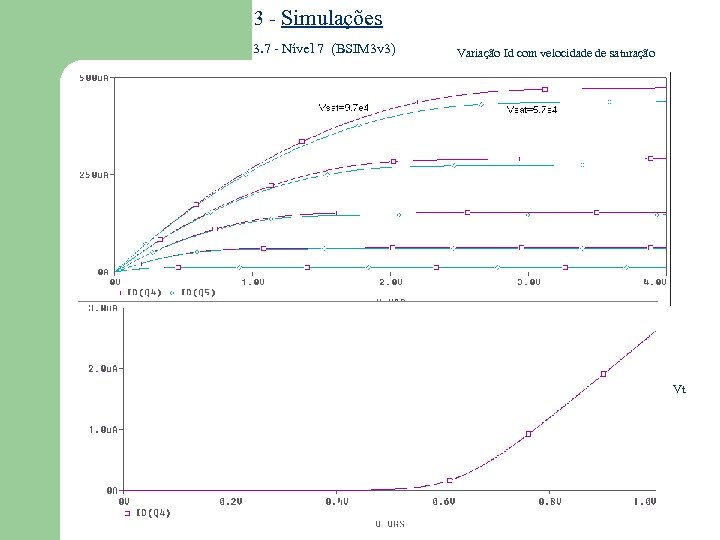

3 - Simulações 3. 7 - Nível 7 (BSIM 3 v 3) Variação Id com velocidade de saturação Vt

3 - Simulações 3. 7 - Nível 7 (BSIM 3 v 3) Variação Id com velocidade de saturação Vt

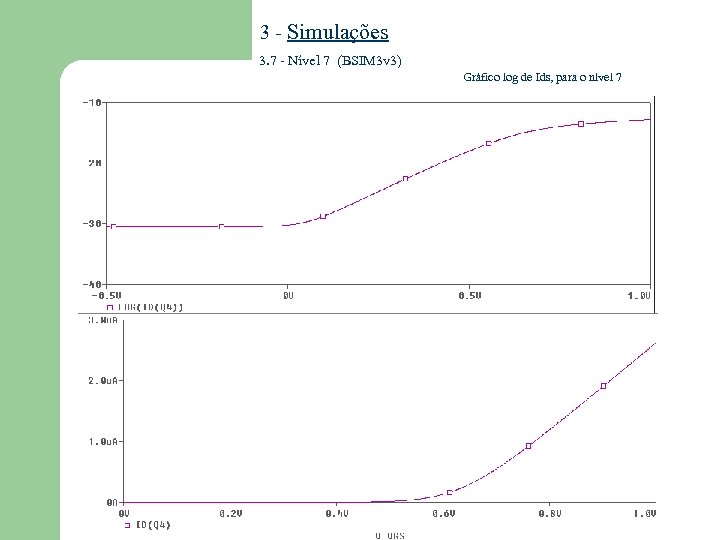

3 - Simulações 3. 7 - Nível 7 (BSIM 3 v 3) Gráfico log de Ids, para o nível 7

3 - Simulações 3. 7 - Nível 7 (BSIM 3 v 3) Gráfico log de Ids, para o nível 7

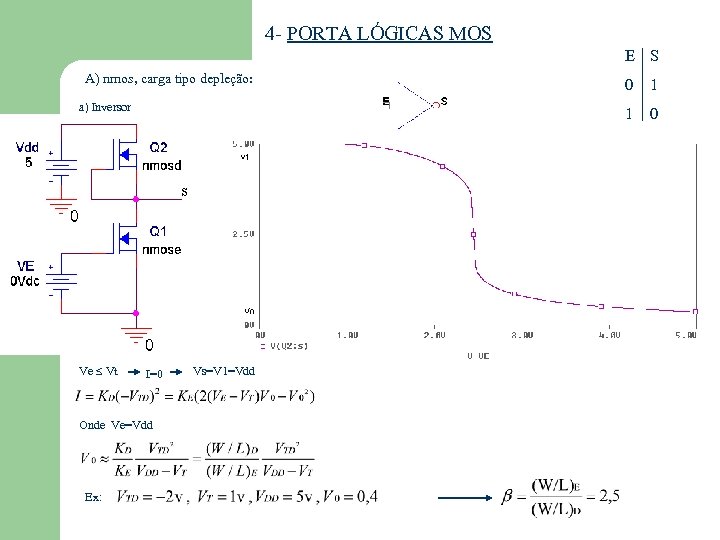

4 - PORTA LÓGICAS MOS E S A) nmos, carga tipo depleção: Ve Vt I=0 Onde Ve=Vdd Ex: Vs=V 1=Vdd 1 1 a) Inversor 0 0

4 - PORTA LÓGICAS MOS E S A) nmos, carga tipo depleção: Ve Vt I=0 Onde Ve=Vdd Ex: Vs=V 1=Vdd 1 1 a) Inversor 0 0

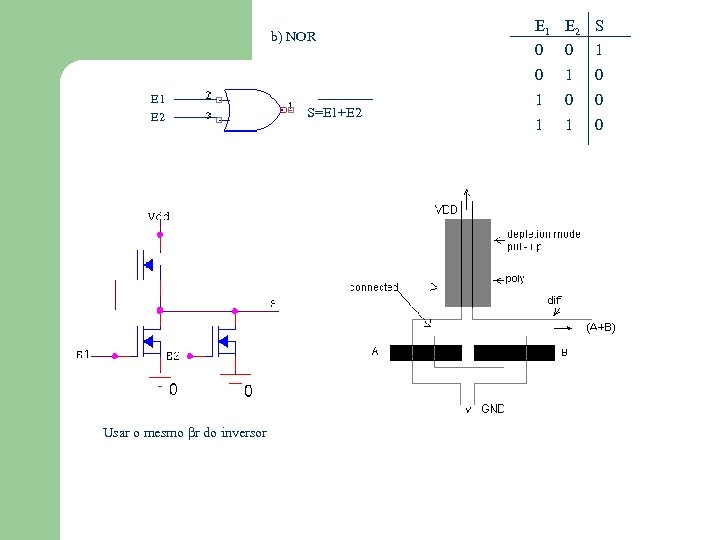

b) NOR E 1 E 2 S Usar o mesmo r do inversor S=E 1+E 2 0 1 0 E 1 E 2 0 1 0 0 1 1 0

b) NOR E 1 E 2 S Usar o mesmo r do inversor S=E 1+E 2 0 1 0 E 1 E 2 0 1 0 0 1 1 0

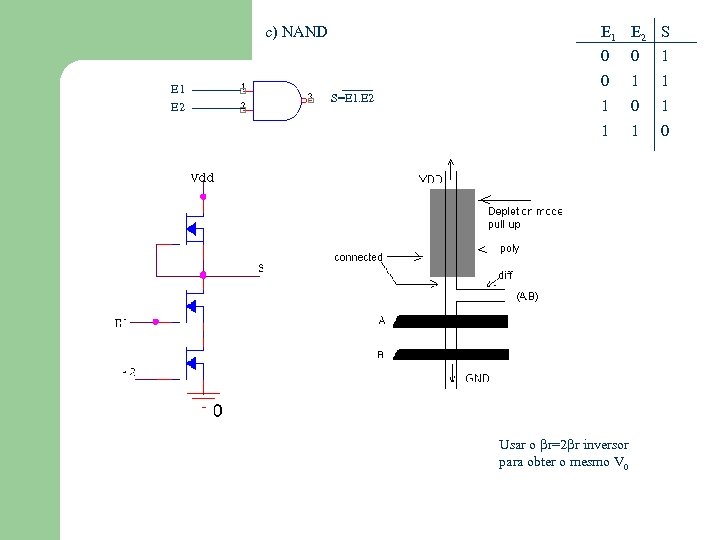

E 1 E 2 S c) NAND 0 E 1 E 2 1 0 S=E 1. E 2 0 1 1 1 0 Usar o r=2 r inversor para obter o mesmo V 0

E 1 E 2 S c) NAND 0 E 1 E 2 1 0 S=E 1. E 2 0 1 1 1 0 Usar o r=2 r inversor para obter o mesmo V 0

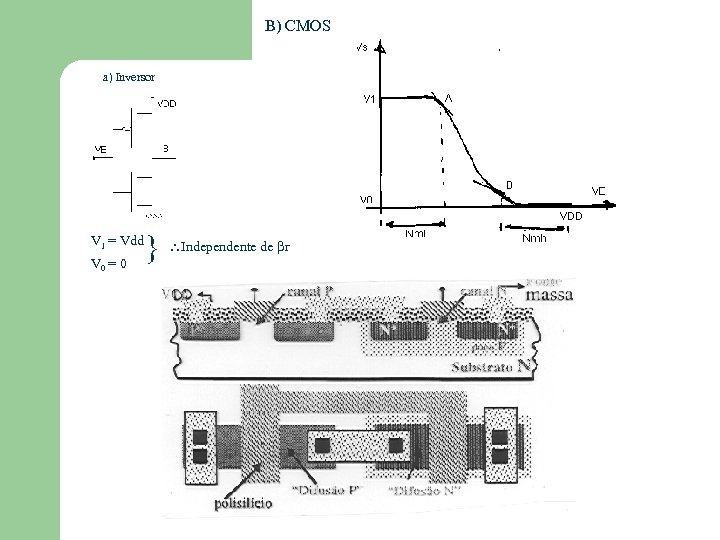

B) CMOS a) Inversor V 1 = Vdd V 0 = 0 } Independente de r

B) CMOS a) Inversor V 1 = Vdd V 0 = 0 } Independente de r

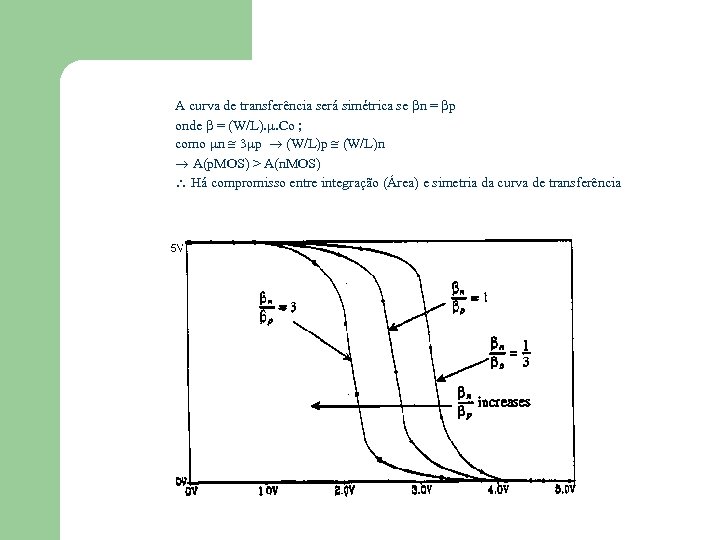

A curva de transferência será simétrica se n = p onde = (W/L). . Co ; como n 3 p (W/L)n A(p. MOS) > A(n. MOS) Há compromisso entre integração (Área) e simetria da curva de transferência

A curva de transferência será simétrica se n = p onde = (W/L). . Co ; como n 3 p (W/L)n A(p. MOS) > A(n. MOS) Há compromisso entre integração (Área) e simetria da curva de transferência

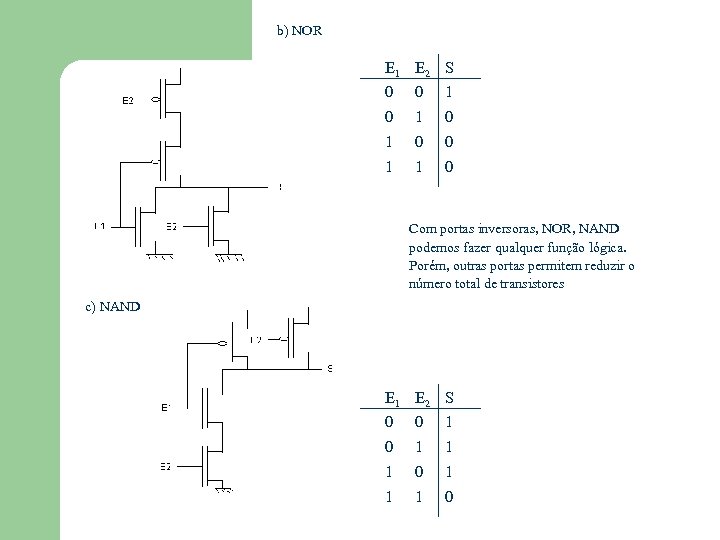

b) NOR E 1 E 2 S 0 0 1 0 1 0 0 1 1 0 Com portas inversoras, NOR, NAND podemos fazer qualquer função lógica. Porém, outras portas permitem reduzir o número total de transistores c) NAND E 1 E 2 S 0 0 1 1 1 0

b) NOR E 1 E 2 S 0 0 1 0 1 0 0 1 1 0 Com portas inversoras, NOR, NAND podemos fazer qualquer função lógica. Porém, outras portas permitem reduzir o número total de transistores c) NAND E 1 E 2 S 0 0 1 1 1 0

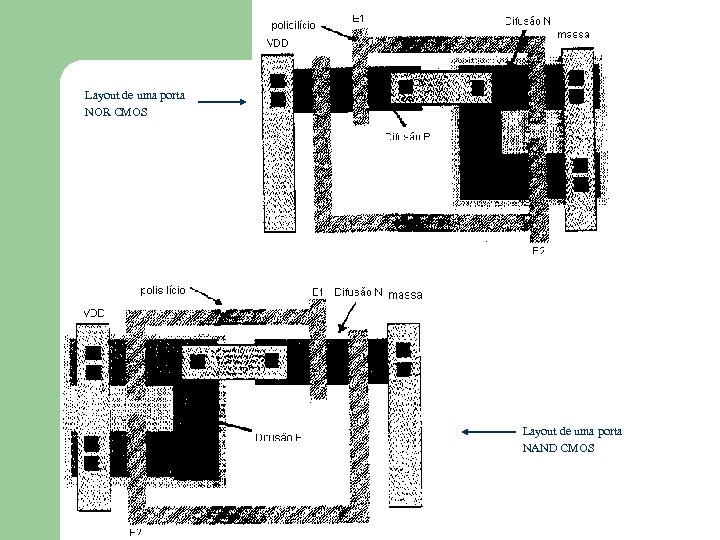

Layout de uma porta NOR CMOS Layout de uma porta NAND CMOS

Layout de uma porta NOR CMOS Layout de uma porta NAND CMOS

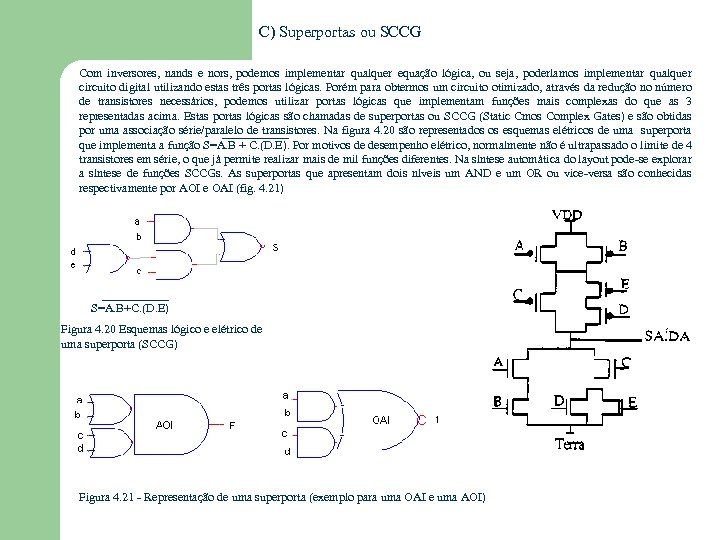

C) Superportas ou SCCG Com inversores, nands e nors, podemos implementar qualquer equação lógica, ou seja, poderíamos implementar qualquer circuito digital utilizando estas três portas lógicas. Porém para obtermos um circuito otimizado, através da redução no número de transistores necessários, podemos utilizar portas lógicas que implementam funções mais complexas do que as 3 representadas acima. Estas portas lógicas são chamadas de superportas ou SCCG (Static Cmos Complex Gates) e são obtidas por uma associação série/paralelo de transistores. Na figura 4. 20 são representados os esquemas elétricos de uma superporta que implementa a função S=A. B + C. (D. E). Por motivos de desempenho elétrico, normalmente não é ultrapassado o limite de 4 transistores em série, o que já permite realizar mais de mil funções diferentes. Na síntese automática do layout pode-se explorar a síntese de funções SCCGs. As superportas que apresentam dois níveis um AND e um OR ou vice-versa são conhecidas respectivamente por AOI e OAI (fig. 4. 21) S=A. B+C. (D. E) Figura 4. 20 Esquemas lógico e elétrico de uma superporta (SCCG) Figura 4. 21 - Representação de uma superporta (exemplo para uma OAI e uma AOI)

C) Superportas ou SCCG Com inversores, nands e nors, podemos implementar qualquer equação lógica, ou seja, poderíamos implementar qualquer circuito digital utilizando estas três portas lógicas. Porém para obtermos um circuito otimizado, através da redução no número de transistores necessários, podemos utilizar portas lógicas que implementam funções mais complexas do que as 3 representadas acima. Estas portas lógicas são chamadas de superportas ou SCCG (Static Cmos Complex Gates) e são obtidas por uma associação série/paralelo de transistores. Na figura 4. 20 são representados os esquemas elétricos de uma superporta que implementa a função S=A. B + C. (D. E). Por motivos de desempenho elétrico, normalmente não é ultrapassado o limite de 4 transistores em série, o que já permite realizar mais de mil funções diferentes. Na síntese automática do layout pode-se explorar a síntese de funções SCCGs. As superportas que apresentam dois níveis um AND e um OR ou vice-versa são conhecidas respectivamente por AOI e OAI (fig. 4. 21) S=A. B+C. (D. E) Figura 4. 20 Esquemas lógico e elétrico de uma superporta (SCCG) Figura 4. 21 - Representação de uma superporta (exemplo para uma OAI e uma AOI)

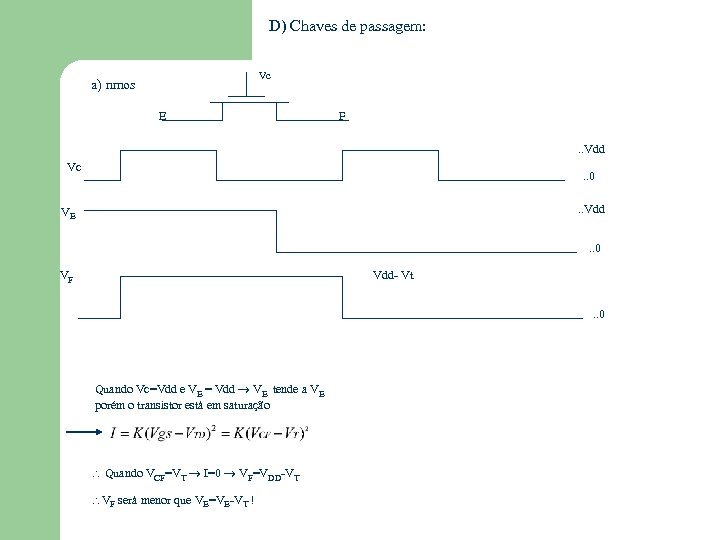

D) Chaves de passagem: Vc a) nmos E F. . Vdd Vc . . 0. . Vdd VE . . 0 VF Vdd- Vt. . 0 Quando Vc=Vdd e VE = Vdd VE tende a VE porém o transistor está em saturação Quando VCF=VT I=0 VF=VDD-VT VF será menor que VE=VE-VT !

D) Chaves de passagem: Vc a) nmos E F. . Vdd Vc . . 0. . Vdd VE . . 0 VF Vdd- Vt. . 0 Quando Vc=Vdd e VE = Vdd VE tende a VE porém o transistor está em saturação Quando VCF=VT I=0 VF=VDD-VT VF será menor que VE=VE-VT !

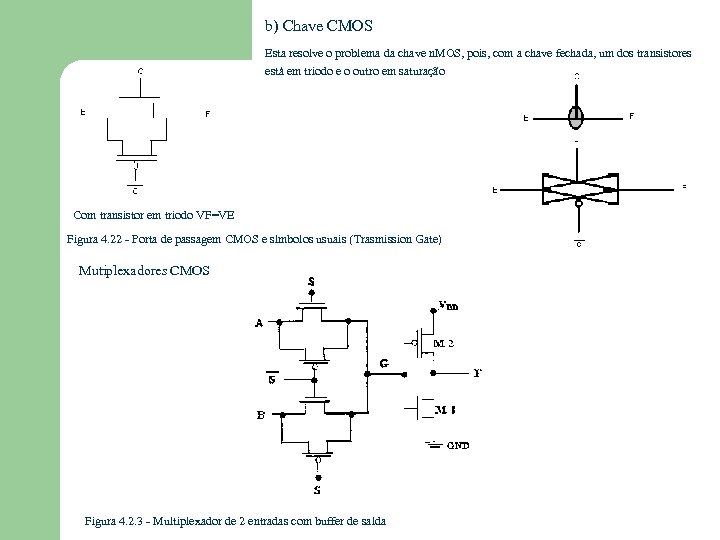

b) Chave CMOS Esta resolve o problema da chave n. MOS, pois, com a chave fechada, um dos transistores está em triodo e o outro em saturação Com transistor em triodo VF=VE Figura 4. 22 - Porta de passagem CMOS e símbolos usuais (Trasmission Gate) Mutiplexadores CMOS Figura 4. 2. 3 - Multiplexador de 2 entradas com buffer de saída

b) Chave CMOS Esta resolve o problema da chave n. MOS, pois, com a chave fechada, um dos transistores está em triodo e o outro em saturação Com transistor em triodo VF=VE Figura 4. 22 - Porta de passagem CMOS e símbolos usuais (Trasmission Gate) Mutiplexadores CMOS Figura 4. 2. 3 - Multiplexador de 2 entradas com buffer de saída

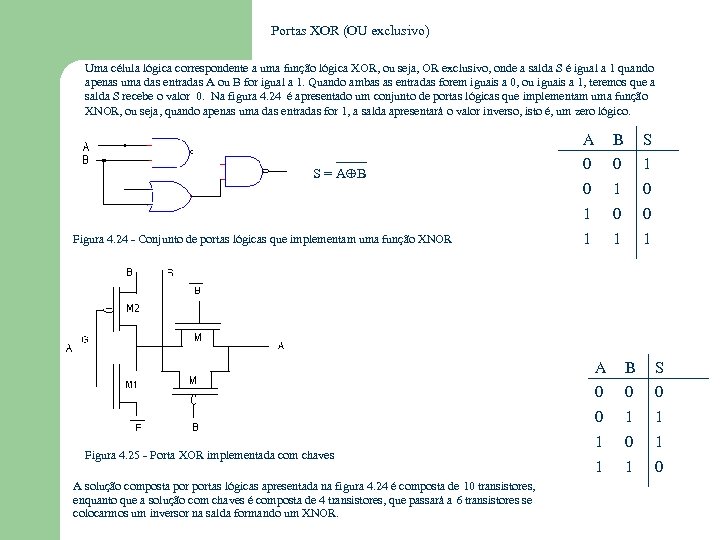

Portas XOR (OU exclusivo) Uma célula lógica correspondente a uma função lógica XOR, ou seja, OR exclusivo, onde a saída S é igual a 1 quando apenas uma das entradas A ou B for igual a 1. Quando ambas as entradas forem iguais a 0, ou iguais a 1, teremos que a saída S recebe o valor 0. Na figura 4. 24 é apresentado um conjunto de portas lógicas que implementam uma função XNOR, ou seja, quando apenas uma das entradas for 1, a saída apresentará o valor inverso, isto é, um zero lógico. A Figura 4. 24 - Conjunto de portas lógicas que implementam uma função XNOR S 0 0 1 0 1 S = A B B 0 0 1 1 1 A 0 0 0 A solução composta portas lógicas apresentada na figura 4. 24 é composta de 10 transistores, enquanto que a solução com chaves é composta de 4 transistores, que passará a 6 transistores se colocarmos um inversor na saída formando um XNOR. S 0 Figura 4. 25 - Porta XOR implementada com chaves B 1 1 1 0

Portas XOR (OU exclusivo) Uma célula lógica correspondente a uma função lógica XOR, ou seja, OR exclusivo, onde a saída S é igual a 1 quando apenas uma das entradas A ou B for igual a 1. Quando ambas as entradas forem iguais a 0, ou iguais a 1, teremos que a saída S recebe o valor 0. Na figura 4. 24 é apresentado um conjunto de portas lógicas que implementam uma função XNOR, ou seja, quando apenas uma das entradas for 1, a saída apresentará o valor inverso, isto é, um zero lógico. A Figura 4. 24 - Conjunto de portas lógicas que implementam uma função XNOR S 0 0 1 0 1 S = A B B 0 0 1 1 1 A 0 0 0 A solução composta portas lógicas apresentada na figura 4. 24 é composta de 10 transistores, enquanto que a solução com chaves é composta de 4 transistores, que passará a 6 transistores se colocarmos um inversor na saída formando um XNOR. S 0 Figura 4. 25 - Porta XOR implementada com chaves B 1 1 1 0

Referências 1 - Semiconductor Device Modeling with Spice (Paolo Antognetti & Giuseppe Massobrio) 2 - CMOS - circuit design, layout and simulation (R. Jacob Baker, Harry W. Li, David Boyce) 3 - Mosfet Modeling & Bsim user’s guide (Yuhua Cheng, Chenming Hu) 4 - Operation and Modeling of the Mos Transistor (Yannis Tsividis) 5 - Orcad’s manual 6 - IEEE - Transactions on Electron Devices n 9 - September 1983 (1219 -1228) Site na Internet: Contém vários modelos de simulação de circuitos http: //sc. tamu. edu/help/hspice/html_doc/manual/hspice-128. html FIM

Referências 1 - Semiconductor Device Modeling with Spice (Paolo Antognetti & Giuseppe Massobrio) 2 - CMOS - circuit design, layout and simulation (R. Jacob Baker, Harry W. Li, David Boyce) 3 - Mosfet Modeling & Bsim user’s guide (Yuhua Cheng, Chenming Hu) 4 - Operation and Modeling of the Mos Transistor (Yannis Tsividis) 5 - Orcad’s manual 6 - IEEE - Transactions on Electron Devices n 9 - September 1983 (1219 -1228) Site na Internet: Contém vários modelos de simulação de circuitos http: //sc. tamu. edu/help/hspice/html_doc/manual/hspice-128. html FIM