4cf401307b1df33c915543a3b1454c5e.ppt

- Количество слайдов: 83

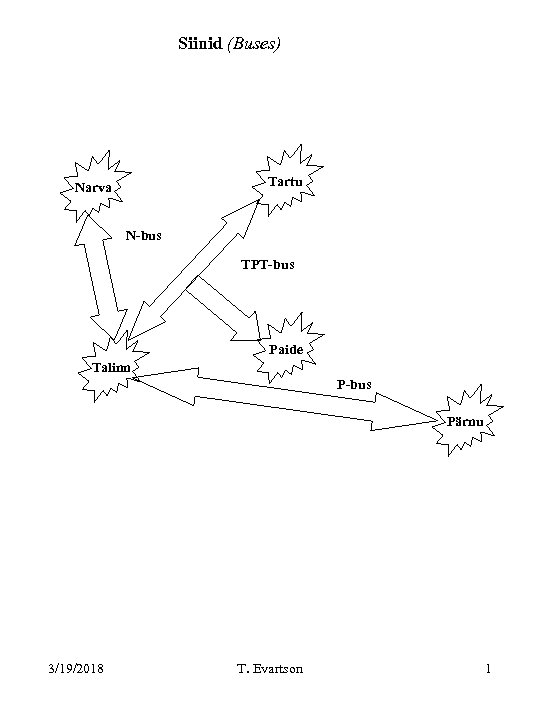

Siinid (Buses) Tartu Narva N-bus TPT-bus Paide Talinn P-bus Pärnu 3/19/2018 T. Evartson 1

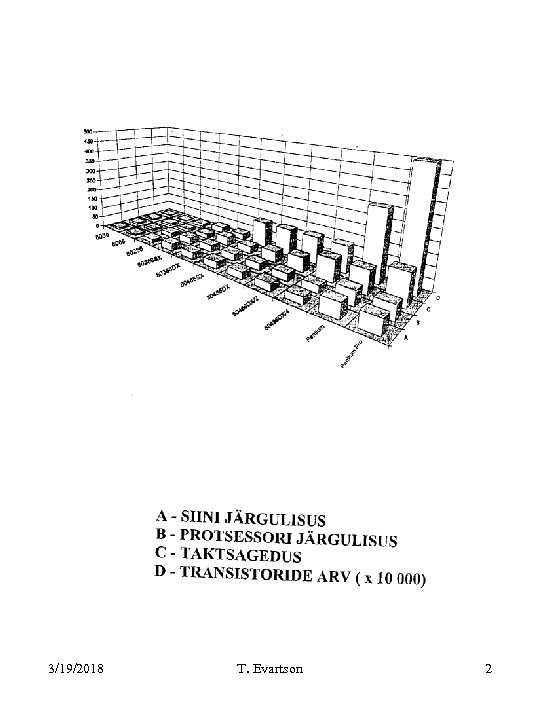

3/19/2018 T. Evartson 2

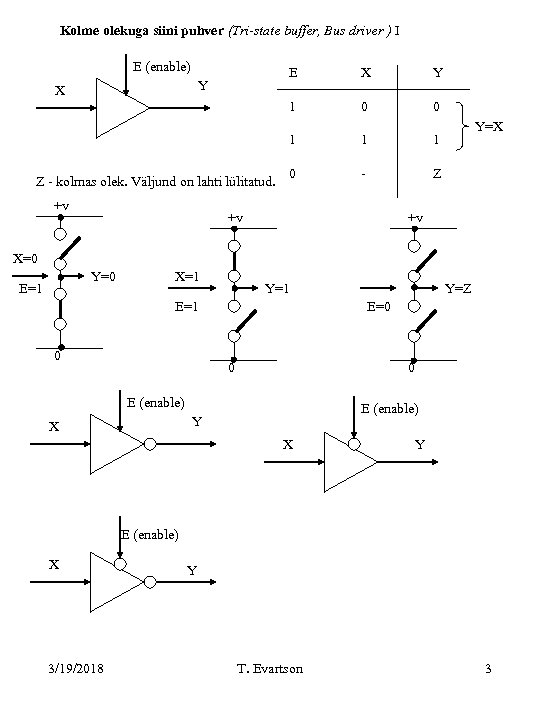

Kolme olekuga siini puhver (Tri-state buffer, Bus driver ) I E (enable) E X X Y 1 Y 0 0 1 Z - kolmas olek. Väljund on lahti lülitatud. +v 1 1 0 - Y=X Z +v +v X=0 Y=0 E=1 X=1 Y=1 E=1 0 E=0 0 0 E (enable) Y X Y=Z X Y E (enable) X 3/19/2018 Y T. Evartson 3

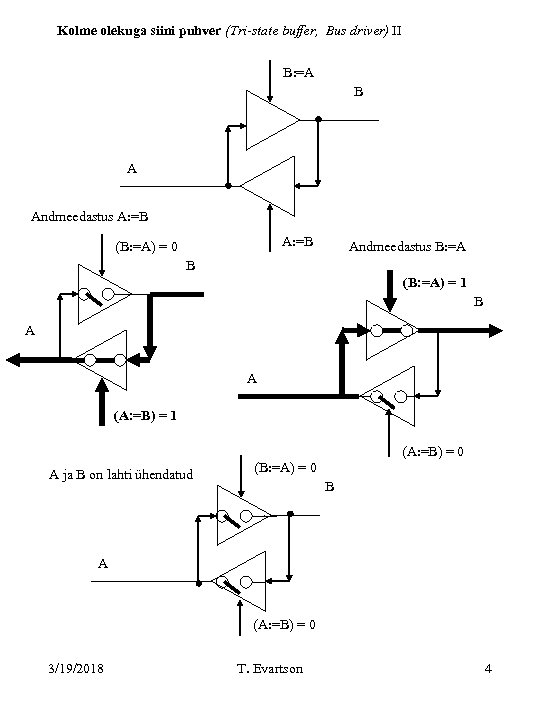

Kolme olekuga siini puhver (Tri-state buffer, Bus driver) II B: =A B A Andmeedastus A: =B (B: =A) = 0 Andmeedastus B: =A B (B: =A) = 1 B A A (A: =B) = 1 (A: =B) = 0 A ja B on lahti ühendatud (B: =A) = 0 B A (A: =B) = 0 3/19/2018 T. Evartson 4

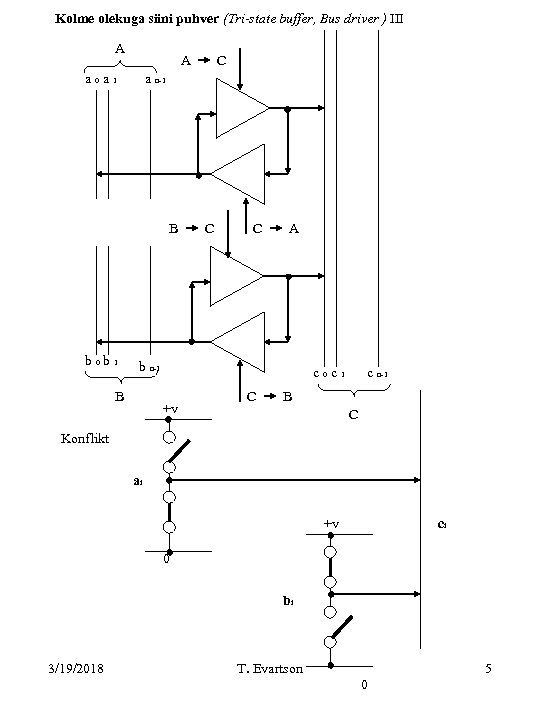

Kolme olekuga siini puhver (Tri-state buffer, Bus driver ) III A A a 0 a 1 a n-1 B b 0 b 1 C C C A b n-1 B c 0 c 1 +v C c n-1 B C Konflikt ai +v ci 0 bi 3/19/2018 T. Evartson 5 0

Siinide sidumine Internal BUS & & 3/19/2018 T. Evartson CS RD WR 6

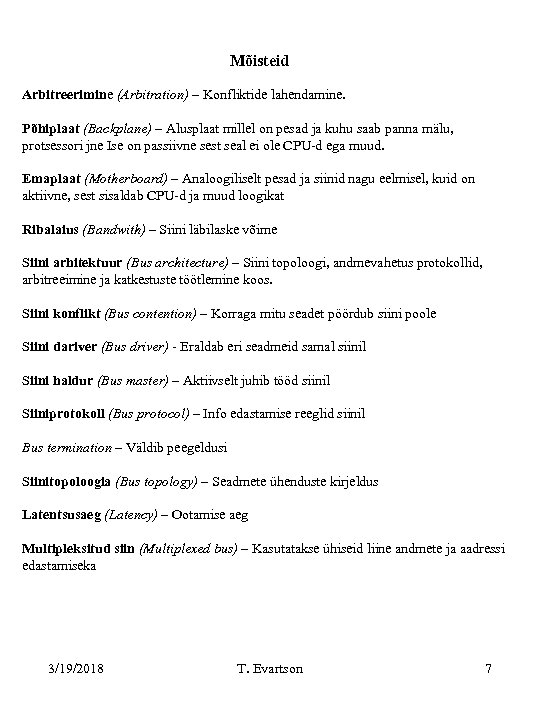

Mõisteid Arbitreerimine (Arbitration) – Konfliktide lahendamine. Põhiplaat (Backplane) – Alusplaat millel on pesad ja kuhu saab panna mälu, protsessori jne Ise on passiivne sest seal ei ole CPU-d ega muud. Emaplaat (Motherboard) – Analoogiliselt pesad ja siinid nagu eelmisel, kuid on aktiivne, sest sisaldab CPU-d ja muud loogikat Ribalaius (Bandwith) – Siini läbilaske võime Siini arhitektuur (Bus architecture) – Siini topoloogi, andmevahetus protokollid, arbitreeimine ja katkestuste töötlemine koos. Siini konflikt (Bus contention) – Korraga mitu seadet pöördub siini poole Siini dariver (Bus driver) - Eraldab eri seadmeid samal siinil Siini haldur (Bus master) – Aktiivselt juhib tööd siinil Siiniprotokoll (Bus protocol) – Info edastamise reeglid siinil Bus termination – Väldib peegeldusi Siinitopoloogia (Bus topology) – Seadmete ühenduste kirjeldus Latentsusaeg (Latency) – Ootamise aeg Multipleksitud siin (Multiplexed bus) – Kasutatakse ühiseid liine andmete ja aadressi edastamiseka 3/19/2018 T. Evartson 7

Ühe siiniga arvuti Mälu CPU I/O 3/19/2018 I/O T. Evartson I/O 8

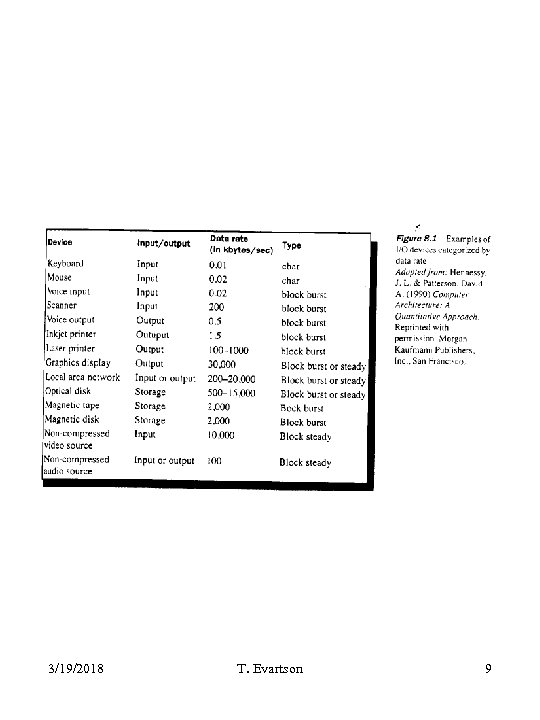

3/19/2018 T. Evartson 9

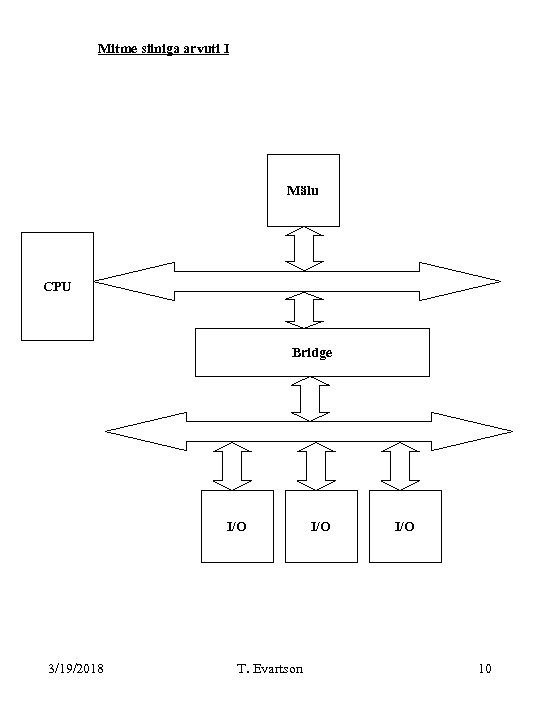

Mitme siiniga arvuti I Mälu CPU Bridge I/O 3/19/2018 T. Evartson I/O 10

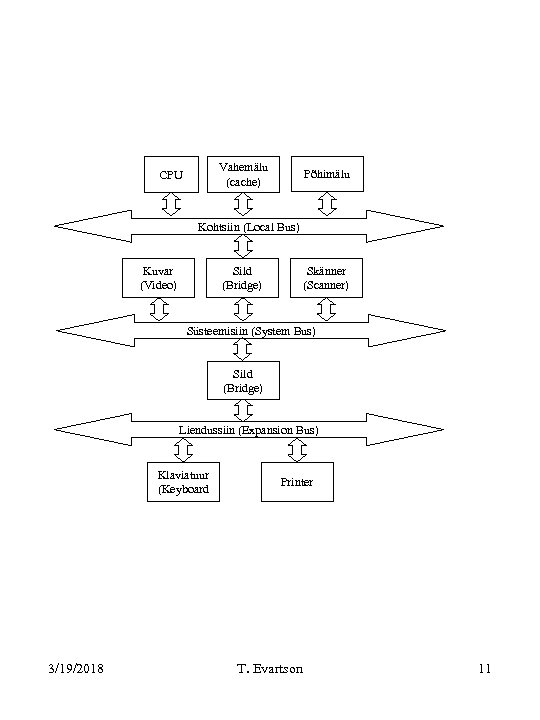

Vahemälu (cache) CPU Põhimälu Kohtsiin (Local Bus) Kuvar (Video) Sild (Bridge) Skänner (Scanner) Süsteemisiin (System Bus) Sild (Bridge) Liendussiin (Expansion Bus) Klaviatuur (Keyboard 3/19/2018 Printer T. Evartson 11

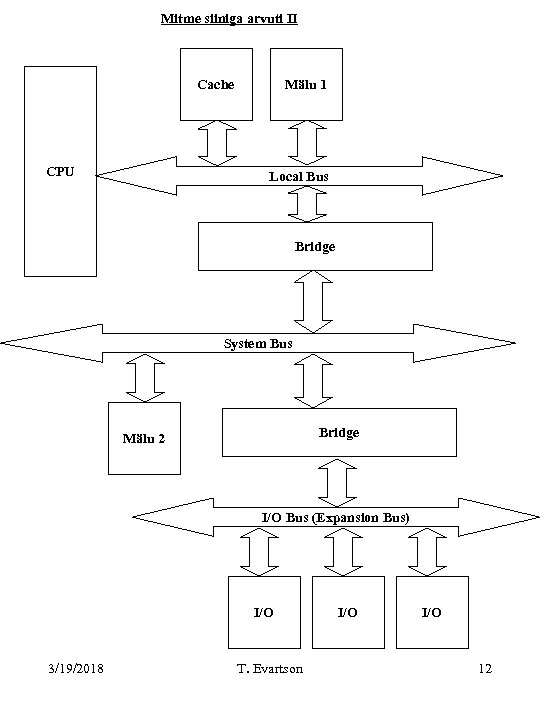

Mitme siiniga arvuti II Cache CPU Mälu 1 Local Bus Bridge System Bus Bridge Mälu 2 I/O Bus (Expansion Bus) I/O 3/19/2018 T. Evartson I/O 12

3/19/2018 T. Evartson 13

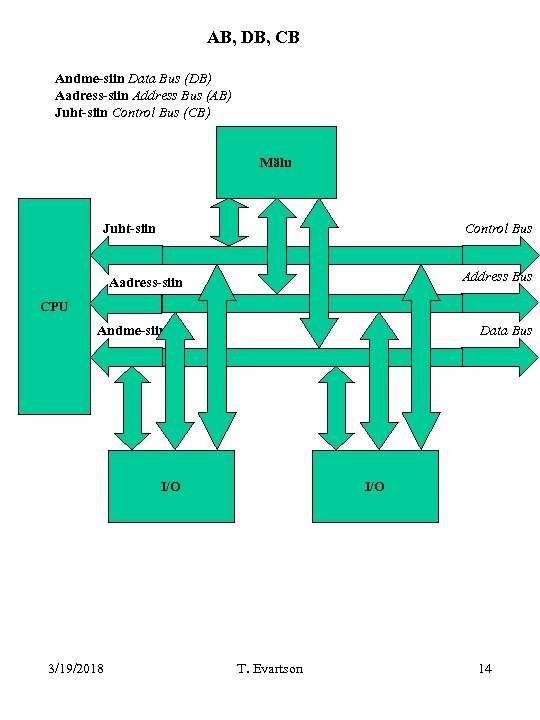

AB, DB, CB Andme-siin Data Bus (DB) Aadress-siin Address Bus (AB) Juht-siin Control Bus (CB) Mälu Juht-siin Control Bus Address Bus Aadress-siin CPU Andme-siin Data Bus I/O 3/19/2018 I/O T. Evartson 14

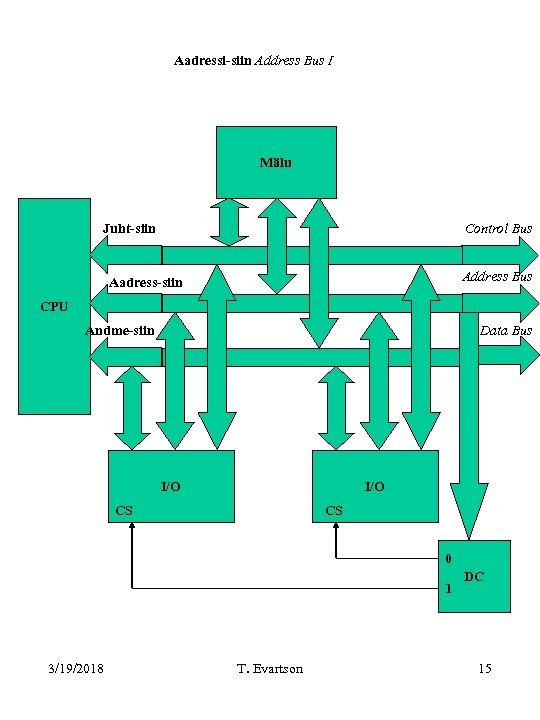

Aadressi-siin Address Bus I Mälu Juht-siin Control Bus Address Bus Aadress-siin CPU Andme-siin Data Bus I/O CS CS 0 1 3/19/2018 T. Evartson DC 15

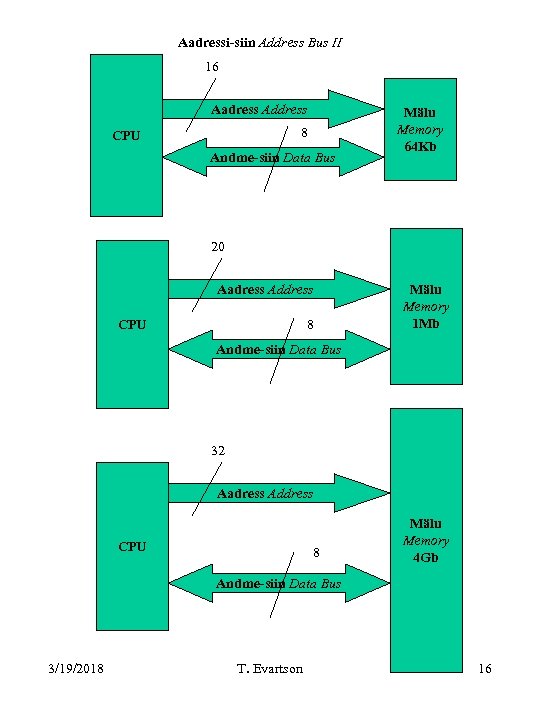

Aadressi-siin Address Bus II 16 Aadress Address 8 CPU Andme-siin Data Bus Mälu Memory 64 Kb 20 Aadress Address CPU 8 Mälu Memory 1 Mb Andme-siin Data Bus 32 Aadress Address CPU 8 Mälu Memory 4 Gb Andme-siin Data Bus 3/19/2018 T. Evartson 16

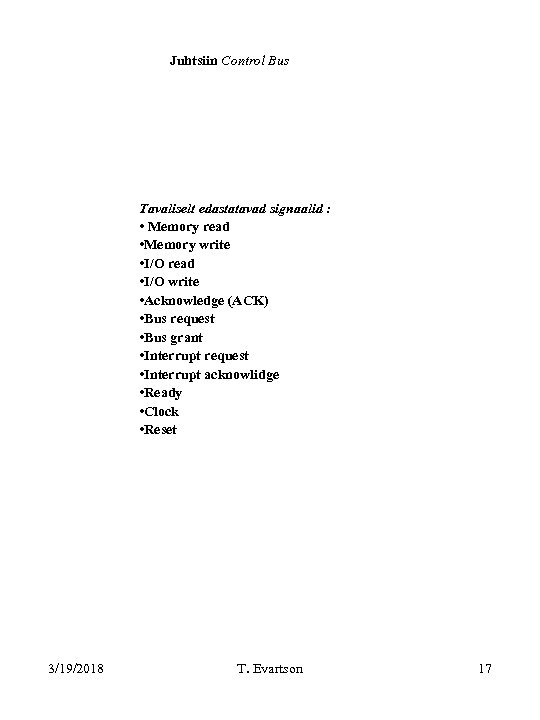

Juhtsiin Control Bus Tavaliselt edastatavad signaalid : • Memory read • Memory write • I/O read • I/O write • Acknowledge (ACK) • Bus request • Bus grant • Interrupt request • Interrupt acknowlidge • Ready • Clock • Reset 3/19/2018 T. Evartson 17

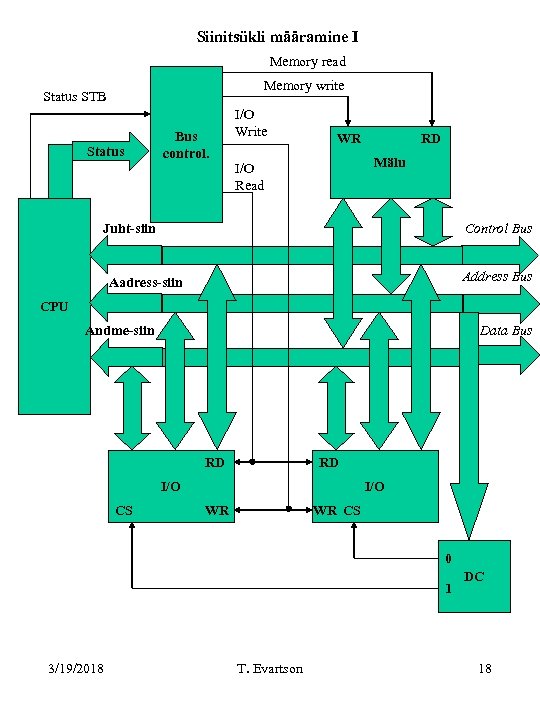

Siinitsükli määramine I Memory read Memory write Status STB Status Bus control. I/O Write WR RD Mälu I/O Read Juht-siin Control Bus Address Bus Aadress-siin CPU Andme-siin Data Bus RD RD I/O CS I/O WR WR CS 0 1 3/19/2018 T. Evartson DC 18

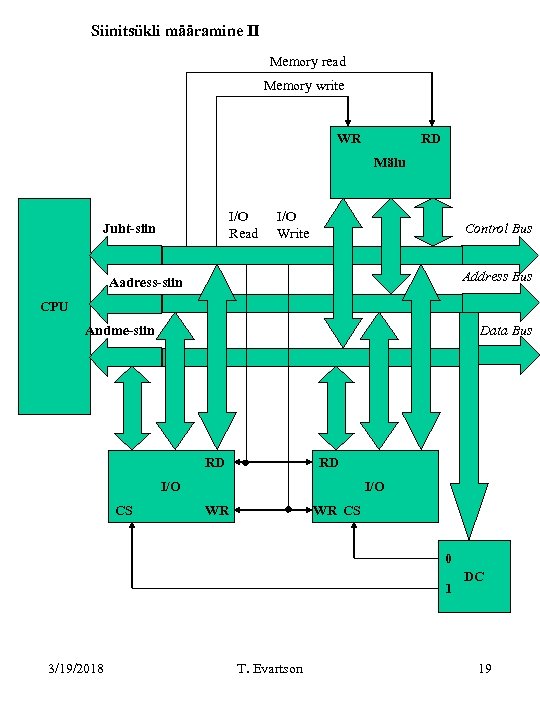

Siinitsükli määramine II Memory read Memory write WR RD Mälu I/O Read Juht-siin I/O Write Control Bus Address Bus Aadress-siin CPU Andme-siin Data Bus RD RD I/O CS I/O WR WR CS 0 1 3/19/2018 T. Evartson DC 19

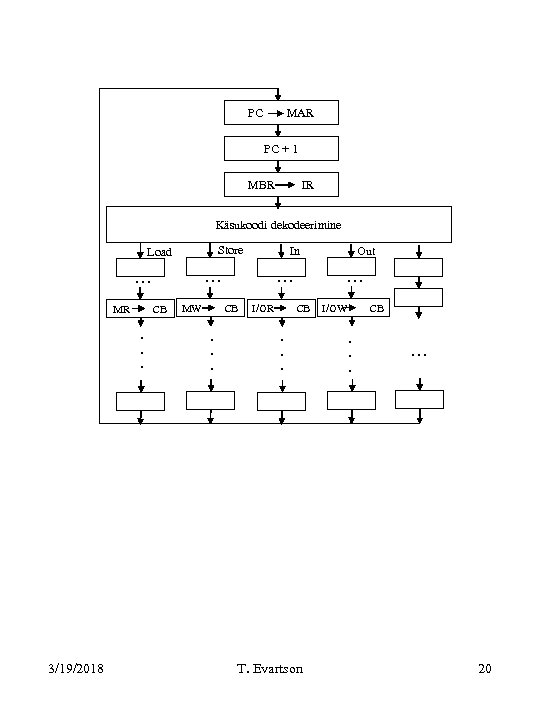

PC MAR PC + 1 MBR IR Käsukoodi dekodeerimine Store Load . . . MR CB . . . 3/19/2018 MW . . CB Out In I/OR CB . . . T. Evartson I/OW CB . . . 20

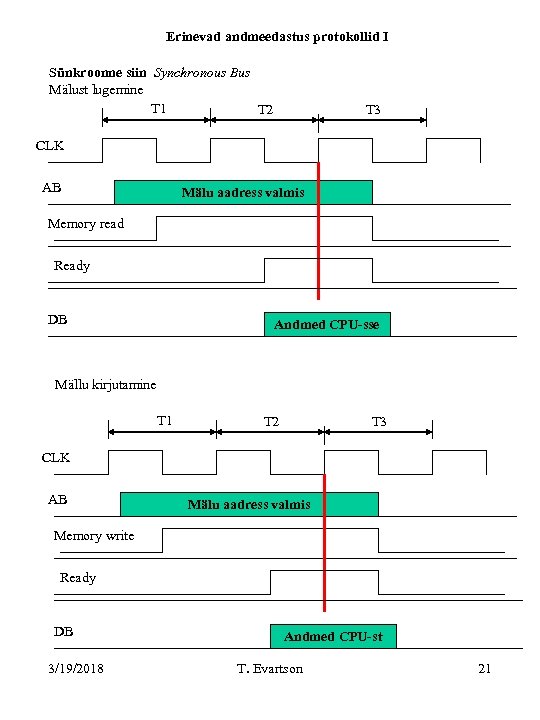

Erinevad andmeedastus protokollid I Sünkroonne siin Synchronous Bus Mälust lugemine T 1 T 2 T 3 CLK AB Mälu aadress valmis Memory read Ready DB Andmed CPU-sse Mällu kirjutamine T 1 T 2 T 3 CLK AB Mälu aadress valmis Memory write Ready DB 3/19/2018 Andmed CPU-st T. Evartson 21

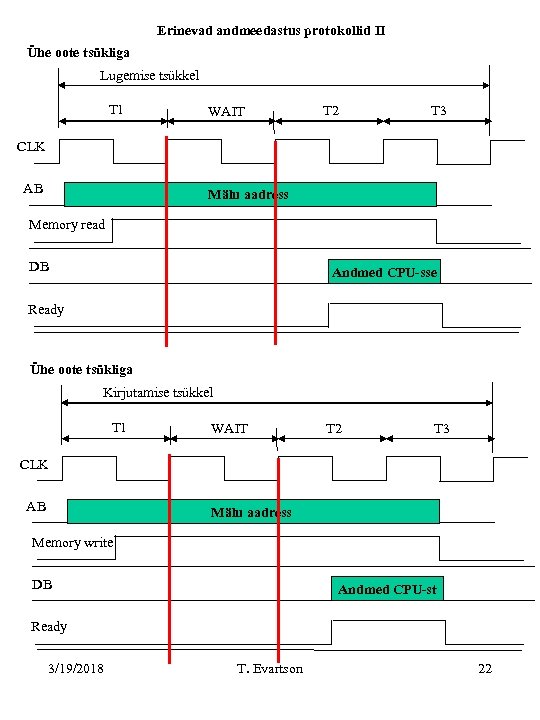

Erinevad andmeedastus protokollid II Ühe oote tsükliga Lugemise tsükkel T 1 WAIT T 2 T 3 CLK AB Mälu aadress Memory read DB Andmed CPU-sse Ready Ühe oote tsükliga Kirjutamise tsükkel T 1 WAIT T 2 T 3 CLK AB Mälu aadress Memory write DB Andmed CPU-st Ready 3/19/2018 T. Evartson 22

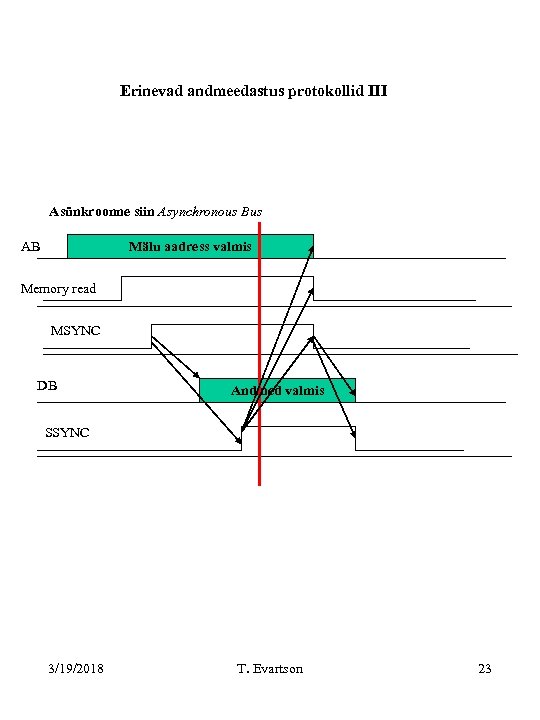

Erinevad andmeedastus protokollid III Asünkroonne siin Asynchronous Bus Mälu aadress valmis AB Memory read MSYNC DB Andmed valmis SSYNC 3/19/2018 T. Evartson 23

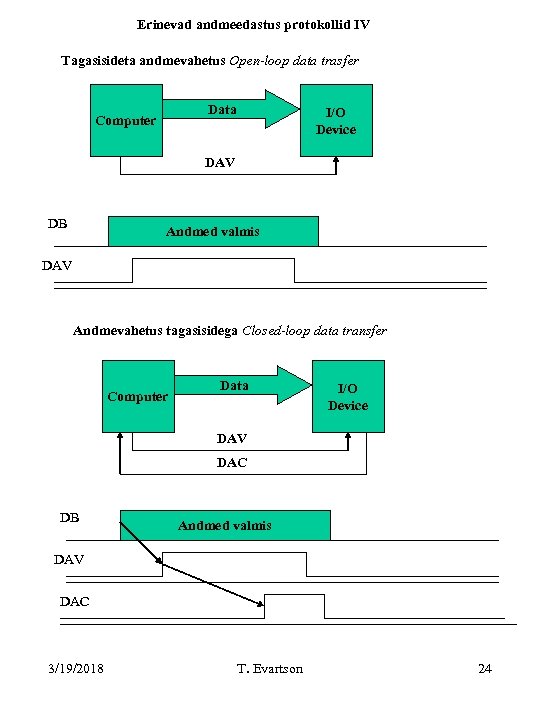

Erinevad andmeedastus protokollid IV Tagasisideta andmevahetus Open-loop data trasfer Data Computer I/O Device DAV DB Andmed valmis DAV Andmevahetus tagasisidega Closed-loop data transfer Computer Data I/O Device DAV DAC DB Andmed valmis DAV DAC 3/19/2018 T. Evartson 24

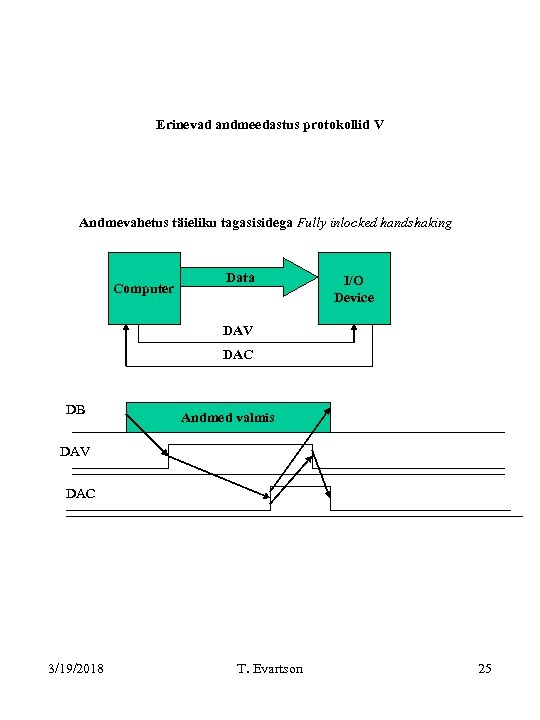

Erinevad andmeedastus protokollid V Andmevahetus täieliku tagasisidega Fully inlocked handshaking Computer Data I/O Device DAV DAC DB Andmed valmis DAV DAC 3/19/2018 T. Evartson 25

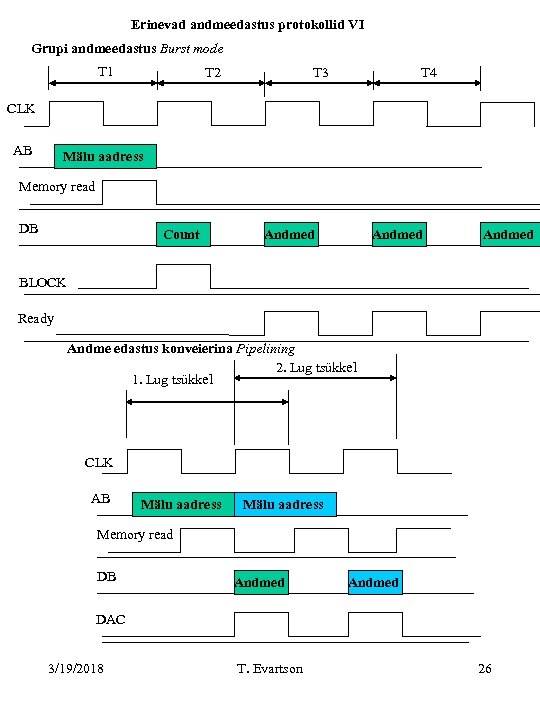

Erinevad andmeedastus protokollid VI Grupi andmeedastus Burst mode T 1 T 2 T 3 T 4 CLK AB Mälu aadress Memory read DB Count Andmed BLOCK Ready Andme edastus konveierina Pipelining 2. Lug tsükkel 1. Lug tsükkel CLK AB Mälu aadress Memory read DB Andmed DAC 3/19/2018 T. Evartson 26

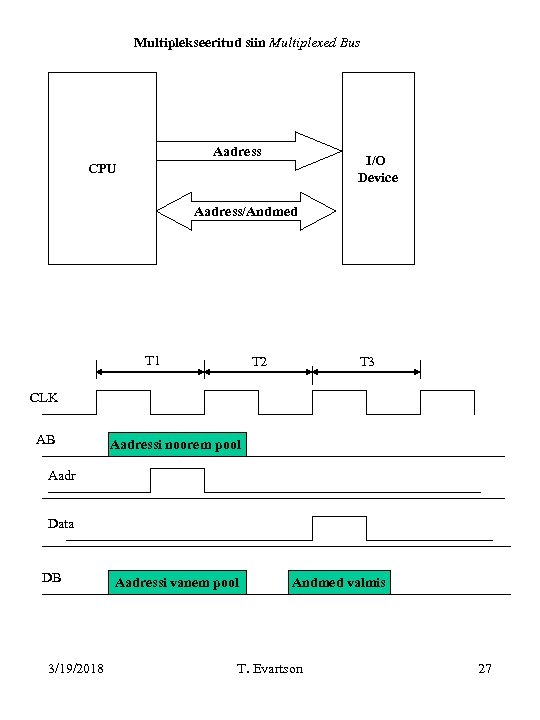

Multiplekseeritud siin Multiplexed Bus Aadress I/O Device CPU Aadress/Andmed T 1 T 2 T 3 CLK AB Aadressi noorem pool Aadr Data DB 3/19/2018 Aadressi vanem pool Andmed valmis T. Evartson 27

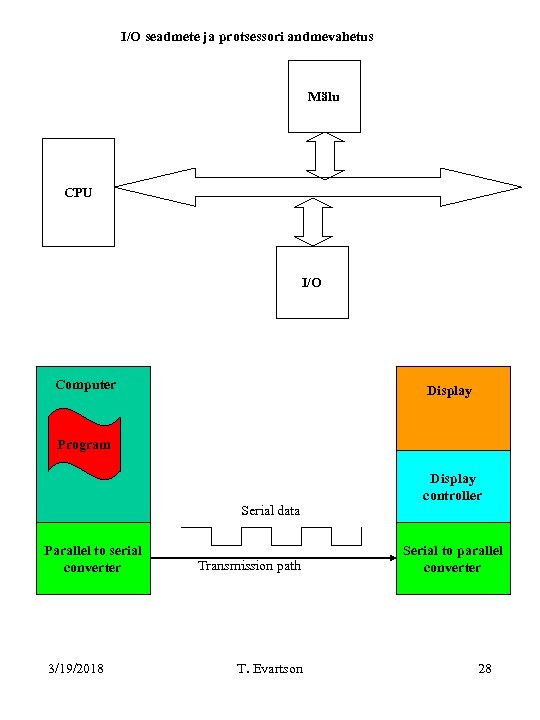

I/O seadmete ja protsessori andmevahetus Mälu CPU I/O Computer Display Program Display controller Serial data Parallel to serial converter 3/19/2018 Transmission path T. Evartson Serial to parallel converter 28

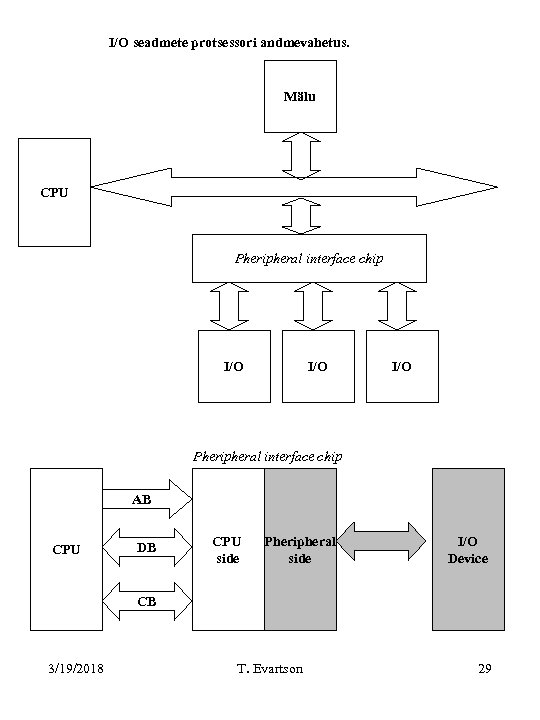

I/O seadmete protsessori andmevahetus. Mälu CPU Pheripheral interface chip I/O I/O Pheripheral interface chip AB CPU DB CPU side Pheripheral side I/O Device CB 3/19/2018 T. Evartson 29

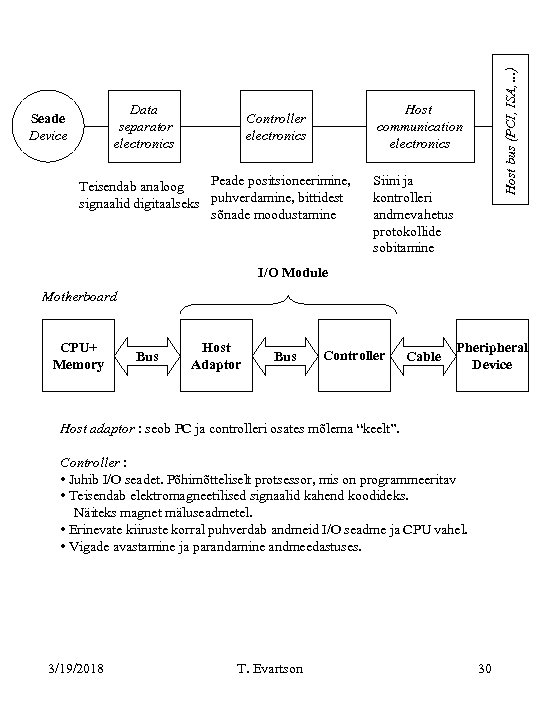

Host bus (PCI, ISA, …) Data separator electronics Seade Device Host communication electronics Controller electronics Peade positsioneerimine, Teisendab analoog signaalid digitaalseks puhverdamine, bittidest sõnade moodustamine Siini ja kontrolleri andmevahetus protokollide sobitamine I/O Module Motherboard CPU+ Memory Bus Host Adaptor Bus Controller Cable Pheripheral Device Host adaptor : seob PC ja controlleri osates mõlema “keelt”. Controller : • Juhib I/O seadet. Põhimõtteliselt protsessor, mis on programmeeritav • Teisendab elektromagneetilised signaalid kahend koodideks. Näiteks magnet mäluseadmetel. • Erinevate kiiruste korral puhverdab andmeid I/O seadme ja CPU vahel. • Vigade avastamine ja parandamine andmeedastuses. 3/19/2018 T. Evartson 30

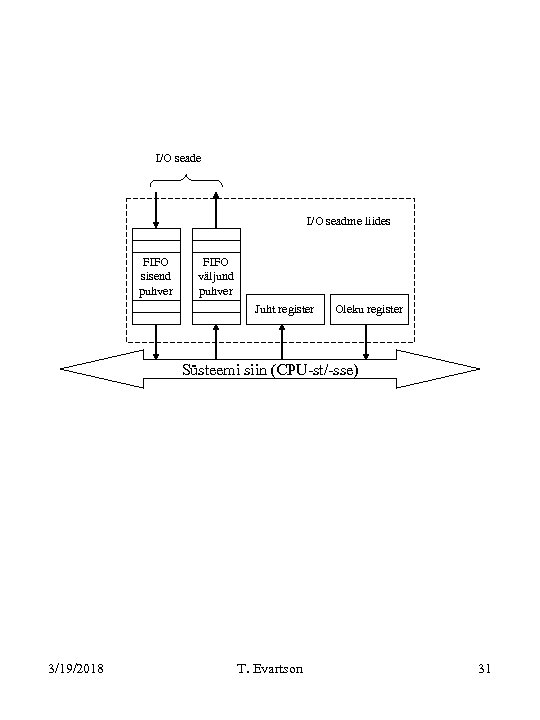

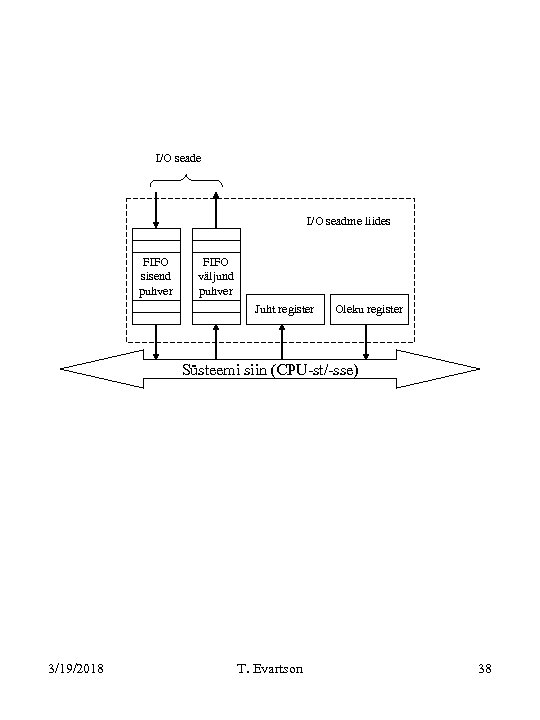

I/O seade I/O seadme liides FIFO sisend puhver FIFO väljund puhver Juht register Oleku register Süsteemi siin (CPU-st/-sse) 3/19/2018 T. Evartson 31

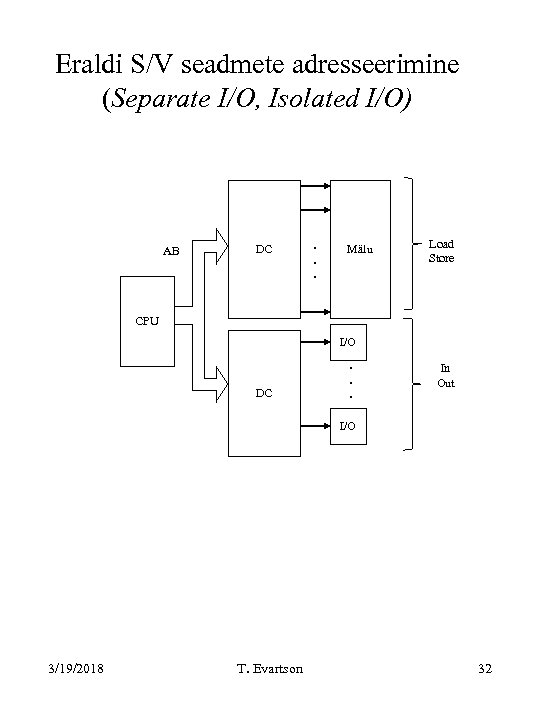

Eraldi S/V seadmete adresseerimine (Separate I/O, Isolated I/O) AB DC . . . Mälu Load Store CPU I/O DC . . . In Out I/O 3/19/2018 T. Evartson 32

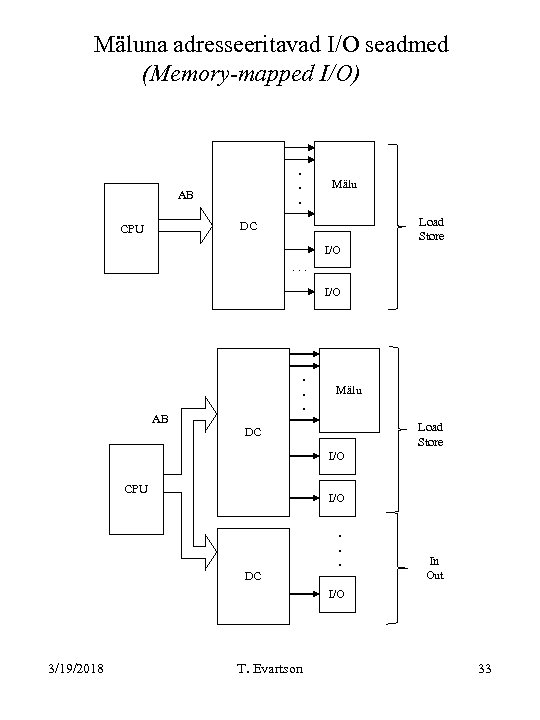

Mäluna adresseeritavad I/O seadmed (Memory-mapped I/O) . . . AB Mälu Load Store DC CPU I/O. . . I/O AB . . . Mälu Load Store DC I/O CPU I/O. . . DC In Out I/O 3/19/2018 T. Evartson 33

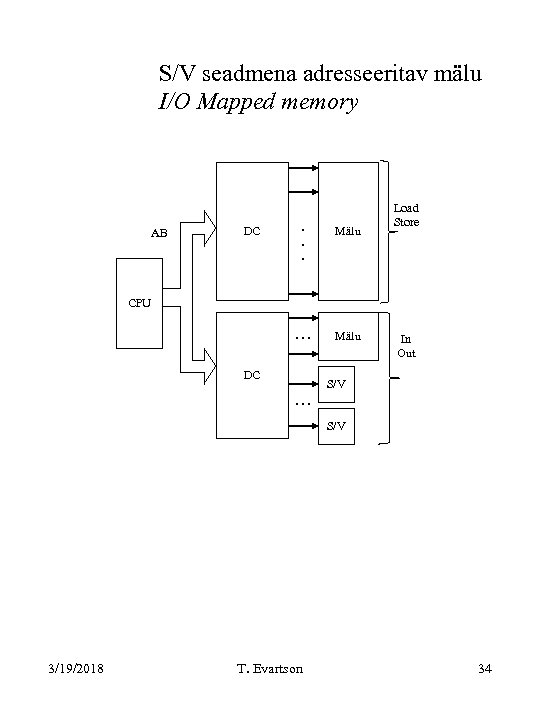

S/V seadmena adresseeritav mälu I/O Mapped memory DC . . . Mälu . . . AB Mälu Load Store CPU DC In Out S/V. . . S/V 3/19/2018 T. Evartson 34

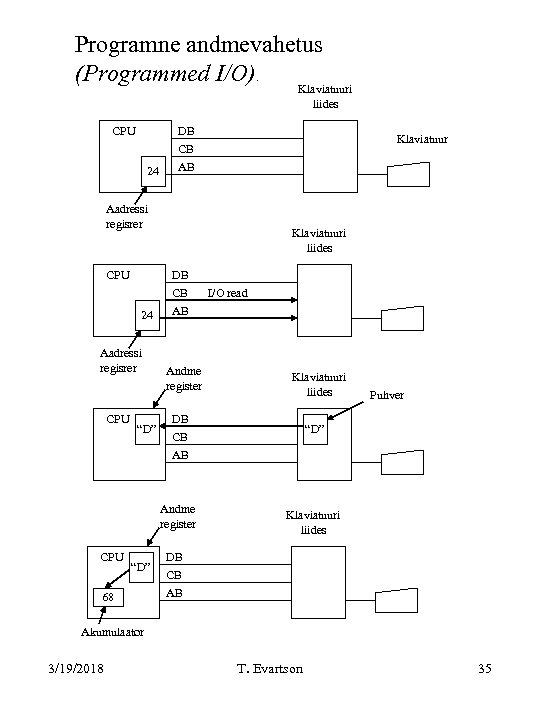

Programne andmevahetus (Programmed I/O). Klaviatuuri liides CPU DB 24 Klaviatuur CB AB Aadressi regisrer CPU 24 Aadressi regisrer CPU “D” Klaviatuuri liides DB CB AB Andme register “D” 68 Klaviatuuri liides DB CB AB Andme register CPU I/O read Puhver “D” Klaviatuuri liides DB CB AB Akumulaator 3/19/2018 T. Evartson 35

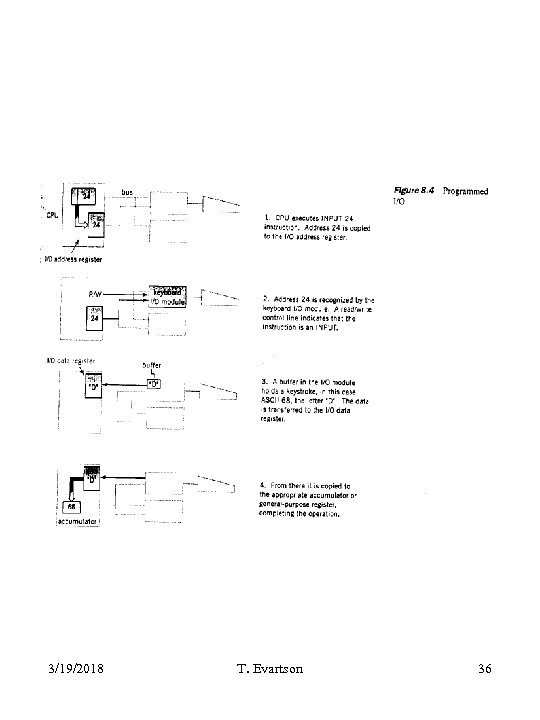

3/19/2018 T. Evartson 36

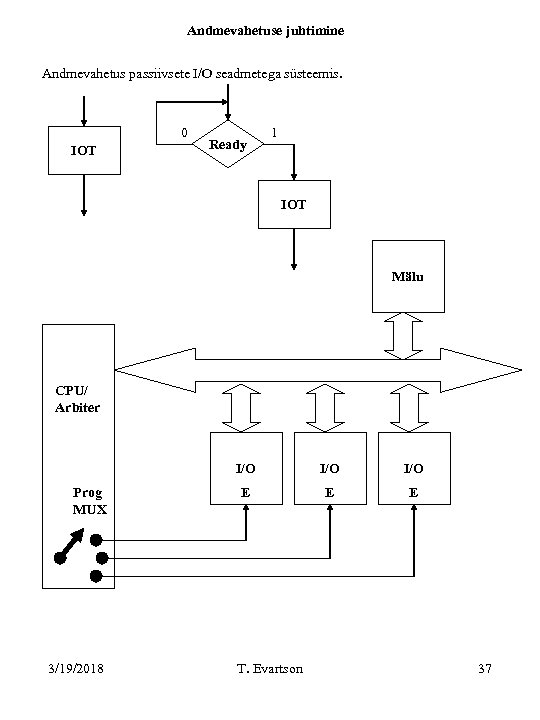

Andmevahetuse juhtimine Andmevahetus passiivsete I/O seadmetega süsteemis. 0 IOT Ready 1 IOT Mälu CPU/ Arbiter I/O Prog MUX 3/19/2018 I/O E E E T. Evartson 37

I/O seade I/O seadme liides FIFO sisend puhver FIFO väljund puhver Juht register Oleku register Süsteemi siin (CPU-st/-sse) 3/19/2018 T. Evartson 38

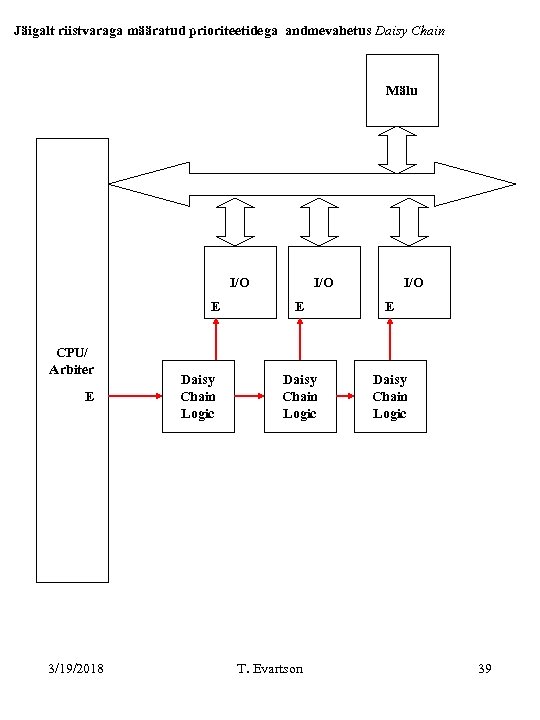

Jäigalt riistvaraga määratud prioriteetidega andmevahetus Daisy Chain Mälu I/O E CPU/ Arbiter E 3/19/2018 Daisy Chain Logic I/O E E Daisy Chain Logic T. Evartson 39

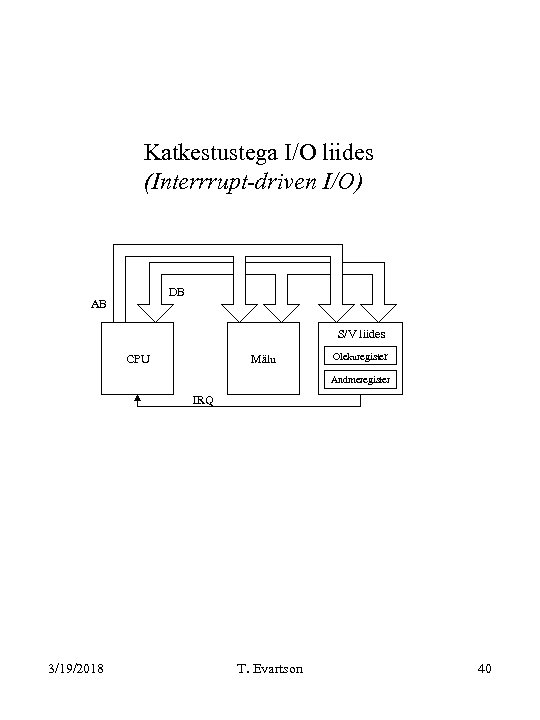

Katkestustega I/O liides (Interrrupt-driven I/O) DB AB S/V liides CPU Mälu Olekuregister Andmeregister IRQ 3/19/2018 T. Evartson 40

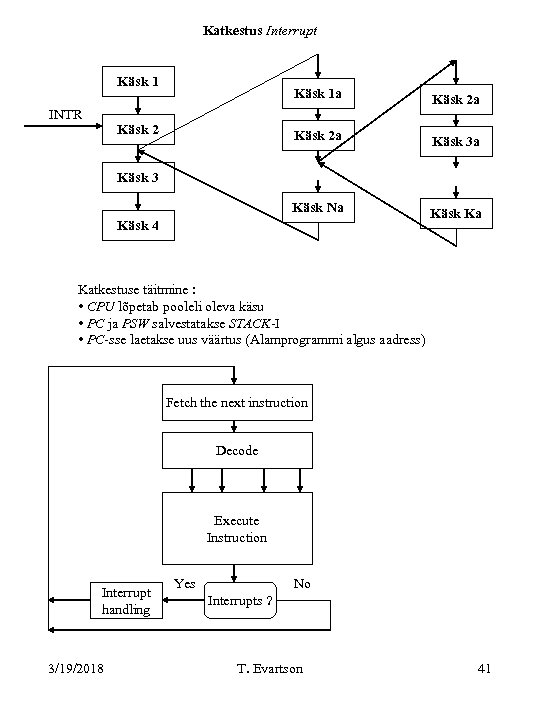

Katkestus Interrupt Käsk 1 Käsk 2 a Käsk 3 a Käsk Na INTR Käsk 1 a Käsk Ka Käsk 3 Käsk 4 Katkestuse täitmine : • CPU lõpetab pooleli oleva käsu • PC ja PSW salvestatakse STACK-I • PC-sse laetakse uus väärtus (Alamprogrammi algus aadress) Fetch the next instruction Decode Execute Instruction Interrupt handling 3/19/2018 Yes No Interrupts ? T. Evartson 41

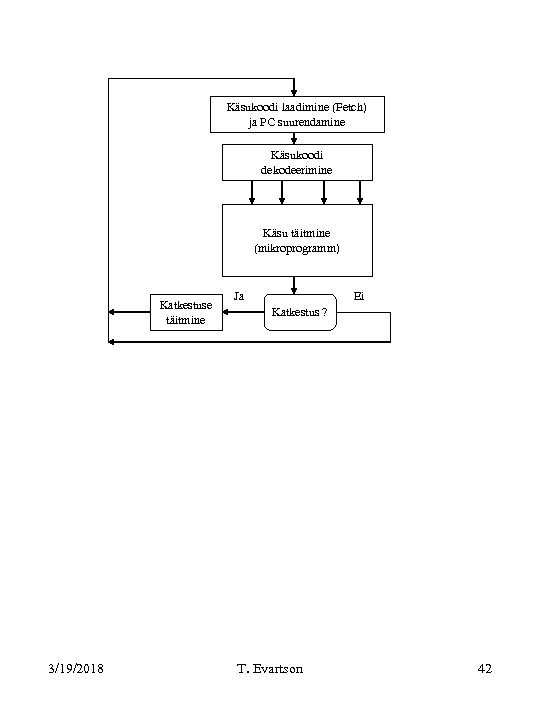

Käsukoodi laadimine (Fetch) ja PC suurendamine Käsukoodi dekodeerimine Käsu täitmine (mikroprogramm) Katkestuse täitmine 3/19/2018 Ja Ei Katkestus ? T. Evartson 42

3/19/2018 T. Evartson 43

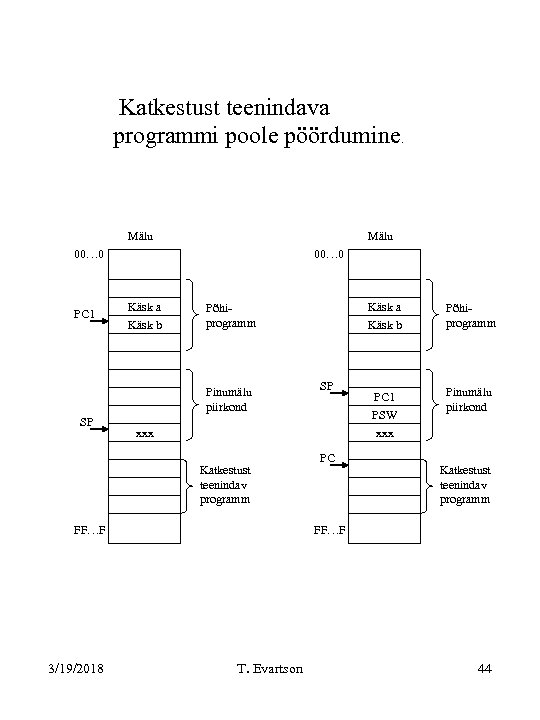

Katkestust teenindava programmi poole pöördumine. Mälu 00… 0 PC 1 00… 0 Käsk a Käsk b Pinumälu piirkond SP SP xxx Katkestust teenindav programm FF…F 3/19/2018 Käsk a Käsk b Põhiprogramm PC 1 PSW xxx Pinumälu piirkond Katkestust teenindav programm FF…F T. Evartson 44

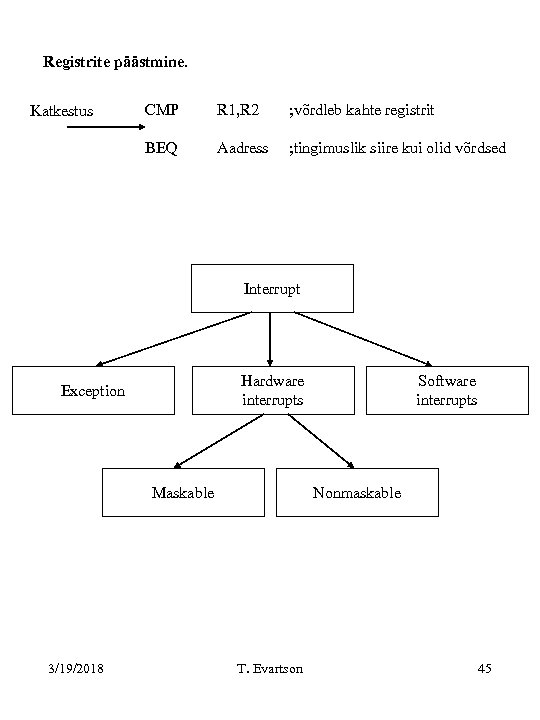

Registrite päästmine. CMP R 1, R 2 ; võrdleb kahte registrit BEQ Katkestus Aadress ; tingimuslik siire kui olid võrdsed Interrupt Hardware interrupts Exception Maskable 3/19/2018 Software interrupts Nonmaskable T. Evartson 45

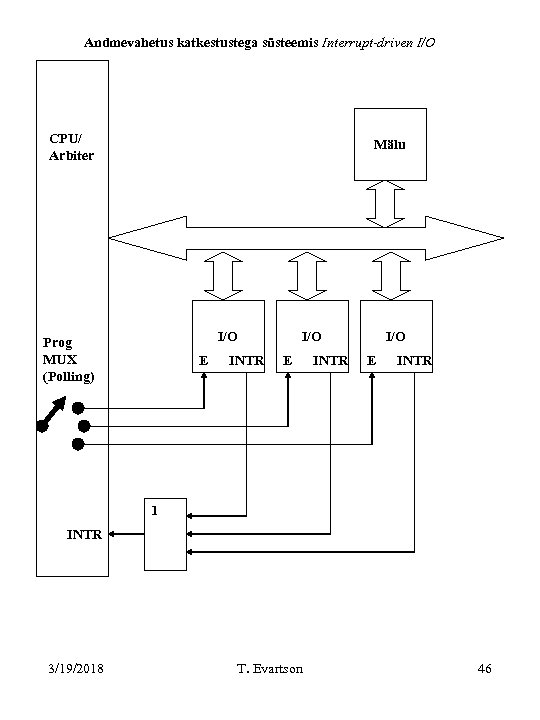

Andmevahetus katkestustega süsteemis Interrupt-driven I/O CPU/ Arbiter Mälu I/O Prog MUX (Polling) E INTR I/O E INTR 1 INTR 3/19/2018 T. Evartson 46

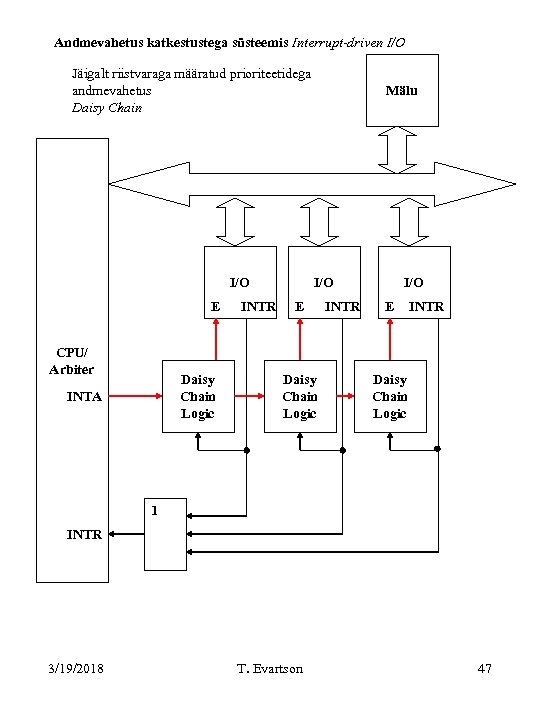

Andmevahetus katkestustega süsteemis Interrupt-driven I/O Jäigalt riistvaraga määratud prioriteetidega andmevahetus Daisy Chain I/O E CPU/ Arbiter Daisy Chain Logic INTA INTR Mälu I/O E Daisy Chain Logic INTR I/O E INTR Daisy Chain Logic 1 INTR 3/19/2018 T. Evartson 47

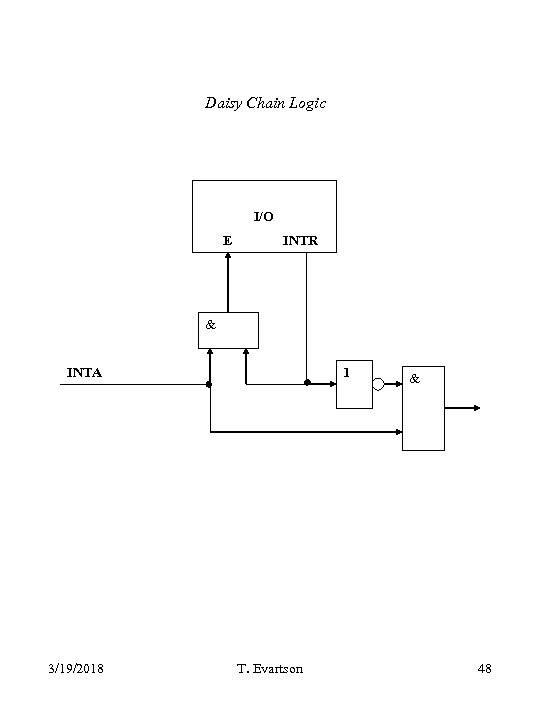

Daisy Chain Logic I/O E INTR & INTA 3/19/2018 1 T. Evartson & 48

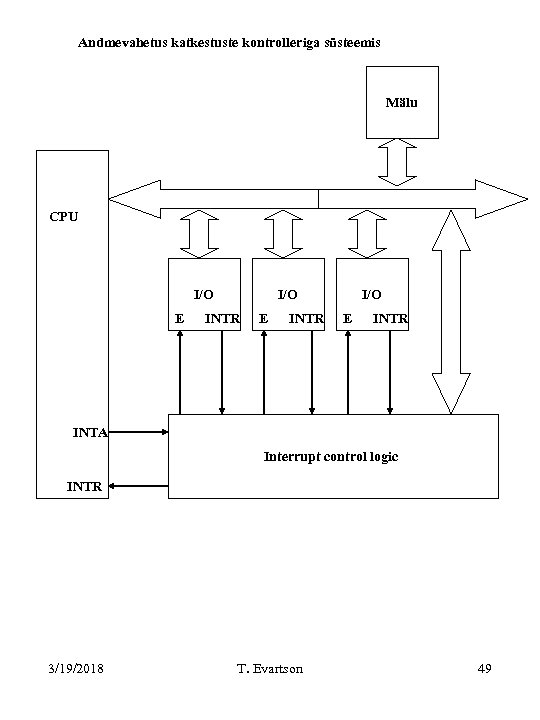

Andmevahetus katkestuste kontrolleriga süsteemis Mälu CPU I/O E I/O INTR E INTR I/O E INTR INTA Interrupt control logic INTR 3/19/2018 T. Evartson 49

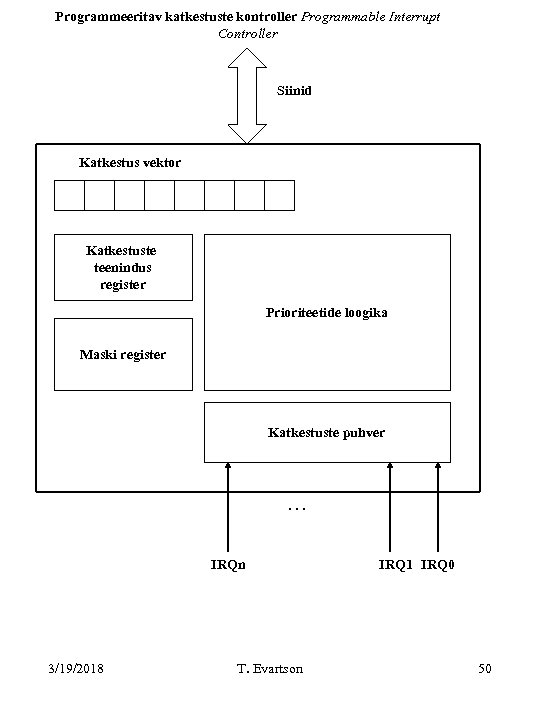

Programmeeritav katkestuste kontroller Programmable Interrupt Controller Siinid Katkestus vektor Katkestuste teenindus register Prioriteetide loogika Maski register Katkestuste puhver . . . IRQn 3/19/2018 T. Evartson IRQ 1 IRQ 0 50

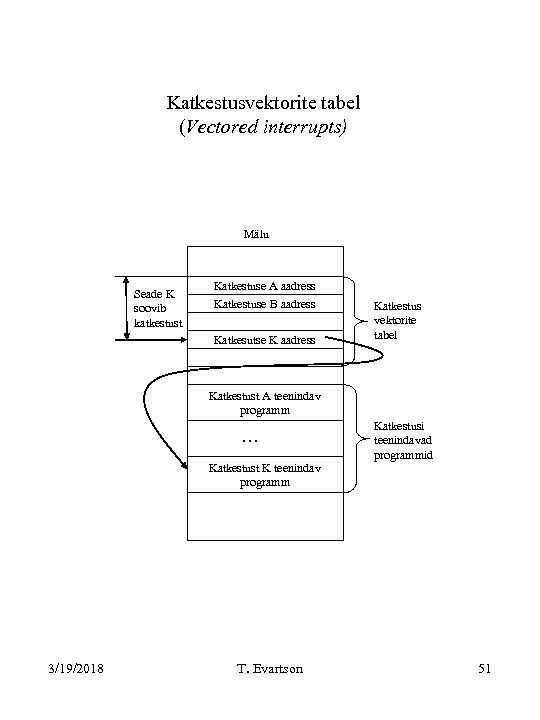

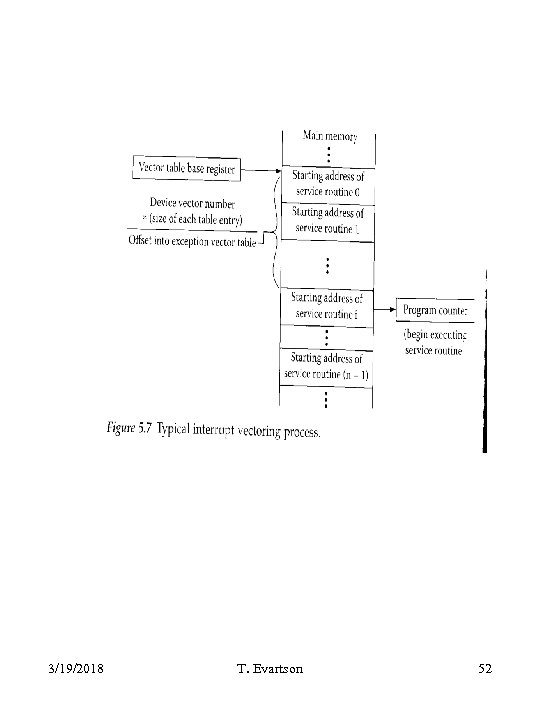

Katkestusvektorite tabel (Vectored interrupts) Mälu Seade K soovib katkestust Katkestuse A aadress Katkestuse B aadress Katkesutse K aadress Katkestus vektorite tabel Katkestust A teenindav programm. . . Katkestust K teenindav programm 3/19/2018 T. Evartson Katkestusi teenindavad programmid 51

3/19/2018 T. Evartson 52

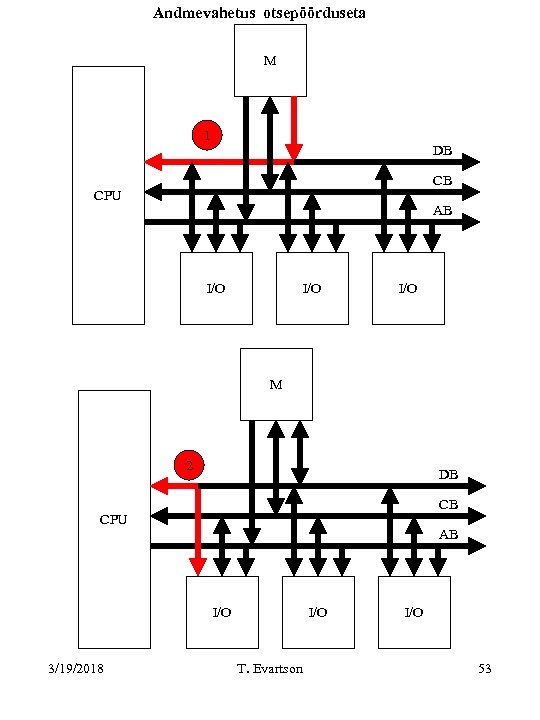

Andmevahetus otsepöörduseta M 1 DB CB CPU AB I/O I/O M 2 DB CB CPU AB I/O 3/19/2018 I/O T. Evartson I/O 53

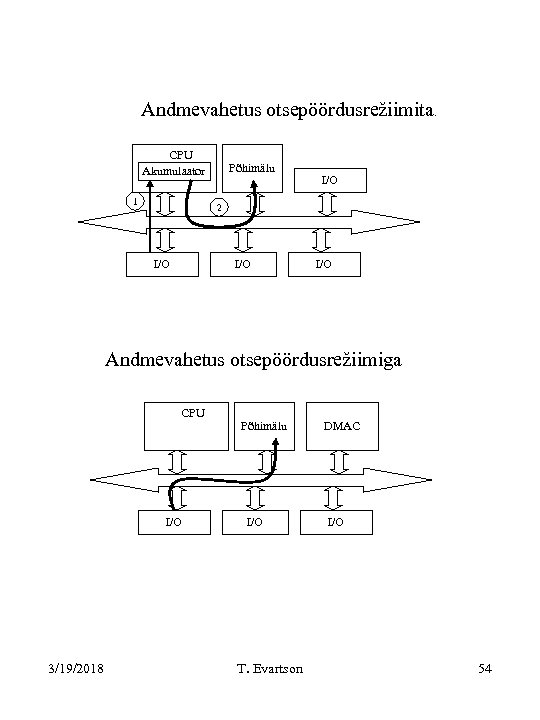

Andmevahetus otsepöördusrežiimita. CPU Akumulaator 1 Põhimälu I/O 2 I/O I/O Andmevahetus otsepöördusrežiimiga CPU I/O 3/19/2018 Põhimälu I/O T. Evartson DMAC I/O 54

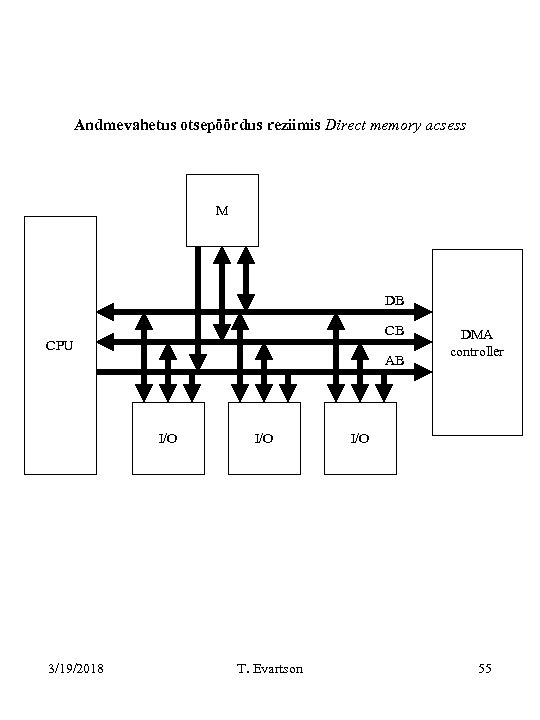

Andmevahetus otsepöördus reziimis Direct memory acsess M DB CB CPU AB I/O 3/19/2018 I/O T. Evartson DMA controller I/O 55

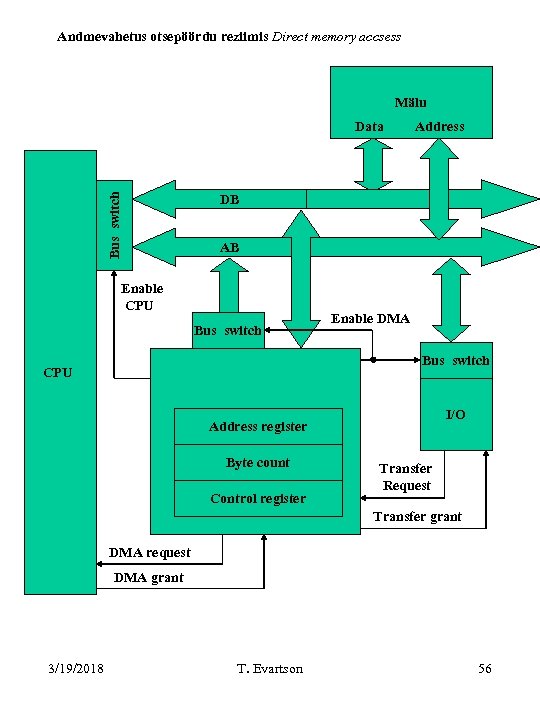

Andmevahetus otsepöördu reziimis Direct memory accsess Mälu Bus switch Data Address DB AB Enable CPU Bus switch Enable DMA Bus switch CPU I/O Address register Byte count Control register Transfer Request Transfer grant DMA request DMA grant 3/19/2018 T. Evartson 56

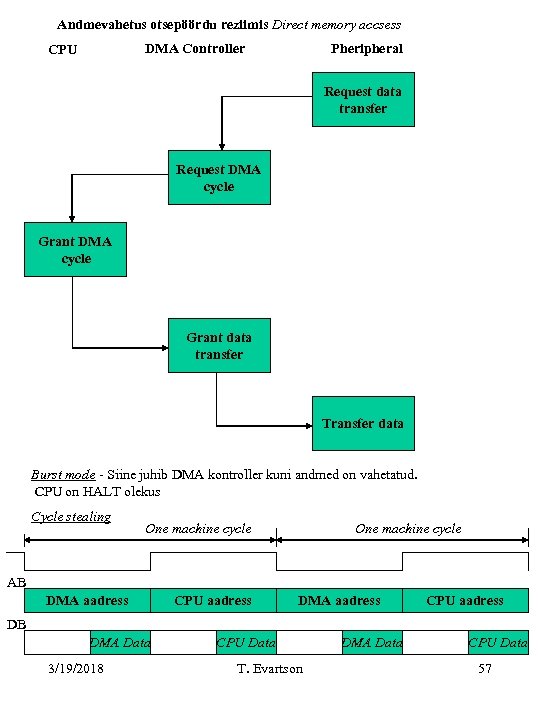

Andmevahetus otsepöördu reziimis Direct memory accsess DMA Controller CPU Pheripheral Request data transfer Request DMA cycle Grant data transfer Transfer data Burst mode - Siine juhib DMA kontroller kuni andmed on vahetatud. CPU on HALT olekus Cycle stealing One machine cycle AB DMA aadress CPU aadress DB DMA Data 3/19/2018 CPU Data T. Evartson DMA Data CPU Data 57

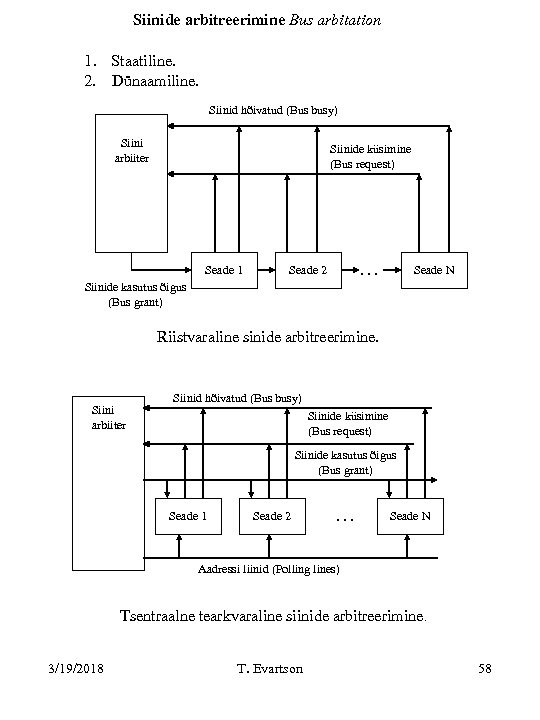

Siinide arbitreerimine Bus arbitation 1. Staatiline. 2. Dünaamiline. Siinid hõivatud (Bus busy) Siini arbiiter Siinide küsimine (Bus request) Seade 1 . . . Seade 2 Seade N Siinide kasutus õigus (Bus grant) Riistvaraline sinide arbitreerimine. Siini arbiiter Siinid hõivatud (Bus busy) Siinide küsimine (Bus request) Siinide kasutus õigus (Bus grant) Seade 1 Seade 2 . . . Seade N Aadressi liinid (Polling lines) Tsentraalne tearkvaraline siinide arbitreerimine. 3/19/2018 T. Evartson 58

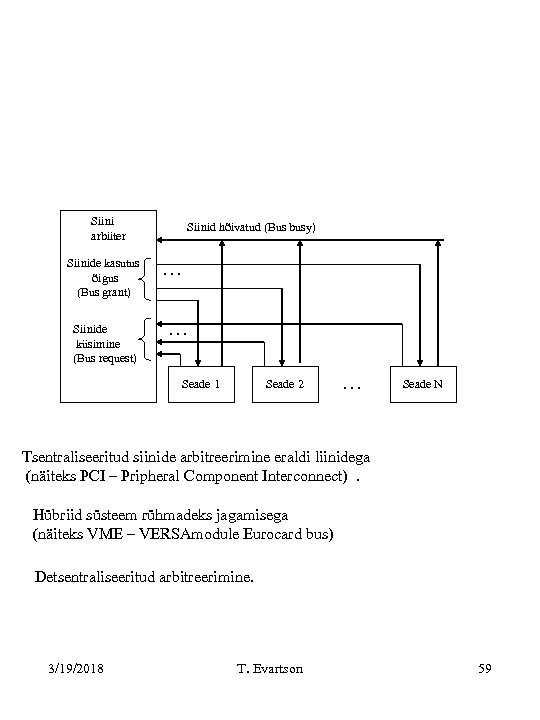

Siini arbiiter Siinide kasutus õigus (Bus grant) Siinide küsimine (Bus request) Siinid hõivatud (Bus busy) . . . Seade 1 Seade 2 . . . Seade N Tsentraliseeritud siinide arbitreerimine eraldi liinidega (näiteks PCI – Pripheral Component Interconnect). Hübriid süsteem rühmadeks jagamisega (näiteks VME – VERSAmodule Eurocard bus) Detsentraliseeritud arbitreerimine. 3/19/2018 T. Evartson 59

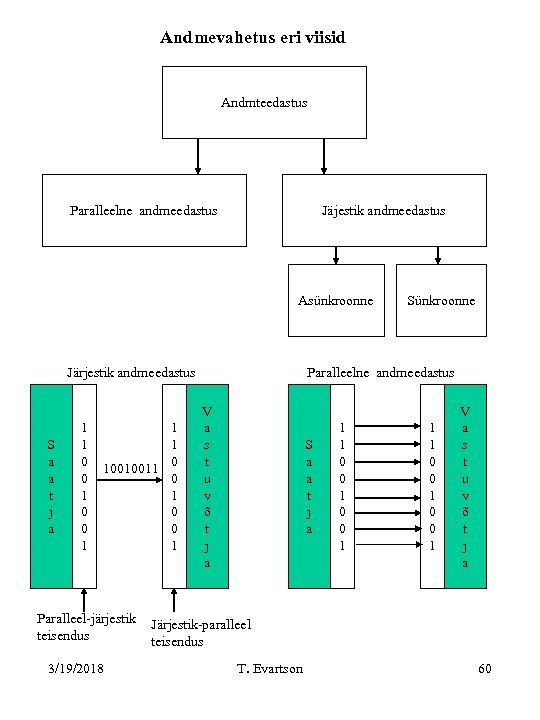

Andmevahetus eri viisid Andmteedastus Paralleelne andmeedastus Jäjestik andmeedastus Asünkroonne Järjestik andmeedastus S a a t j a 1 1 0 0 1 1 1 0 10010011 0 0 1 Paralleel-järjestik teisendus 3/19/2018 Sünkroonne Paralleelne andmeedastus V a s t u v õ t j a S a a t j a 1 1 0 0 1 V a s t u v õ t j a Järjestik-paralleel teisendus T. Evartson 60

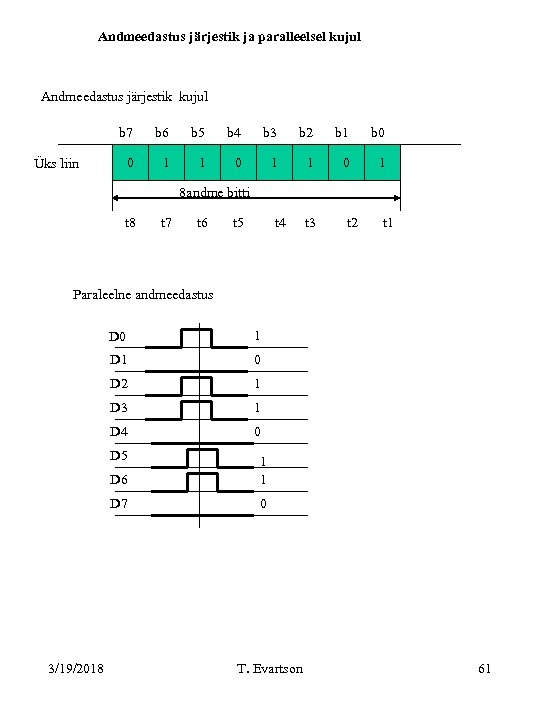

Andmeedastus järjestik ja paralleelsel kujul Andmeedastus järjestik kujul b 7 b 6 b 5 b 4 b 3 b 2 b 1 b 0 0 1 1 0 1 Üks liin 8 andme bitti t 8 t 7 t 6 t 5 t 4 t 3 t 2 t 1 Paraleelne andmeedastus D 0 1 D 1 0 D 2 1 D 3 1 D 4 0 D 5 D 6 D 7 3/19/2018 1 1 0 T. Evartson 61

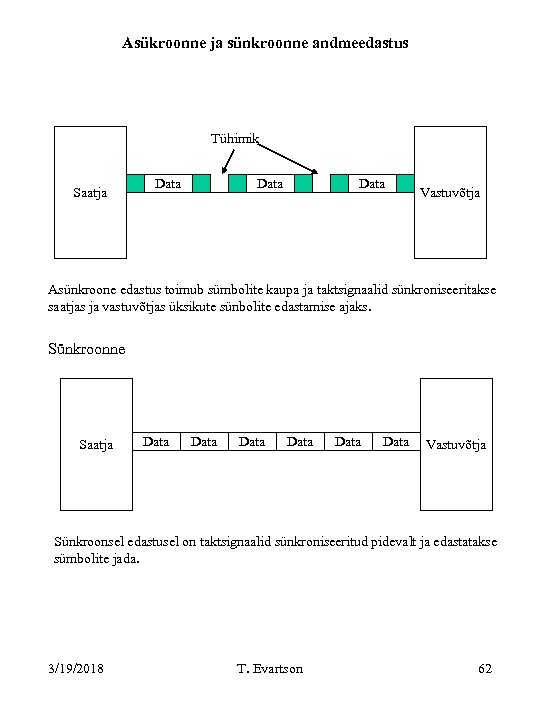

Asükroonne ja sünkroonne andmeedastus Tühimik Saatja Data Vastuvõtja Asünkroone edastus toimub sümbolite kaupa ja taktsignaalid sünkroniseeritakse saatjas ja vastuvõtjas üksikute sünbolite edastamise ajaks. Sünkroonne Saatja Data Data Vastuvõtja Sünkroonsel edastusel on taktsignaalid sünkroniseeritud pidevalt ja edastatakse sümbolite jada. 3/19/2018 T. Evartson 62

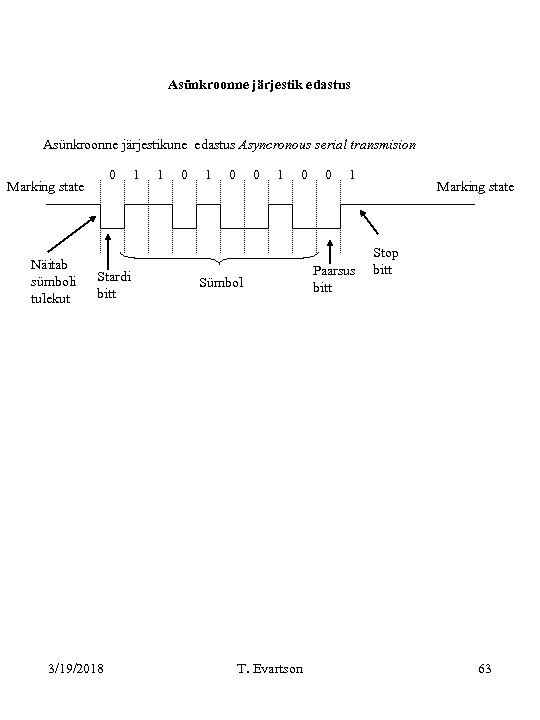

Asünkroonne järjestik edastus Asünkroonne järjestikune edastus Asyncronous serial transmision 0 Marking state Näitab sümboli tulekut Stardi bitt 3/19/2018 1 1 0 0 1 0 Sümbol T. Evartson 0 1 Paarsus bitt Marking state Stop bitt 63

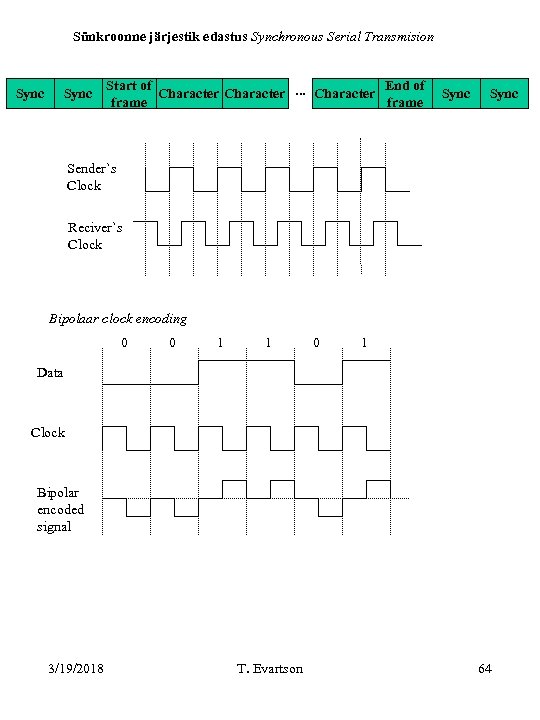

Sünkroonne järjestik edastus Synchronous Serial Transmision Sync Start of End of Character. . . Character frame Sync Sender`s Clock Reciver`s Clock Bipolaar clock encoding 0 0 1 1 0 1 Data Clock Bipolar encoded signal 3/19/2018 T. Evartson 64

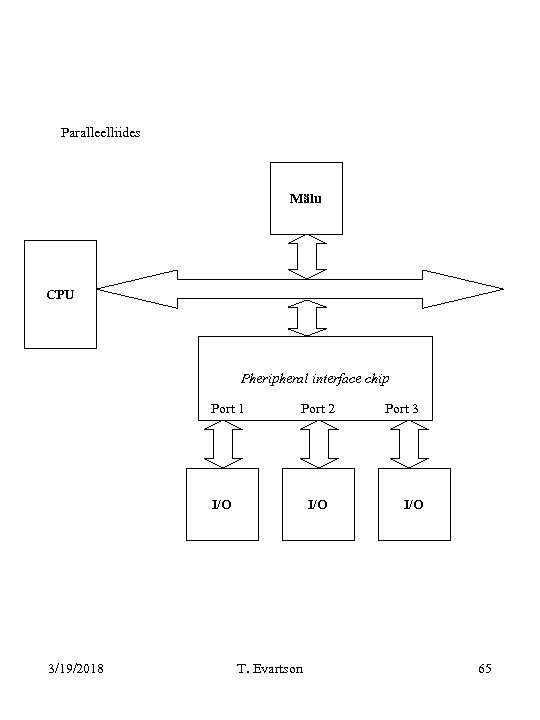

Paralleelliides Mälu CPU Pheripheral interface chip Port 1 Port 2 I/O 3/19/2018 I/O T. Evartson Port 3 I/O 65

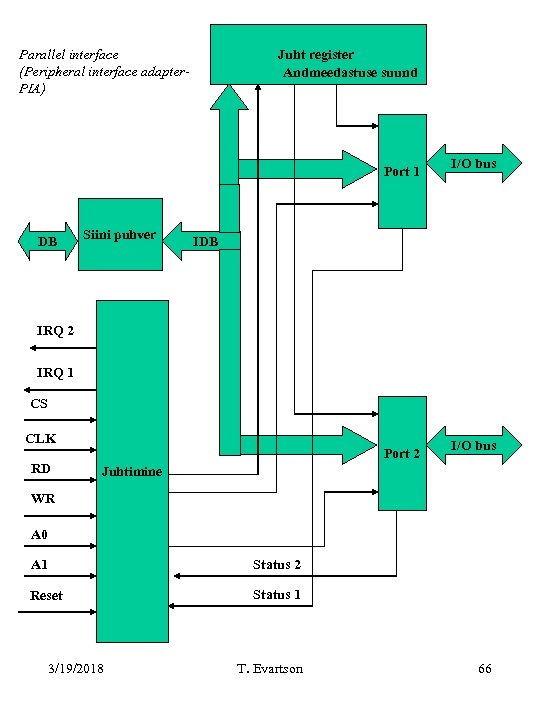

Parallel interface (Peripheral interface adapter. PIA) Juht register Andmeedastuse suund Port 1 DB Siini puhver I/O bus IDB IRQ 2 IRQ 1 CS CLK RD Port 2 I/O bus Juhtimine WR A 0 A 1 Status 2 Reset Status 1 3/19/2018 T. Evartson 66

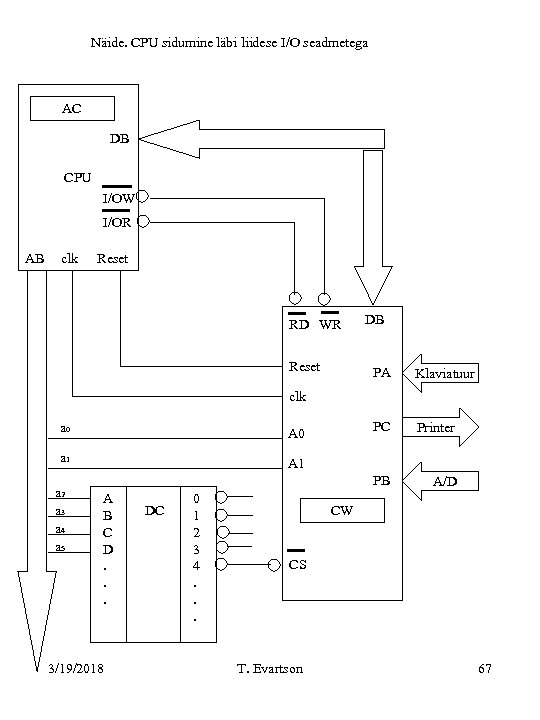

Näide. CPU sidumine läbi liidese I/O seadmetega AC DB CPU I/OW I/OR AB clk Reset RD WR Reset DB PA Klaviatuur PC Printer PB A/D clk a 0 A 0 a 1 A 1 a 2 a 3 a 4 a 5 A B C D. . . 3/19/2018 DC 0 1 2 3 4. . . CW CS T. Evartson 67

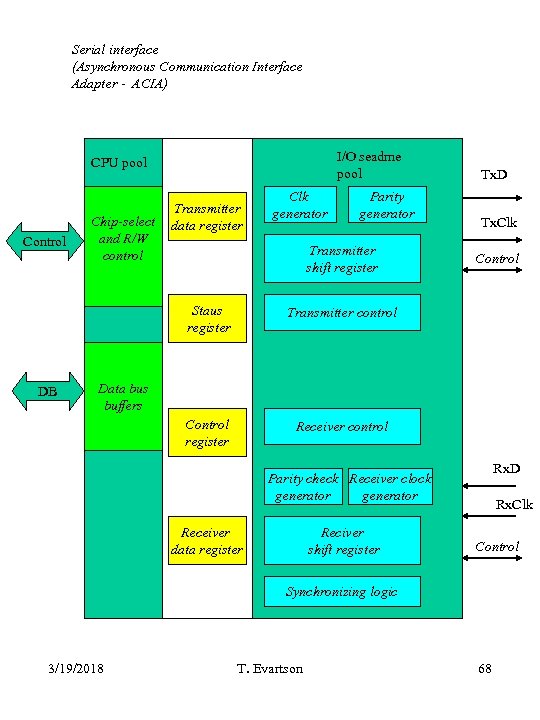

Serial interface (Asynchronous Communication Interface Adapter - ACIA) I/O seadme pool CPU pool Control Chip-select and R/W control Transmitter data register Clk generator Parity generator Transmitter shift register Staus register Tx. Clk Control Transmitter control Control register DB Tx. D Receiver control Data bus buffers Rx. D Parity check Receiver clock generator Receiver data register Reciver shift register Rx. Clk Control Synchronizing logic 3/19/2018 T. Evartson 68

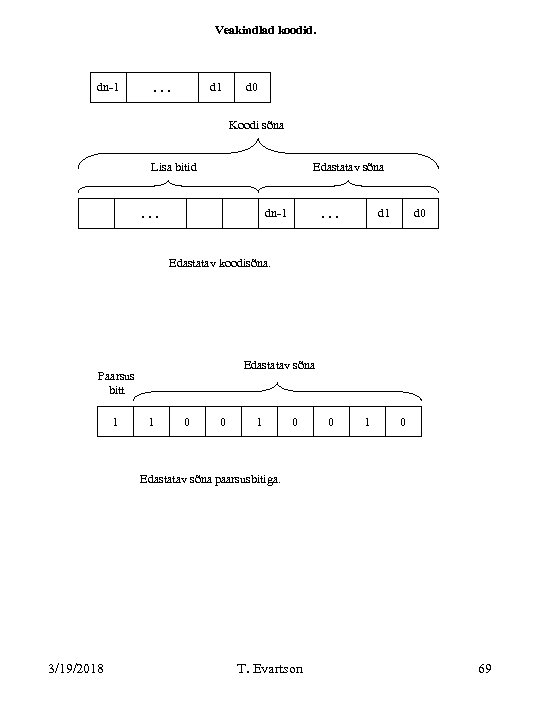

Veakindlad koodid. dn-1 . . . d 1 d 0 Koodi sõna Lisa bitid Edastatav sõna . . . dn-1 d 0 Edastatav koodisõna. Edastatav sõna Paarsus bitt 1 1 0 0 1 0 Edastatav sõna paarsusbitiga. 3/19/2018 T. Evartson 69

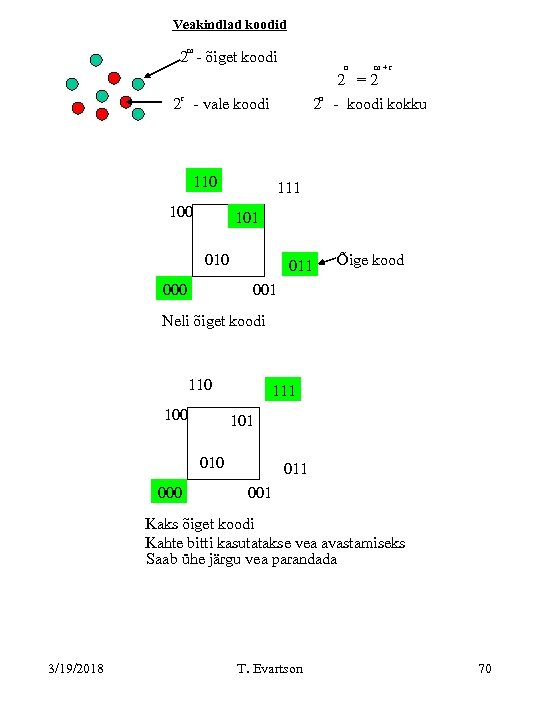

Veakindlad koodid m 2 - õiget koodi n 2 =2 2 n - koodi kokku 2 r - vale koodi 110 100 m+r 111 101 010 000 011 Õige kood 001 Neli õiget koodi 110 100 111 101 010 000 011 001 Kaks õiget koodi Kahte bitti kasutatakse vea avastamiseks Saab ühe järgu vea parandada 3/19/2018 T. Evartson 70

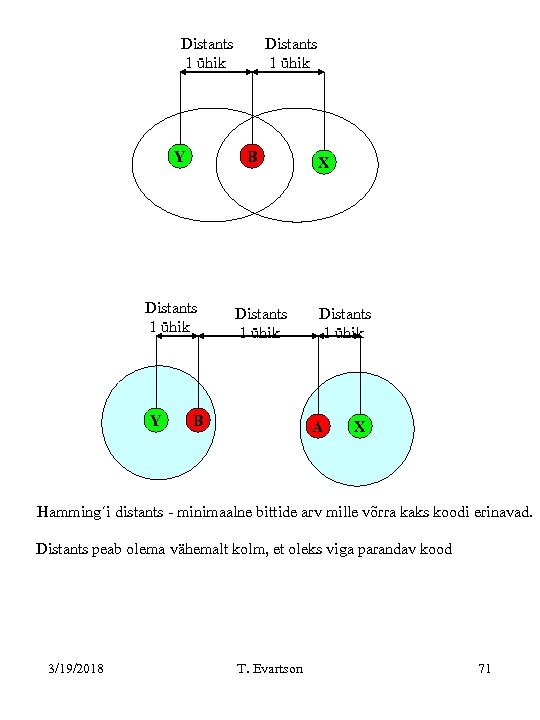

Distants 1 ühik Y B Distants 1 ühik Y Distants 1 ühik B X Distants 1 ühik A X Hamming´i distants - minimaalne bittide arv mille võrra kaks koodi erinavad. Distants peab olema vähemalt kolm, et oleks viga parandav kood 3/19/2018 T. Evartson 71

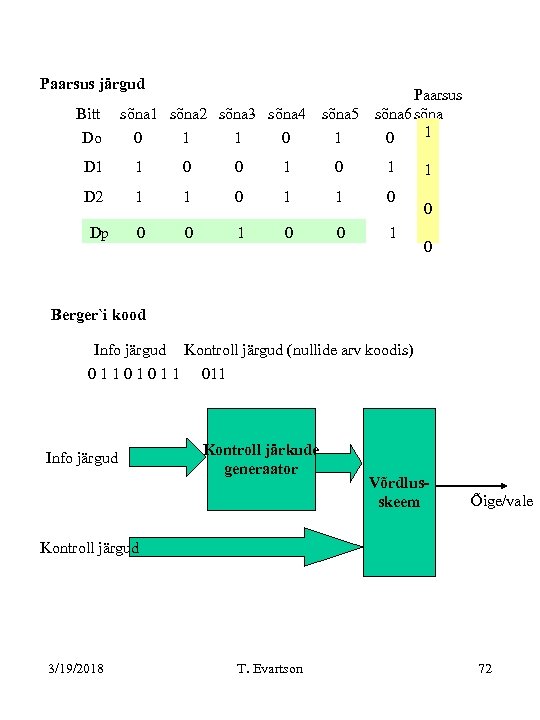

Paarsus järgud Bitt Do sõna 1 sõna 2 sõna 3 sõna 4 0 1 1 0 sõna 5 1 Paarsus sõna 6 sõna 1 0 D 1 1 0 0 1 D 2 1 1 0 0 0 1 Dp 1 0 0 Berger`i kood Info järgud Kontroll järgud (nullide arv koodis) 0 1 1 011 Info järgud Kontroll järkude generaator Võrdlusskeem Õige/vale Kontroll järgud 3/19/2018 T. Evartson 72

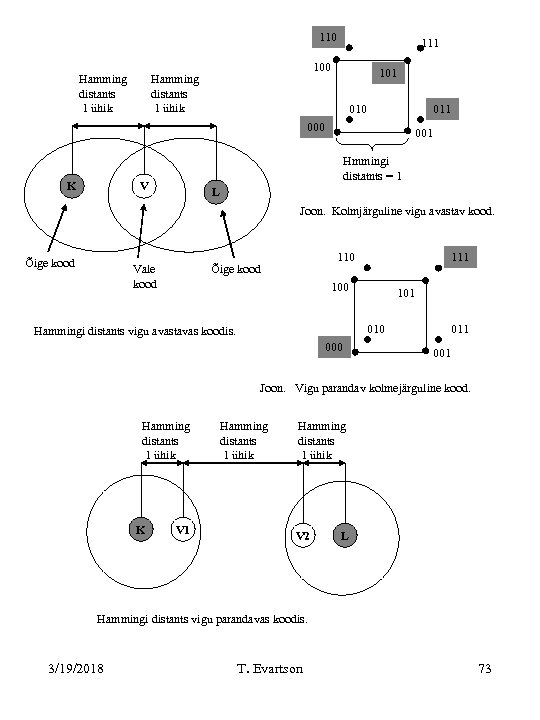

110 Hamming distants 1 ühik 111 100 Hamming distants 1 ühik 101 010 011 000 K 001 Hmmingi distatnts = 1 V L Joon. Kolmjärguline vigu avastav kood. Õige kood Vale kood 110 Õige kood 111 100 101 010 Hammingi distants vigu avastavas koodis. 000 011 001 Joon. Vigu parandav kolmejärguline kood. Hamming distants 1 ühik K V 1 Hamming distants 1 ühik V 2 L Hammingi distants vigu parandavas koodis. 3/19/2018 T. Evartson 73

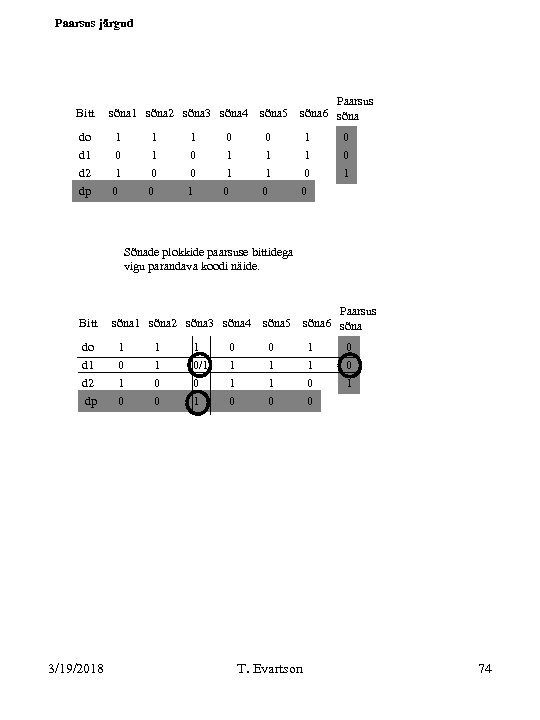

Paarsus järgud Bitt sõna 1 sõna 2 sõna 3 sõna 4 sõna 5 Paarsus sõna 6 sõna do d 1 d 2 dp 1 0 0 1 1 0 0 1 0 1 1 0 0 0 1 Sõnade plokkide paarsuse bittidega vigu parandava koodi näide. Bitt do d 1 d 2 dp 3/19/2018 sõna 1 sõna 2 sõna 3 sõna 4 1 0 1 1 0 0 1 0/1 0 1 1 0 sõna 5 0 1 1 0 T. Evartson Paarsus sõna 6 sõna 1 1 0 0 1 74

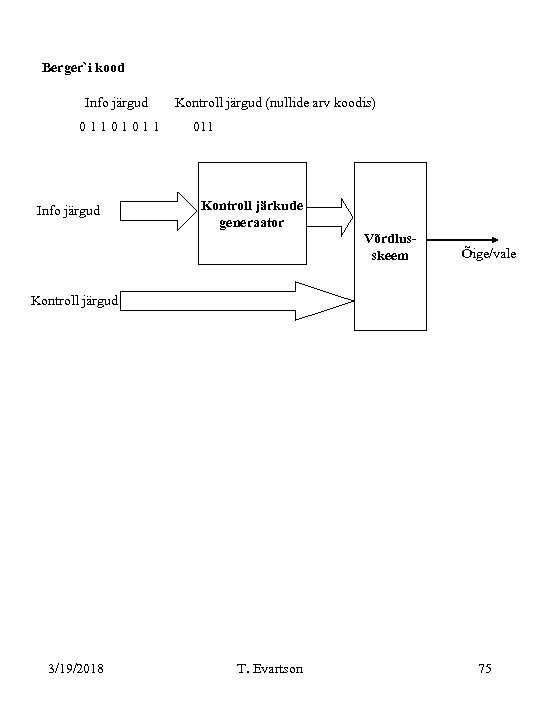

Berger`i kood Info järgud 01101011 Info järgud Kontroll järgud (nullide arv koodis) 011 Kontroll järkude generaator Võrdlusskeem Õige/vale Kontroll järgud 3/19/2018 T. Evartson 75

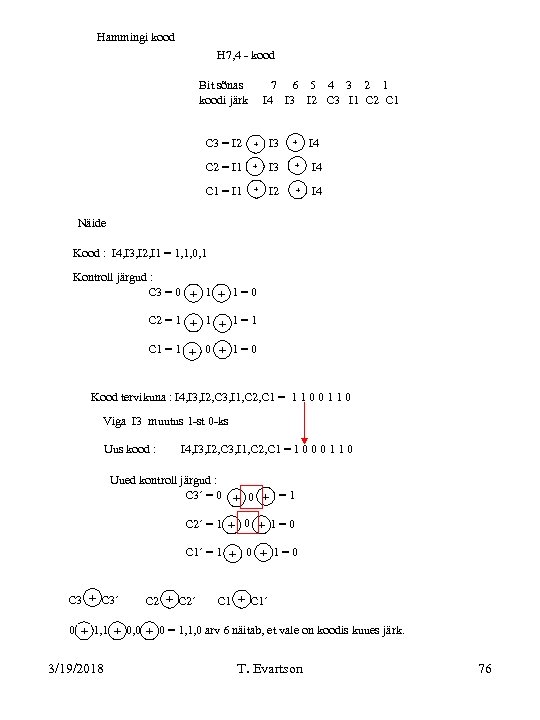

Hammingi kood H 7, 4 - kood Bit sõnas koodi järk 7 6 5 4 3 2 1 I 4 I 3 I 2 C 3 I 1 C 2 C 1 C 3 = I 2 + I 3 + I 4 C 2 = I 1 + I 3 + I 4 C 1 = I 1 + I 2 + I 4 Näide Kood : I 4, I 3, I 2, I 1 = 1, 1, 0, 1 Kontroll järgud : C 3 = 0 + 1 = 0 C 2 = 1 + 1 = 1 C 1 = 1 + 0 + 1 = 0 Kood tervikuna : I 4, I 3, I 2, C 3, I 1, C 2, C 1 = 1 1 0 0 1 1 0 Viga I 3 muutus 1 -st 0 -ks Uus kood : I 4, I 3, I 2, C 3, I 1, C 2, C 1 = 1 0 0 0 1 1 0 Uued kontroll järgud : C 3´ = 0 + 1 = 1 C 2´ = 1 + 0 + 1 = 0 C 1´ = 1 + 0 + 1 = 0 C 3 + C 3´ C 2 + C 2´ C 1 + C 1´ 0 + 1, 1 + 0, 0 + 0 = 1, 1, 0 arv 6 näitab, et vale on koodis kuues järk. 3/19/2018 T. Evartson 76

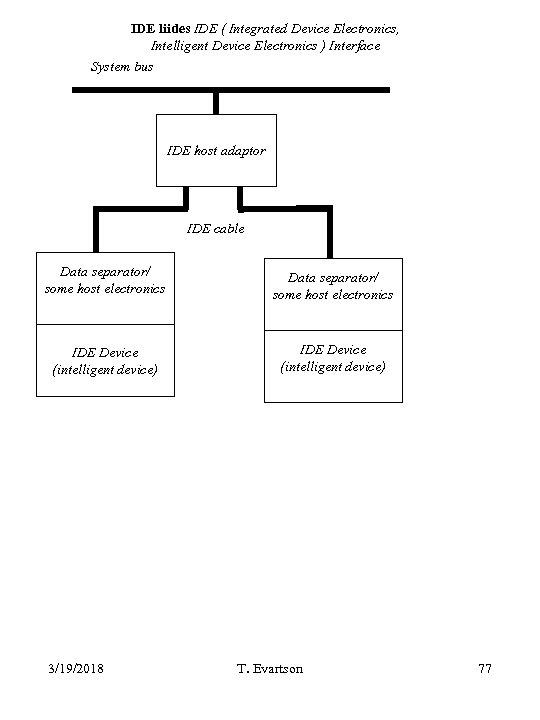

IDE liides IDE ( Integrated Device Electronics, Intelligent Device Electronics ) Interface System bus IDE host adaptor IDE cable Data separator/ some host electronics IDE Device (intelligent device) 3/19/2018 T. Evartson 77

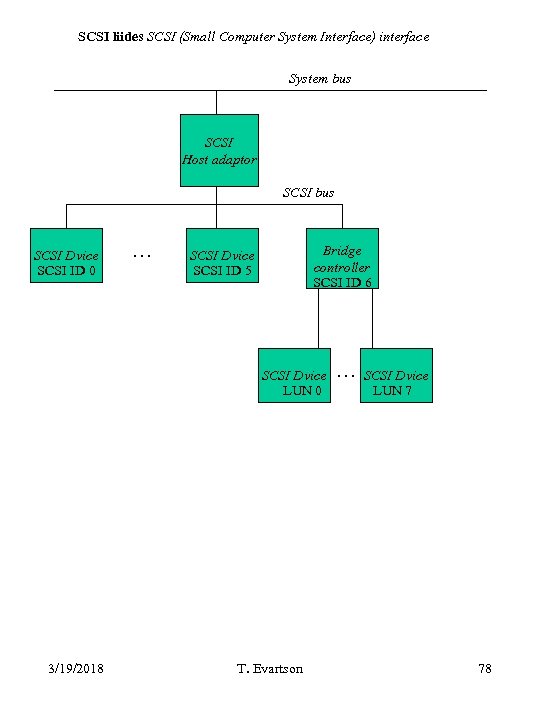

SCSI liides SCSI (Small Computer System Interface) interface System bus SCSI Host adaptor SCSI bus SCSI Dvice SCSI ID 0 . . . Bridge controller SCSI ID 6 SCSI Dvice SCSI ID 5 SCSI Dvice. . . SCSI Dvice LUN 0 LUN 7 3/19/2018 T. Evartson 78

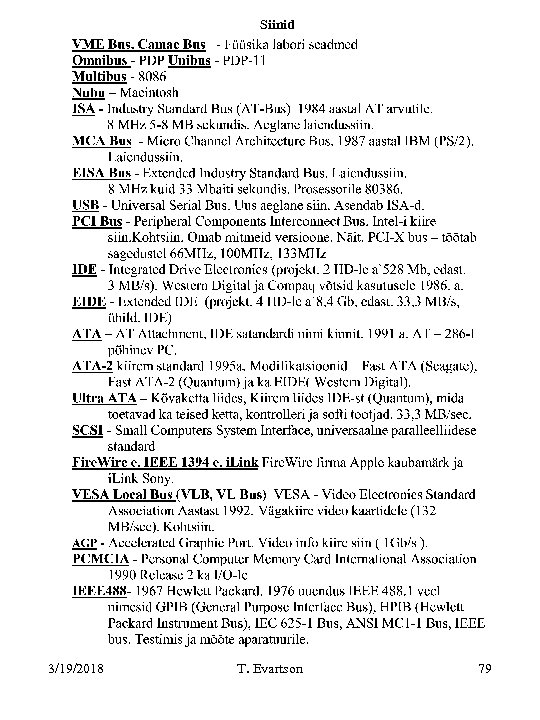

Siinid 3/19/2018 T. Evartson 79

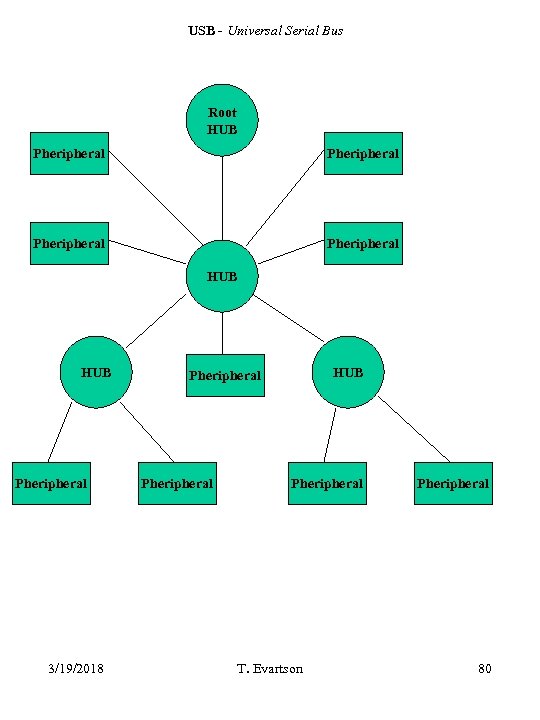

USB - Universal Serial Bus Root HUB Pheripheral HUB Pheripheral 3/19/2018 HUB Pheripheral T. Evartson Pheripheral 80

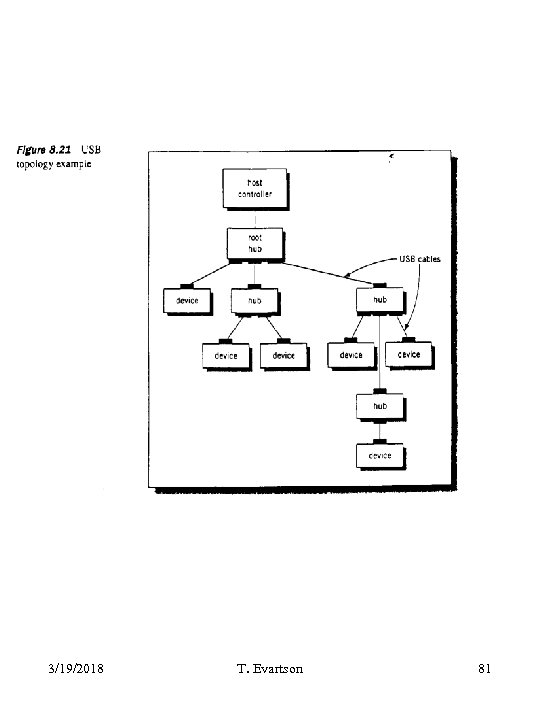

3/19/2018 T. Evartson 81

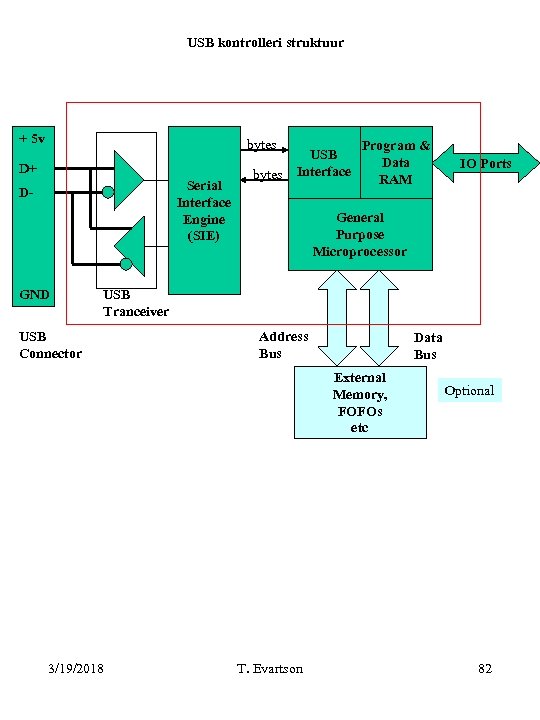

USB kontrolleri struktuur + 5 v bytes D+ Serial Interface Engine (SIE) D- GND bytes USB Interface Program & Data RAM IO Ports General Purpose Microprocessor USB Tranceiver USB Connector Address Bus Data Bus External Memory, FOFOs etc 3/19/2018 T. Evartson Optional 82

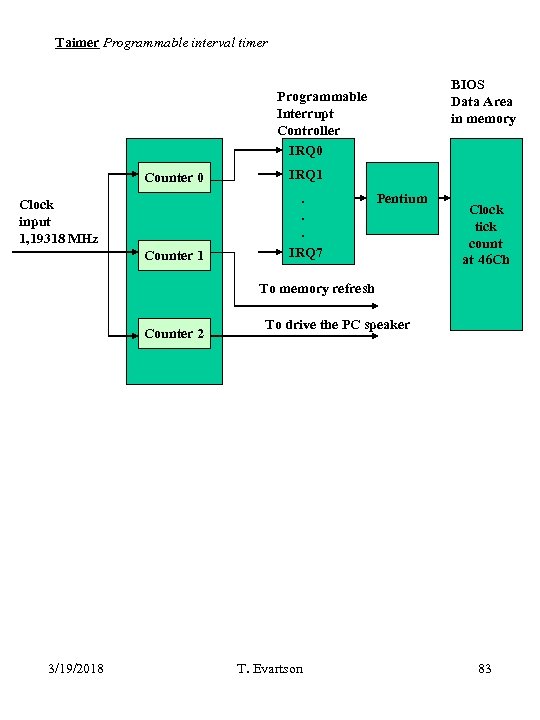

Taimer Programmable interval timer BIOS Data Area in memory Programmable Interrupt Controller IRQ 0 Counter 0 IRQ 1 Counter 1 . . . IRQ 7 Clock input 1, 19318 MHz Pentium Clock tick count at 46 Ch To memory refresh Counter 2 3/19/2018 To drive the PC speaker T. Evartson 83

4cf401307b1df33c915543a3b1454c5e.ppt