4d0ec6d458029bb9760b16111a4cf9e4.ppt

- Количество слайдов: 1

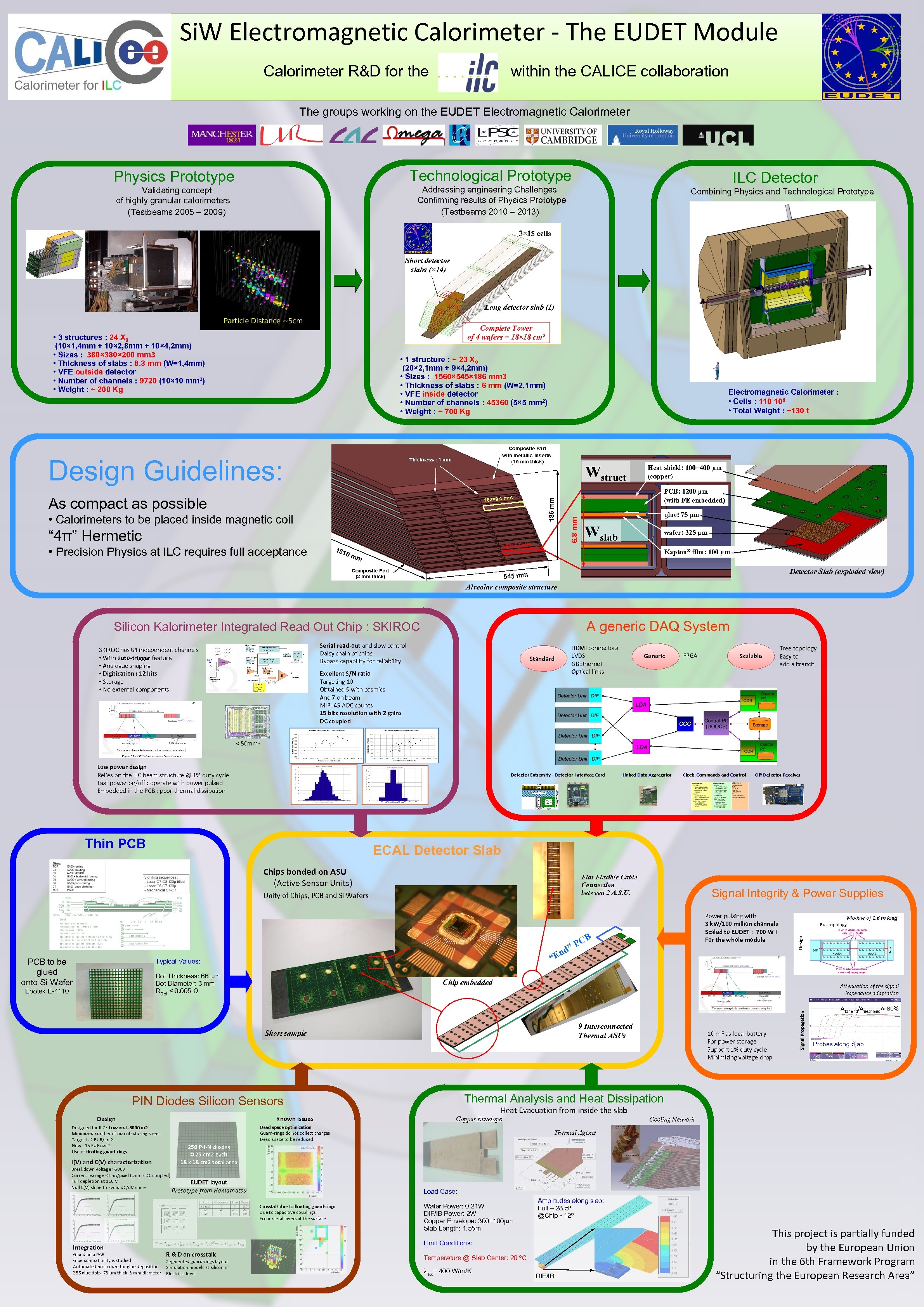

Si. W Electromagnetic Calorimeter - The EUDET Module Calorimeter R&D for the within the CALICE collaboration The groups working on the EUDET Electromagnetic Calorimeter Physics Prototype Technological Prototype Validating concept of highly granular calorimeters (Testbeams 2005 – 2009) Addressing engineering Challenges Confirming results of Physics Prototype (Testbeams 2010 – 2013) ILC Detector Combining Physics and Technological Prototype 3× 15 cells Short detector slabs (× 14) Long detector slab (1) Complete Tower of 4 wafers = 18× 18 cm 2 • 3 structures : 24 X 0 (10× 1, 4 mm + 10× 2, 8 mm + 10× 4, 2 mm) • Sizes : 380× 200 mm 3 • Thickness of slabs : 8. 3 mm (W=1, 4 mm) • VFE outside detector • Number of channels : 9720 (10× 10 mm 2) • Weight : ~ 200 Kg • 1 structure : ~ 23 X 0 (20× 2, 1 mm + 9× 4, 2 mm) • Sizes : 1560× 545× 186 mm 3 • Thickness of slabs : 6 mm (W=2, 1 mm) • VFE inside detector • Number of channels : 45360 (5× 5 mm 2) • Weight : ~ 700 Kg Composite Part with metallic inserts (15 mm thick) Thickness : 1 mm m As compact as possible • Calorimeters to be placed inside magnetic coil “ 4π” Hermetic • Precision Physics at ILC requires full acceptance m 182× 7, 3 m 151 Heat shield: 100+400 µm (copper) PCB: 1200 µm (with FE embedded) 186 mm 182× 9, 4 m Wstruct 6. 8 mm Design Guidelines: Electromagnetic Calorimeter : • Cells : 110 106 • Total Weight : ~130 t glue: 75 µm Wslab wafer: 325 µm Kapton® film: 100 µm 0 m m Composite Part (2 mm thick) Detector Slab (exploded view) 545 mm Alveolar composite structure A generic DAQ System Silicon Kalorimeter Integrated Read Out Chip : SKIROC Serial read-out and slow control Daisy chain of chips Bypass capability for reliability SKIROC has 64 independent channels • With auto-trigger feature • Analogue shaping • Digitization : 12 bits • Storage • No external components HDMI connectors LVDS GBEthernet Optical links Standard Excellent S/N ratio Targeting 10 Obtained 9 with cosmics And 7 on beam MIP=45 ADC counts 15 bits resolution with 2 gains DC coupled Generic FPGA Scalable Tree topology Easy to add a branch < 50 mm 2 Low power design Relies on the ILC beam structure @ 1% duty cycle Fast power on/off : operate with power pulsed Embedded in the PCB : poor thermal dissipation Detector Extremity - Detector Interface Card Thin PCB Flat Flexible Cable Connection between 2 A. S. U. ” d En Dot Thickness: 66 μm Dot Diameter: 3 mm RDot < 0. 005 Ω Known issues A. 9 Interconnected Thermal ASUs 10 m. F as local battery For power storage Support 1% duty cycle Minimizing voltage drop Signal Propagation Attenuation of the signal Impedance adaptation Afar End/Anear End ≈ 80% Probes along Slab Heat Evacuation from inside the slab Copper Envelope Dead space optimization Guard-rings do not collect charges Dead space to be reduced Cooling Network Thermal Agents 256 P-I-N diodes 0. 25 cm 2 each 18 x 18 cm 2 total area Breakdown voltage >500 V Current leakage <4 n. A/pixel (chip is DC coupled) Full depletion at 150 V Null C(V) slope to avoid d. C/d. V noise EUDET layout Prototype from Hamamatsu Load Case: Crosstalk due to floating guard-rings Due to capacitive couplings From metal layers at the surface Glued on a PCB Glue compatibility is studied Automated procedure for glue deposition 256 glue dots, 75 µm thick, 3 mm diameter Bus topology Module of 1. 6 m long Thermal Analysis and Heat Dissipation PIN Diodes Silicon Sensors I(V) and C(V) characterization CB P U. S. Short sample Designed for ILC : Low cost, 3000 m 2 Minimized number of manufacturing steps Target is 2 EUR/cm 2 Now : 15 EUR/cm 2 Use of floating guard-rings Power pulsing with 3 k. W/100 million channels Scaled to EUDET : 700 W ! For the whole module Chip embedded 7 Design Signal Integrity & Power Supplies “ Typical Values: Integration Off Detector Receiver Design Unity of Chips, PCB and Si Wafers Epotek E-4110 Clock, Commands and Control ECAL Detector Slab Chips bonded on ASU (Active Sensor Units) PCB to be glued onto Si Wafer Linked Data Aggregator Wafer Power: 0. 21 W DIF/IB Power: 2 W Copper Envelope: 300+100μm Slab Length: 1. 55 m Amplitudes along slab: Full – 28. 5 o @Chip - 12 o Limit Conditions: R & D on crosstalk Segmented guard-rings layout Simulation models at silicon or Electrical level Temperature @ Slab Center: 20 o. C λ Cu= 400 W/m/K DIF/IB This project is partially funded by the European Union in the 6 th Framework Program “Structuring the European Research Area”

Si. W Electromagnetic Calorimeter - The EUDET Module Calorimeter R&D for the within the CALICE collaboration The groups working on the EUDET Electromagnetic Calorimeter Physics Prototype Technological Prototype Validating concept of highly granular calorimeters (Testbeams 2005 – 2009) Addressing engineering Challenges Confirming results of Physics Prototype (Testbeams 2010 – 2013) ILC Detector Combining Physics and Technological Prototype 3× 15 cells Short detector slabs (× 14) Long detector slab (1) Complete Tower of 4 wafers = 18× 18 cm 2 • 3 structures : 24 X 0 (10× 1, 4 mm + 10× 2, 8 mm + 10× 4, 2 mm) • Sizes : 380× 200 mm 3 • Thickness of slabs : 8. 3 mm (W=1, 4 mm) • VFE outside detector • Number of channels : 9720 (10× 10 mm 2) • Weight : ~ 200 Kg • 1 structure : ~ 23 X 0 (20× 2, 1 mm + 9× 4, 2 mm) • Sizes : 1560× 545× 186 mm 3 • Thickness of slabs : 6 mm (W=2, 1 mm) • VFE inside detector • Number of channels : 45360 (5× 5 mm 2) • Weight : ~ 700 Kg Composite Part with metallic inserts (15 mm thick) Thickness : 1 mm m As compact as possible • Calorimeters to be placed inside magnetic coil “ 4π” Hermetic • Precision Physics at ILC requires full acceptance m 182× 7, 3 m 151 Heat shield: 100+400 µm (copper) PCB: 1200 µm (with FE embedded) 186 mm 182× 9, 4 m Wstruct 6. 8 mm Design Guidelines: Electromagnetic Calorimeter : • Cells : 110 106 • Total Weight : ~130 t glue: 75 µm Wslab wafer: 325 µm Kapton® film: 100 µm 0 m m Composite Part (2 mm thick) Detector Slab (exploded view) 545 mm Alveolar composite structure A generic DAQ System Silicon Kalorimeter Integrated Read Out Chip : SKIROC Serial read-out and slow control Daisy chain of chips Bypass capability for reliability SKIROC has 64 independent channels • With auto-trigger feature • Analogue shaping • Digitization : 12 bits • Storage • No external components HDMI connectors LVDS GBEthernet Optical links Standard Excellent S/N ratio Targeting 10 Obtained 9 with cosmics And 7 on beam MIP=45 ADC counts 15 bits resolution with 2 gains DC coupled Generic FPGA Scalable Tree topology Easy to add a branch < 50 mm 2 Low power design Relies on the ILC beam structure @ 1% duty cycle Fast power on/off : operate with power pulsed Embedded in the PCB : poor thermal dissipation Detector Extremity - Detector Interface Card Thin PCB Flat Flexible Cable Connection between 2 A. S. U. ” d En Dot Thickness: 66 μm Dot Diameter: 3 mm RDot < 0. 005 Ω Known issues A. 9 Interconnected Thermal ASUs 10 m. F as local battery For power storage Support 1% duty cycle Minimizing voltage drop Signal Propagation Attenuation of the signal Impedance adaptation Afar End/Anear End ≈ 80% Probes along Slab Heat Evacuation from inside the slab Copper Envelope Dead space optimization Guard-rings do not collect charges Dead space to be reduced Cooling Network Thermal Agents 256 P-I-N diodes 0. 25 cm 2 each 18 x 18 cm 2 total area Breakdown voltage >500 V Current leakage <4 n. A/pixel (chip is DC coupled) Full depletion at 150 V Null C(V) slope to avoid d. C/d. V noise EUDET layout Prototype from Hamamatsu Load Case: Crosstalk due to floating guard-rings Due to capacitive couplings From metal layers at the surface Glued on a PCB Glue compatibility is studied Automated procedure for glue deposition 256 glue dots, 75 µm thick, 3 mm diameter Bus topology Module of 1. 6 m long Thermal Analysis and Heat Dissipation PIN Diodes Silicon Sensors I(V) and C(V) characterization CB P U. S. Short sample Designed for ILC : Low cost, 3000 m 2 Minimized number of manufacturing steps Target is 2 EUR/cm 2 Now : 15 EUR/cm 2 Use of floating guard-rings Power pulsing with 3 k. W/100 million channels Scaled to EUDET : 700 W ! For the whole module Chip embedded 7 Design Signal Integrity & Power Supplies “ Typical Values: Integration Off Detector Receiver Design Unity of Chips, PCB and Si Wafers Epotek E-4110 Clock, Commands and Control ECAL Detector Slab Chips bonded on ASU (Active Sensor Units) PCB to be glued onto Si Wafer Linked Data Aggregator Wafer Power: 0. 21 W DIF/IB Power: 2 W Copper Envelope: 300+100μm Slab Length: 1. 55 m Amplitudes along slab: Full – 28. 5 o @Chip - 12 o Limit Conditions: R & D on crosstalk Segmented guard-rings layout Simulation models at silicon or Electrical level Temperature @ Slab Center: 20 o. C λ Cu= 400 W/m/K DIF/IB This project is partially funded by the European Union in the 6 th Framework Program “Structuring the European Research Area”