Шины микропроцессорных систем.ppt

- Количество слайдов: 47

Шины микропроцессорных систем Цель лекции: рассмотреть классификацию шин, синхронные шины, асинхронные шины, последовательные, пакетные, арбитраж, прерывания, ISA, EISA, PCIE, Hyper Transport.

Шины микропроцессорных систем Цель лекции: рассмотреть классификацию шин, синхронные шины, асинхронные шины, последовательные, пакетные, арбитраж, прерывания, ISA, EISA, PCIE, Hyper Transport.

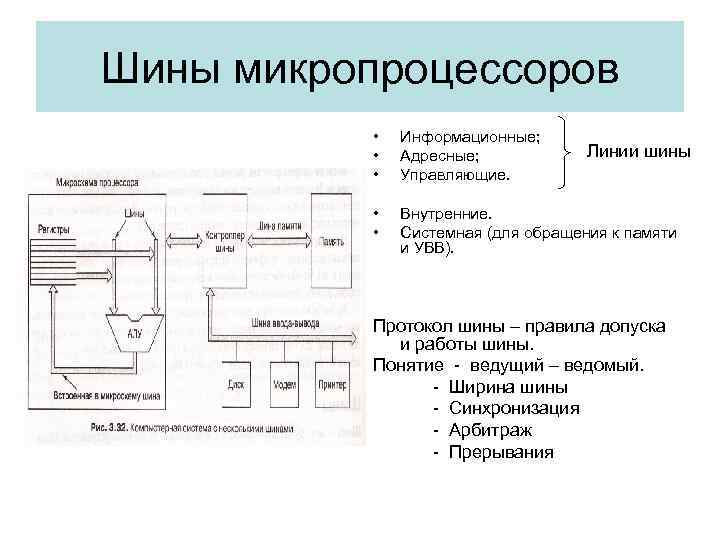

Шины микропроцессоров • • • Информационные; Адресные; Управляющие. • • Внутренние. Системная (для обращения к памяти и УВВ). Линии шины Протокол шины – правила допуска и работы шины. Понятие - ведущий – ведомый. - Ширина шины - Синхронизация - Арбитраж - Прерывания

Шины микропроцессоров • • • Информационные; Адресные; Управляющие. • • Внутренние. Системная (для обращения к памяти и УВВ). Линии шины Протокол шины – правила допуска и работы шины. Понятие - ведущий – ведомый. - Ширина шины - Синхронизация - Арбитраж - Прерывания

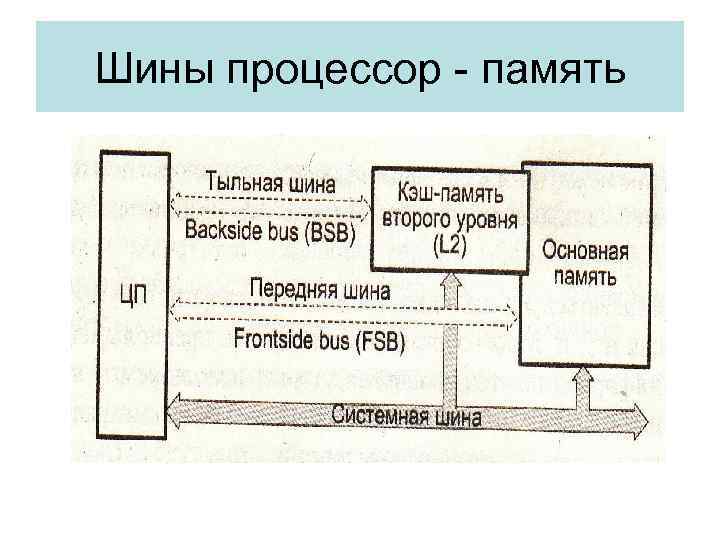

Шины процессор - память

Шины процессор - память

Стандарт шины Физические параметры: - разъемы; - разводка сигнальных линий. Электрические параметры: - напряжение; - уровни сигналов; Логические параметры: - типы циклов шины; - способ адресации.

Стандарт шины Физические параметры: - разъемы; - разводка сигнальных линий. Электрические параметры: - напряжение; - уровни сигналов; Логические параметры: - типы циклов шины; - способ адресации.

Разделение линий шины на группы • Группа линий адреса; • Группа линий данных; • Группа линий управления: - линии передачи информации состояния; - линии передачи прерываний; - линии передачи арбитража; - линии непосредственного управления; - линии синхронизации.

Разделение линий шины на группы • Группа линий адреса; • Группа линий данных; • Группа линий управления: - линии передачи информации состояния; - линии передачи прерываний; - линии передачи арбитража; - линии непосредственного управления; - линии синхронизации.

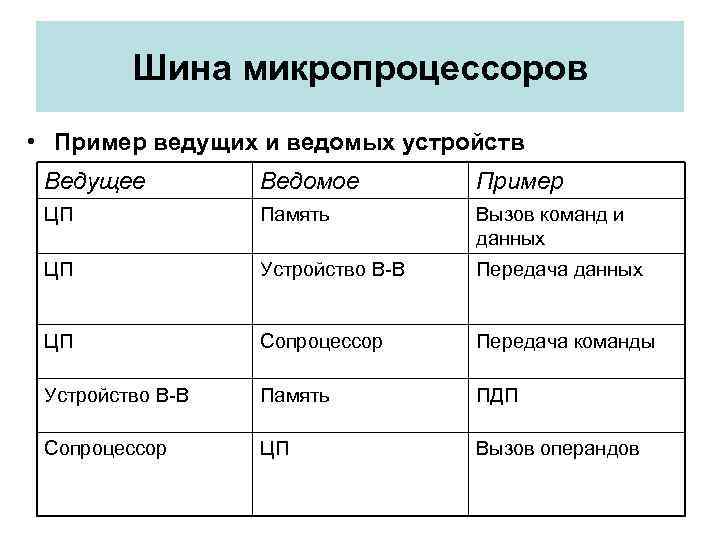

Шина микропроцессоров • Пример ведущих и ведомых устройств Ведущее Ведомое Пример ЦП Память Вызов команд и данных ЦП Устройство В-В Передача данных ЦП Сопроцессор Передача команды Устройство В-В Память ПДП Сопроцессор ЦП Вызов операндов

Шина микропроцессоров • Пример ведущих и ведомых устройств Ведущее Ведомое Пример ЦП Память Вызов команд и данных ЦП Устройство В-В Передача данных ЦП Сопроцессор Передача команды Устройство В-В Память ПДП Сопроцессор ЦП Вызов операндов

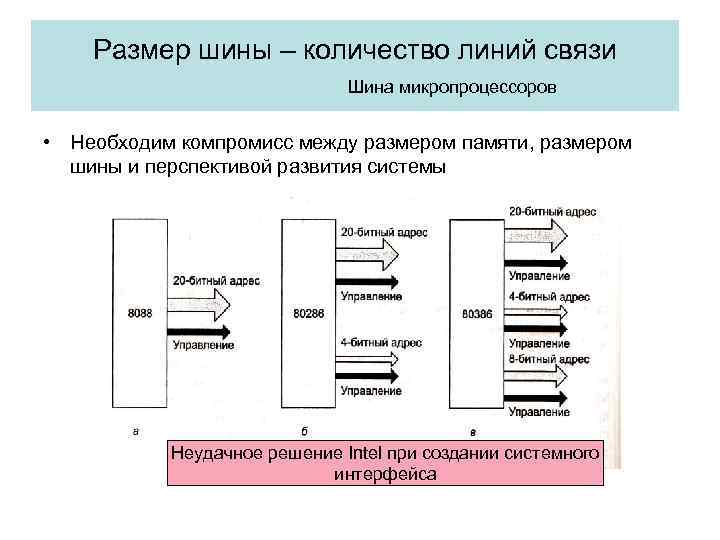

Размер шины – количество линий связи Шина микропроцессоров • Необходим компромисс между размером памяти, размером шины и перспективой развития системы Неудачное решение Intel при создании системного интерфейса

Размер шины – количество линий связи Шина микропроцессоров • Необходим компромисс между размером памяти, размером шины и перспективой развития системы Неудачное решение Intel при создании системного интерфейса

Производительность шины Шина микропроцессоров Способы увеличения производительности: - сокращение цикла шины; - увеличение размера шины; - пакетный- способ передачи. - применение иерархии шин. ПРОБЛЕМЫ – перекос шины и несовместимость внешних устройств. ВАРИАНТ уменьшения количества линий - МУЛЬТИПЛЕКСИРОВАНИЕ

Производительность шины Шина микропроцессоров Способы увеличения производительности: - сокращение цикла шины; - увеличение размера шины; - пакетный- способ передачи. - применение иерархии шин. ПРОБЛЕМЫ – перекос шины и несовместимость внешних устройств. ВАРИАНТ уменьшения количества линий - МУЛЬТИПЛЕКСИРОВАНИЕ

Общая классификация шин - Синхронные; - Асинхронные; - Параллельные; - Последовательные; - Однонаправленные; - Двунаправленные; - Дуплексные; - Симплексные

Общая классификация шин - Синхронные; - Асинхронные; - Параллельные; - Последовательные; - Однонаправленные; - Двунаправленные; - Дуплексные; - Симплексные

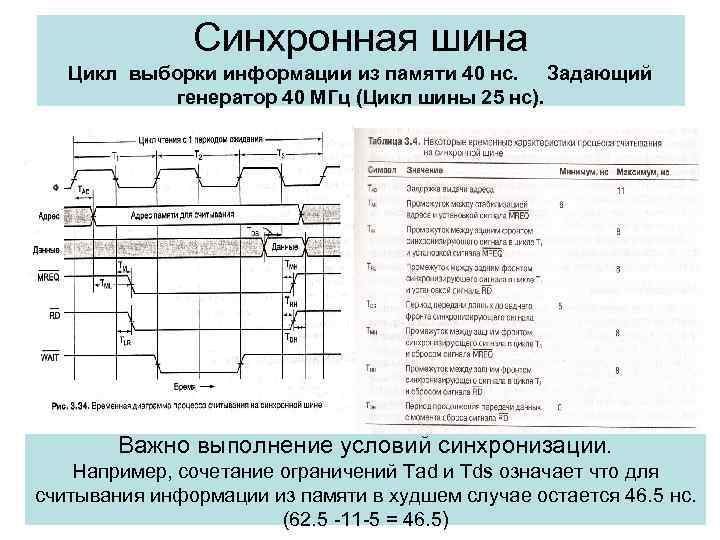

Синхронная шина Цикл выборки информации из памяти 40 нс. Задающий генератор 40 МГц (Цикл шины 25 нс). Важно выполнение условий синхронизации. Например, сочетание ограничений Тad и Tds означает что для считывания информации из памяти в худшем случае остается 46. 5 нс. (62. 5 -11 -5 = 46. 5)

Синхронная шина Цикл выборки информации из памяти 40 нс. Задающий генератор 40 МГц (Цикл шины 25 нс). Важно выполнение условий синхронизации. Например, сочетание ограничений Тad и Tds означает что для считывания информации из памяти в худшем случае остается 46. 5 нс. (62. 5 -11 -5 = 46. 5)

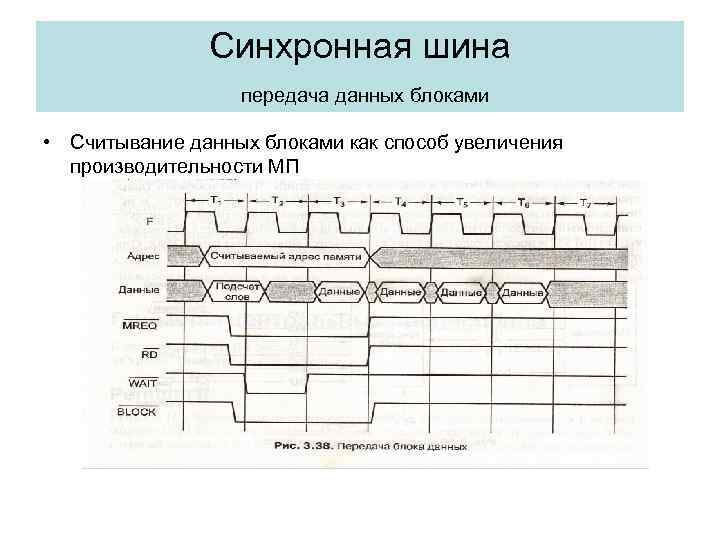

Синхронная шина передача данных блоками • Считывание данных блоками как способ увеличения производительности МП

Синхронная шина передача данных блоками • Считывание данных блоками как способ увеличения производительности МП

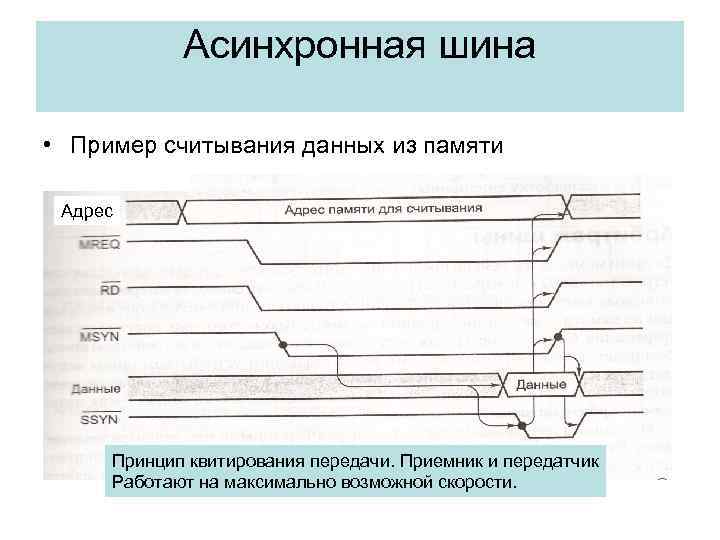

Асинхронная шина • Пример считывания данных из памяти Адрес Принцип квитирования передачи. Приемник и передатчик Работают на максимально возможной скорости.

Асинхронная шина • Пример считывания данных из памяти Адрес Принцип квитирования передачи. Приемник и передатчик Работают на максимально возможной скорости.

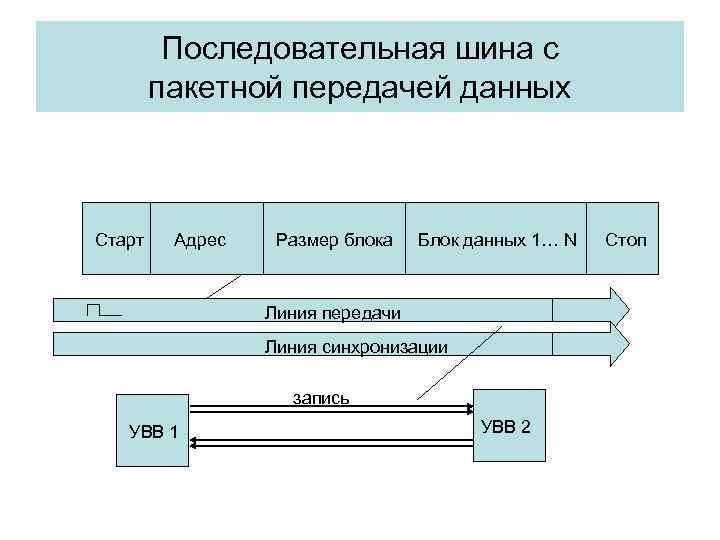

Последовательная шина с пакетной передачей данных Старт Адрес Размер блока Блок данных 1… N Линия передачи Линия синхронизации запись УВВ 1 УВВ 2 Стоп

Последовательная шина с пакетной передачей данных Старт Адрес Размер блока Блок данных 1… N Линия передачи Линия синхронизации запись УВВ 1 УВВ 2 Стоп

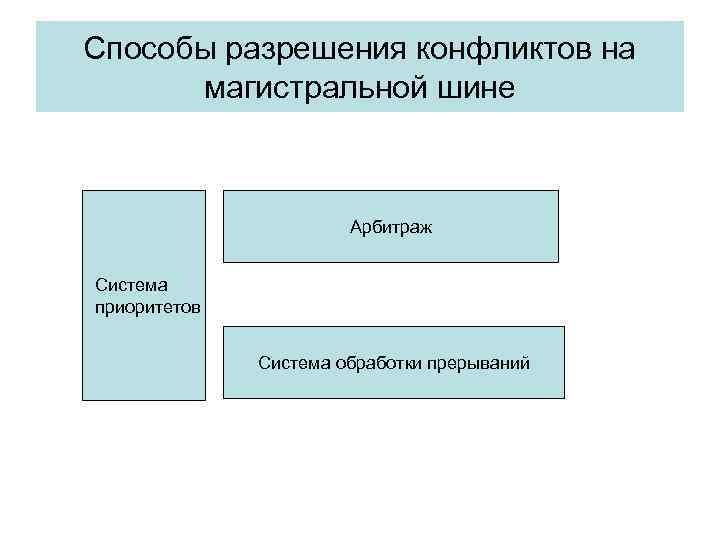

Способы разрешения конфликтов на магистральной шине Арбитраж Система приоритетов Система обработки прерываний

Способы разрешения конфликтов на магистральной шине Арбитраж Система приоритетов Система обработки прерываний

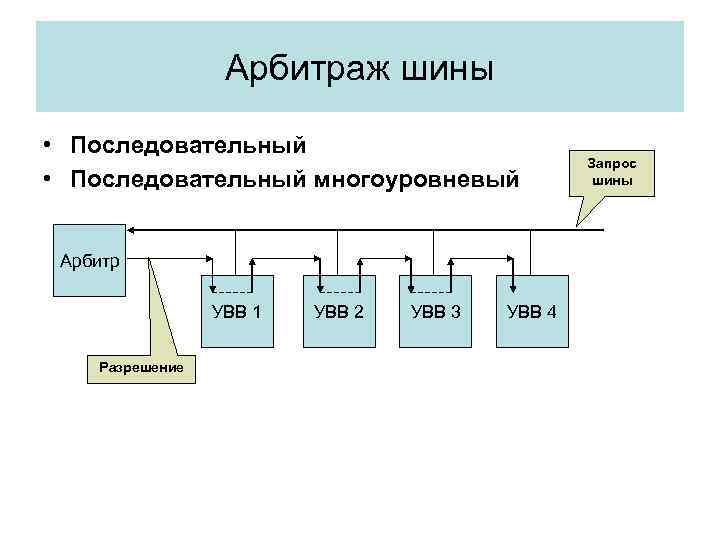

Арбитраж шины • Последовательный многоуровневый Арбитр УВВ 1 Разрешение УВВ 2 УВВ 3 УВВ 4 Запрос шины

Арбитраж шины • Последовательный многоуровневый Арбитр УВВ 1 Разрешение УВВ 2 УВВ 3 УВВ 4 Запрос шины

Арбитраж шины – Децентрализованный in out УВВ 1 Линия арбитра +5 в in out УВВ 2 in out УВВ 3 Запрос шины in out УВВ 4 Шина занята

Арбитраж шины – Децентрализованный in out УВВ 1 Линия арбитра +5 в in out УВВ 2 in out УВВ 3 Запрос шины in out УВВ 4 Шина занята

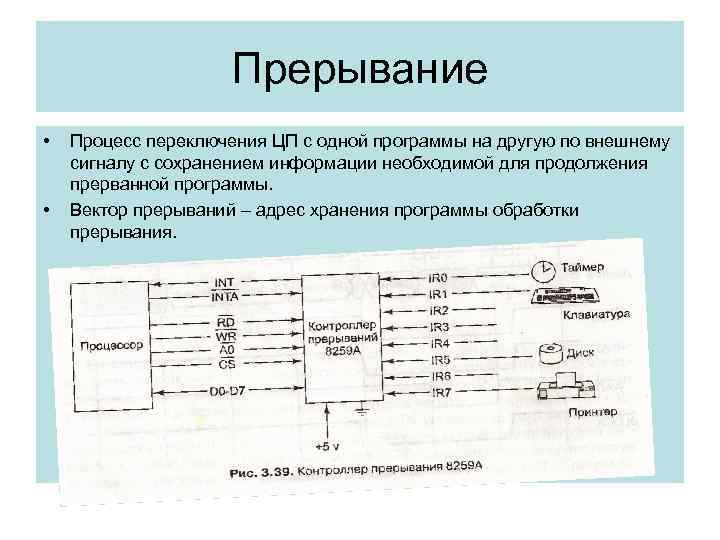

Прерывание • • Процесс переключения ЦП с одной программы на другую по внешнему сигналу с сохранением информации необходимой для продолжения прерванной программы. Вектор прерываний – адрес хранения программы обработки прерывания.

Прерывание • • Процесс переключения ЦП с одной программы на другую по внешнему сигналу с сохранением информации необходимой для продолжения прерванной программы. Вектор прерываний – адрес хранения программы обработки прерывания.

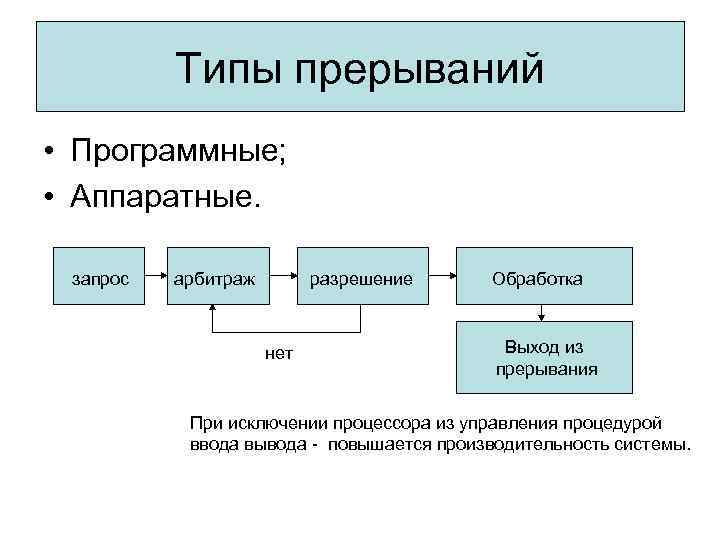

Типы прерываний • Программные; • Аппаратные. запрос арбитраж разрешение нет Обработка Выход из прерывания При исключении процессора из управления процедурой ввода вывода - повышается производительность системы.

Типы прерываний • Программные; • Аппаратные. запрос арбитраж разрешение нет Обработка Выход из прерывания При исключении процессора из управления процедурой ввода вывода - повышается производительность системы.

Шины универсальных МП Стандарт Год Типичное применение Пиковая пропускная способность Примечание ISAEISA 1981 – 1988 Звуковые карты Модемы, адаптеры SCSI 2 – 8. 33 – 33 Мбайт с Используется редко, замещается PCI и РС104 PCI 1991 – 1997 Внешние устройства 133 Мбайт с 32 бита на частоте 33 МГц Для ВУ PCI-X 1993 – 1997 Универсальный 1 Гбайт с 64 бита на частоте 133 МГц Увеличено количество подключаемых ВУ PCI-E 1997 – 2011 Универсальный До 16 Гбайт с Последовательная Гипер. Транспорт 2001 – 2011 Универсальный До 51. 6 Гбайт с Двунаправленная, П оследовательнопараллельная.

Шины универсальных МП Стандарт Год Типичное применение Пиковая пропускная способность Примечание ISAEISA 1981 – 1988 Звуковые карты Модемы, адаптеры SCSI 2 – 8. 33 – 33 Мбайт с Используется редко, замещается PCI и РС104 PCI 1991 – 1997 Внешние устройства 133 Мбайт с 32 бита на частоте 33 МГц Для ВУ PCI-X 1993 – 1997 Универсальный 1 Гбайт с 64 бита на частоте 133 МГц Увеличено количество подключаемых ВУ PCI-E 1997 – 2011 Универсальный До 16 Гбайт с Последовательная Гипер. Транспорт 2001 – 2011 Универсальный До 51. 6 Гбайт с Двунаправленная, П оследовательнопараллельная.

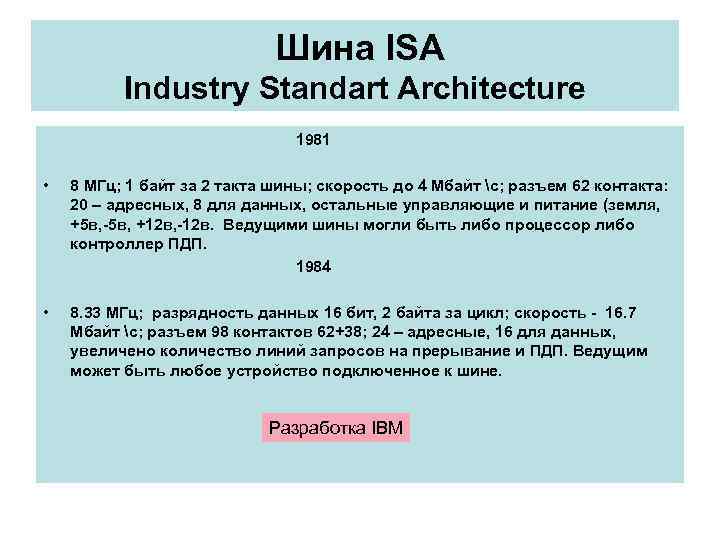

Шина ISA Industry Standart Architecture 1981 • 8 МГц; 1 байт за 2 такта шины; скорость до 4 Мбайт с; разъем 62 контакта: 20 – адресных, 8 для данных, остальные управляющие и питание (земля, +5 в, -5 в, +12 в, -12 в. Ведущими шины могли быть либо процессор либо контроллер ПДП. 1984 • 8. 33 МГц; разрядность данных 16 бит, 2 байта за цикл; скорость - 16. 7 Мбайт с; разъем 98 контактов 62+38; 24 – адресные, 16 для данных, увеличено количество линий запросов на прерывание и ПДП. Ведущим может быть любое устройство подключенное к шине. Разработка IBM

Шина ISA Industry Standart Architecture 1981 • 8 МГц; 1 байт за 2 такта шины; скорость до 4 Мбайт с; разъем 62 контакта: 20 – адресных, 8 для данных, остальные управляющие и питание (земля, +5 в, -5 в, +12 в, -12 в. Ведущими шины могли быть либо процессор либо контроллер ПДП. 1984 • 8. 33 МГц; разрядность данных 16 бит, 2 байта за цикл; скорость - 16. 7 Мбайт с; разъем 98 контактов 62+38; 24 – адресные, 16 для данных, увеличено количество линий запросов на прерывание и ПДП. Ведущим может быть любое устройство подключенное к шине. Разработка IBM

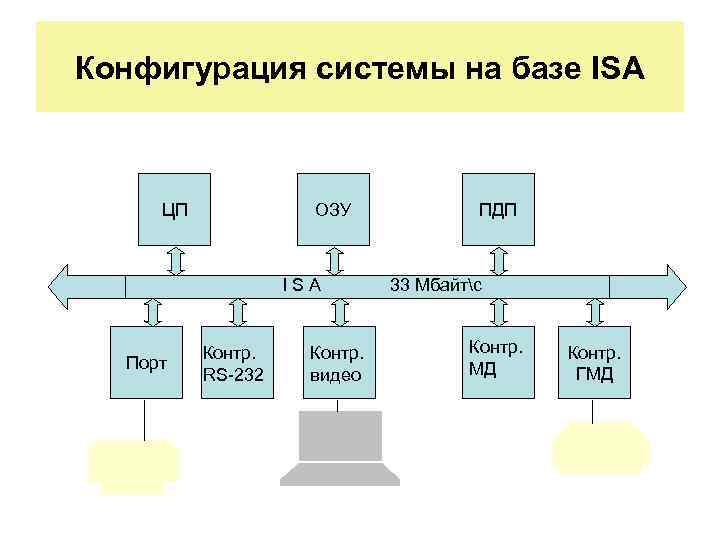

Конфигурация системы на базе ISA ЦП ОЗУ ISA Порт Контр. RS-232 Контр. видео ПДП 33 Мбайтс Контр. МД Контр. ГМД

Конфигурация системы на базе ISA ЦП ОЗУ ISA Порт Контр. RS-232 Контр. видео ПДП 33 Мбайтс Контр. МД Контр. ГМД

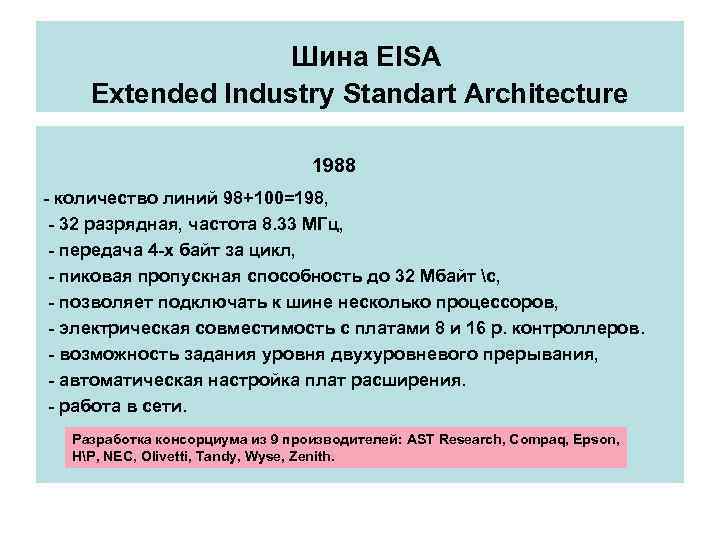

Шина EISA Extended Industry Standart Architecture 1988 - количество линий 98+100=198, - 32 разрядная, частота 8. 33 МГц, - передача 4 -х байт за цикл, - пиковая пропускная способность до 32 Мбайт с, - позволяет подключать к шине несколько процессоров, - электрическая совместимость с платами 8 и 16 р. контроллеров. - возможность задания уровня двухуровневого прерывания, - автоматическая настройка плат расширения. - работа в сети. Разработка консорциума из 9 производителей: AST Research, Compaq, Epson, HP, NEC, Olivetti, Tandy, Wyse, Zenith.

Шина EISA Extended Industry Standart Architecture 1988 - количество линий 98+100=198, - 32 разрядная, частота 8. 33 МГц, - передача 4 -х байт за цикл, - пиковая пропускная способность до 32 Мбайт с, - позволяет подключать к шине несколько процессоров, - электрическая совместимость с платами 8 и 16 р. контроллеров. - возможность задания уровня двухуровневого прерывания, - автоматическая настройка плат расширения. - работа в сети. Разработка консорциума из 9 производителей: AST Research, Compaq, Epson, HP, NEC, Olivetti, Tandy, Wyse, Zenith.

Шина LPT - Low Pin Count Предложена фирмой Intel в 1998 г. для замены ISA. Используется для подключения низкоскоростных устройств. - 30 линий вместо 72 у ISA; - 4 линии для передачи мультиплексированного сигнала адреса и данных; - 3 линии управления: кадр, сброс, синхронизация. - Частота 33 МГц как у ISA.

Шина LPT - Low Pin Count Предложена фирмой Intel в 1998 г. для замены ISA. Используется для подключения низкоскоростных устройств. - 30 линий вместо 72 у ISA; - 4 линии для передачи мультиплексированного сигнала адреса и данных; - 3 линии управления: кадр, сброс, синхронизация. - Частота 33 МГц как у ISA.

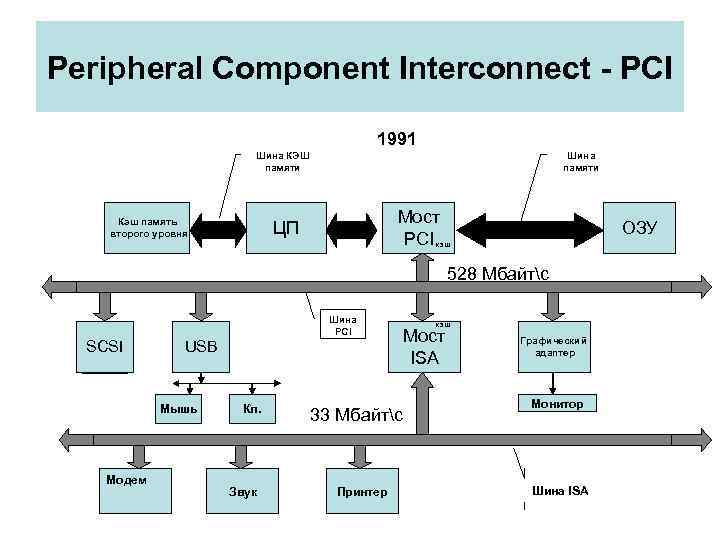

Peripheral Component Interconnect - PCI 1991 Шина КЭШ памяти Кэш память второго уровня Шина памяти Мост PCI кэш ЦП ОЗУ 528 Мбайтс Шина PCI SCSI USB Мышь Модем Кл. Звук 33 Мбайтс Принтер кэш Мост ISA Графический адаптер Монитор Шина ISA

Peripheral Component Interconnect - PCI 1991 Шина КЭШ памяти Кэш память второго уровня Шина памяти Мост PCI кэш ЦП ОЗУ 528 Мбайтс Шина PCI SCSI USB Мышь Модем Кл. Звук 33 Мбайтс Принтер кэш Мост ISA Графический адаптер Монитор Шина ISA

Возможности шины PCI • • Синхронный 32 или 64 разрядный обмен данными с мультиплексированием; Частота работы шины 33 или 66 МГц; Широкий диапазон скорости обмена от 132 до 528 Мбайт с. Поддерживает два вида плат 120 или 184 вывода. Типы слотов: 5 в 32 -бит; 3. 3 в 32 бит; 5 в 64 бит; 3. 3 в 64 бит. Пакетный режим обмена. Поддержка режимов кэширования и межмашинных мостов. Поддержка режима автоматической настройки (Plug and Play). Модификации - PCI 64, PCI 6664 - PCI- XT - 64 разрядный обмен на частоте 133 МГц. Ограничения по количеству подключаемых к шине устройств: 66 МГц - 4; 100 МГц – 2; свыше 133 МГЦ -1.

Возможности шины PCI • • Синхронный 32 или 64 разрядный обмен данными с мультиплексированием; Частота работы шины 33 или 66 МГц; Широкий диапазон скорости обмена от 132 до 528 Мбайт с. Поддерживает два вида плат 120 или 184 вывода. Типы слотов: 5 в 32 -бит; 3. 3 в 32 бит; 5 в 64 бит; 3. 3 в 64 бит. Пакетный режим обмена. Поддержка режимов кэширования и межмашинных мостов. Поддержка режима автоматической настройки (Plug and Play). Модификации - PCI 64, PCI 6664 - PCI- XT - 64 разрядный обмен на частоте 133 МГц. Ограничения по количеству подключаемых к шине устройств: 66 МГц - 4; 100 МГц – 2; свыше 133 МГЦ -1.

Обязательные сигналы шины PCI • • CLK AD PAR CBE# • FRAME# IRDY# 1 1 IDSEL DEVSEL# TRDY# 1 1 1 STOP# 1 PERR# SERR# REQ# GNT# RST# 1 1 1 32 1 4 Тактовый генератор. шины адреса и данных. Бит четности для адреса или данных. 1) команда шине 2) битовый массив, показывающий какие байты из слова нужно считать или записать. Установлены сигналы AD и CBE#. При чтении: задающее устройство готово принять данные. При записи: данные находятся на шине. Считывание пространства конфигураций. Подчиненное устройство распознало свой адрес и ждет сигнала. При чтении: данные находятся на линии AD. При записи: подчиненное устройство готово принять данные. Подчиненное устройство требует немедленно прервать текущую транзакцию. Обнаружена ошибка четности данных. Обнаружена ошибка четности адреса или системная ошибка. Арбитраж шины: запрос на доступ к шине. Арбитраж шины: предоставление шины. Перезагрузка системы и всех устройств.

Обязательные сигналы шины PCI • • CLK AD PAR CBE# • FRAME# IRDY# 1 1 IDSEL DEVSEL# TRDY# 1 1 1 STOP# 1 PERR# SERR# REQ# GNT# RST# 1 1 1 32 1 4 Тактовый генератор. шины адреса и данных. Бит четности для адреса или данных. 1) команда шине 2) битовый массив, показывающий какие байты из слова нужно считать или записать. Установлены сигналы AD и CBE#. При чтении: задающее устройство готово принять данные. При записи: данные находятся на шине. Считывание пространства конфигураций. Подчиненное устройство распознало свой адрес и ждет сигнала. При чтении: данные находятся на линии AD. При записи: подчиненное устройство готово принять данные. Подчиненное устройство требует немедленно прервать текущую транзакцию. Обнаружена ошибка четности данных. Обнаружена ошибка четности адреса или системная ошибка. Арбитраж шины: запрос на доступ к шине. Арбитраж шины: предоставление шины. Перезагрузка системы и всех устройств.

Дополнительные сигналы шины PCI • • • • REQ 64# ACK 64# AD PAR 64 CBE# 1 1 32 1 4 LOCK 1 SBO# SDONE 1 1 INTx JTAG M 66 EN 4 5 1 Запрос на 64 битную транзакцию. Разрешение 64 битной транзакции. Дополнительные 32 бита адреса и данных. Проверка четности для дополнительных 32 бит. Дополнительные биты для указания какие байты из слова нужно записать или считать. В многопроцессорных системах: блокировка шины при осуществлении транзакции из процессора. Обращение к Кэш памяти другого процессора. Отслеживание адресов, по которым произошли изменения завершено. Запрос прерывания. Сигналы тестирования по IEEE 1149/1. Сигнал связывания с источником питания или «землей» .

Дополнительные сигналы шины PCI • • • • REQ 64# ACK 64# AD PAR 64 CBE# 1 1 32 1 4 LOCK 1 SBO# SDONE 1 1 INTx JTAG M 66 EN 4 5 1 Запрос на 64 битную транзакцию. Разрешение 64 битной транзакции. Дополнительные 32 бита адреса и данных. Проверка четности для дополнительных 32 бит. Дополнительные биты для указания какие байты из слова нужно записать или считать. В многопроцессорных системах: блокировка шины при осуществлении транзакции из процессора. Обращение к Кэш памяти другого процессора. Отслеживание адресов, по которым произошли изменения завершено. Запрос прерывания. Сигналы тестирования по IEEE 1149/1. Сигнал связывания с источником питания или «землей» .

Транзакции шины PCI

Транзакции шины PCI

AGP - accelerated graphics port 1998 • 66 МГц; • 2 блока данных за такт; • Скорость 528 Мбайт с; • Взаимодействует с 4 –мя источниками: - процессором; - оперативной памятью; - графической картой; - PCI; Решение для обработки графики

AGP - accelerated graphics port 1998 • 66 МГц; • 2 блока данных за такт; • Скорость 528 Мбайт с; • Взаимодействует с 4 –мя источниками: - процессором; - оперативной памятью; - графической картой; - PCI; Решение для обработки графики

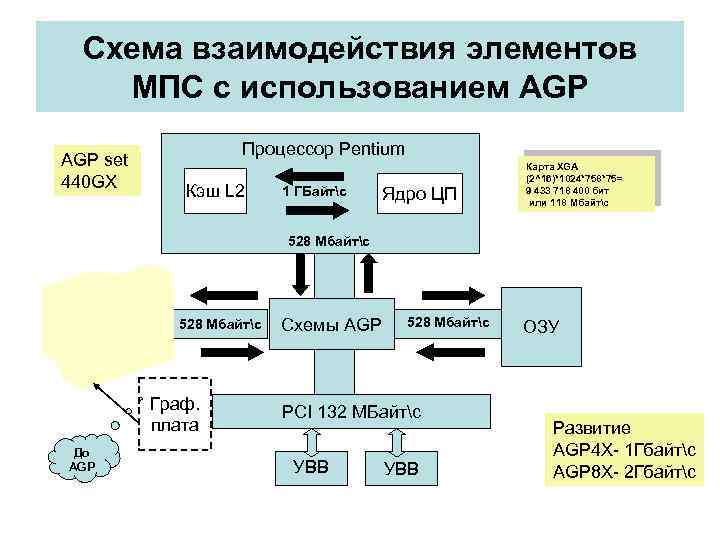

Схема взаимодействия элементов МПС с использованием AGP set 440 GX Процессор Pentium Кэш L 2 1 ГБайтс Ядро ЦП Карта XGA (2^16)*1024*758*75= 9 433 718 400 бит или 118 Мбайтс 528 Мбайтс Граф. плата До AGP Схемы AGP 528 Мбайтс PCI 132 МБайтс УВВ ОЗУ Развитие AGP 4 X- 1 Гбайтс AGP 8 X- 2 Гбайтс

Схема взаимодействия элементов МПС с использованием AGP set 440 GX Процессор Pentium Кэш L 2 1 ГБайтс Ядро ЦП Карта XGA (2^16)*1024*758*75= 9 433 718 400 бит или 118 Мбайтс 528 Мбайтс Граф. плата До AGP Схемы AGP 528 Мбайтс PCI 132 МБайтс УВВ ОЗУ Развитие AGP 4 X- 1 Гбайтс AGP 8 X- 2 Гбайтс

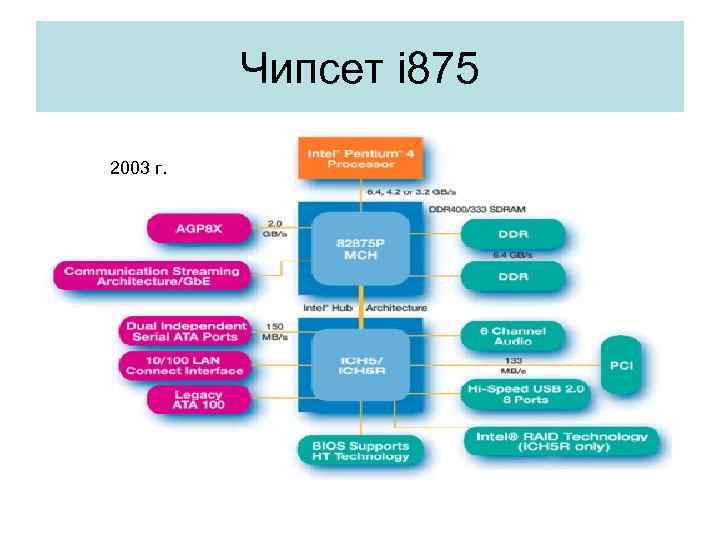

Чипсет i 875 2003 г.

Чипсет i 875 2003 г.

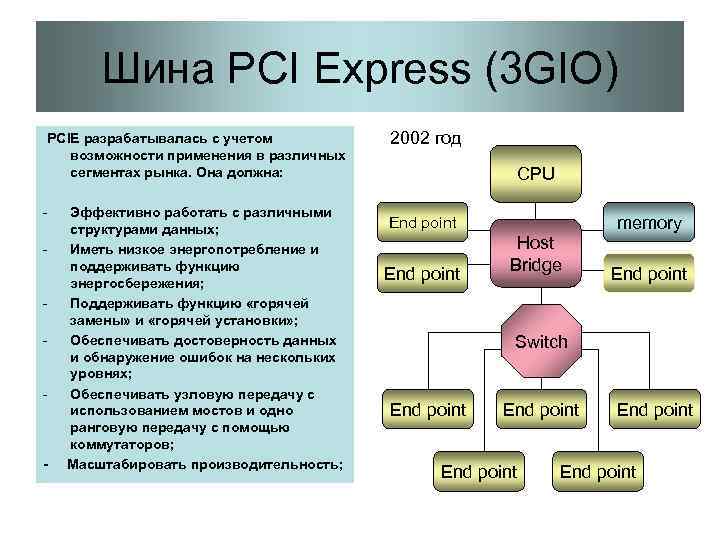

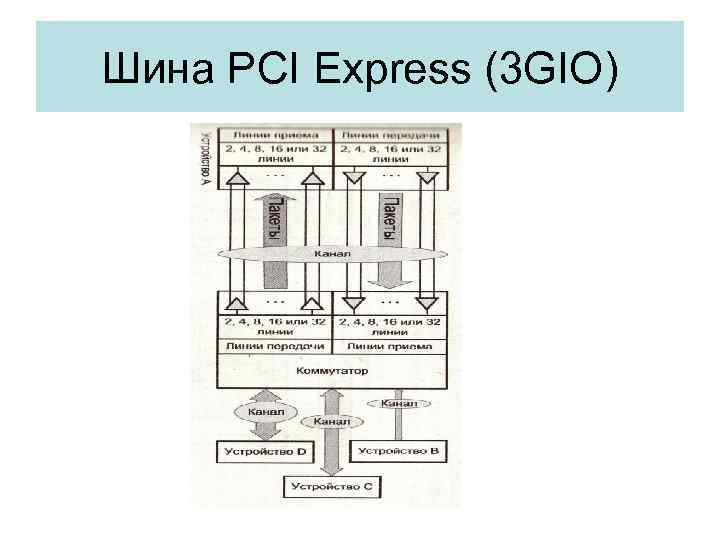

Шина PCI Express (3 GIO) PCIE разрабатывалась с учетом возможности применения в различных сегментах рынка. Она должна: - - Эффективно работать с различными структурами данных; Иметь низкое энергопотребление и поддерживать функцию энергосбережения; Поддерживать функцию «горячей замены» и «горячей установки» ; Обеспечивать достоверность данных и обнаружение ошибок на нескольких уровнях; Обеспечивать узловую передачу с использованием мостов и одно ранговую передачу с помощью коммутаторов; Масштабировать производительность; 2002 год CPU memory End point Host Bridge End point Switch End point End point

Шина PCI Express (3 GIO) PCIE разрабатывалась с учетом возможности применения в различных сегментах рынка. Она должна: - - Эффективно работать с различными структурами данных; Иметь низкое энергопотребление и поддерживать функцию энергосбережения; Поддерживать функцию «горячей замены» и «горячей установки» ; Обеспечивать достоверность данных и обнаружение ошибок на нескольких уровнях; Обеспечивать узловую передачу с использованием мостов и одно ранговую передачу с помощью коммутаторов; Масштабировать производительность; 2002 год CPU memory End point Host Bridge End point Switch End point End point

Шина PCI Express (3 GIO)

Шина PCI Express (3 GIO)

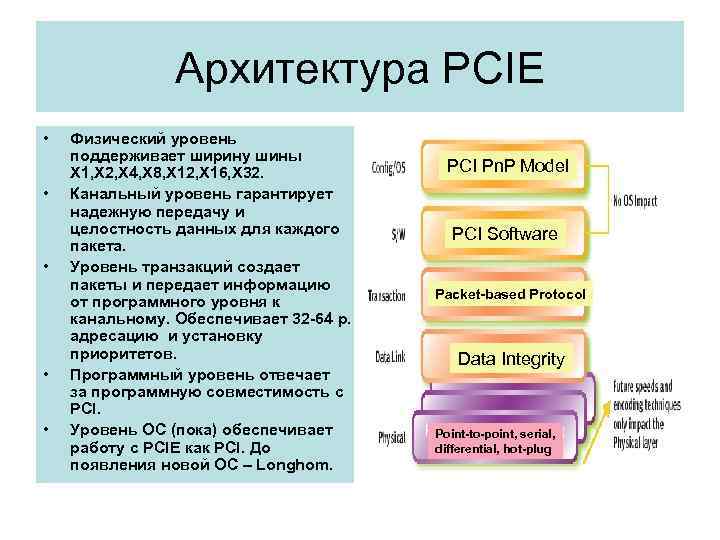

Архитектура PCIE • • • Физический уровень поддерживает ширину шины X 1, X 2, X 4, X 8, X 12, X 16, X 32. Канальный уровень гарантирует надежную передачу и целостность данных для каждого пакета. Уровень транзакций создает пакеты и передает информацию от программного уровня к канальному. Обеспечивает 32 -64 р. адресацию и установку приоритетов. Программный уровень отвечает за программную совместимость с PCI. Уровень ОС (пока) обеспечивает работу с PCIE как PCI. До появления новой ОС – Longhom. PCI Pn. P Model PCI Software Packet-based Protocol Data Integrity Point-to-point, serial, differential, hot-plug

Архитектура PCIE • • • Физический уровень поддерживает ширину шины X 1, X 2, X 4, X 8, X 12, X 16, X 32. Канальный уровень гарантирует надежную передачу и целостность данных для каждого пакета. Уровень транзакций создает пакеты и передает информацию от программного уровня к канальному. Обеспечивает 32 -64 р. адресацию и установку приоритетов. Программный уровень отвечает за программную совместимость с PCI. Уровень ОС (пока) обеспечивает работу с PCIE как PCI. До появления новой ОС – Longhom. PCI Pn. P Model PCI Software Packet-based Protocol Data Integrity Point-to-point, serial, differential, hot-plug

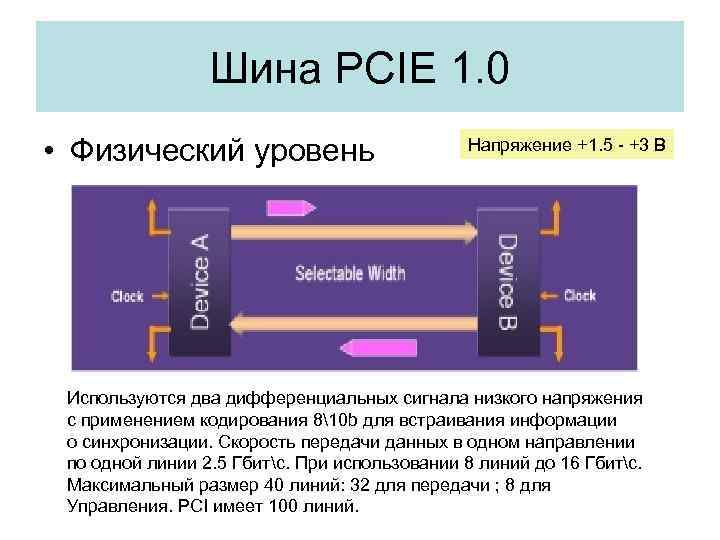

Шина PCIE 1. 0 • Физический уровень Напряжение +1. 5 - +3 В Используются два дифференциальных сигнала низкого напряжения с применением кодирования 810 b для встраивания информации о синхронизации. Скорость передачи данных в одном направлении по одной линии 2. 5 Гбитс. При использовании 8 линий до 16 Гбитс. Максимальный размер 40 линий: 32 для передачи ; 8 для Управления. PCI имеет 100 линий.

Шина PCIE 1. 0 • Физический уровень Напряжение +1. 5 - +3 В Используются два дифференциальных сигнала низкого напряжения с применением кодирования 810 b для встраивания информации о синхронизации. Скорость передачи данных в одном направлении по одной линии 2. 5 Гбитс. При использовании 8 линий до 16 Гбитс. Максимальный размер 40 линий: 32 для передачи ; 8 для Управления. PCI имеет 100 линий.

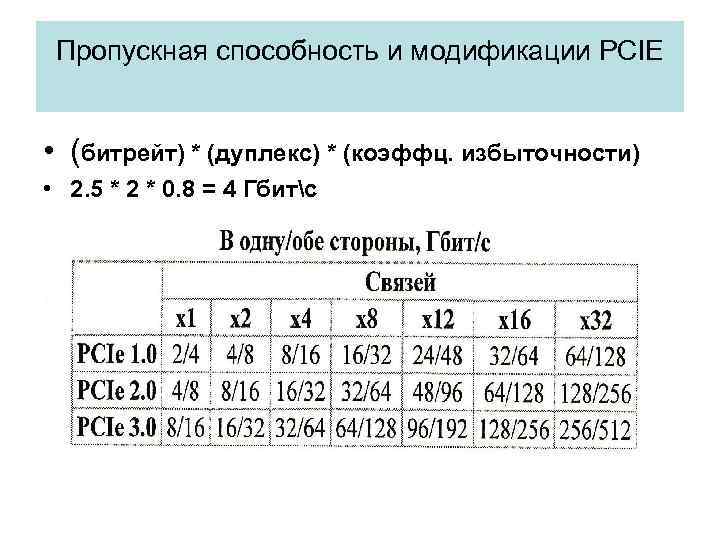

Пропускная способность и модификации PCIE • (битрейт) * (дуплекс) * (коэффц. избыточности) • 2. 5 * 2 * 0. 8 = 4 Гбитс

Пропускная способность и модификации PCIE • (битрейт) * (дуплекс) * (коэффц. избыточности) • 2. 5 * 2 * 0. 8 = 4 Гбитс

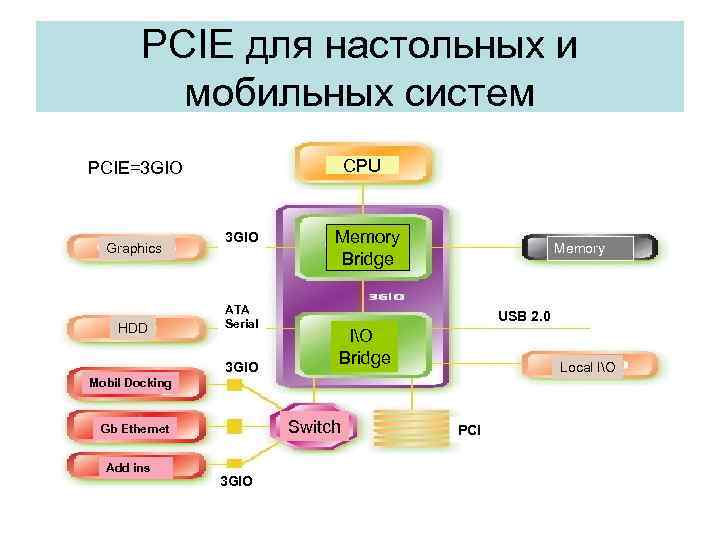

PCIE для настольных и мобильных систем CPU PCIE=3 GIO Graphics HDD 3 GIO ATA Serial 3 GIO Memory Bridge Memory USB 2. 0 IO Bridge Local IO Mobil Docking Switch Gb Ethernet Add ins 3 GIO PCI

PCIE для настольных и мобильных систем CPU PCIE=3 GIO Graphics HDD 3 GIO ATA Serial 3 GIO Memory Bridge Memory USB 2. 0 IO Bridge Local IO Mobil Docking Switch Gb Ethernet Add ins 3 GIO PCI

PCIE для серверов и рабочих станций CPU Gb. E IBA Bridge

PCIE для серверов и рабочих станций CPU Gb. E IBA Bridge

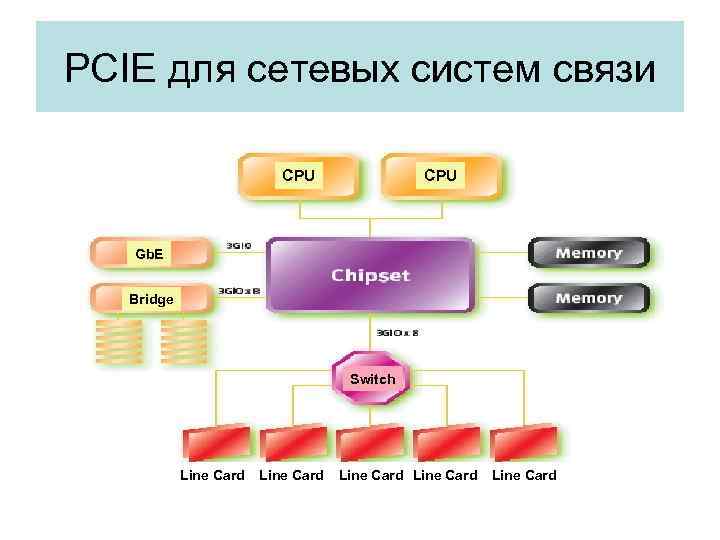

PCIE для сетевых систем связи CPU Gb. E Bridge Switch Line Card Line Card

PCIE для сетевых систем связи CPU Gb. E Bridge Switch Line Card Line Card

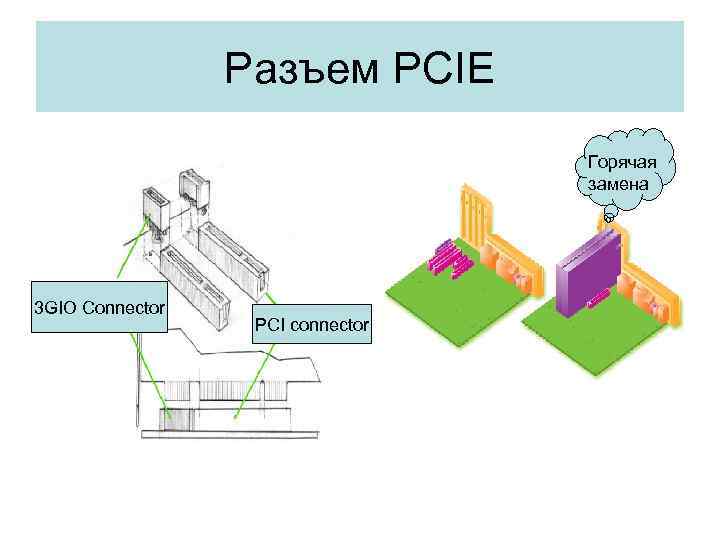

Разъем PCIE Горячая замена 3 GIO Connector PCI connector

Разъем PCIE Горячая замена 3 GIO Connector PCI connector

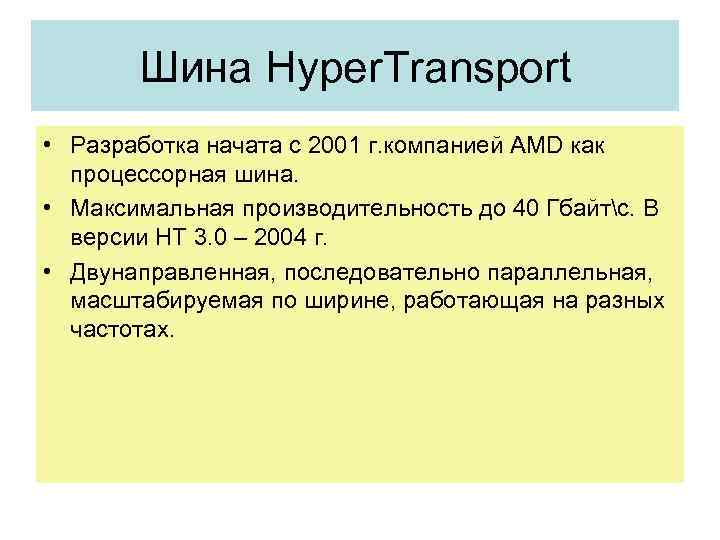

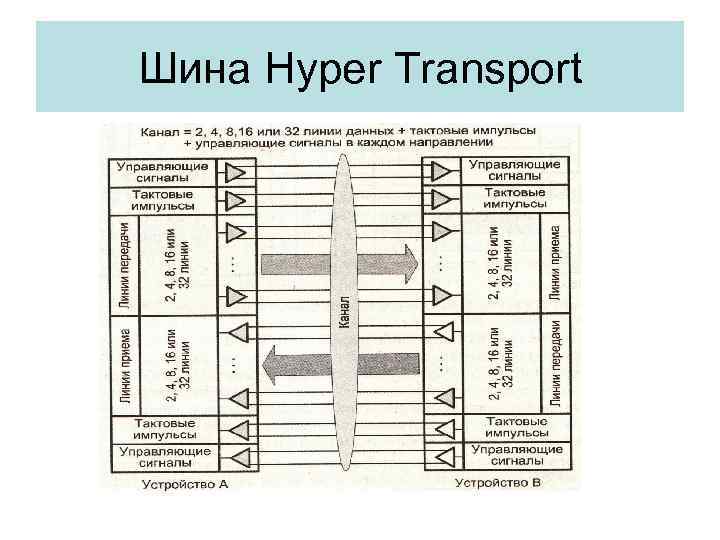

Шина Hyper. Transport • Разработка начата с 2001 г. компанией AMD как процессорная шина. • Максимальная производительность до 40 Гбайтс. В версии НТ 3. 0 – 2004 г. • Двунаправленная, последовательно параллельная, масштабируемая по ширине, работающая на разных частотах.

Шина Hyper. Transport • Разработка начата с 2001 г. компанией AMD как процессорная шина. • Максимальная производительность до 40 Гбайтс. В версии НТ 3. 0 – 2004 г. • Двунаправленная, последовательно параллельная, масштабируемая по ширине, работающая на разных частотах.

Шина Hyper Transport

Шина Hyper Transport

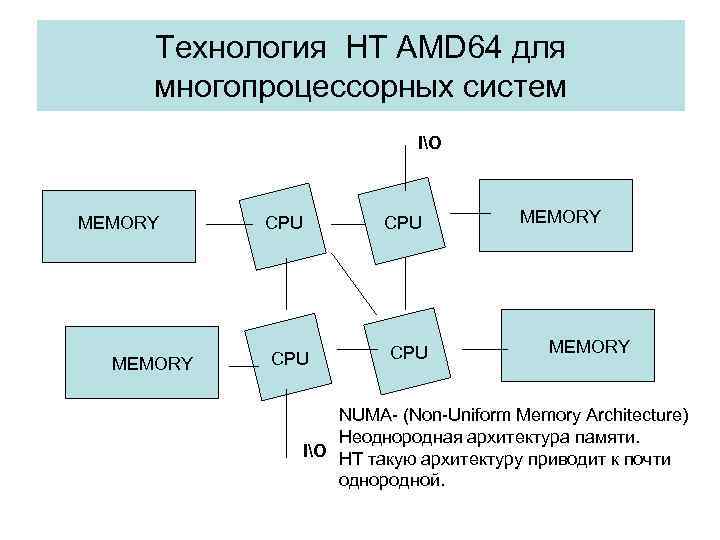

Технология НТ AMD 64 для многопроцессорных систем IO MEMORY CPU CPU MEMORY NUMA- (Non-Uniform Memory Architecture) Неоднородная архитектура памяти. IO НТ такую архитектуру приводит к почти однородной.

Технология НТ AMD 64 для многопроцессорных систем IO MEMORY CPU CPU MEMORY NUMA- (Non-Uniform Memory Architecture) Неоднородная архитектура памяти. IO НТ такую архитектуру приводит к почти однородной.

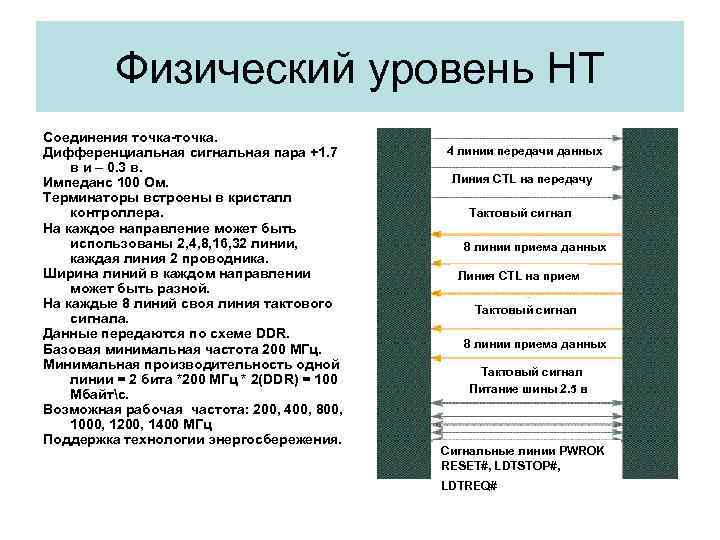

Физический уровень HT Соединения точка-точка. Дифференциальная сигнальная пара +1. 7 в и – 0. 3 в. Импеданс 100 Ом. Терминаторы встроены в кристалл контроллера. На каждое направление может быть использованы 2, 4, 8, 16, 32 линии, каждая линия 2 проводника. Ширина линий в каждом направлении может быть разной. На каждые 8 линий своя линия тактового сигнала. Данные передаются по схеме DDR. Базовая минимальная частота 200 МГц. Минимальная производительность одной линии = 2 бита *200 МГц * 2(DDR) = 100 Мбайтс. Возможная рабочая частота: 200, 400, 800, 1000, 1200, 1400 МГц Поддержка технологии энергосбережения. 4 линии передачи данных Линия CTL на передачу Тактовый сигнал 8 линии приема данных Линия CTL на прием Тактовый сигнал 8 линии приема данных Тактовый сигнал Питание шины 2. 5 в Сигнальные линии PWROK RESET#, LDTSTOP#, LDTREQ#

Физический уровень HT Соединения точка-точка. Дифференциальная сигнальная пара +1. 7 в и – 0. 3 в. Импеданс 100 Ом. Терминаторы встроены в кристалл контроллера. На каждое направление может быть использованы 2, 4, 8, 16, 32 линии, каждая линия 2 проводника. Ширина линий в каждом направлении может быть разной. На каждые 8 линий своя линия тактового сигнала. Данные передаются по схеме DDR. Базовая минимальная частота 200 МГц. Минимальная производительность одной линии = 2 бита *200 МГц * 2(DDR) = 100 Мбайтс. Возможная рабочая частота: 200, 400, 800, 1000, 1200, 1400 МГц Поддержка технологии энергосбережения. 4 линии передачи данных Линия CTL на передачу Тактовый сигнал 8 линии приема данных Линия CTL на прием Тактовый сигнал 8 линии приема данных Тактовый сигнал Питание шины 2. 5 в Сигнальные линии PWROK RESET#, LDTSTOP#, LDTREQ#

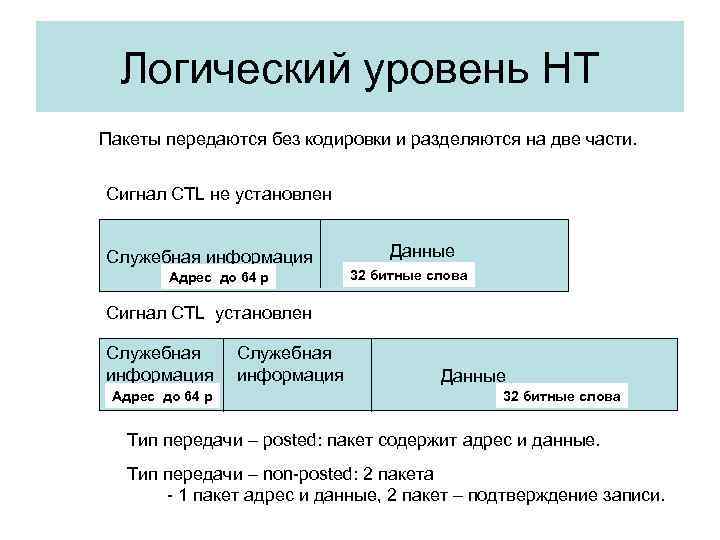

Логический уровень НТ Пакеты передаются без кодировки и разделяются на две части. Сигнал CTL не установлен Служебная информация Адрес до 64 р Данные 32 битные слова Сигнал CTL установлен Служебная информация Адрес до 64 р Служебная информация Данные 32 битные слова Тип передачи – posted: пакет содержит адрес и данные. Тип передачи – non-posted: 2 пакета - 1 пакет адрес и данные, 2 пакет – подтверждение записи.

Логический уровень НТ Пакеты передаются без кодировки и разделяются на две части. Сигнал CTL не установлен Служебная информация Адрес до 64 р Данные 32 битные слова Сигнал CTL установлен Служебная информация Адрес до 64 р Служебная информация Данные 32 битные слова Тип передачи – posted: пакет содержит адрес и данные. Тип передачи – non-posted: 2 пакета - 1 пакет адрес и данные, 2 пакет – подтверждение записи.

Применение НТ • • Процессорная шина и шина мостов. Межпроцессорная шина многопроцессорных компьютеров. В маршрутизаторах и коммутаторах. Сопроцессорные соединения. • • Технология используется компаниями AMD и Transmeta в х- 86 процессорах; PMC-Sierra, Broadcom, Raza Microelectronics в процессорах MIPS. n. Vidia, VIA, Si. S, AMD, Apple, HP в наборах системной логики для ПК. IBM в серверах. • Cray в суперкомпьютерах.

Применение НТ • • Процессорная шина и шина мостов. Межпроцессорная шина многопроцессорных компьютеров. В маршрутизаторах и коммутаторах. Сопроцессорные соединения. • • Технология используется компаниями AMD и Transmeta в х- 86 процессорах; PMC-Sierra, Broadcom, Raza Microelectronics в процессорах MIPS. n. Vidia, VIA, Si. S, AMD, Apple, HP в наборах системной логики для ПК. IBM в серверах. • Cray в суперкомпьютерах.

Шина QPI (Quick Path Interconnect) Применяется в многоядерных микропроцессорах Nehalem фирмы Intel. Аналог HP. Пропускная способность 12. 8 Гбайт в одном направлении.

Шина QPI (Quick Path Interconnect) Применяется в многоядерных микропроцессорах Nehalem фирмы Intel. Аналог HP. Пропускная способность 12. 8 Гбайт в одном направлении.