Шина ISA

Шина ISA

1. Введение Шина ISA (Industrial Standart Arhitecture) является фактически стандартной шиной для персональных компьютеров типа IBM PC/AT и совместимых с ними. Шина EISA, с которой ряд фирм выпускал персональные компьютеры, уступила шине PCI и в настоящее время используется редко. IBM PC/AT 5 разъёмов 16 -битной и 1 разъём 8 -битной шины ISA 8 - или 16 -разрядная шина ввода-вывода IBM PC-совместимых компьютеров. Служит для подключения плат расширения стандарта ISA. Конструктивно выполняется в виде 62 - или 98 контактного разъёма на материнской плате. Корзина с разъёмами шин ISA и PCI внутри промышленного компьютера Siemens SIMATIC RACK PC 840 V 2. С выпуском Спецификации PC 99, которая декларировала полный отказ от шины ISA, её роль в компьютерах стала сокращаться. С появлением материнских плат формата ATX и соответствующих плат адаптеров, шина ISA перестала широко использоваться в компьютерах, хотя встречается в промышленных компьютерах (как правило, в качестве «мезонинной шины» в специальной корзине расширения).

1. Введение Шина ISA (Industrial Standart Arhitecture) является фактически стандартной шиной для персональных компьютеров типа IBM PC/AT и совместимых с ними. Шина EISA, с которой ряд фирм выпускал персональные компьютеры, уступила шине PCI и в настоящее время используется редко. IBM PC/AT 5 разъёмов 16 -битной и 1 разъём 8 -битной шины ISA 8 - или 16 -разрядная шина ввода-вывода IBM PC-совместимых компьютеров. Служит для подключения плат расширения стандарта ISA. Конструктивно выполняется в виде 62 - или 98 контактного разъёма на материнской плате. Корзина с разъёмами шин ISA и PCI внутри промышленного компьютера Siemens SIMATIC RACK PC 840 V 2. С выпуском Спецификации PC 99, которая декларировала полный отказ от шины ISA, её роль в компьютерах стала сокращаться. С появлением материнских плат формата ATX и соответствующих плат адаптеров, шина ISA перестала широко использоваться в компьютерах, хотя встречается в промышленных компьютерах (как правило, в качестве «мезонинной шины» в специальной корзине расширения).

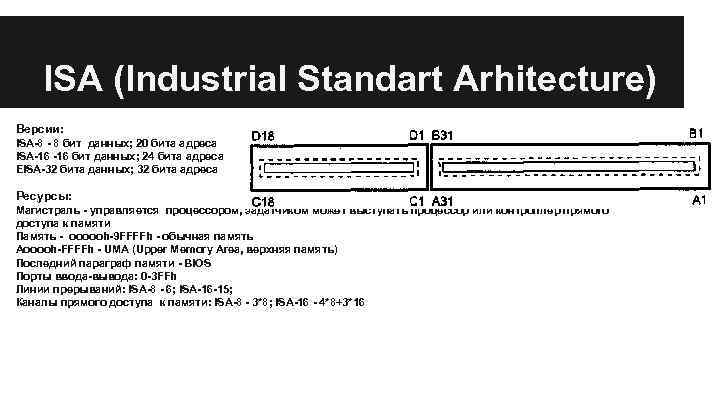

ISA (Industrial Standart Arhitecture) Версии: ISA-8 - 8 бит данных; 20 бита адреса ISA-16 бит данных; 24 бита адреса EISA-32 бита данных; 32 бита адреса Ресурсы: Магистраль - управляется процессором, задатчиком может выступать процессор или контроллер прямого доступа к памяти Память - oooooh-9 FFFFh - обычная память Aooooh-FFFFh - UMA (Upper Memory Area, верхняя память) Последний параграф памяти - BIOS Порты ввода-вывода: 0 -3 FFh Линии прерываний: ISA-8 - 6; ISA-16 -15; Каналы прямого доступа к памяти: ISA-8 - 3*8; ISA-16 - 4*8+3*16

ISA (Industrial Standart Arhitecture) Версии: ISA-8 - 8 бит данных; 20 бита адреса ISA-16 бит данных; 24 бита адреса EISA-32 бита данных; 32 бита адреса Ресурсы: Магистраль - управляется процессором, задатчиком может выступать процессор или контроллер прямого доступа к памяти Память - oooooh-9 FFFFh - обычная память Aooooh-FFFFh - UMA (Upper Memory Area, верхняя память) Последний параграф памяти - BIOS Порты ввода-вывода: 0 -3 FFh Линии прерываний: ISA-8 - 6; ISA-16 -15; Каналы прямого доступа к памяти: ISA-8 - 3*8; ISA-16 - 4*8+3*16

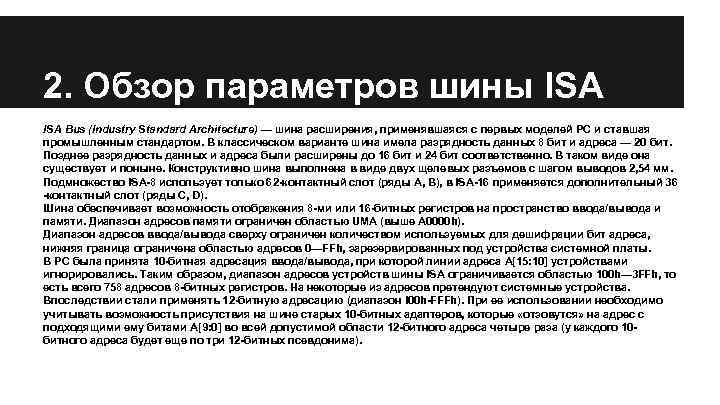

2. Обзор параметров шины ISA Bus (Industry Standard Architecture) — шина расширения, применявшаяся с первых моделей PC и ставшая промышленным стандартом. В классическом варианте шина имела разрядность данных 8 бит и адреса — 20 бит. Позднее разрядность данных и адреса были расширены до 16 бит и 24 бит соответственно. В таком виде она существует и поныне. Конструктивно шина выполнена в виде двух щелевых разъемов с шагом выводов 2, 54 мм. Подмножество ISA-8 использует только 62 -контактный слот (ряды А, В), в ISA-16 применяется дополнительный 36 -контактный слот (ряды С, D). Шина обеспечивает возможность отображения 8 -ми или 16 -битных регистров на пространство ввода/вывода и памяти. Диапазон адресов памяти ограничен областью UMA (выше A 0000 h). Диапазон адресов ввода/вывода сверху ограничен количеством используемых для дешифрации бит адреса, нижняя граница ограничена областью адресов 0—FFh, зарезервированных под устройства системной платы. В PC была принята 10 -битная адресация ввода/вывода, при которой линии адреса А[15: 10] устройствами игнорировались. Таким образом, диапазон адресов устройств шины ISA ограничивается областью 100 h— 3 FFh, то есть всего 758 адресов 8 -битных регистров. На некоторые из адресов претендуют системные устройства. Впоследствии стали применять 12 -битную адресацию (диапазон l 00 h-FFFh). При ее использовании необходимо учитывать возможность присутствия на шине старых 10 -битных адаптеров, которые «отзовутся» на адрес с подходящими ему битами А[9: 0] во всей допустимой области 12 -битного адреса четыре раза (у каждого 10 битного адреса будет еще по три 12 -битных псевдонима).

2. Обзор параметров шины ISA Bus (Industry Standard Architecture) — шина расширения, применявшаяся с первых моделей PC и ставшая промышленным стандартом. В классическом варианте шина имела разрядность данных 8 бит и адреса — 20 бит. Позднее разрядность данных и адреса были расширены до 16 бит и 24 бит соответственно. В таком виде она существует и поныне. Конструктивно шина выполнена в виде двух щелевых разъемов с шагом выводов 2, 54 мм. Подмножество ISA-8 использует только 62 -контактный слот (ряды А, В), в ISA-16 применяется дополнительный 36 -контактный слот (ряды С, D). Шина обеспечивает возможность отображения 8 -ми или 16 -битных регистров на пространство ввода/вывода и памяти. Диапазон адресов памяти ограничен областью UMA (выше A 0000 h). Диапазон адресов ввода/вывода сверху ограничен количеством используемых для дешифрации бит адреса, нижняя граница ограничена областью адресов 0—FFh, зарезервированных под устройства системной платы. В PC была принята 10 -битная адресация ввода/вывода, при которой линии адреса А[15: 10] устройствами игнорировались. Таким образом, диапазон адресов устройств шины ISA ограничивается областью 100 h— 3 FFh, то есть всего 758 адресов 8 -битных регистров. На некоторые из адресов претендуют системные устройства. Впоследствии стали применять 12 -битную адресацию (диапазон l 00 h-FFFh). При ее использовании необходимо учитывать возможность присутствия на шине старых 10 -битных адаптеров, которые «отзовутся» на адрес с подходящими ему битами А[9: 0] во всей допустимой области 12 -битного адреса четыре раза (у каждого 10 битного адреса будет еще по три 12 -битных псевдонима).

2. Обзор параметров шины ISA Карты расширения для шины ISA

2. Обзор параметров шины ISA Карты расширения для шины ISA

3. Протокол передачи данных Для передачи данных от исполнителя к задатчику предназначены циклы чтения ячейки памяти или порта вводавывода, для передачи данных от задатчика к исполнителю — циклы записи ячейки памяти или порта вводавывода. В каждом цикле текущий (на время данного цикла) задатчик формирует адрес обращения и управляющие сигналы, а в циклах записи еще и данные на шине. Адресуемое устройство-исполнитель в соответствии с полученными управляющими сигналами принимает (в цикле записи) или формирует (в цикле чтения) данные. Также оно может, при необходимости, управлять длительностью цикла и разрядностью передачи.

3. Протокол передачи данных Для передачи данных от исполнителя к задатчику предназначены циклы чтения ячейки памяти или порта вводавывода, для передачи данных от задатчика к исполнителю — циклы записи ячейки памяти или порта вводавывода. В каждом цикле текущий (на время данного цикла) задатчик формирует адрес обращения и управляющие сигналы, а в циклах записи еще и данные на шине. Адресуемое устройство-исполнитель в соответствии с полученными управляющими сигналами принимает (в цикле записи) или формирует (в цикле чтения) данные. Также оно может, при необходимости, управлять длительностью цикла и разрядностью передачи.

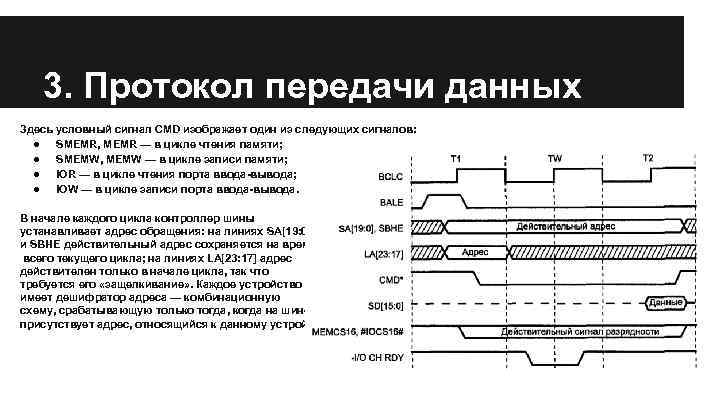

3. Протокол передачи данных Здесь условный сигнал CMD изображает один из следующих сигналов: ● SMEMR, MEMR — в цикле чтения памяти; ● SMEMW, MEMW — в цикле записи памяти; ● IOR — в цикле чтения порта ввода-вывода; ● IOW — в цикле записи порта ввода-вывода. В начале каждого цикла контроллер шины устанавливает адрес обращения: на линиях SA[19: 0] и SBHE действительный адрес сохраняется на время всего текущего цикла; на линиях LА[23: 17] адрес действителен только в начале цикла, так что требуется его «защелкивание» . Каждое устройство имеет дешифратор адреса — комбинационную схему, срабатывающую только тогда, когда на шине присутствует адрес, относящийся к данному устройству.

3. Протокол передачи данных Здесь условный сигнал CMD изображает один из следующих сигналов: ● SMEMR, MEMR — в цикле чтения памяти; ● SMEMW, MEMW — в цикле записи памяти; ● IOR — в цикле чтения порта ввода-вывода; ● IOW — в цикле записи порта ввода-вывода. В начале каждого цикла контроллер шины устанавливает адрес обращения: на линиях SA[19: 0] и SBHE действительный адрес сохраняется на время всего текущего цикла; на линиях LА[23: 17] адрес действителен только в начале цикла, так что требуется его «защелкивание» . Каждое устройство имеет дешифратор адреса — комбинационную схему, срабатывающую только тогда, когда на шине присутствует адрес, относящийся к данному устройству.

3. Протокол передачи данных В фазе адресации устройства еще «не знают» , к какому из пространств (памяти или ввода-вывода) относится выставленный адрес. Но дешифраторы адресов уже срабатывают, и, когда в следующей фазе шина управления сообщает тип операции, адресуемое устройство уже оказывается готовым к ее исполнению. Если устройство использует линии LA[23: 17] (они нужны лишь для обращений к памяти выше границы FFFFFh), то они на дешифратор адреса должны проходить через регистрзащелку, «прозрачный» во время действия сигнала BALE и фиксирующий состояние выходов по его спаду. Это позволяет дешифратору, всегда вносящему некоторую задержку, начинать работу раньше, чем поступит управляющий сигнал чтения или записи. При обращении к портам ввода-вывода сигналы LА[32: 17] не используются. Если устройство имеет более одного регистра (ячейки), то для выбора конкретного регистра (ячейки) ему требуется несколько линий адреса. Как правило, старшие биты шины адреса поступают на вход дешифраторов адреса, формирующих сигналы выборки устройств, а младшие биты — на адресные входы самих устройств. Тогда каждое устройство в пространстве будет занимать наиболее компактную область смежных адресов размером в 2 n байт, где n — номер младшей линии адреса, поступающей на дешифратор. Из них реально необходимы 2 m адресов, где m — номер самой старшей линии адреса, участвующей в выборе регистра устройства. В идеале должно быть n=m+l: при большем значении n отведенное (по дешифратору) пространство адресов не будет использовано полностью и регистры устройства будут повторяться в отведенной области 2 n-m-1 раз, то есть у них появятся адресапсевдонимы (alias). Адреса-псевдонимы будут отличаться от истинного адреса (минимального из всех псевдонимов) на K× 2 m+1, где К — целое число. Меньшее значение n недопустимо, поскольку тогда не все регистры устройства будут доступны задатчику. В принципе можно использовать дешифратор адреса, срабатывающий только на какой-то части адресов из области 2 n (не кратной степени двойки), если устройству требуется «неудобное» количество регистров. Однако на практике «фигурное выпиливание» областей из пространства адресов обычно не делают, так что часть адресов может пропадать бесполезно.

3. Протокол передачи данных В фазе адресации устройства еще «не знают» , к какому из пространств (памяти или ввода-вывода) относится выставленный адрес. Но дешифраторы адресов уже срабатывают, и, когда в следующей фазе шина управления сообщает тип операции, адресуемое устройство уже оказывается готовым к ее исполнению. Если устройство использует линии LA[23: 17] (они нужны лишь для обращений к памяти выше границы FFFFFh), то они на дешифратор адреса должны проходить через регистрзащелку, «прозрачный» во время действия сигнала BALE и фиксирующий состояние выходов по его спаду. Это позволяет дешифратору, всегда вносящему некоторую задержку, начинать работу раньше, чем поступит управляющий сигнал чтения или записи. При обращении к портам ввода-вывода сигналы LА[32: 17] не используются. Если устройство имеет более одного регистра (ячейки), то для выбора конкретного регистра (ячейки) ему требуется несколько линий адреса. Как правило, старшие биты шины адреса поступают на вход дешифраторов адреса, формирующих сигналы выборки устройств, а младшие биты — на адресные входы самих устройств. Тогда каждое устройство в пространстве будет занимать наиболее компактную область смежных адресов размером в 2 n байт, где n — номер младшей линии адреса, поступающей на дешифратор. Из них реально необходимы 2 m адресов, где m — номер самой старшей линии адреса, участвующей в выборе регистра устройства. В идеале должно быть n=m+l: при большем значении n отведенное (по дешифратору) пространство адресов не будет использовано полностью и регистры устройства будут повторяться в отведенной области 2 n-m-1 раз, то есть у них появятся адресапсевдонимы (alias). Адреса-псевдонимы будут отличаться от истинного адреса (минимального из всех псевдонимов) на K× 2 m+1, где К — целое число. Меньшее значение n недопустимо, поскольку тогда не все регистры устройства будут доступны задатчику. В принципе можно использовать дешифратор адреса, срабатывающий только на какой-то части адресов из области 2 n (не кратной степени двойки), если устройству требуется «неудобное» количество регистров. Однако на практике «фигурное выпиливание» областей из пространства адресов обычно не делают, так что часть адресов может пропадать бесполезно.

3. Протокол передачи данных Разрядность данных в каждом цикле обращения определяется потребностями текущего задатчика и возможностями исполнителя. Момент помещения действительных данных на линии SD[15: 0] определяется управляющими сигналами чтения/записи, так что исполнителю не требуется синхронизация с тактовым сигналом шины. В циклах чтения адресованный исполнитель должен выдать данные на шину по началу (спаду) соответствующего сигнала чтения (IOR, MEMR, SMEMR) и удерживать их до конца действия сигнала (пока не произойдет подъем сигнала). В циклах записи задатчик выставляет действительные данные несколько позже начала (спада) сигнала записи (IOW, MEMW, SMEMW). Устройство-исполнитель должно фиксировать для себя эти данные в конце цикла по подъему сигнала записи. От устройства-исполнителя не предусматривается никаких подтверждений исполнения циклов; длительность цикла устанавливает задатчик, но исполнитель может потребовать удлинения или укорочения циклов. С помощью сигнала IOCHRDY исполнитель может удлинить цикл на произвольное число тактов, при этом задатчик будет вводить дополнительные такты ожидания (wait states). Обычно контроллер шины следит за длительностью цикла и по достижении критического времени принудительно его завершает (по тайм-ауту, возможно, и не сообщая об этом событии). Слишком длинные циклы тормозят работу компьютера, а превышение длительности 15 мкс может привести к сбою регенерации и потере данных в ОЗУ. С помощью сигнала 0 WS исполнитель предлагает задатчику укоротить цикл, исключив такты ожидания. Реакция задатчика на одновременное использование сигналов IOCHRDY и 0 WS непредсказуема, этой ситуации следует избегать.

3. Протокол передачи данных Разрядность данных в каждом цикле обращения определяется потребностями текущего задатчика и возможностями исполнителя. Момент помещения действительных данных на линии SD[15: 0] определяется управляющими сигналами чтения/записи, так что исполнителю не требуется синхронизация с тактовым сигналом шины. В циклах чтения адресованный исполнитель должен выдать данные на шину по началу (спаду) соответствующего сигнала чтения (IOR, MEMR, SMEMR) и удерживать их до конца действия сигнала (пока не произойдет подъем сигнала). В циклах записи задатчик выставляет действительные данные несколько позже начала (спада) сигнала записи (IOW, MEMW, SMEMW). Устройство-исполнитель должно фиксировать для себя эти данные в конце цикла по подъему сигнала записи. От устройства-исполнителя не предусматривается никаких подтверждений исполнения циклов; длительность цикла устанавливает задатчик, но исполнитель может потребовать удлинения или укорочения циклов. С помощью сигнала IOCHRDY исполнитель может удлинить цикл на произвольное число тактов, при этом задатчик будет вводить дополнительные такты ожидания (wait states). Обычно контроллер шины следит за длительностью цикла и по достижении критического времени принудительно его завершает (по тайм-ауту, возможно, и не сообщая об этом событии). Слишком длинные циклы тормозят работу компьютера, а превышение длительности 15 мкс может привести к сбою регенерации и потере данных в ОЗУ. С помощью сигнала 0 WS исполнитель предлагает задатчику укоротить цикл, исключив такты ожидания. Реакция задатчика на одновременное использование сигналов IOCHRDY и 0 WS непредсказуема, этой ситуации следует избегать.

4. Согласование разрядности данных Разрядность данных в каждом цикле обращения определяется потребностями текущего задатчика и возможностями исполнителя. На системной плате имеется специальный буфер, он же перестановщик байтов, который при необходимости транслирует данные с младшего байта шины на старшую или обратно. Его задача точно согласовать размер данных, которыми обмениваются устройства. Логика управления этим буфером использует сигналы SBHE, SAO, IOCS 16 и MEMCS 16. Поддержка 16 -разрядных передач сообщается адресуемым исполнителем сигналами IOCS 16 и MEMCS 16 при срабатывании его дешифратора адреса. Сигнал IOCS 16 влияет только на разрядность обращений к портам, MEMCS 16 — к памяти. Все операции обмена (транзакции) начинаются задатчиком единообразно, поскольку он еще не «знает» возможностей исполнителя. Развитие событий зависит от намерений задатчика и полученных сигналов разрешения 16 -битных передач. В чисто 16 -разрядных машинах начальный адрес однозначно соответствует передаваемому байту или младшему байту передаваемого слова. В машинах с 32 -разрядными процессорами начальный адрес, выставляемый на шине в начале транзакции, зависит от разрядности данных, запланированной задатчиком, и может зависеть от положения адресуемых данных относительно границы двойного слова (32 битного). 16 -разрядные передачи выполняются за 1 цикл только при условии передачи по четному адресу (А 0=0) и при ответе исполнителя сигналом IOCS 16* или MEMCS 16#, в иных случаях они разбиваются на два цикла. 32 -разрядные передачи будут разбиваться на 2 (16+16), 3 (8+16+8) или 4 (8+8+8+8) цикла, в зависимости от возможностей исполнителя и четности адреса. Порядок, в котором передаются байты (во времени), неоднозначен (возможен как инкремент, так и декремент адреса), но в адресном пространстве они раскладываются по своим местам однозначно.

4. Согласование разрядности данных Разрядность данных в каждом цикле обращения определяется потребностями текущего задатчика и возможностями исполнителя. На системной плате имеется специальный буфер, он же перестановщик байтов, который при необходимости транслирует данные с младшего байта шины на старшую или обратно. Его задача точно согласовать размер данных, которыми обмениваются устройства. Логика управления этим буфером использует сигналы SBHE, SAO, IOCS 16 и MEMCS 16. Поддержка 16 -разрядных передач сообщается адресуемым исполнителем сигналами IOCS 16 и MEMCS 16 при срабатывании его дешифратора адреса. Сигнал IOCS 16 влияет только на разрядность обращений к портам, MEMCS 16 — к памяти. Все операции обмена (транзакции) начинаются задатчиком единообразно, поскольку он еще не «знает» возможностей исполнителя. Развитие событий зависит от намерений задатчика и полученных сигналов разрешения 16 -битных передач. В чисто 16 -разрядных машинах начальный адрес однозначно соответствует передаваемому байту или младшему байту передаваемого слова. В машинах с 32 -разрядными процессорами начальный адрес, выставляемый на шине в начале транзакции, зависит от разрядности данных, запланированной задатчиком, и может зависеть от положения адресуемых данных относительно границы двойного слова (32 битного). 16 -разрядные передачи выполняются за 1 цикл только при условии передачи по четному адресу (А 0=0) и при ответе исполнителя сигналом IOCS 16* или MEMCS 16#, в иных случаях они разбиваются на два цикла. 32 -разрядные передачи будут разбиваться на 2 (16+16), 3 (8+16+8) или 4 (8+8+8+8) цикла, в зависимости от возможностей исполнителя и четности адреса. Порядок, в котором передаются байты (во времени), неоднозначен (возможен как инкремент, так и декремент адреса), но в адресном пространстве они раскладываются по своим местам однозначно.

5. Прямое управление шиной В случае прямого управления шиной (bus mastering) инициатором обмена становится контроллер какого-либо устройства или интерфейса, но не процессор и не канал DMA. Прямое управление позволяет контроллеру, не отвлекая центральный процессор, выполнять обмен данными с высокой производительностью и, возможно, по более сложным правилам и без ограничений, присущих каналам DMA (невозможность пересечения границы страницы). Контроллер, как правило, обеспечивает обмен данными между системным ОЗУ и своим периферийным устройством или интерфейсом. В принципе он может общаться с памятью или портами другого абонента шины, но для упрощения организации всех информационных связей центральным «перевалочным пунктом» все-таки является системное ОЗУ. Получить право на управление шиной ISA может только контроллер, подключенный к 16 -битному слоту. Для арбитража запросов на управление шиной от нескольких источников — центрального процессора, контроллера DMA и контроллеров-абонентов шины используется второй контроллер DMA (каналы 5 -7). Устройство, желающее получить управление, выставляет запрос DRQx (x=5. . . 7), по которому контроллер DMA запрашивает управление шиной у центрального процессора. Получив подтверждение от процессора, контроллер устанавливает сигнал AEN (для блокировки дешифрации адреса портов) и формирует сигнал DACKx. Получив этот сигнал, устройство устанавливает низкий уровень на линии MASTER, по которому контроллер шины DMA снимает сигнал AEN и освобождает линии командных сигналов. Таким образом, управление шиной переходит к данному устройству до тех пор, пока оно не снимет запрос DRQx. В режиме прямого управления шиной ISA устройство становится полновластным и бесконтрольным хозяином как самой шины, так и системы в целом (через мост шины). Если шина захватывается более чем на 15 мкс, контроллер устройства должен заботиться о регенерации памяти (см. ниже). Устройства (и память), к которым обращается задатчик шины, могут потребовать введения тактов ожидания сигналом IOCHRDY, и это требование должно удовлетворяться.

5. Прямое управление шиной В случае прямого управления шиной (bus mastering) инициатором обмена становится контроллер какого-либо устройства или интерфейса, но не процессор и не канал DMA. Прямое управление позволяет контроллеру, не отвлекая центральный процессор, выполнять обмен данными с высокой производительностью и, возможно, по более сложным правилам и без ограничений, присущих каналам DMA (невозможность пересечения границы страницы). Контроллер, как правило, обеспечивает обмен данными между системным ОЗУ и своим периферийным устройством или интерфейсом. В принципе он может общаться с памятью или портами другого абонента шины, но для упрощения организации всех информационных связей центральным «перевалочным пунктом» все-таки является системное ОЗУ. Получить право на управление шиной ISA может только контроллер, подключенный к 16 -битному слоту. Для арбитража запросов на управление шиной от нескольких источников — центрального процессора, контроллера DMA и контроллеров-абонентов шины используется второй контроллер DMA (каналы 5 -7). Устройство, желающее получить управление, выставляет запрос DRQx (x=5. . . 7), по которому контроллер DMA запрашивает управление шиной у центрального процессора. Получив подтверждение от процессора, контроллер устанавливает сигнал AEN (для блокировки дешифрации адреса портов) и формирует сигнал DACKx. Получив этот сигнал, устройство устанавливает низкий уровень на линии MASTER, по которому контроллер шины DMA снимает сигнал AEN и освобождает линии командных сигналов. Таким образом, управление шиной переходит к данному устройству до тех пор, пока оно не снимет запрос DRQx. В режиме прямого управления шиной ISA устройство становится полновластным и бесконтрольным хозяином как самой шины, так и системы в целом (через мост шины). Если шина захватывается более чем на 15 мкс, контроллер устройства должен заботиться о регенерации памяти (см. ниже). Устройства (и память), к которым обращается задатчик шины, могут потребовать введения тактов ожидания сигналом IOCHRDY, и это требование должно удовлетворяться.

6. Регенерация памяти Динамическая память, применяемая в компьютере в качестве системного ОЗУ, а также, возможно, находящаяся на картах расширения, требует регенерации — периодического обновления (refresh) всех строк матрицы. На системной плате всегда имеется контроллер регенерации памяти, в задачу которого входит регулярный перебор строк памяти с формированием специального цикла регенерации. Каждые 15 мкс контроллер регенерации формирует цикл регенерации (сигнал REFRESH), диаграмма которого аналогична циклу DMA, но вместо чтения данных выполняется регенерация.

6. Регенерация памяти Динамическая память, применяемая в компьютере в качестве системного ОЗУ, а также, возможно, находящаяся на картах расширения, требует регенерации — периодического обновления (refresh) всех строк матрицы. На системной плате всегда имеется контроллер регенерации памяти, в задачу которого входит регулярный перебор строк памяти с формированием специального цикла регенерации. Каждые 15 мкс контроллер регенерации формирует цикл регенерации (сигнал REFRESH), диаграмма которого аналогична циклу DMA, но вместо чтения данных выполняется регенерация.

6. Регенерация памяти В этом цикле считывания данных из микросхем памяти не производится, но стробы строк формируются. На шине ISA контроллер регенерации работает как нулевой канал DMA (в старых машинах он непосредственно и использовался). Каждые 15 мкс контроллер регенерации формирует сигнал REFRESH*, во время действия которого устанавливается AEN=H и BALE=H, формируется сигнал MEMR, а на линиях SA[7: 0] устанавливается адрес текущей регенерируемой строки. Диаграмма цикла регенерации аналогична циклу DMA, но сигнал REFRESH указывает на то, что вместо чтения данных выполняется регенерация.

6. Регенерация памяти В этом цикле считывания данных из микросхем памяти не производится, но стробы строк формируются. На шине ISA контроллер регенерации работает как нулевой канал DMA (в старых машинах он непосредственно и использовался). Каждые 15 мкс контроллер регенерации формирует сигнал REFRESH*, во время действия которого устанавливается AEN=H и BALE=H, формируется сигнал MEMR, а на линиях SA[7: 0] устанавливается адрес текущей регенерируемой строки. Диаграмма цикла регенерации аналогична циклу DMA, но сигнал REFRESH указывает на то, что вместо чтения данных выполняется регенерация.

7. Распайка шин ISA и EISA

7. Распайка шин ISA и EISA

8. Виды устройств, работающие на шине ISA При описании шины целесообразно представить компьютер как состоящий из материнской платы (motherboard) и внешних плат, которые взаимодействуют между собой и ресурсами материнской платы через шину. Все пассивные устройства (не могущие стать задачиками) на шине можно разделить на две группы - память и устройства ввода/вывода (порты). Циклы доступа для каждой из групп отличаются друг от друга как по временным характеристикам, так и по вырабатываемым на шине сигналам. Чисто условно, для удобства понимания функционирования шины ISA, будем считать, что на материнской плате компьютера существуют следующие устройства, способные быть владельцами (задатчиками) шины: центральный процессор (ЦП), контроллер прямого доступа в память (ПДП), контроллер регенерации памяти (КРП). Кроме этого, задатчиком на шине может быть и внешняя плата. При выполнении цикла доступа на шине задатчиком может быть только одно из устройств. Рассмотрим подробнее функции этих устройств на шине ISA. Центральный процессор (ЦП) Контроллер ПДП ввода/вывода Контроллер регенерации памяти Внешняя плата плате Часы реального времени (Таймер-счетчик) Виды устройств, работающие на шине ISA Контроллер прерываний Устройства Перестановщик байтов данных Память на материнской Кросс материнской платы Центральный процессор (ЦП)

8. Виды устройств, работающие на шине ISA При описании шины целесообразно представить компьютер как состоящий из материнской платы (motherboard) и внешних плат, которые взаимодействуют между собой и ресурсами материнской платы через шину. Все пассивные устройства (не могущие стать задачиками) на шине можно разделить на две группы - память и устройства ввода/вывода (порты). Циклы доступа для каждой из групп отличаются друг от друга как по временным характеристикам, так и по вырабатываемым на шине сигналам. Чисто условно, для удобства понимания функционирования шины ISA, будем считать, что на материнской плате компьютера существуют следующие устройства, способные быть владельцами (задатчиками) шины: центральный процессор (ЦП), контроллер прямого доступа в память (ПДП), контроллер регенерации памяти (КРП). Кроме этого, задатчиком на шине может быть и внешняя плата. При выполнении цикла доступа на шине задатчиком может быть только одно из устройств. Рассмотрим подробнее функции этих устройств на шине ISA. Центральный процессор (ЦП) Контроллер ПДП ввода/вывода Контроллер регенерации памяти Внешняя плата плате Часы реального времени (Таймер-счетчик) Виды устройств, работающие на шине ISA Контроллер прерываний Устройства Перестановщик байтов данных Память на материнской Кросс материнской платы Центральный процессор (ЦП)

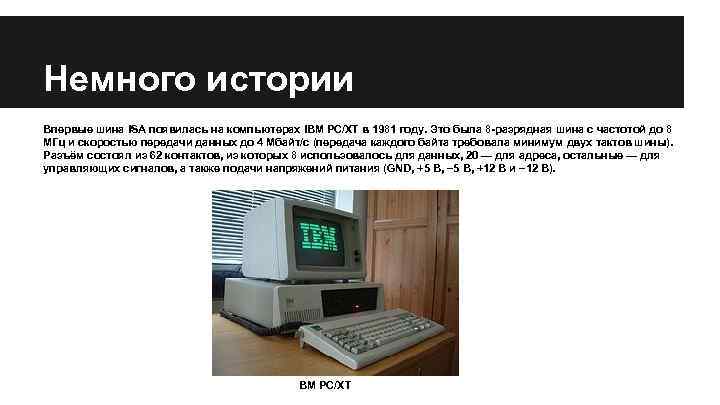

Немного истории Впервые шина ISA появилась на компьютерах IBM PC/XT в 1981 году. Это была 8 -разрядная шина с частотой до 8 МГц и скоростью передачи данных до 4 Мбайт/с (передача каждого байта требовала минимум двух тактов шины). Разъём состоял из 62 контактов, из которых 8 использовалось для данных, 20 — для адреса, остальные — для управляющих сигналов, а также подачи напряжений питания (GND, +5 В, − 5 В, +12 В и − 12 В). BM PC/XT

Немного истории Впервые шина ISA появилась на компьютерах IBM PC/XT в 1981 году. Это была 8 -разрядная шина с частотой до 8 МГц и скоростью передачи данных до 4 Мбайт/с (передача каждого байта требовала минимум двух тактов шины). Разъём состоял из 62 контактов, из которых 8 использовалось для данных, 20 — для адреса, остальные — для управляющих сигналов, а также подачи напряжений питания (GND, +5 В, − 5 В, +12 В и − 12 В). BM PC/XT

Немного истории В 1984 году шина была усовершенствована. Была удвоена разрядность данных (что повлекло удвоение пропускной способности) и добавлены четыре разряда адреса; кроме того, увеличилось число линий запросов прерываний и запросов прямого доступа к памяти (DMA). Кроме того, в 16 -разрядной шине ISA любое подключенное к ней устройство могло выступать в роли задатчика, то есть инициировать операцию обмена данными (в 8 -разрядной шине задатчиками были только процессор и контроллер DMA). Для подключения 16 разрядных устройств используются разъёмы, состоящие из двух частей: полностью совместимой с 8 -разрядной шиной 62 -контактной и новой 36 -контактной. Ввиду движения по направлению к проприетарной шине Micro Channel Architecture (MCA), IBM тогда практически прекратила поддержку ISA в своих продуктах. 16 -bit Network Interface Card IBM 83 X 9648.

Немного истории В 1984 году шина была усовершенствована. Была удвоена разрядность данных (что повлекло удвоение пропускной способности) и добавлены четыре разряда адреса; кроме того, увеличилось число линий запросов прерываний и запросов прямого доступа к памяти (DMA). Кроме того, в 16 -разрядной шине ISA любое подключенное к ней устройство могло выступать в роли задатчика, то есть инициировать операцию обмена данными (в 8 -разрядной шине задатчиками были только процессор и контроллер DMA). Для подключения 16 разрядных устройств используются разъёмы, состоящие из двух частей: полностью совместимой с 8 -разрядной шиной 62 -контактной и новой 36 -контактной. Ввиду движения по направлению к проприетарной шине Micro Channel Architecture (MCA), IBM тогда практически прекратила поддержку ISA в своих продуктах. 16 -bit Network Interface Card IBM 83 X 9648.

Немного истории В противовес усилиям IBM по созданию MCA, в 1988 консорциумом из девяти основных производителей компьютеров была обнародована 32 -разрядная архитектура системной шины EISA, которая при сходных возможностях и перспективах развития являлась всего лишь надстройкой над «классической ISA» . В 1993 году компании Intel и Microsoft усовершенствовали шину в плане поддержки Plug and Play, таким образом явив миру ISA Pn. P, которая позволяла операционной системе самой определять ресурсы, назначаемое для устройства (прерывание, адреса памяти для обмена с системой и т. п. ). Интерфейс ISA был основным на системах типа AT, в дальнейшем с середины 1990 -х годов на материнских платах форм-фактора ATX, он стал вытесняться перспективными PCI. Последним чипсетом домашнего назначения использующим шину ISA стал KT 133 фирмы VIA выпускавшийся в 2000 -2001 годах. Белые разъёмы на материнской плате — 32 -разрядные PCI

Немного истории В противовес усилиям IBM по созданию MCA, в 1988 консорциумом из девяти основных производителей компьютеров была обнародована 32 -разрядная архитектура системной шины EISA, которая при сходных возможностях и перспективах развития являлась всего лишь надстройкой над «классической ISA» . В 1993 году компании Intel и Microsoft усовершенствовали шину в плане поддержки Plug and Play, таким образом явив миру ISA Pn. P, которая позволяла операционной системе самой определять ресурсы, назначаемое для устройства (прерывание, адреса памяти для обмена с системой и т. п. ). Интерфейс ISA был основным на системах типа AT, в дальнейшем с середины 1990 -х годов на материнских платах форм-фактора ATX, он стал вытесняться перспективными PCI. Последним чипсетом домашнего назначения использующим шину ISA стал KT 133 фирмы VIA выпускавшийся в 2000 -2001 годах. Белые разъёмы на материнской плате — 32 -разрядные PCI