Шестнадцатибитные таймеры – счетчики общего назначения Т 1

Шестнадцатибитные таймеры – счетчики общего назначения Т 1 и Т 3.

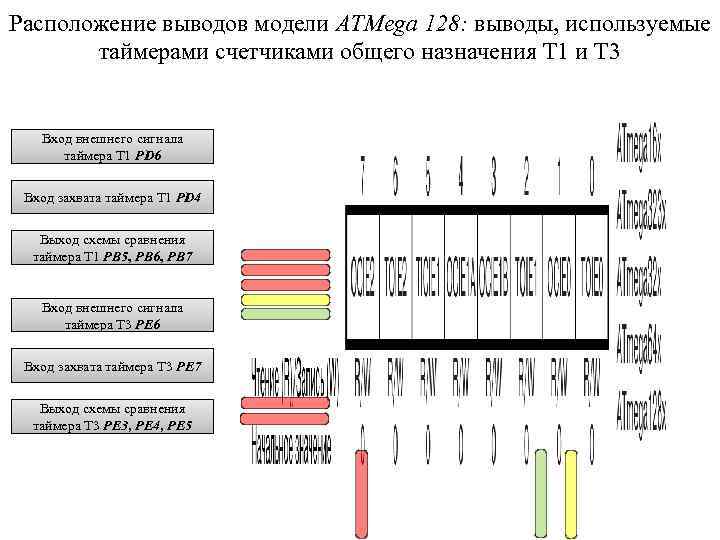

Расположение выводов модели ATMega 128: выводы, используемые таймерами счетчиками общего назначения Т 1 и Т 3 Вход внешнего сигнала таймера T 1 PD 6 Вход захвата таймера T 1 PD 4 Выход схемы сравнения таймера T 1 PB 5, PB 6, PB 7 Вход внешнего сигнала таймера T 3 PE 6 Вход захвата таймера T 3 PE 7 Выход схемы сравнения таймера T 3 PE 3, PE 4, PE 5

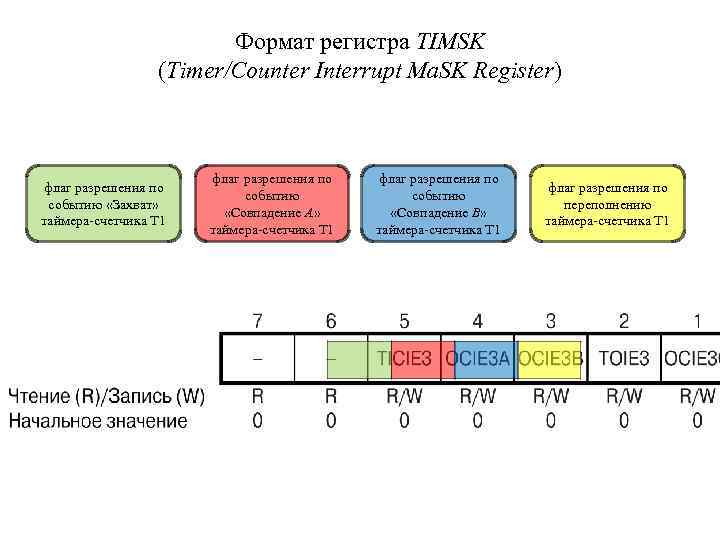

Формат регистра TIMSK (Timer/Counter Interrupt Ma. SK Register) флаг разрешения по флаг разрешения по событию «Захват» переполнению «Совпадение А» «Совпадение B» таймера-счетчика Т 1 таймера-счетчика Т 1

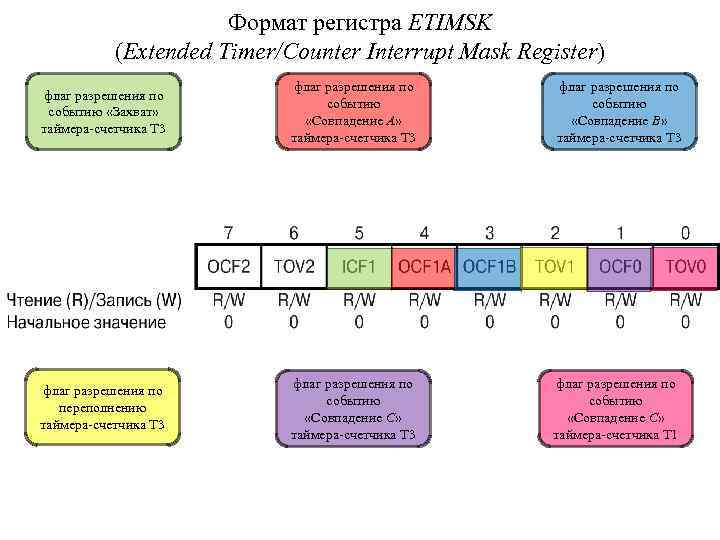

Формат регистра ETIMSK (Extended Timer/Counter Interrupt Mask Register) флаг разрешения по событию «Захват» «Совпадение А» «Совпадение B» таймера-счетчика Т 3 таймера-счетчика Т 3 флаг разрешения по переполнению событию таймера-счетчика Т 3 «Совпадение C» таймера-счетчика Т 3 таймера-счетчика Т 1

Формат регистра TIFR (Timer/Counter Interrupt Flag Register) флаг прерывания по флаг прерывания по событию «Захват» переполнению «Совпадение А» «Совпадение B» таймера-счетчика Т 1 таймера-счетчика Т 1

Блок предделителя таймера-счетчика (с асинхронным режимом) Счетчик (синхронизация по фронту) PD 6 задает сброс предделитей задают вывод необходимого сигнала Мультиплексор

Структурная схема 16 -разрядных таймеров – счетчиков (Т 1 и Т 3) тактовый сигнал вход внешнего сигнала 16 -разрядный счетный регистр TCNT 1(TCNT 3) выходы схемы сравнения 16 -разрядные регистры сравнения OCR 1 A, OCR 1 B, OCR 1 C (OCR 3 A, OCR 3 B, OCR 3 C) 16 -разрядный регистр вход захвата таймера захвата ICR 1(ICR 3) 16 -разрядные регистры управления TCC 1 A, TCC 1 B, TCCC 1 C (TCC 1 A, TCC 1 B, TCCC 1 C)

Работа регистров OCR 1 A/OCR 1 B/OCR 1 C (OCR 3 A/OCR 3 B/OCR 3 C) на примере OCR 1 A Машинные Операции: Результат Действия при « 1» циклы сравнения N OCR 1 A == TCNT 1 неверно N+1 OCR 1 A == TCNT 1 неверно N+2 OCR 1 A == TCNT 1 верно N+3 OCR 1 A == TCNT 1 неверно Установить TIFR[OCF 1 A] =1; сгенерировать прерывание. Кроме того возможно: изменение состояние вывода OC 1 A N+4 OCR 1 A == TCNT 1 неверно . . N+k-1 OCR 1 A == TCNT 1 верно N+k OCR 1 A == TCNT 1 неверно Установить TIFR[OCF 1 A] =1; сгенерировать прерывание. Кроме того возможно: изменение состояние вывода OC 1 A

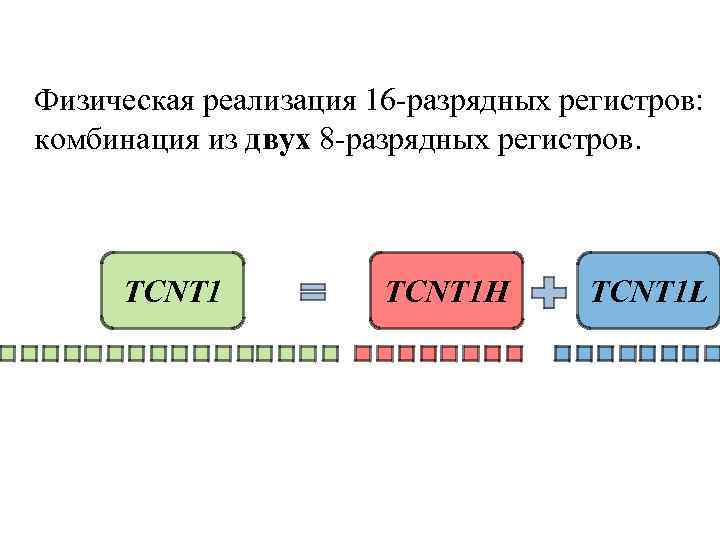

Физическая реализация 16 -разрядных регистров: комбинация из двух 8 -разрядных регистров. TCNT 1 H TCNT 1 L

Структурная схема блока захвата Разряды регистра TCCR 1 B

Формат и разряды регистров TCCR 1 A (a) и TCCR 3 A (б) 0

Формат регистров TCCR 1 B (а) и TCCR 3 B (б)

Разряды регистров TCCR 1 B (а) и TCCR 3 B (б)

Формат и разряды регистров TCCR 1 C (а) и TCCR 3 C (б)

Временные диаграммы для режима СТС

Управление выводом OC 1 A (OC 3 A) в режиме СТС

Спасибо за внимание

Лекция Таймеры-счетчики общего назначения.ppt

- Количество слайдов: 17