САПР комбинационных логических схем на основе методов

САПР комбинационных логических схем на основе методов декомпозиции

Детализация блоков 1. Принудительная параллельная декомпозиция 2. Последовательная декомпозиция одновыходовых блоков 3. Выделение тёхвходового блока

Детализация блоков. 1 этап.

Детализация блоков. 2 этап.

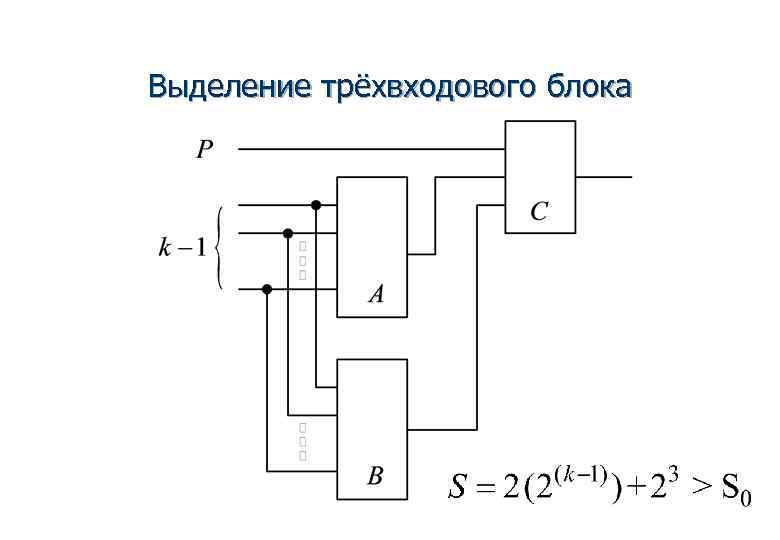

Выделение трёхвходового блока

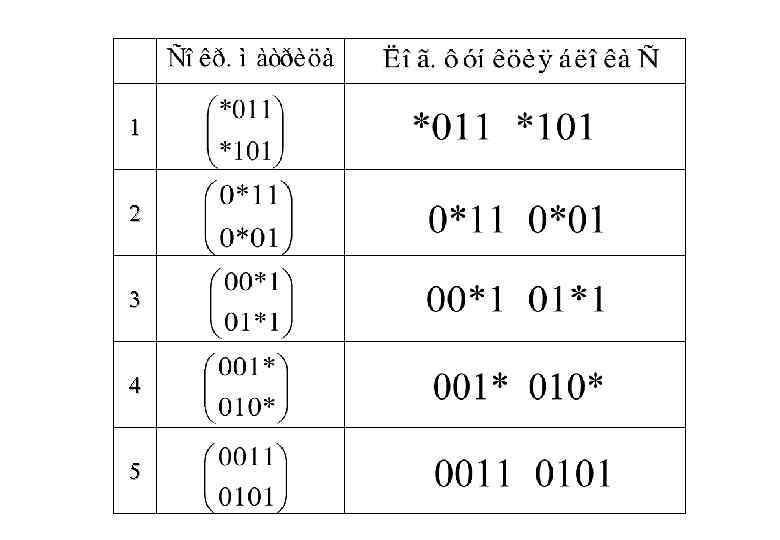

1 2 3 4 5

3 -й этап детализации – разделение трёхвходовых блоков на двухвходовые

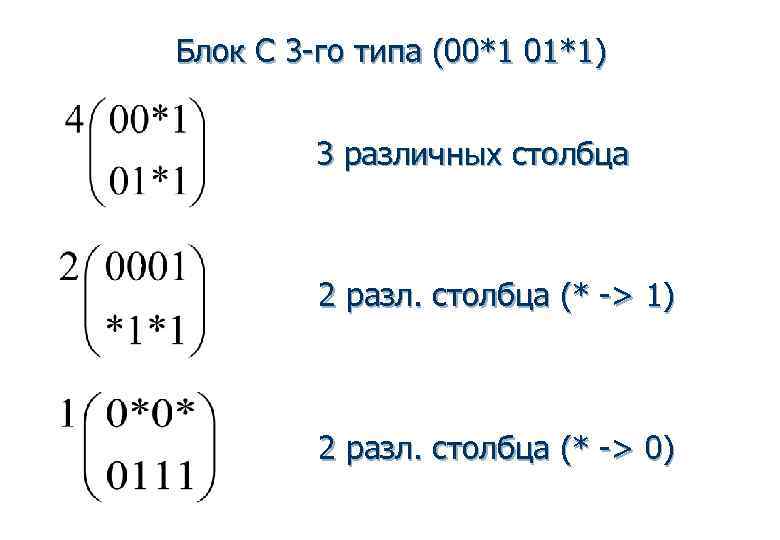

Блок С 3 -го типа (00*1 01*1) 3 различных столбца 2 разл. столбца (* -> 1) 2 разл. столбца (* -> 0)

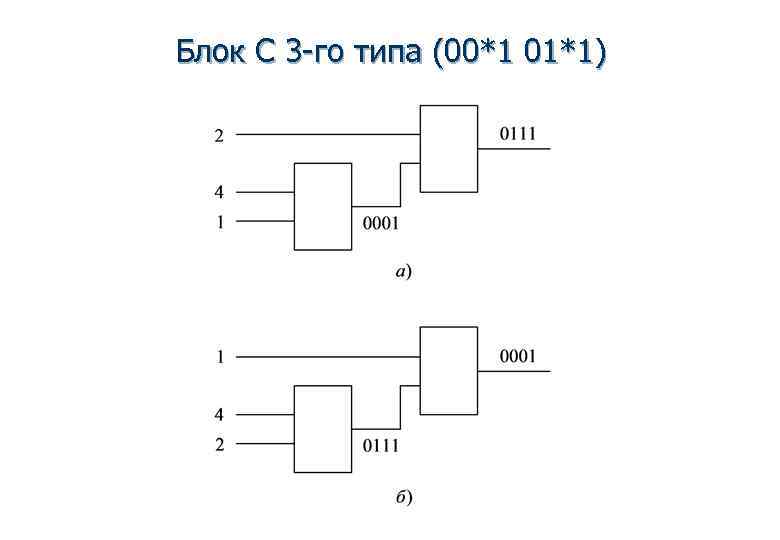

Блок С 3 -го типа (00*1 01*1)

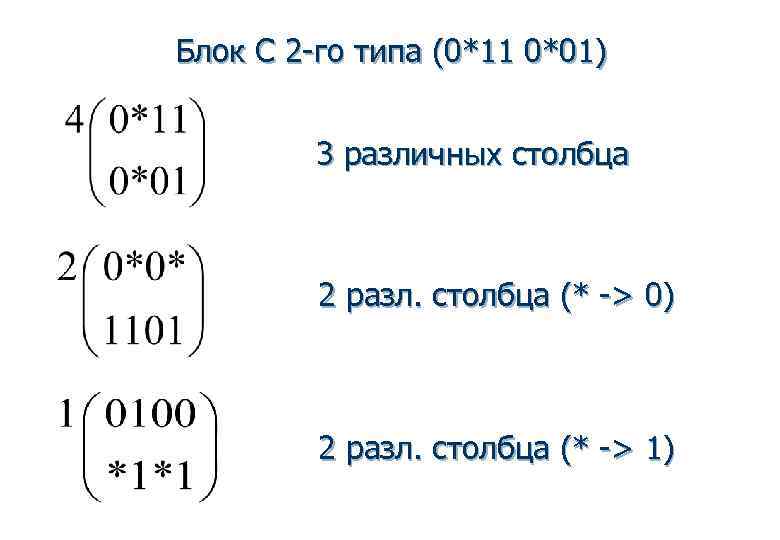

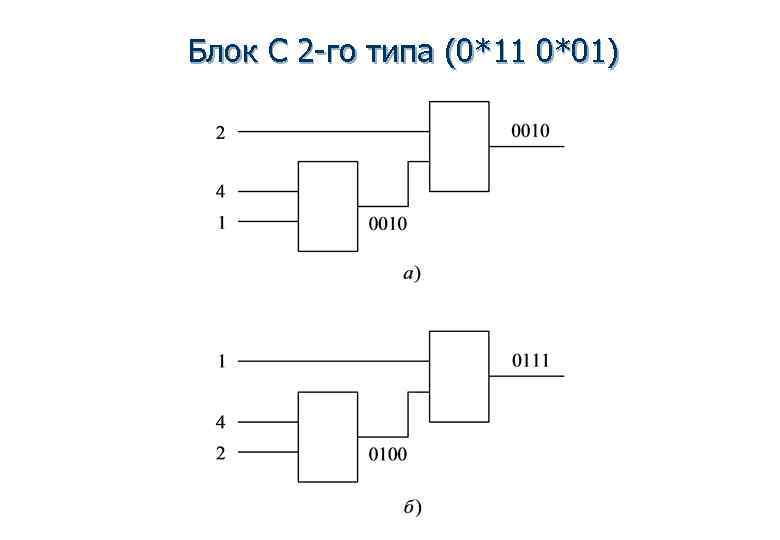

Блок С 2 -го типа (0*11 0*01) 3 различных столбца 2 разл. столбца (* -> 0) 2 разл. столбца (* -> 1)

Блок С 2 -го типа (0*11 0*01)

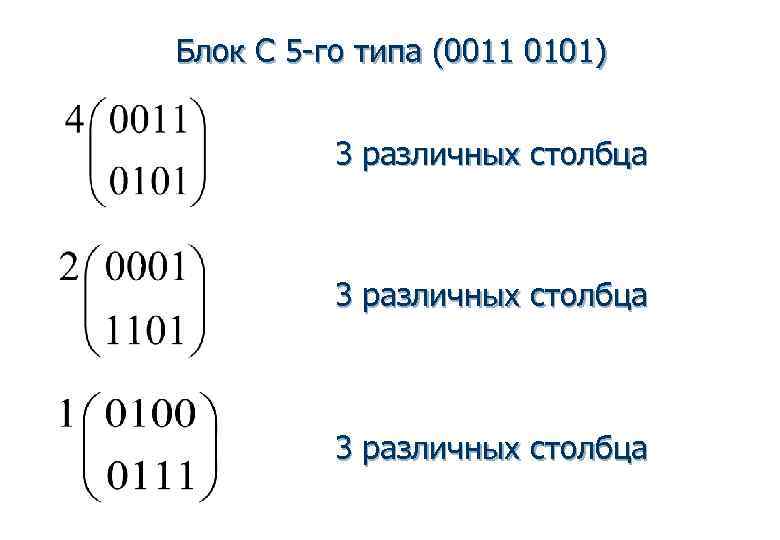

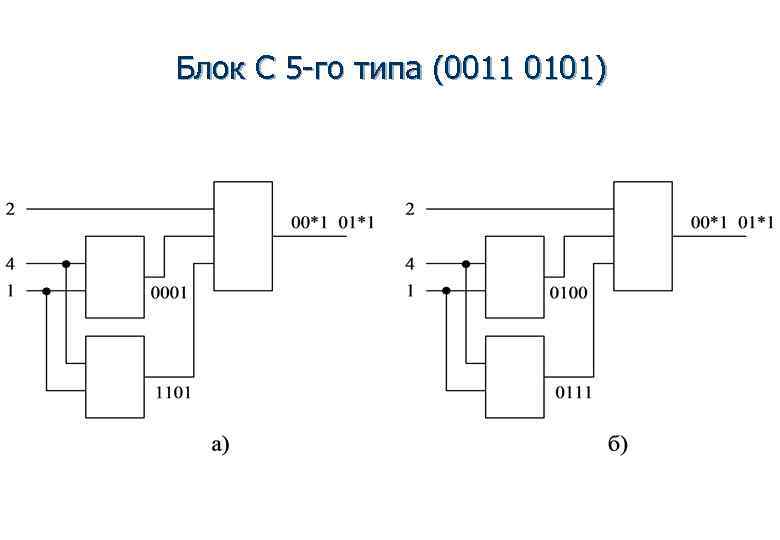

Блок С 5 -го типа (0011 0101) 3 различных столбца

Блок С 5 -го типа (0011 0101)

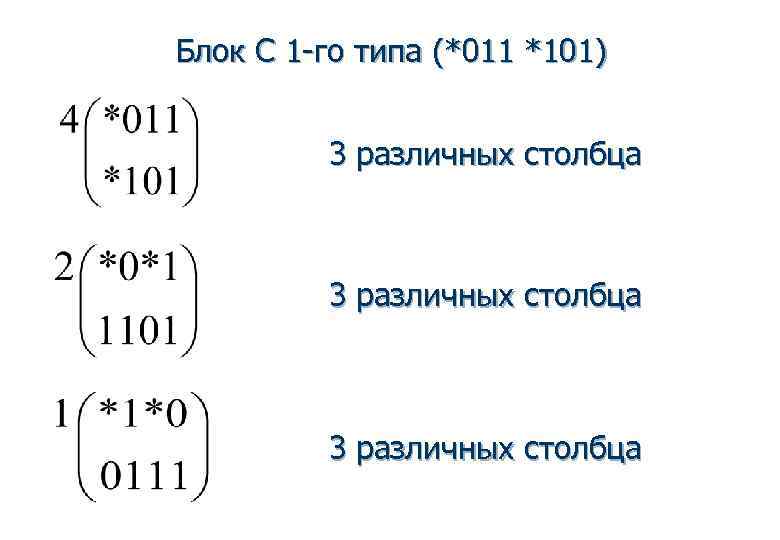

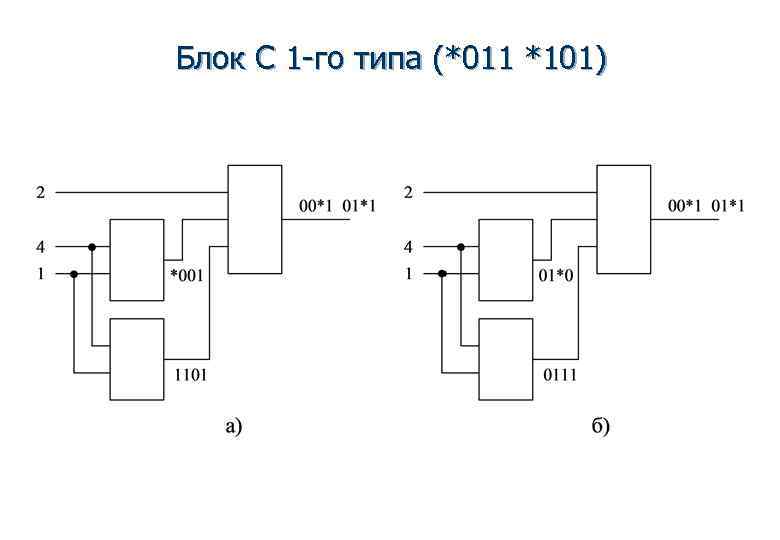

Блок С 1 -го типа (*011 *101) 3 различных столбца

Блок С 1 -го типа (*011 *101)

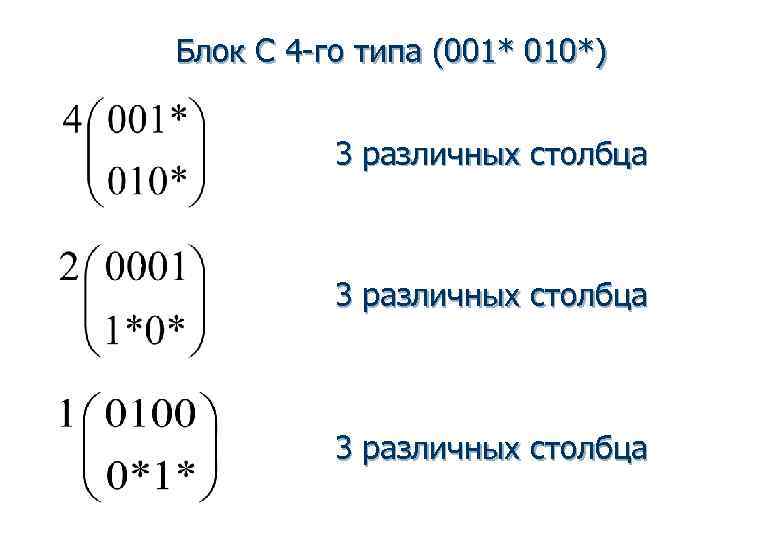

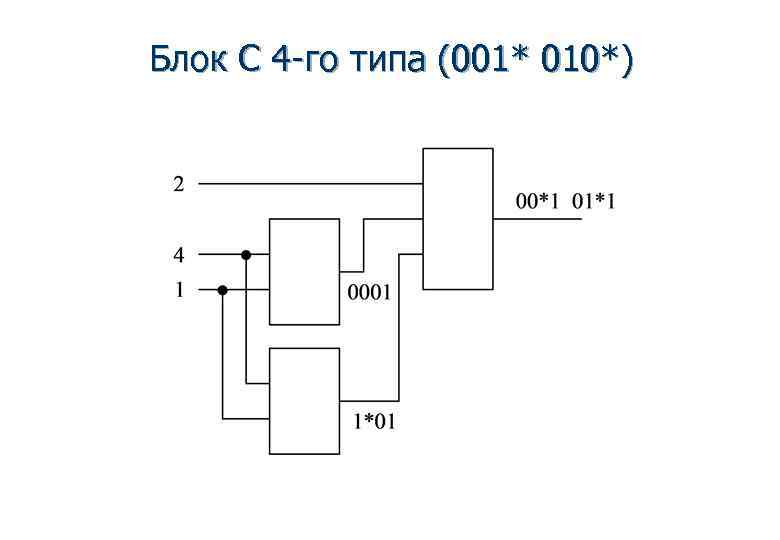

Блок С 4 -го типа (001* 010*) 3 различных столбца

Блок С 4 -го типа (001* 010*)

Покрытие схем двухвходовыми элементами: 1. « 2 И» , « 2 ИЛИ» , «НЕ» 2. « 2 И-НЕ» 3. « 2 ИЛИ-НЕ»

Основные принципы преобразования логических элементов

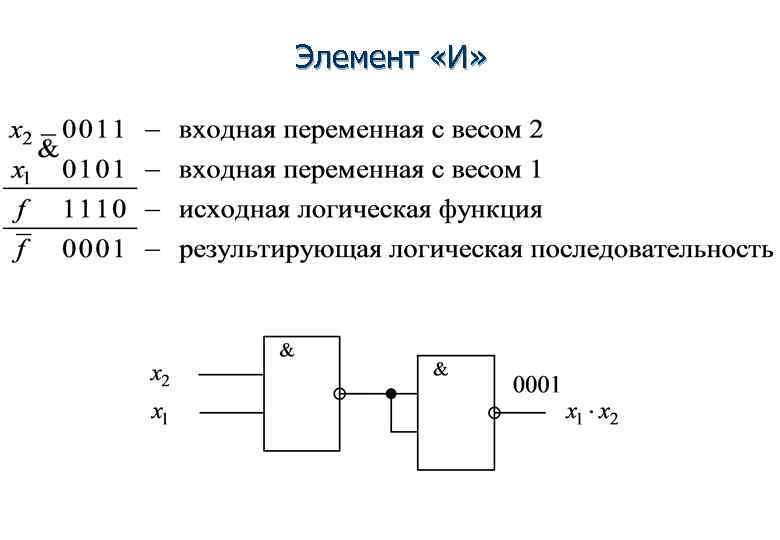

Элементы типа «И» (содержат одну единицу в последовательности) - 0001, функция «И» - 0010, функция «ЗАПРЕТ» - 0100, функция «ЗАПРЕТ» - 1000, ф. «СТРЕЛКА ПИРСА»

Элементы типа «ИЛИ» (содержат три единицы в последовательности) - 0111, функция «ИЛИ» - 1011, ф. «ИМПЛИКАЦИЯ» - 1101, ф. «ИМПЛИКАЦИЯ» - 1110, ф. «ШТРИХ ШЕФФЕРА»

Элементы типа «М 2» (содержат две единицы в последовательности) - 0110, функция «НЕРАВНОЗНАЧНОСТЬ» , «ИСКЛЮЧАЮЩЕЕ ИЛИ» -1001, функция «РАВНОЗНАЧНОСТЬ» , «ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ»

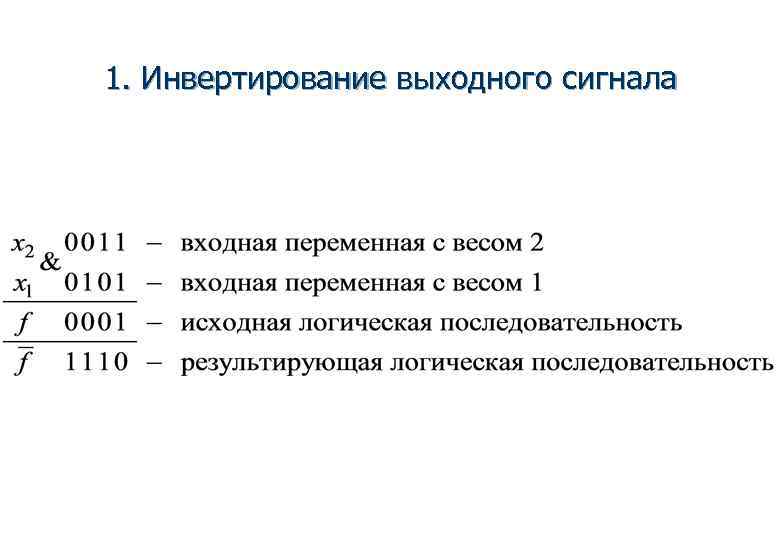

1. Инвертирование выходного сигнала

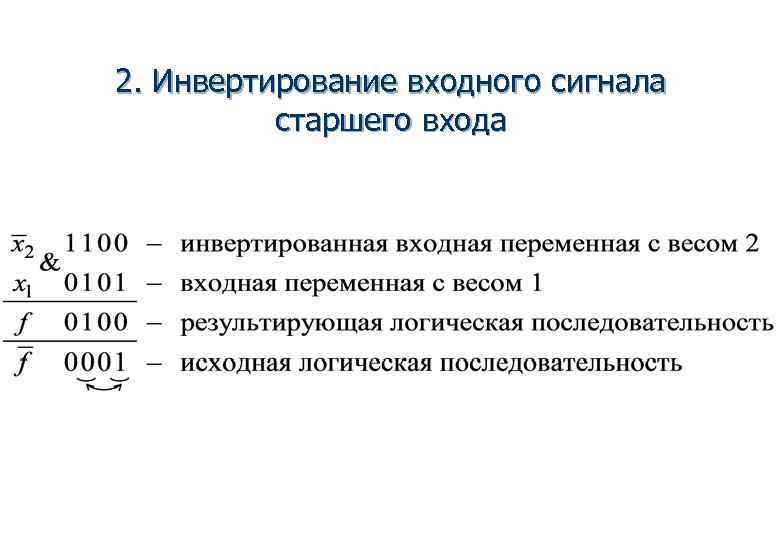

2. Инвертирование входного сигнала старшего входа

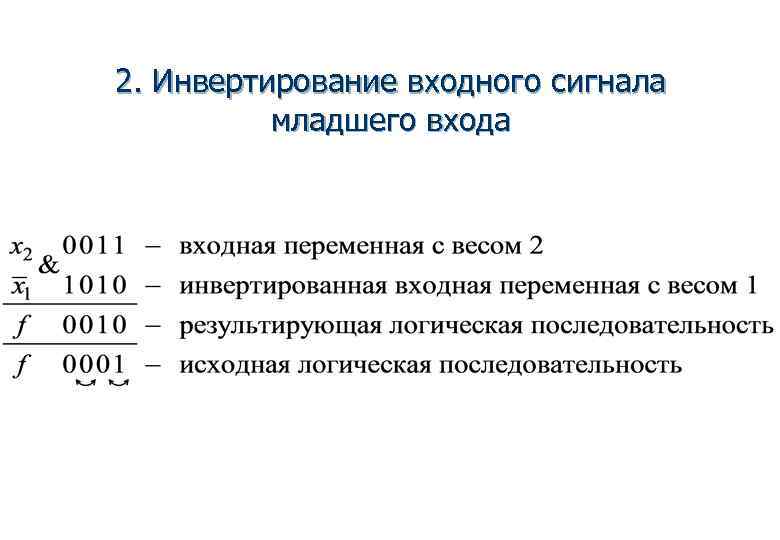

2. Инвертирование входного сигнала младшего входа

Инвертор

Элемент «И»

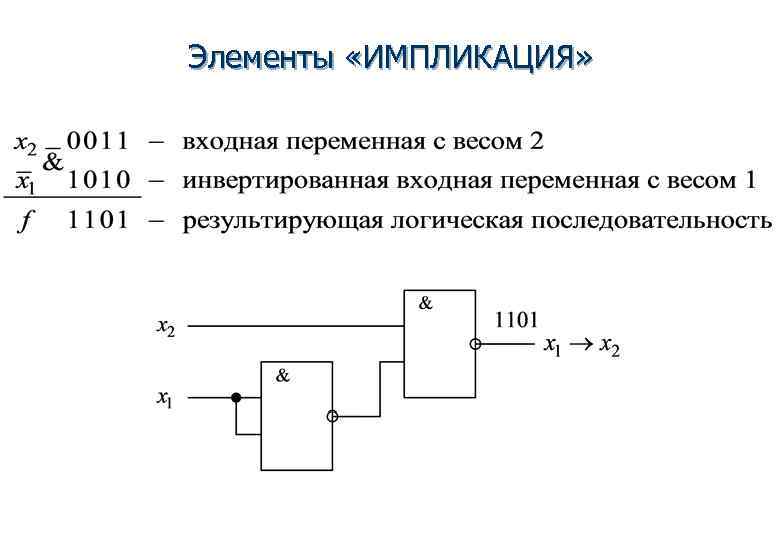

Элементы «ИМПЛИКАЦИЯ»

Элементы «ИМПЛИКАЦИЯ»

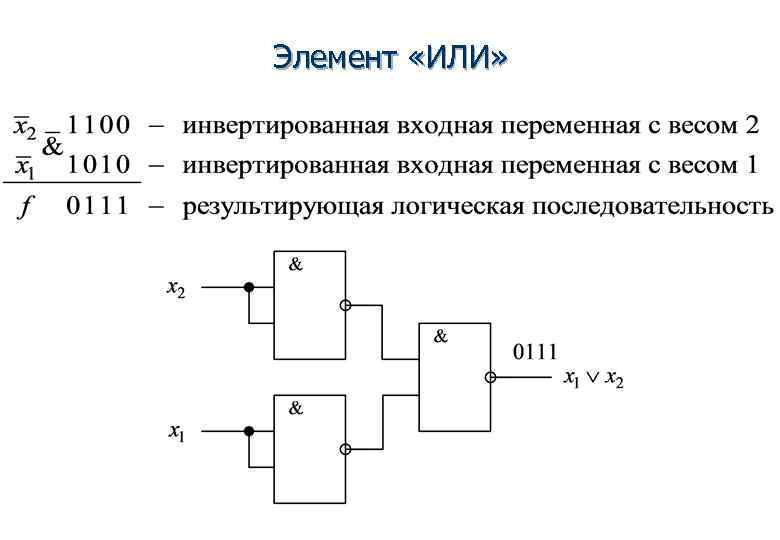

Элемент «ИЛИ»

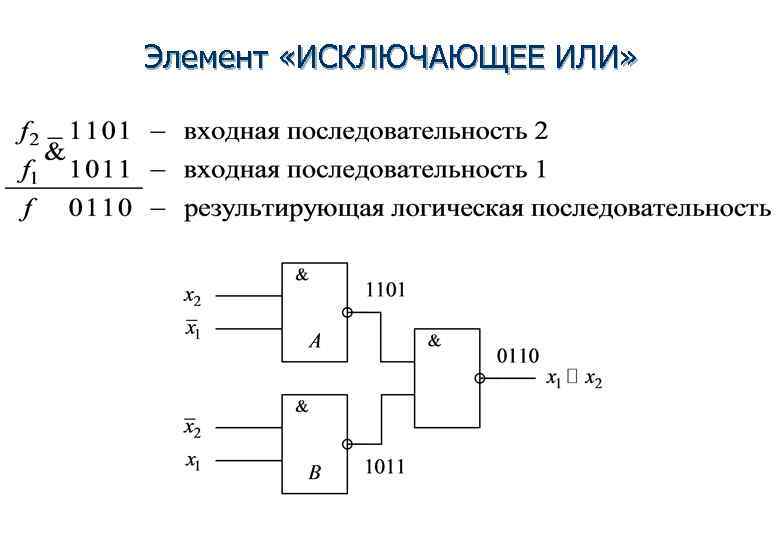

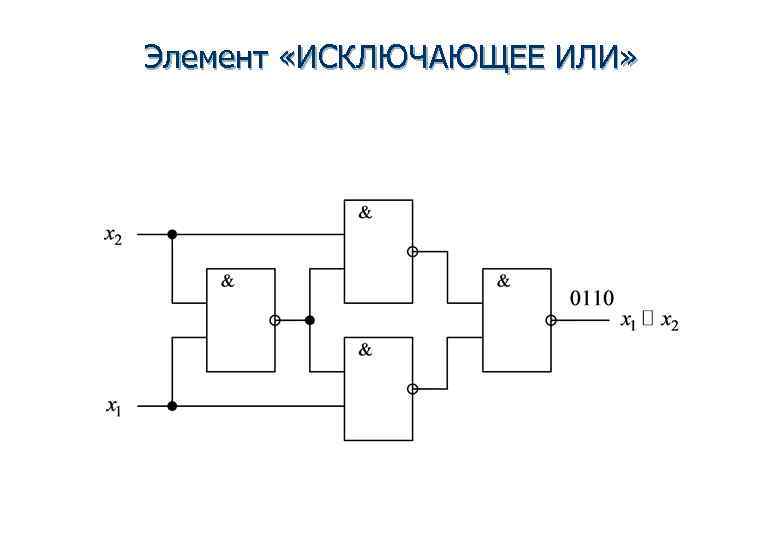

Элемент «ИСКЛЮЧАЮЩЕЕ ИЛИ»

Элемент «ИСКЛЮЧАЮЩЕЕ ИЛИ»

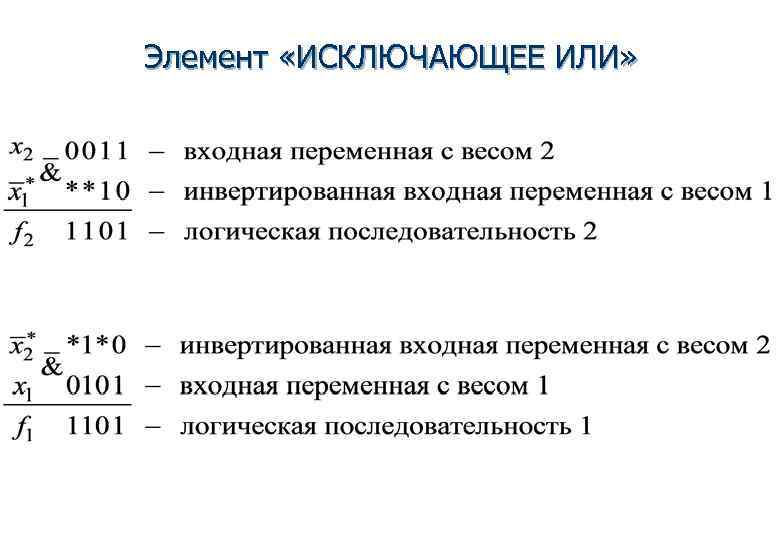

Элемент «ИСКЛЮЧАЮЩЕЕ ИЛИ»

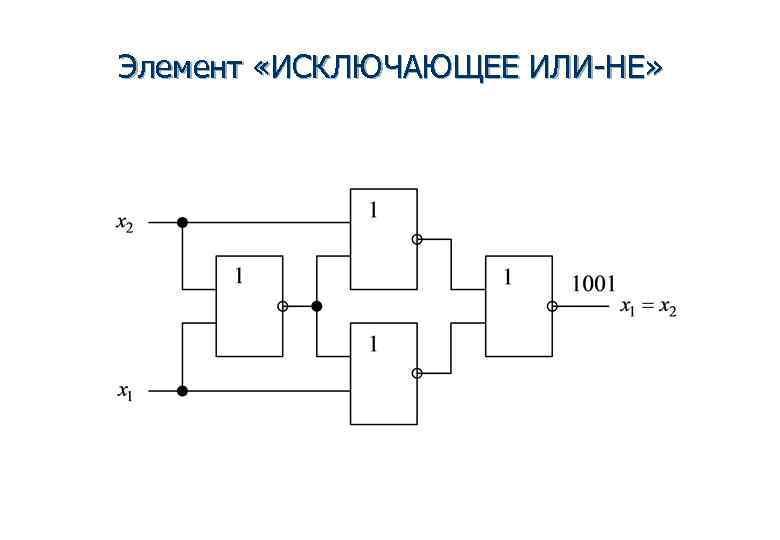

Элемент «ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ»

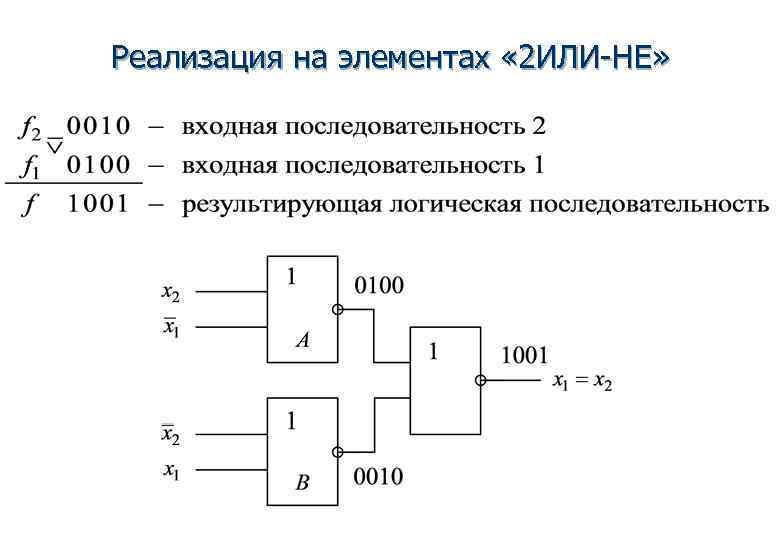

Реализация на элементах « 2 ИЛИ-НЕ»

Элемент «ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ»

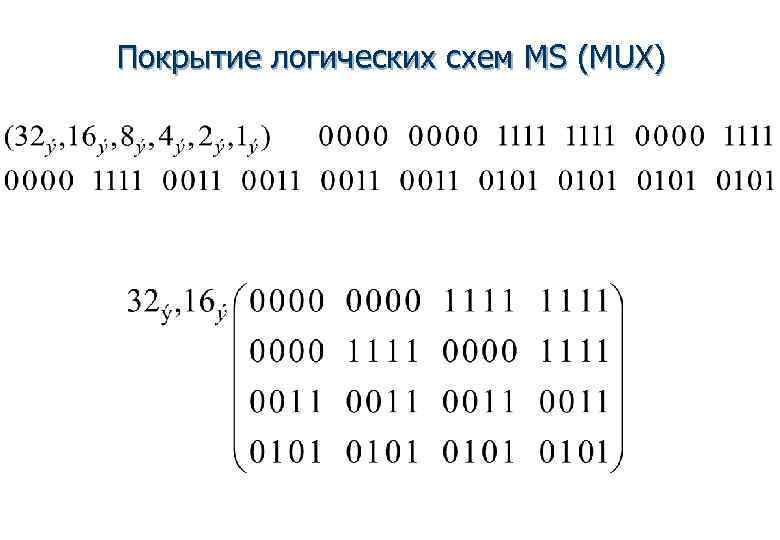

Покрытие логических схем MS (MUX)

Покрытие логических схем MS (MUX)

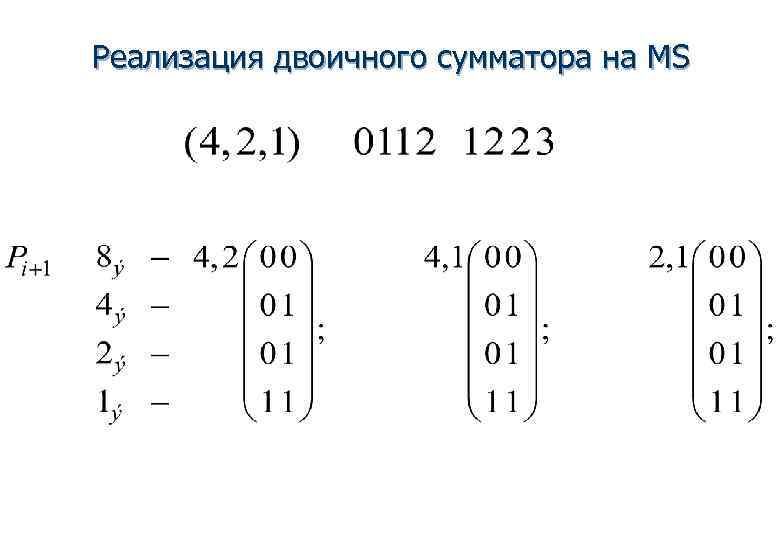

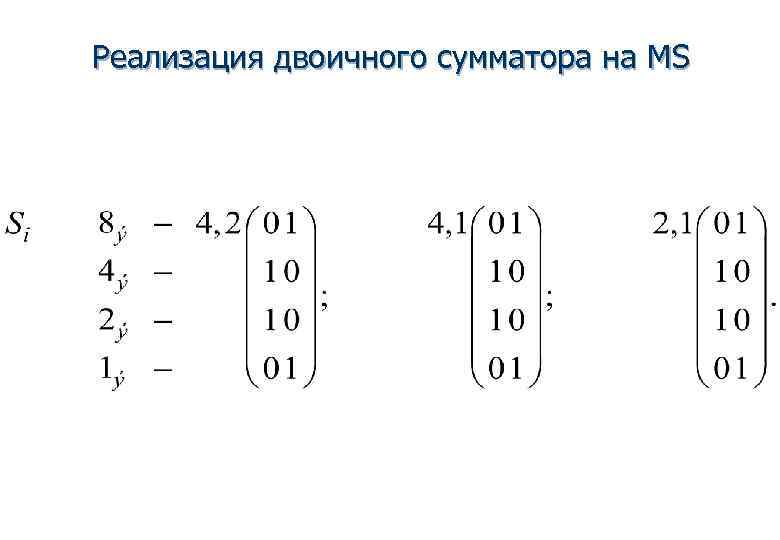

Реализация двоичного сумматора на MS

Реализация двоичного сумматора на MS

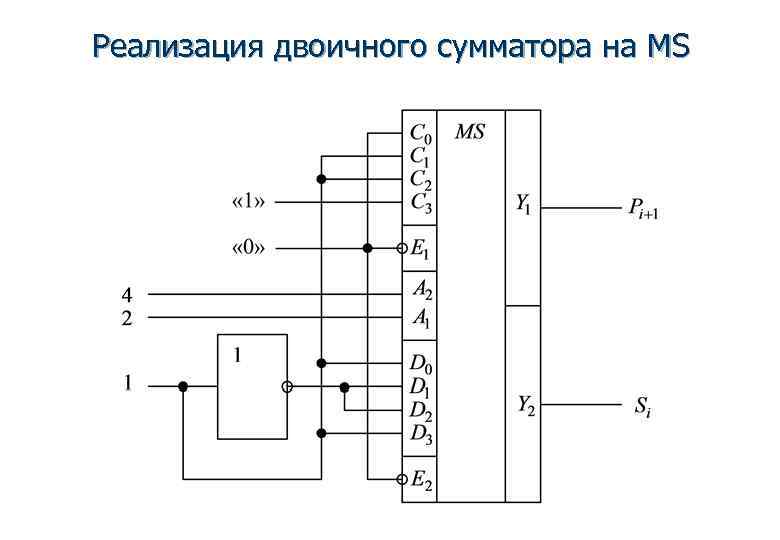

Реализация двоичного сумматора на MS

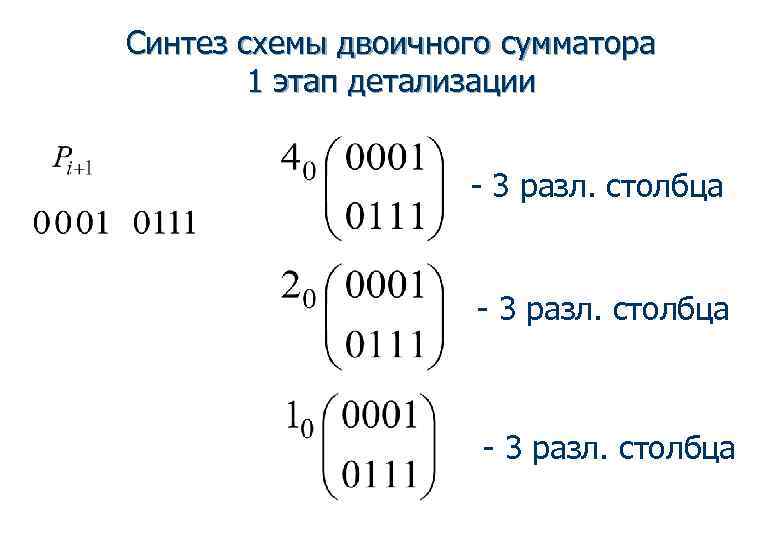

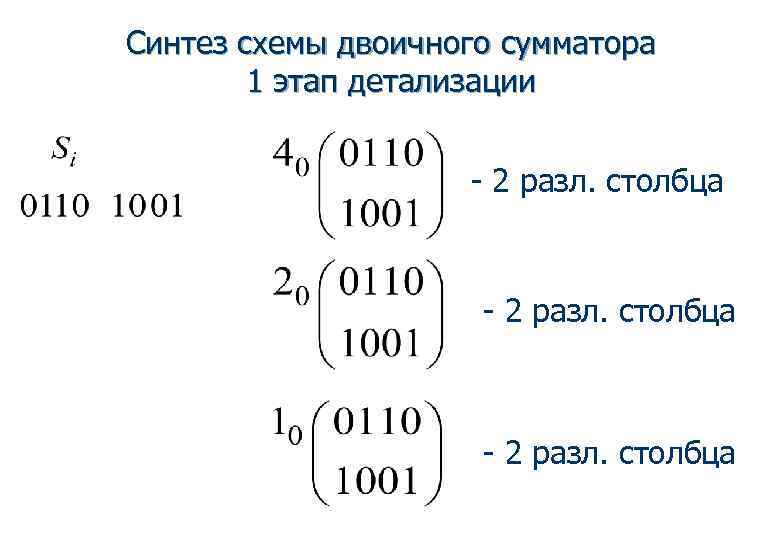

Синтез схемы двоичного сумматора 1 этап детализации - 3 разл. столбца

Синтез схемы двоичного сумматора 1 этап детализации - 2 разл. столбца

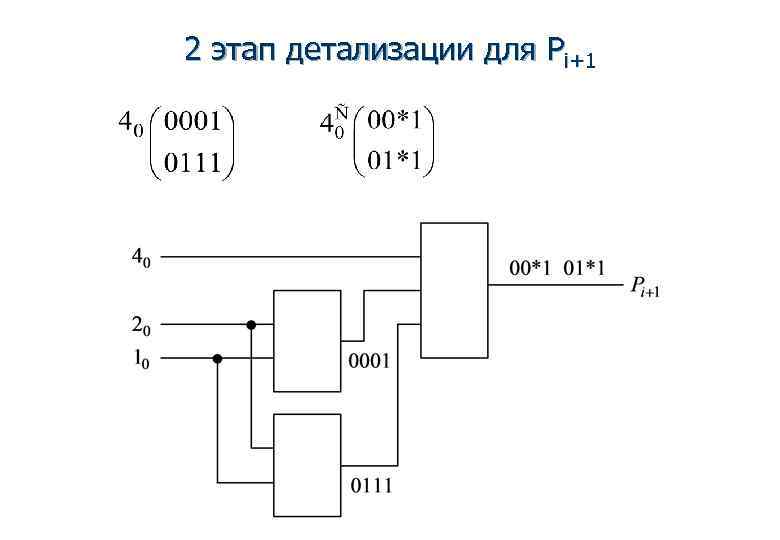

2 этап детализации для Pi+1

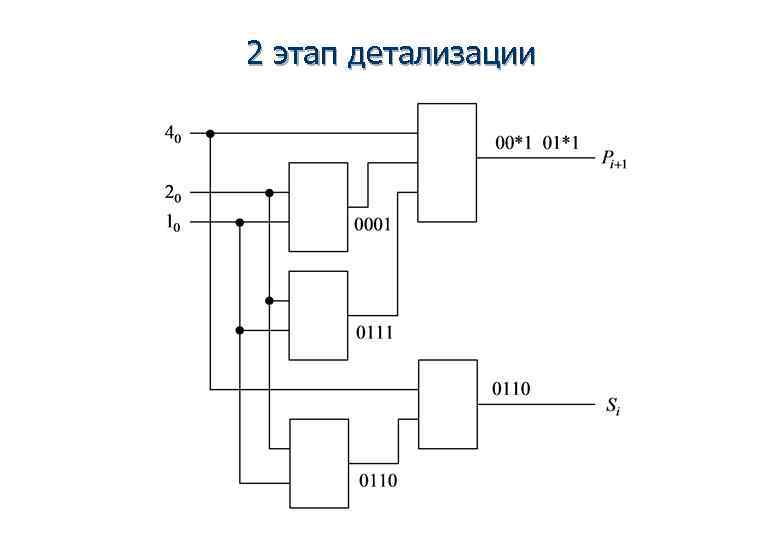

2 этап детализации

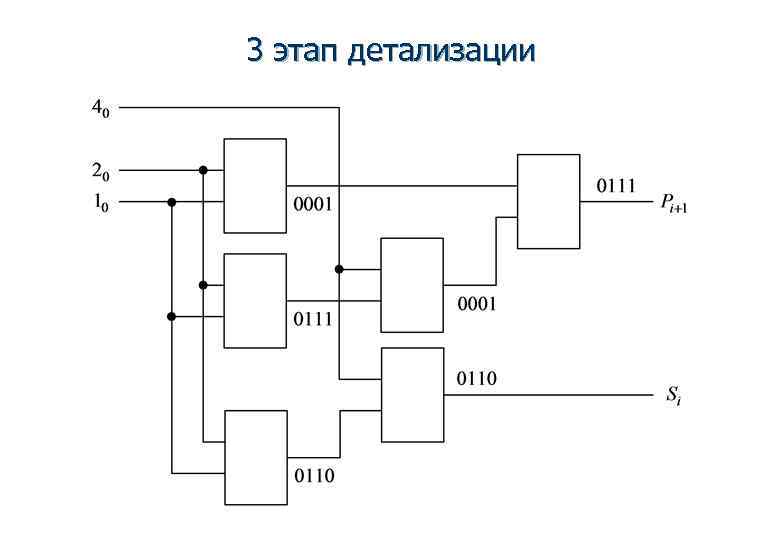

3 этап детализации

Покрытие схемы двоичного сумматора элементами «И» , «ИЛИ» , «НЕ»

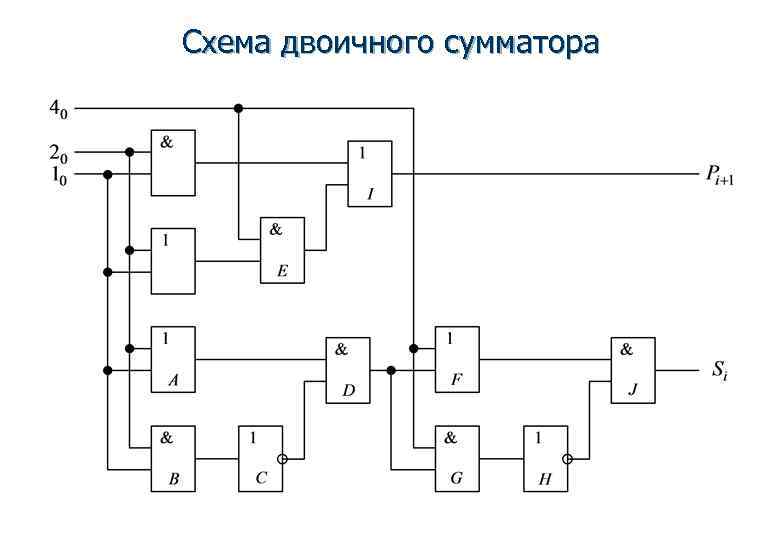

Схема двоичного сумматора

Оптимизация схемы двоичного сумматора 1 этап

Оптимизация схемы двоичного сумматора 2 этап Исключение из схемы цепочек последовательно соединённых инверторов

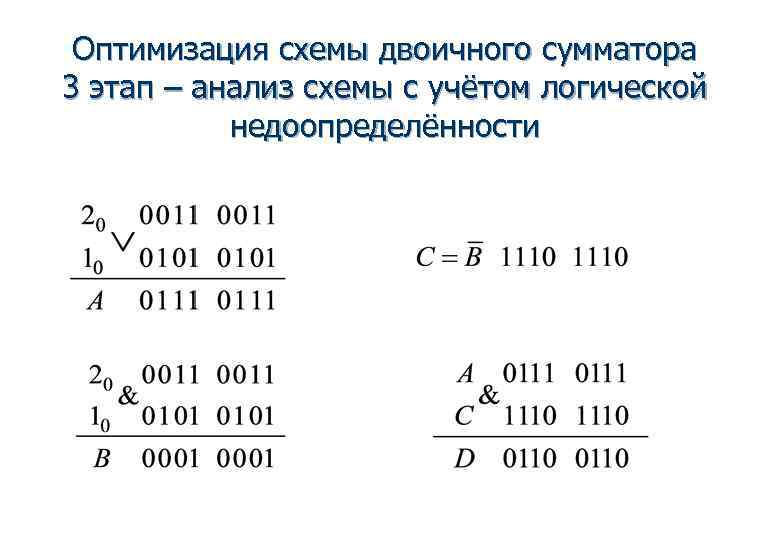

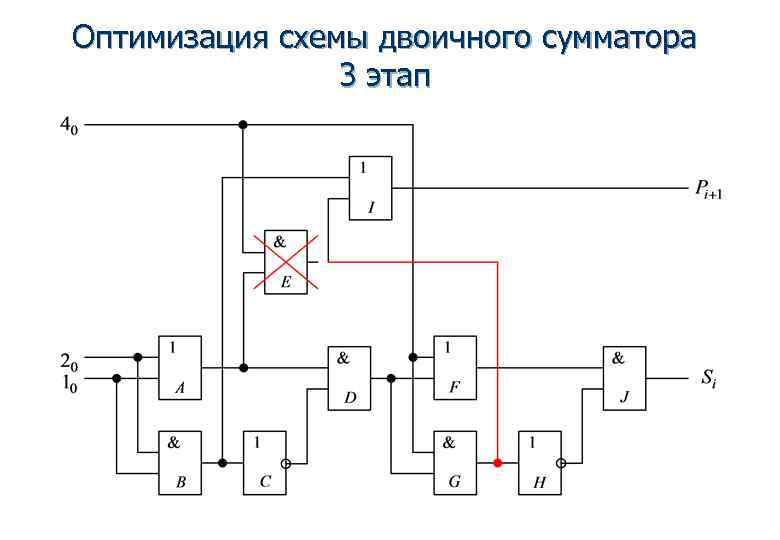

Оптимизация схемы двоичного сумматора 3 этап – анализ схемы с учётом логической недоопределённости

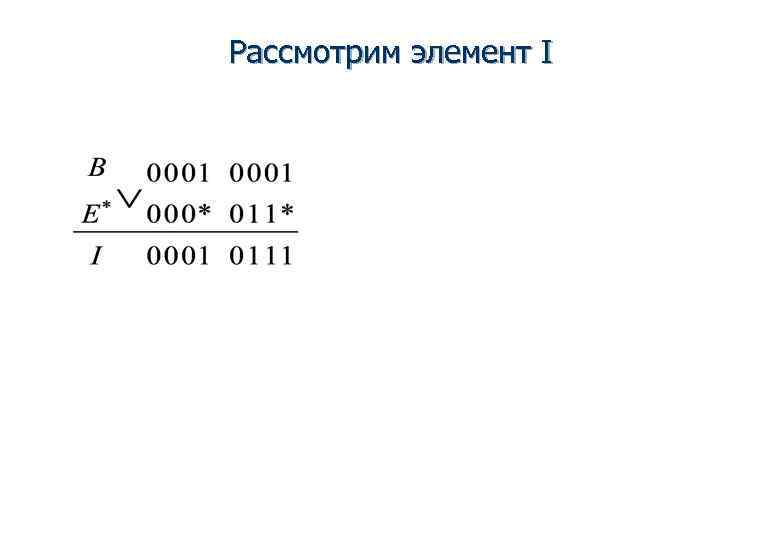

Рассмотрим элемент I

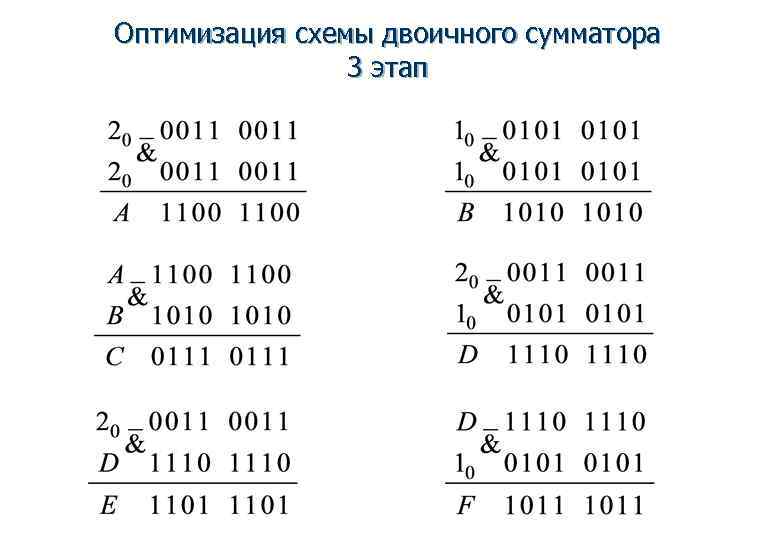

Оптимизация схемы двоичного сумматора 3 этап

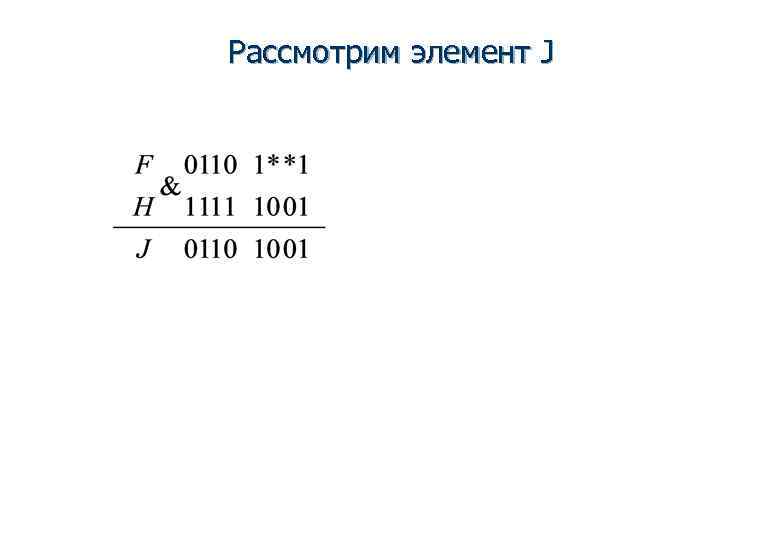

Рассмотрим элемент J

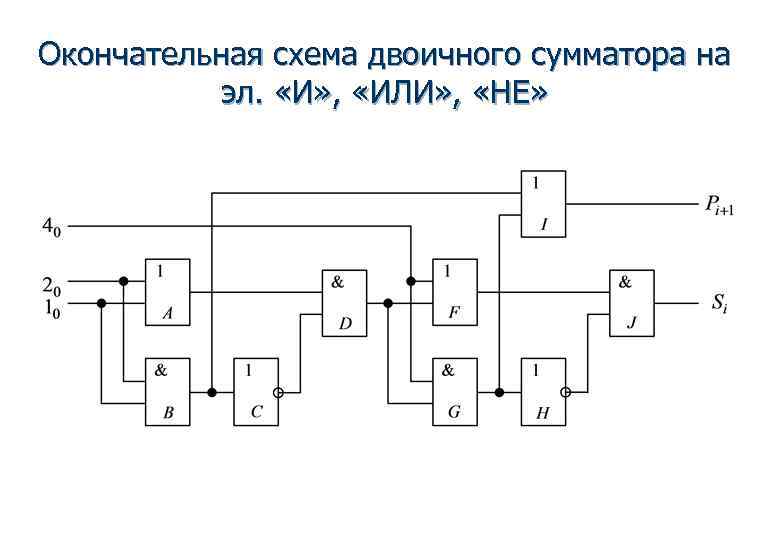

Окончательная схема двоичного сумматора на эл. «И» , «ИЛИ» , «НЕ»

Покрытие схемы двоичного сумматора элементами «И-НЕ»

Оптимизация схемы двоичного сумматора на элементах «И-НЕ»

Оптимизация схемы двоичного сумматора 3 этап

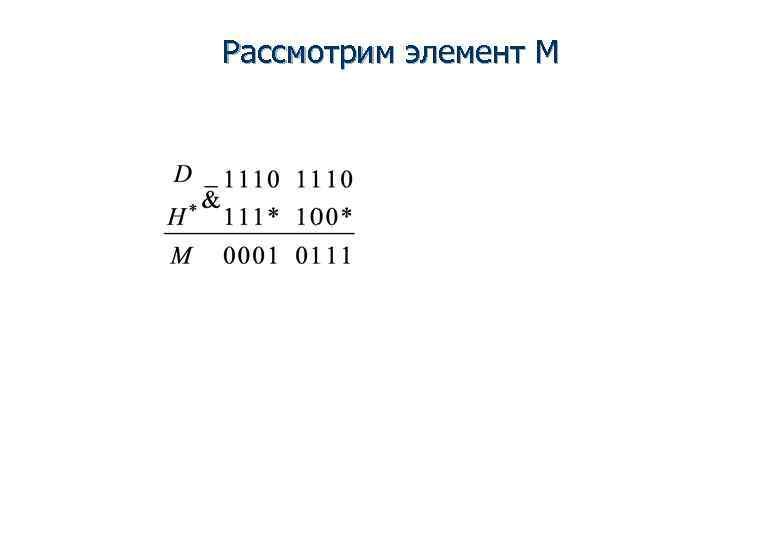

Рассмотрим элемент M

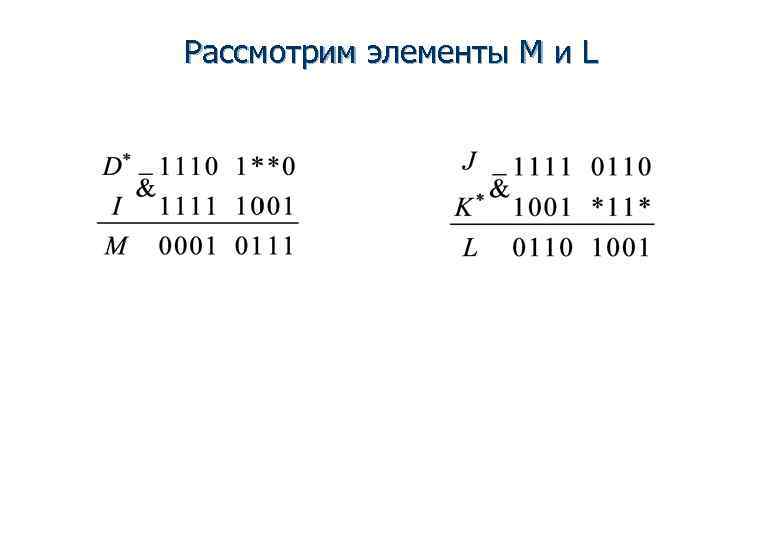

Рассмотрим элементы M и L

Окончательная оптимизированная схема двоичного сумматора на эл. « 2 И-НЕ»

Многоуровневая оптимизация Мультиплексор 2/1

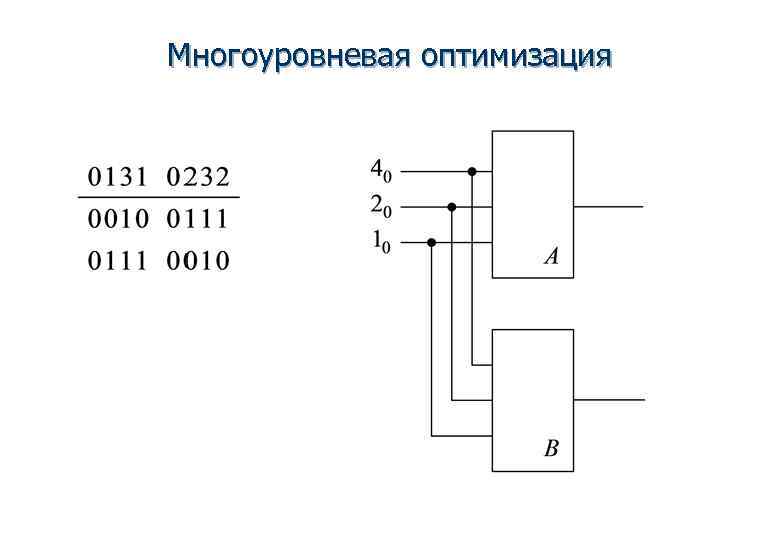

Многоуровневая оптимизация

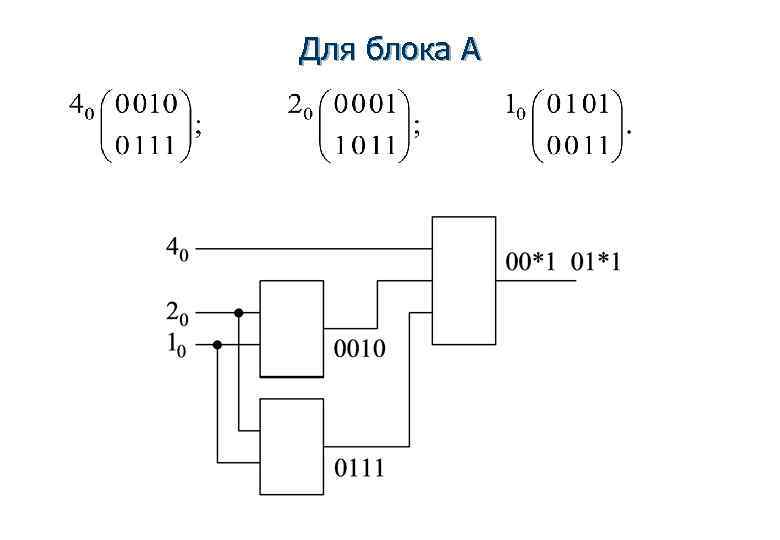

Для блока A

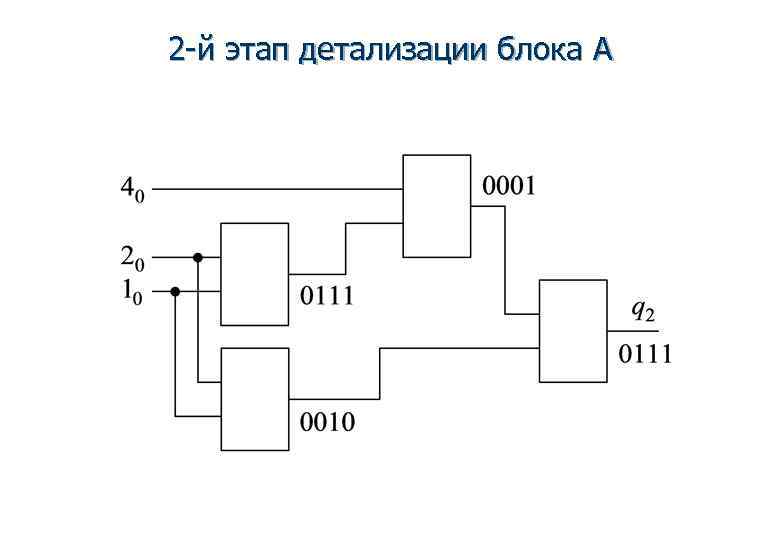

2 -й этап детализации блока A

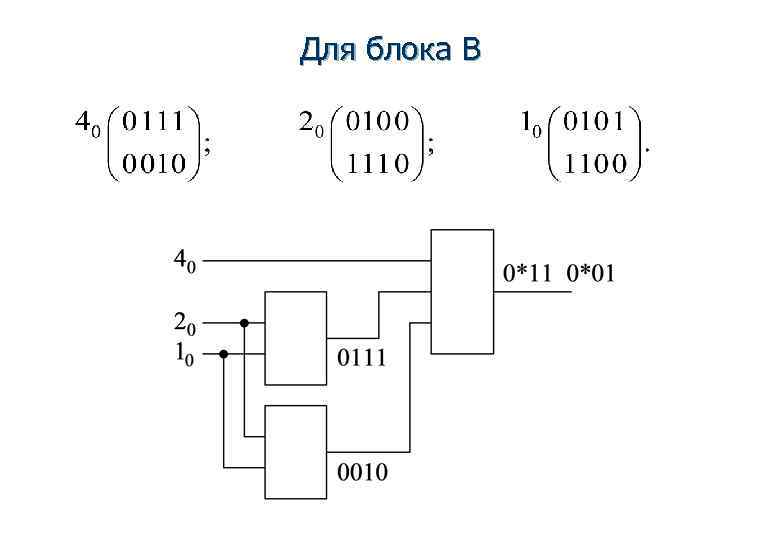

Для блока B

2 -й этап детализации блока B

Синтез двоично-десятичного сумматора с использованием программы Decomposer Иллюстрация возможностей программы на примере синтеза двоично-десятичного сумматора

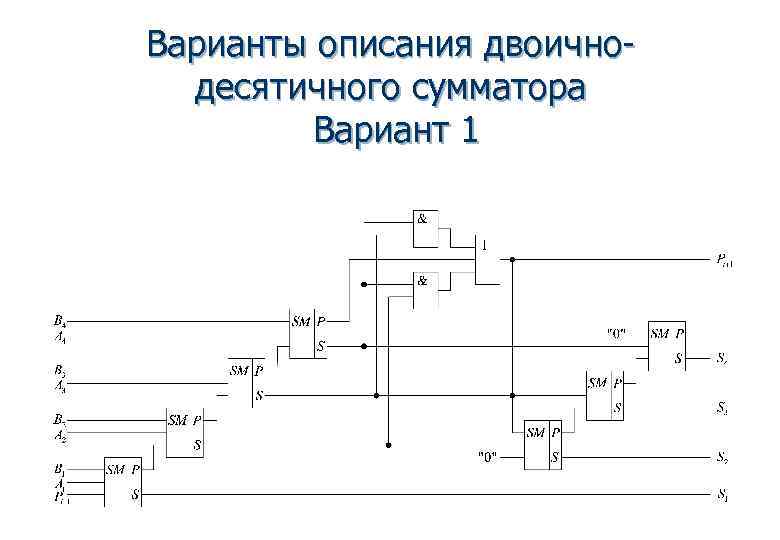

Варианты описания двоично- десятичного сумматора Вариант 1

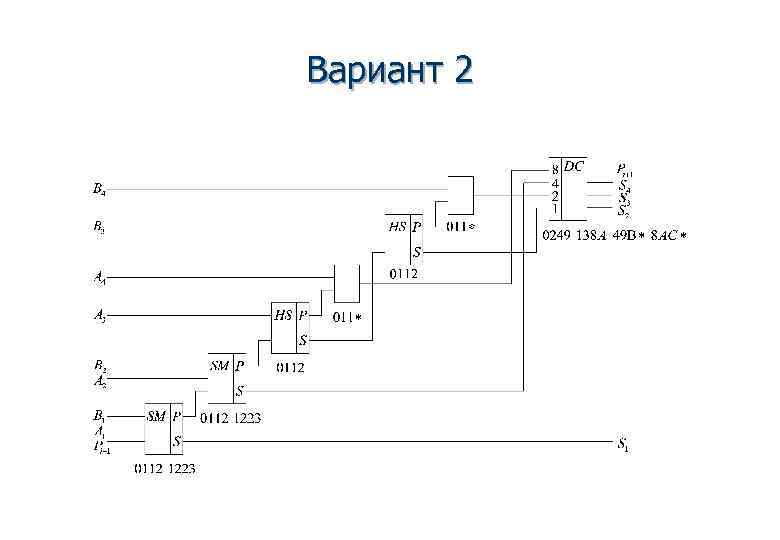

Вариант 2

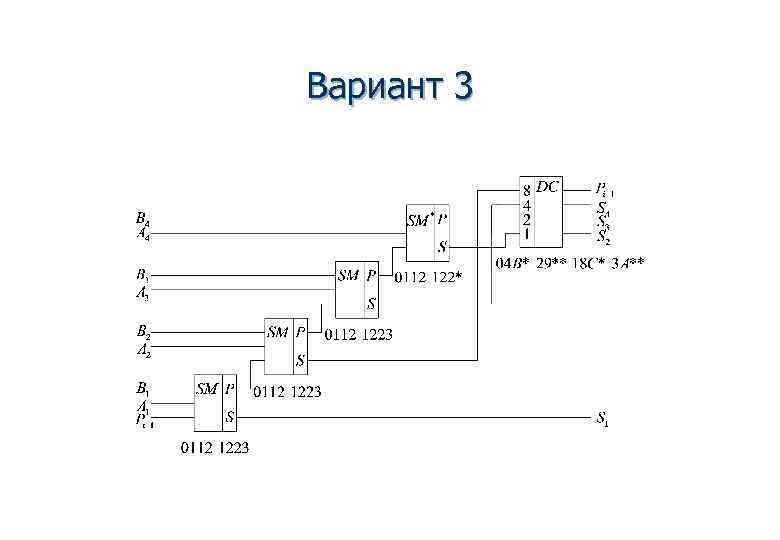

Вариант 3

Вариант 4 – Описание на языке VHDL library IEEE; use IEEE. STD_LOGIC_1164. ALL; use IEEE. STD_LOGIC_ARITH. ALL; use IEEE. STD_LOGIC_UNSIGNED. ALL; entity ADD is Port(A: in std_logic_vector(3 downto 0); B: in std_logic_vector(3 downto 0); S: out std_logic_vector(3 downto 0); CI: in std_logic; CO: out std_logic); end ADD; architecture Behavioral of ADD is signal sum: std_logic_vector(4 downto 0); begin sum <= ('0'&A) + ('0'&B) + CI; S <= sum(3 downto 0) when sum < "01010" else (sum - "01010"); CO <= '0' when sum < "01010" else '1'; end Behavioral;

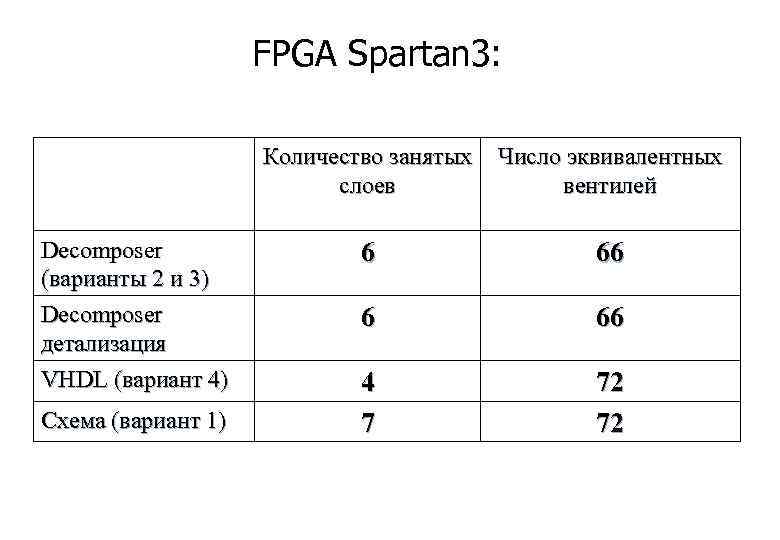

FPGA Spartan 3: Количество занятых Число эквивалентных слоев вентилей Decomposer 66 (варианты 2 и 3) Decomposer 66 детализация VHDL (вариант 4) 4 72 Схема (вариант 1) 7 72

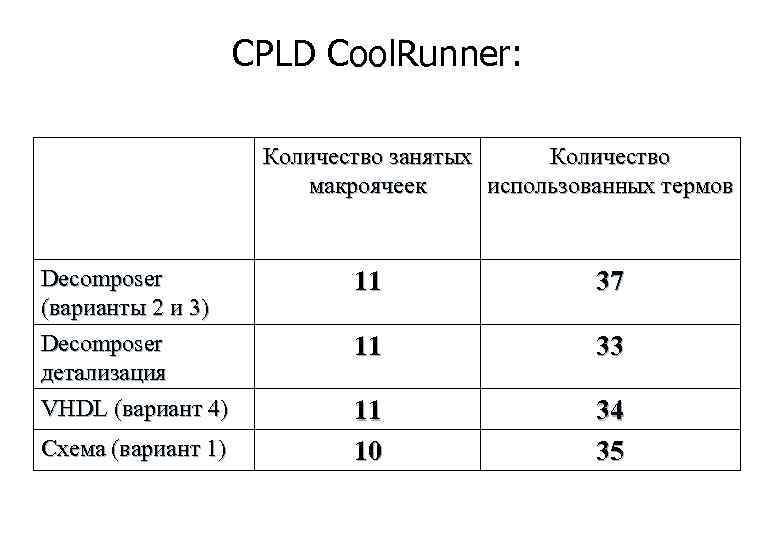

CPLD Cool. Runner: Количество занятых Количество макроячеек использованных термов Decomposer 11 37 (варианты 2 и 3) Decomposer 11 33 детализация VHDL (вариант 4) 11 34 Схема (вариант 1) 10 35

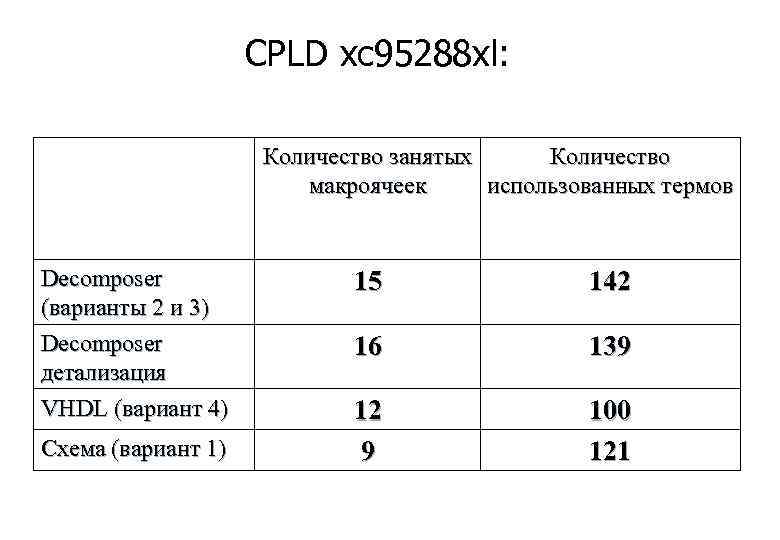

CPLD xc 95288 xl: Количество занятых Количество макроячеек использованных термов Decomposer 15 142 (варианты 2 и 3) Decomposer 16 139 детализация VHDL (вариант 4) 12 100 Схема (вариант 1) 9 121

Детализация, покрытие и оптимизация КЛС.ppt

- Количество слайдов: 75