9c438ffc54427669ad1f844e9fe9a587.ppt

- Количество слайдов: 16

RPC Trigger Software ESR, July 2003

RPC Trigger Software ESR, July 2003

Tasks n n n n subsystem DCS subsystem Run Control online monitoring of the subsystem provide tools needed to perform on- and offdetector diagnostic tests provide a repository for storing information about state, history, etc. of each hardware item provide tools needed to perform analysis of the whole subsystem, e. g. to find possible causes of the lack of input from one particular strip (problem solver) perform subsystem calibration ESR, July 2003 2

Tasks n n n n subsystem DCS subsystem Run Control online monitoring of the subsystem provide tools needed to perform on- and offdetector diagnostic tests provide a repository for storing information about state, history, etc. of each hardware item provide tools needed to perform analysis of the whole subsystem, e. g. to find possible causes of the lack of input from one particular strip (problem solver) perform subsystem calibration ESR, July 2003 2

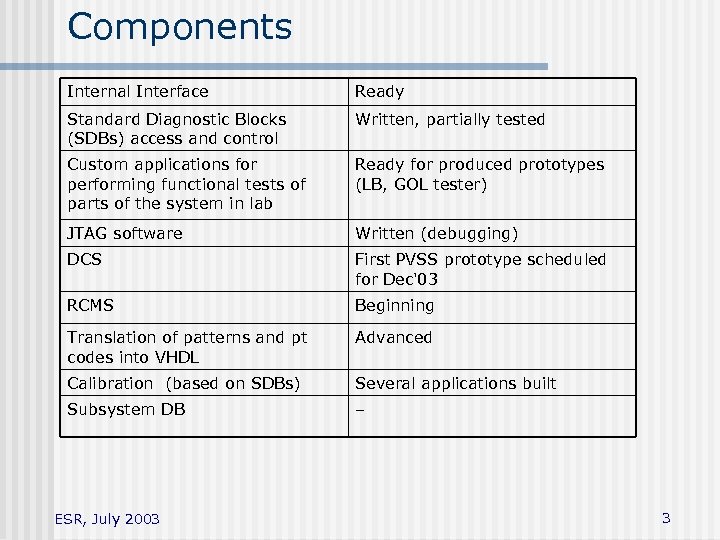

Components Internal Interface Ready Standard Diagnostic Blocks (SDBs) access and control Written, partially tested Custom applications for performing functional tests of parts of the system in lab Ready for produced prototypes (LB, GOL tester) JTAG software Written (debugging) DCS First PVSS prototype scheduled for Dec'03 RCMS Beginning Translation of patterns and pt codes into VHDL Advanced Calibration (based on SDBs) Several applications built Subsystem DB – ESR, July 2003 3

Components Internal Interface Ready Standard Diagnostic Blocks (SDBs) access and control Written, partially tested Custom applications for performing functional tests of parts of the system in lab Ready for produced prototypes (LB, GOL tester) JTAG software Written (debugging) DCS First PVSS prototype scheduled for Dec'03 RCMS Beginning Translation of patterns and pt codes into VHDL Advanced Calibration (based on SDBs) Several applications built Subsystem DB – ESR, July 2003 3

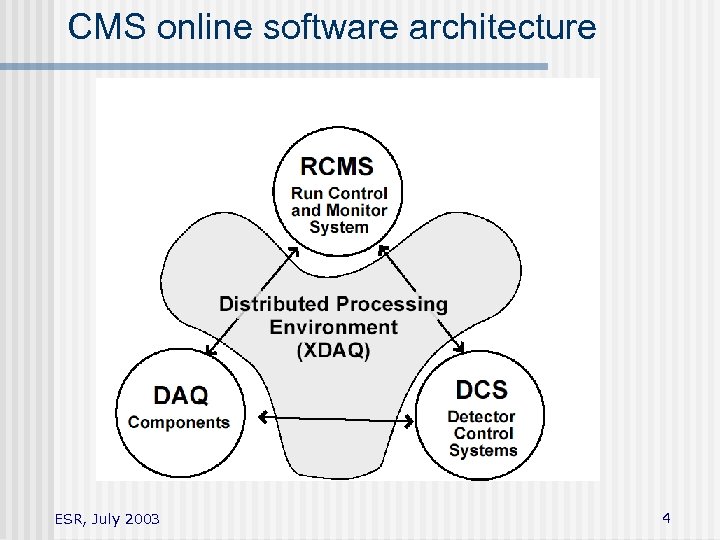

CMS online software architecture ESR, July 2003 4

CMS online software architecture ESR, July 2003 4

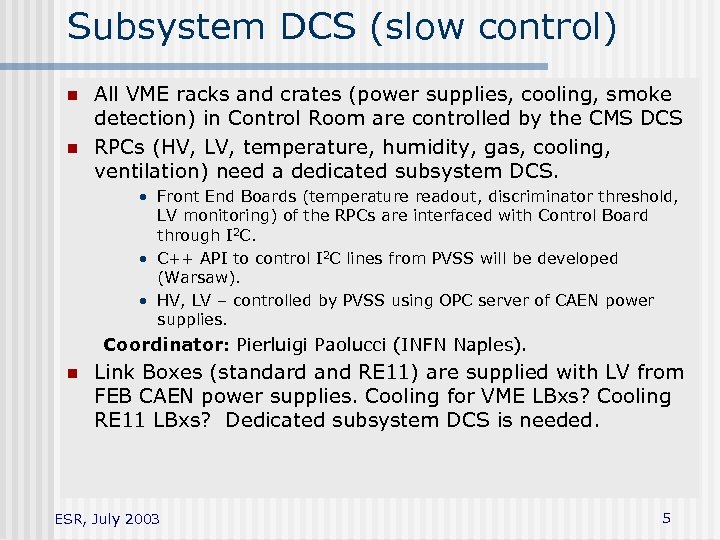

Subsystem DCS (slow control) n n All VME racks and crates (power supplies, cooling, smoke detection) in Control Room are controlled by the CMS DCS RPCs (HV, LV, temperature, humidity, gas, cooling, ventilation) need a dedicated subsystem DCS. • Front End Boards (temperature readout, discriminator threshold, LV monitoring) of the RPCs are interfaced with Control Board through I 2 C. • C++ API to control I 2 C lines from PVSS will be developed (Warsaw). • HV, LV – controlled by PVSS using OPC server of CAEN power supplies. Coordinator: Pierluigi Paolucci (INFN Naples). n Link Boxes (standard and RE 11) are supplied with LV from FEB CAEN power supplies. Cooling for VME LBxs? Cooling RE 11 LBxs? Dedicated subsystem DCS is needed. ESR, July 2003 5

Subsystem DCS (slow control) n n All VME racks and crates (power supplies, cooling, smoke detection) in Control Room are controlled by the CMS DCS RPCs (HV, LV, temperature, humidity, gas, cooling, ventilation) need a dedicated subsystem DCS. • Front End Boards (temperature readout, discriminator threshold, LV monitoring) of the RPCs are interfaced with Control Board through I 2 C. • C++ API to control I 2 C lines from PVSS will be developed (Warsaw). • HV, LV – controlled by PVSS using OPC server of CAEN power supplies. Coordinator: Pierluigi Paolucci (INFN Naples). n Link Boxes (standard and RE 11) are supplied with LV from FEB CAEN power supplies. Cooling for VME LBxs? Cooling RE 11 LBxs? Dedicated subsystem DCS is needed. ESR, July 2003 5

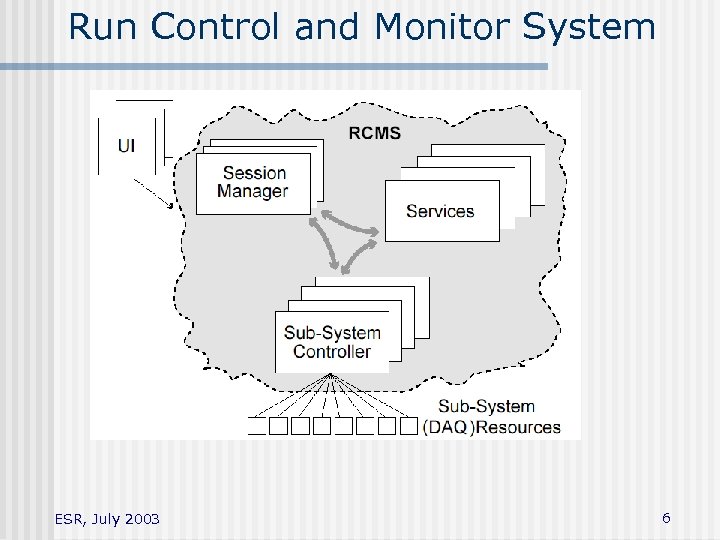

Run Control and Monitor System ESR, July 2003 6

Run Control and Monitor System ESR, July 2003 6

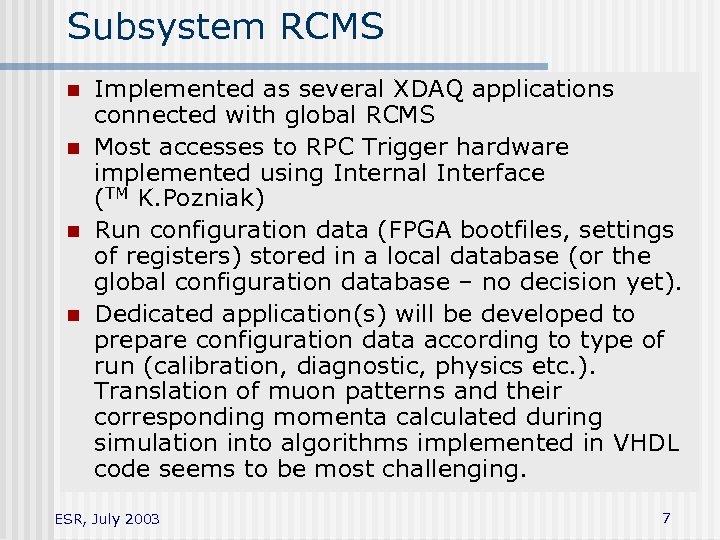

Subsystem RCMS n n Implemented as several XDAQ applications connected with global RCMS Most accesses to RPC Trigger hardware implemented using Internal Interface (TM K. Pozniak) Run configuration data (FPGA bootfiles, settings of registers) stored in a local database (or the global configuration database – no decision yet). Dedicated application(s) will be developed to prepare configuration data according to type of run (calibration, diagnostic, physics etc. ). Translation of muon patterns and their corresponding momenta calculated during simulation into algorithms implemented in VHDL code seems to be most challenging. ESR, July 2003 7

Subsystem RCMS n n Implemented as several XDAQ applications connected with global RCMS Most accesses to RPC Trigger hardware implemented using Internal Interface (TM K. Pozniak) Run configuration data (FPGA bootfiles, settings of registers) stored in a local database (or the global configuration database – no decision yet). Dedicated application(s) will be developed to prepare configuration data according to type of run (calibration, diagnostic, physics etc. ). Translation of muon patterns and their corresponding momenta calculated during simulation into algorithms implemented in VHDL code seems to be most challenging. ESR, July 2003 7

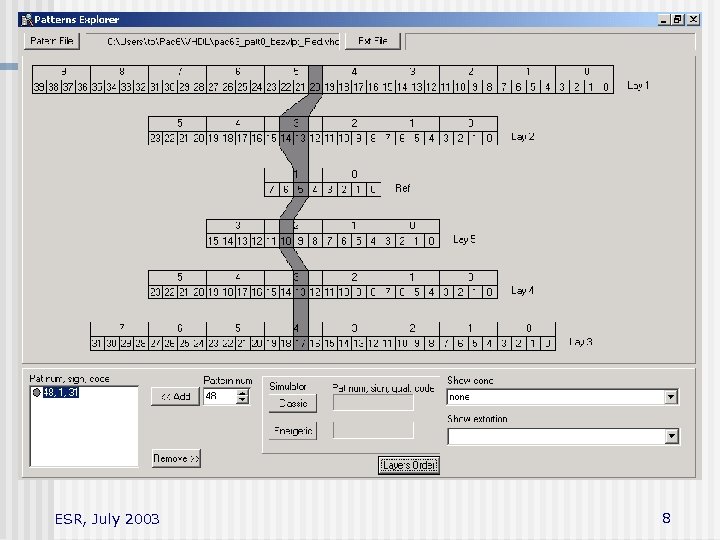

ESR, July 2003 8

ESR, July 2003 8

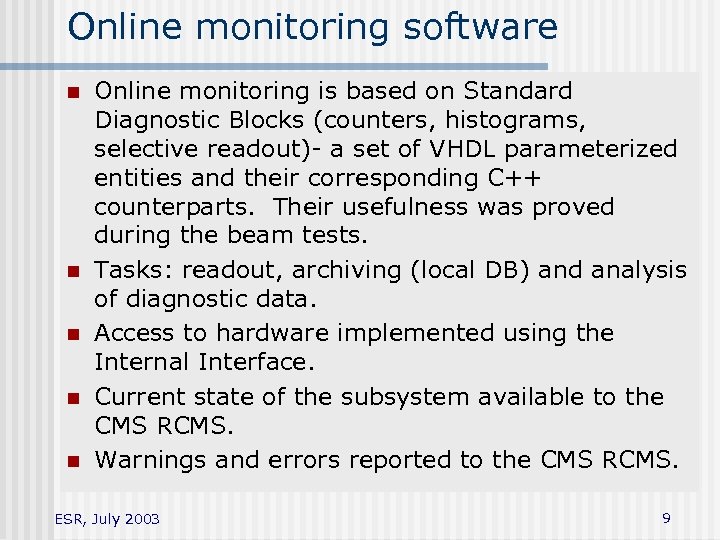

Online monitoring software n n n Online monitoring is based on Standard Diagnostic Blocks (counters, histograms, selective readout)- a set of VHDL parameterized entities and their corresponding C++ counterparts. Their usefulness was proved during the beam tests. Tasks: readout, archiving (local DB) and analysis of diagnostic data. Access to hardware implemented using the Internal Interface. Current state of the subsystem available to the CMS RCMS. Warnings and errors reported to the CMS RCMS. ESR, July 2003 9

Online monitoring software n n n Online monitoring is based on Standard Diagnostic Blocks (counters, histograms, selective readout)- a set of VHDL parameterized entities and their corresponding C++ counterparts. Their usefulness was proved during the beam tests. Tasks: readout, archiving (local DB) and analysis of diagnostic data. Access to hardware implemented using the Internal Interface. Current state of the subsystem available to the CMS RCMS. Warnings and errors reported to the CMS RCMS. ESR, July 2003 9

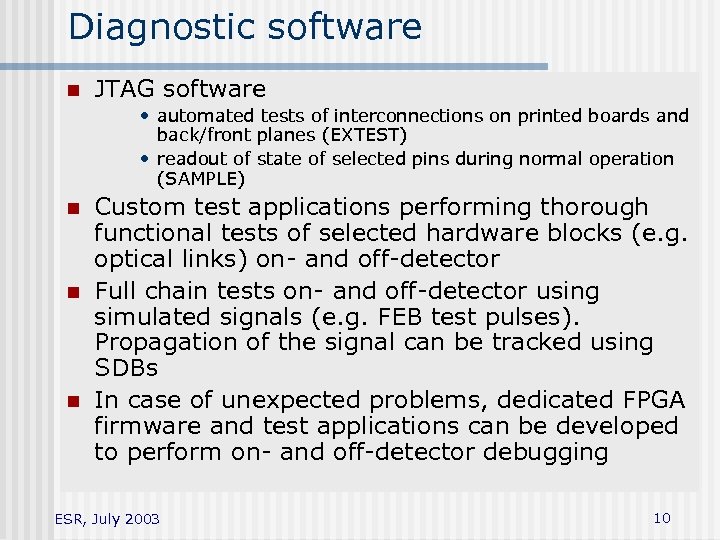

Diagnostic software n JTAG software • automated tests of interconnections on printed boards and back/front planes (EXTEST) • readout of state of selected pins during normal operation (SAMPLE) n n n Custom test applications performing thorough functional tests of selected hardware blocks (e. g. optical links) on- and off-detector Full chain tests on- and off-detector using simulated signals (e. g. FEB test pulses). Propagation of the signal can be tracked using SDBs In case of unexpected problems, dedicated FPGA firmware and test applications can be developed to perform on- and off-detector debugging ESR, July 2003 10

Diagnostic software n JTAG software • automated tests of interconnections on printed boards and back/front planes (EXTEST) • readout of state of selected pins during normal operation (SAMPLE) n n n Custom test applications performing thorough functional tests of selected hardware blocks (e. g. optical links) on- and off-detector Full chain tests on- and off-detector using simulated signals (e. g. FEB test pulses). Propagation of the signal can be tracked using SDBs In case of unexpected problems, dedicated FPGA firmware and test applications can be developed to perform on- and off-detector debugging ESR, July 2003 10

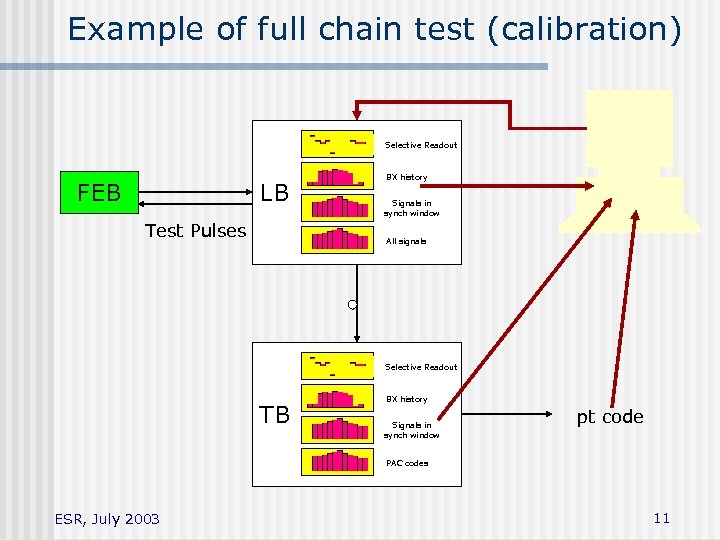

Example of full chain test (calibration) Selective Readout LB FEB Test Pulses BX history Signals in synch window All signals Selective Readout TB BX history Signals in synch window pt code PAC codes ESR, July 2003 11

Example of full chain test (calibration) Selective Readout LB FEB Test Pulses BX history Signals in synch window All signals Selective Readout TB BX history Signals in synch window pt code PAC codes ESR, July 2003 11

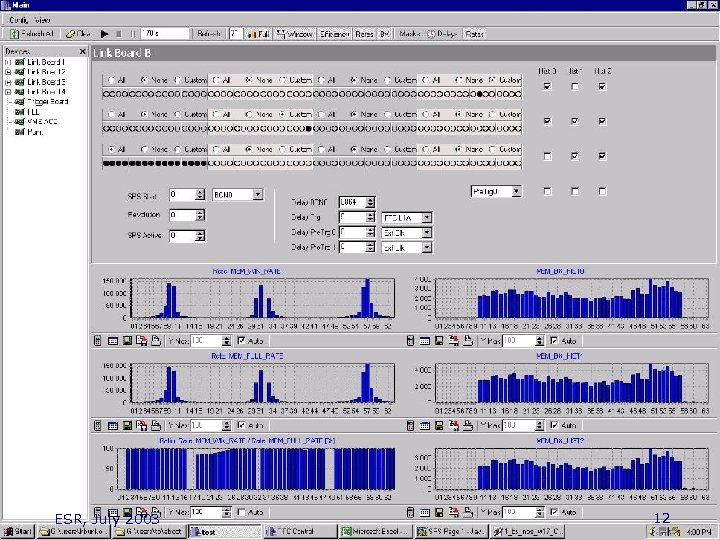

Tbcc screenshot ESR, July 2003 12

Tbcc screenshot ESR, July 2003 12

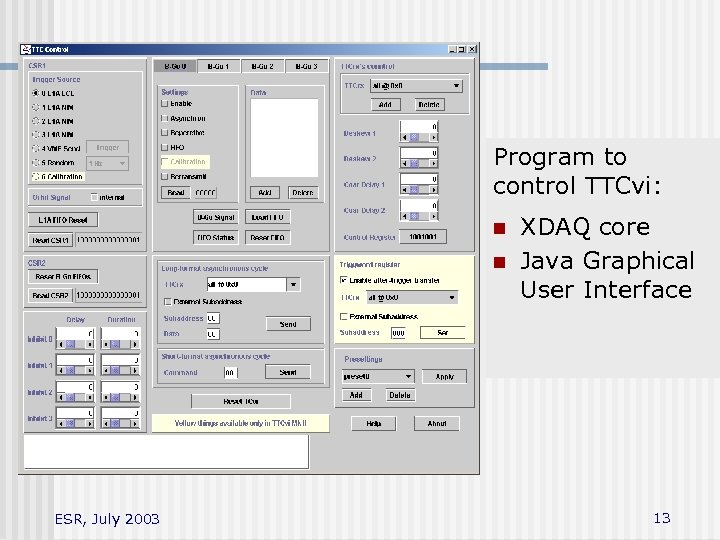

Program to control TTCvi: n n ESR, July 2003 XDAQ core Java Graphical User Interface 13

Program to control TTCvi: n n ESR, July 2003 XDAQ core Java Graphical User Interface 13

Internal Interface (TM Krzysztof Pozniak) n n n n A set of VHDL library functions Implements internal communication bus Can work with any sizes of data line and address line Data is automatically divided into several words or memory areas if it is too wide Data is arranged to occupy minimum possible size VHDL and C++ code use common description files (IID) Internal Interface Description (IID) files describe: n n n Registers, meanings of bits in registers, memory areas Their sizes Types of access IID files are directly included in C++ projects and automatically converted to VHDL using C++ preprocessor Result: no need to manually create address maps, calculate address etc fast, reliable development ESR, July 2003 14

Internal Interface (TM Krzysztof Pozniak) n n n n A set of VHDL library functions Implements internal communication bus Can work with any sizes of data line and address line Data is automatically divided into several words or memory areas if it is too wide Data is arranged to occupy minimum possible size VHDL and C++ code use common description files (IID) Internal Interface Description (IID) files describe: n n n Registers, meanings of bits in registers, memory areas Their sizes Types of access IID files are directly included in C++ projects and automatically converted to VHDL using C++ preprocessor Result: no need to manually create address maps, calculate address etc fast, reliable development ESR, July 2003 14

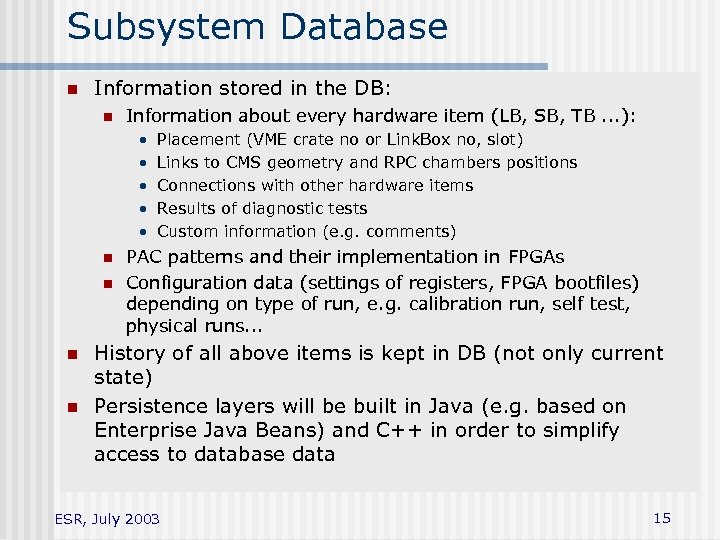

Subsystem Database n Information stored in the DB: n Information about every hardware item (LB, SB, TB. . . ): • • • n n Placement (VME crate no or Link. Box no, slot) Links to CMS geometry and RPC chambers positions Connections with other hardware items Results of diagnostic tests Custom information (e. g. comments) PAC patterns and their implementation in FPGAs Configuration data (settings of registers, FPGA bootfiles) depending on type of run, e. g. calibration run, self test, physical runs. . . History of all above items is kept in DB (not only current state) Persistence layers will be built in Java (e. g. based on Enterprise Java Beans) and C++ in order to simplify access to database data ESR, July 2003 15

Subsystem Database n Information stored in the DB: n Information about every hardware item (LB, SB, TB. . . ): • • • n n Placement (VME crate no or Link. Box no, slot) Links to CMS geometry and RPC chambers positions Connections with other hardware items Results of diagnostic tests Custom information (e. g. comments) PAC patterns and their implementation in FPGAs Configuration data (settings of registers, FPGA bootfiles) depending on type of run, e. g. calibration run, self test, physical runs. . . History of all above items is kept in DB (not only current state) Persistence layers will be built in Java (e. g. based on Enterprise Java Beans) and C++ in order to simplify access to database data ESR, July 2003 15

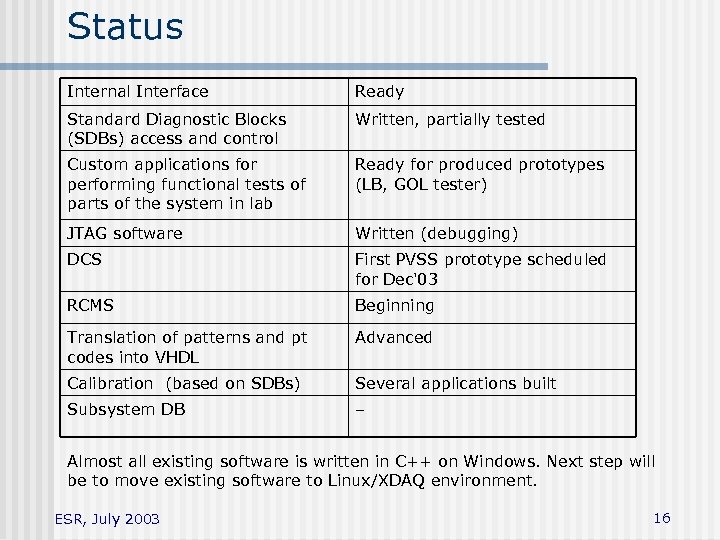

Status Internal Interface Ready Standard Diagnostic Blocks (SDBs) access and control Written, partially tested Custom applications for performing functional tests of parts of the system in lab Ready for produced prototypes (LB, GOL tester) JTAG software Written (debugging) DCS First PVSS prototype scheduled for Dec'03 RCMS Beginning Translation of patterns and pt codes into VHDL Advanced Calibration (based on SDBs) Several applications built Subsystem DB – Almost all existing software is written in C++ on Windows. Next step will be to move existing software to Linux/XDAQ environment. ESR, July 2003 16

Status Internal Interface Ready Standard Diagnostic Blocks (SDBs) access and control Written, partially tested Custom applications for performing functional tests of parts of the system in lab Ready for produced prototypes (LB, GOL tester) JTAG software Written (debugging) DCS First PVSS prototype scheduled for Dec'03 RCMS Beginning Translation of patterns and pt codes into VHDL Advanced Calibration (based on SDBs) Several applications built Subsystem DB – Almost all existing software is written in C++ on Windows. Next step will be to move existing software to Linux/XDAQ environment. ESR, July 2003 16