3a480774e42978f17e8ed68341d8e21f.ppt

- Количество слайдов: 18

RPC Front End Electronics n On chamber discriminator q q n The TDC board q q q n n The strips The CMS discriminator chips The discriminator board Test results The TDC and Crate block diagram The TDC board test result The trigger board The board counts Status Sept 25, 2008 PHENIX RPC review C. Y. Chi 1

RPC Strip n n Our chamber is closely follow the CMS design. Our on-chamber electronics will try to follow their electronics too. The CMS barrel strips is 1. 3 m long, 4 cm or 2 cm wide. q 15/40 ohms impedance. 420 pf/160 pf capacitance. q Fully terminated strips. CMS encap RPC q Cover 5/16 degree in phi, 7 to 38 mm in width and 22 to 55 cm in length q Un-terminated. q Lemo cables are used to connect strip to the discriminator board PHENIX RPC strip width range from 11. 4 mm by 141 mm to 64. 6 mm by 554. 2 mm. q The smallest one has 46 ohms impedance and 16 pf of capacitance. q The largest one has 10 ohms impedance and 286 pf of capacitance. Sept 25, 2008 PHENIX RPC review C. Y. Chi 2

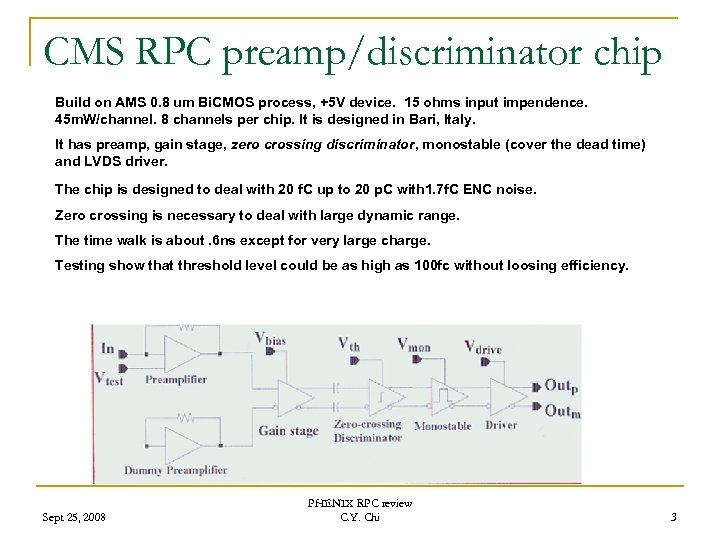

CMS RPC preamp/discriminator chip Build on AMS 0. 8 um Bi. CMOS process, +5 V device. 15 ohms input impendence. 45 m. W/channel. 8 channels per chip. It is designed in Bari, Italy. It has preamp, gain stage, zero crossing discriminator, monostable (cover the dead time) and LVDS driver. The chip is designed to deal with 20 f. C up to 20 p. C with 1. 7 f. C ENC noise. Zero crossing is necessary to deal with large dynamic range. The time walk is about. 6 ns except for very large charge. Testing show that threshold level could be as high as 100 fc without loosing efficiency. Sept 25, 2008 PHENIX RPC review C. Y. Chi 3

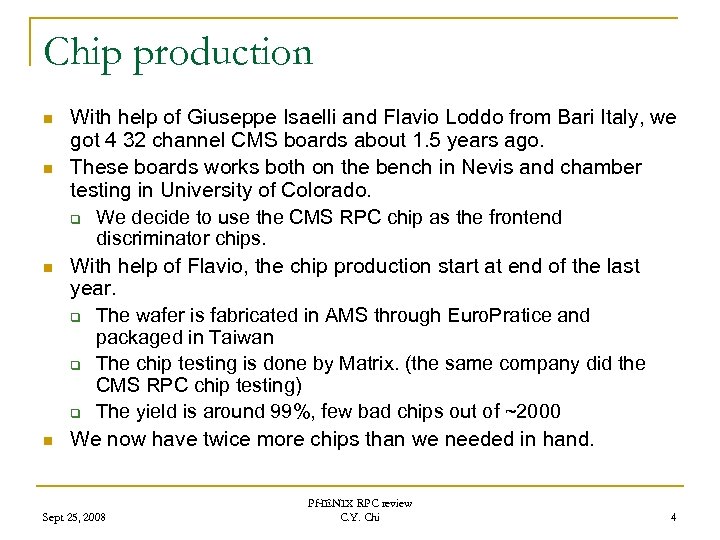

Chip production n n With help of Giuseppe Isaelli and Flavio Loddo from Bari Italy, we got 4 32 channel CMS boards about 1. 5 years ago. These boards works both on the bench in Nevis and chamber testing in University of Colorado. q We decide to use the CMS RPC chip as the frontend discriminator chips. With help of Flavio, the chip production start at end of the last year. q The wafer is fabricated in AMS through Euro. Pratice and packaged in Taiwan q The chip testing is done by Matrix. (the same company did the CMS RPC chip testing) q The yield is around 99%, few bad chips out of ~2000 We now have twice more chips than we needed in hand. Sept 25, 2008 PHENIX RPC review C. Y. Chi 4

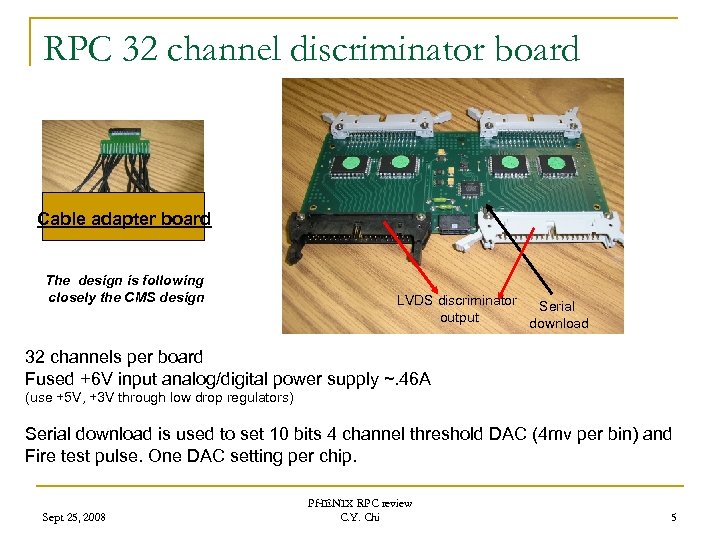

RPC 32 channel discriminator board Cable adapter board The design is following closely the CMS design LVDS discriminator Serial output download 32 channels per board Fused +6 V input analog/digital power supply ~. 46 A (use +5 V, +3 V through low drop regulators) Serial download is used to set 10 bits 4 channel threshold DAC (4 mv per bin) and Fire test pulse. One DAC setting per chip. Sept 25, 2008 PHENIX RPC review C. Y. Chi 5

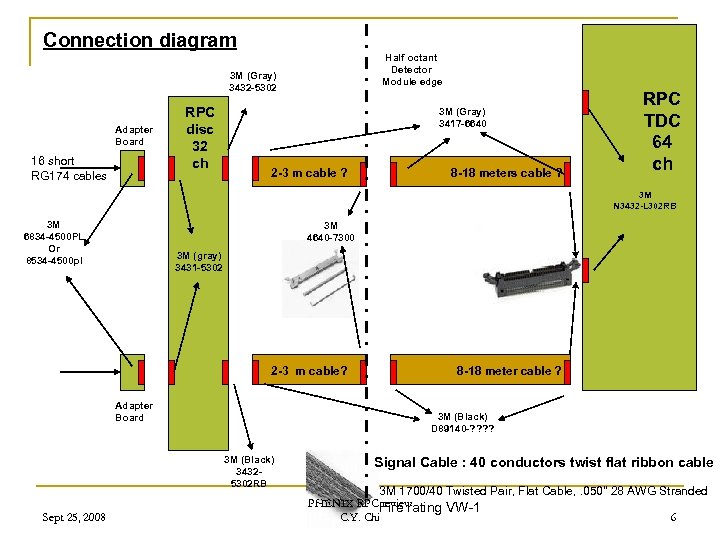

Connection diagram Half octant Detector Module edge 3 M (Gray) 3432 -5302 Adapter Board 16 short RG 174 cables RPC disc 32 ch 3 M (Gray) 3417 -6640 2 -3 m cable ? 8 -18 meters cable ? RPC TDC 64 ch 3 M N 3432 -L 302 RB 3 M 6834 -4500 PL Or 8534 -4500 pl 3 M 4640 -7300 3 M (gray) 3431 -5302 2 -3 m cable? Adapter Board 3 M (Black) D 89140 -? ? 3 M (Black) 34325302 RB Sept 25, 2008 8 -18 meter cable ? Signal Cable : 40 conductors twist flat ribbon cable 3 M 1700/40 Twisted Pair, Flat Cable, . 050" 28 AWG Stranded PHENIX RPC Fire rating VW-1 review 6 C. Y. Chi

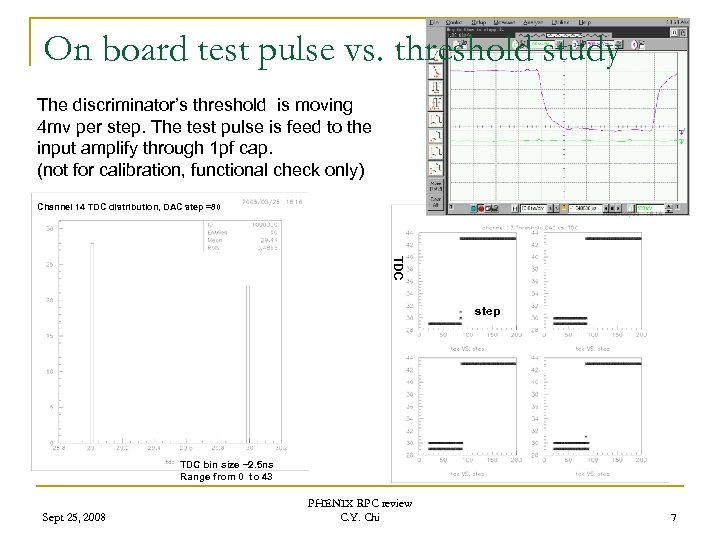

On board test pulse vs. threshold study The discriminator’s threshold is moving 4 mv per step. The test pulse is feed to the input amplify through 1 pf cap. (not for calibration, functional check only) Channel 14 TDC distribution, DAC step =80 TDC step TDC bin size ~2. 5 ns Range from 0 to 43 Sept 25, 2008 PHENIX RPC review C. Y. Chi 7

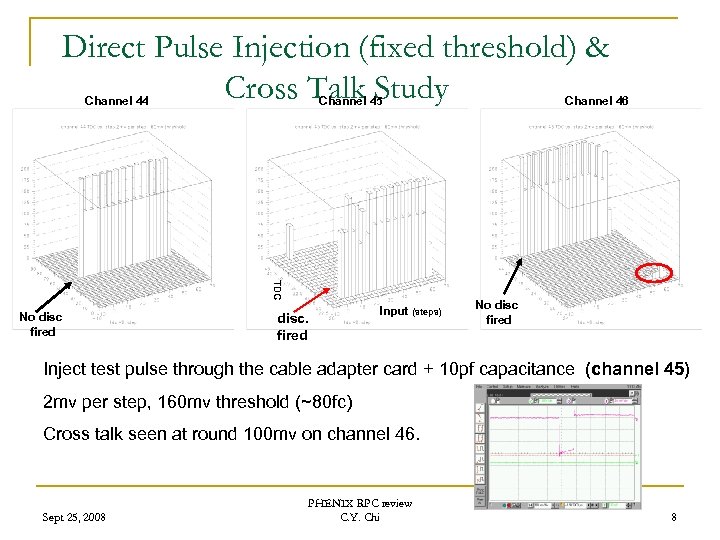

Direct Pulse Injection (fixed threshold) & Cross Talk Study Channel 44 Channel 45 TDC No disc fired disc. fired Input (steps) Channel 46 No disc fired Inject test pulse through the cable adapter card + 10 pf capacitance (channel 45) 2 mv per step, 160 mv threshold (~80 fc) Cross talk seen at round 100 mv on channel 46. Sept 25, 2008 PHENIX RPC review C. Y. Chi 8

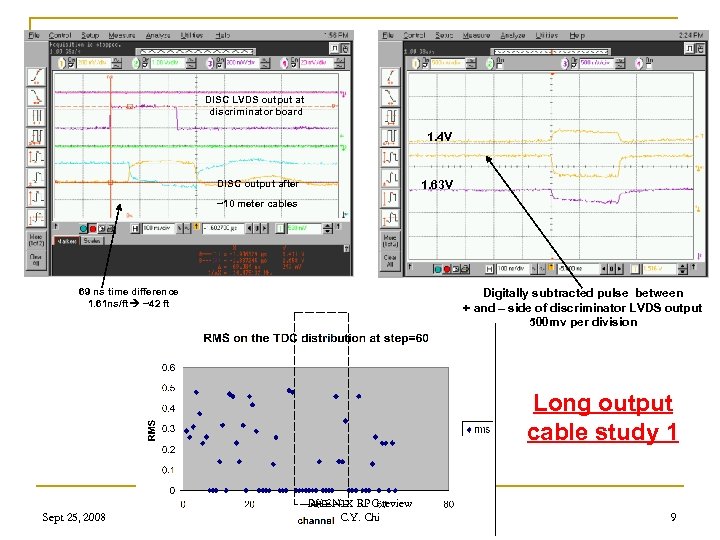

DISC LVDS output at discriminator board 1. 4 V DISC output after 1. 63 V ~10 meter cables 69 ns time difference 1. 61 ns/ft ~42 ft Digitally subtracted pulse between + and – side of discriminator LVDS output 500 mv per division Long output cable study 1 Sept 25, 2008 PHENIX RPC review C. Y. Chi 9

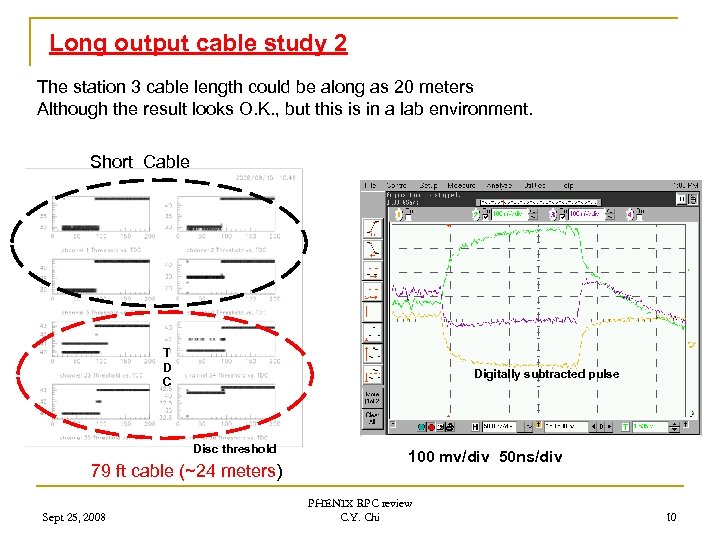

Long output cable study 2 The station 3 cable length could be along as 20 meters Although the result looks O. K. , but this is in a lab environment. Short Cable T D C Digitally subtracted pulse Disc threshold 79 ft cable (~24 meters) Sept 25, 2008 100 mv/div 50 ns/div PHENIX RPC review C. Y. Chi 10

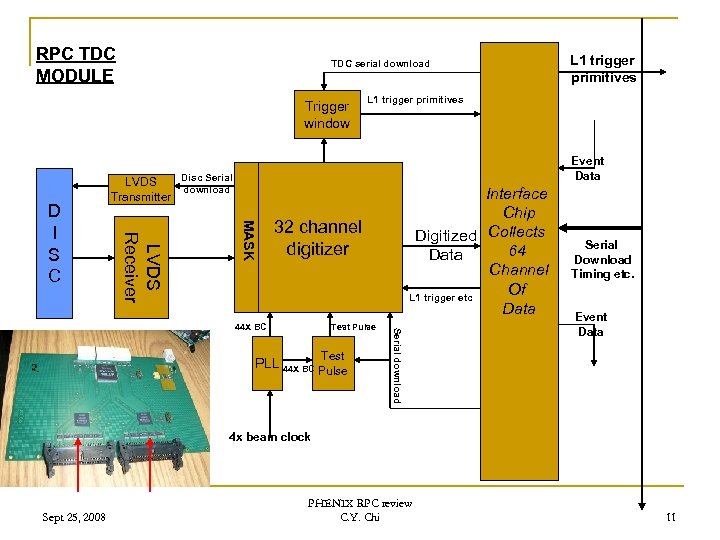

RPC TDC MODULE TDC serial download Trigger window L 1 trigger primitives Event Data Disc Serial LVDS download Transmitter MASK LVDS Receiver D I S C L 1 trigger primitives Interface Chip Digitized Collects 64 Data Channel Of L 1 trigger etc Data 32 channel digitizer Test Pulse Test PLL 44 X BC Pulse Serial download 44 X BC Serial Download Timing etc. Event Data 4 x beam clock Sept 25, 2008 PHENIX RPC review C. Y. Chi 11

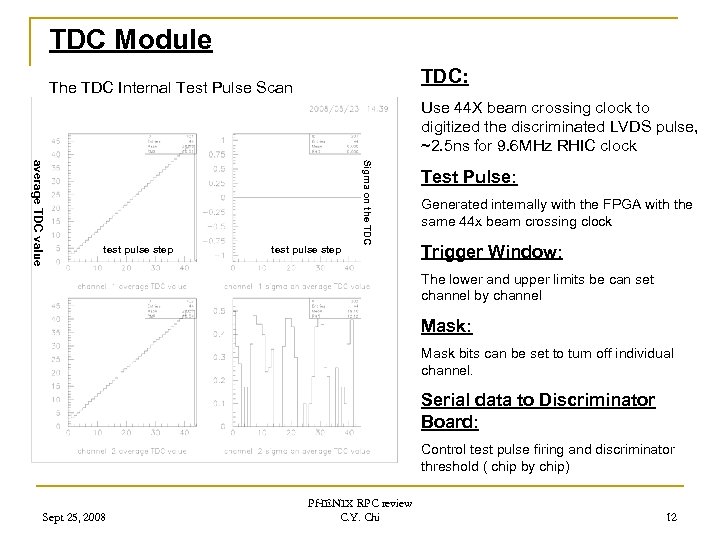

TDC Module TDC: The TDC Internal Test Pulse Scan Use 44 X beam crossing clock to digitized the discriminated LVDS pulse, ~2. 5 ns for 9. 6 MHz RHIC clock test pulse step Sigma on the TDC average TDC value test pulse step Test Pulse: Generated internally with the FPGA with the same 44 x beam crossing clock Trigger Window: The lower and upper limits be can set channel by channel Mask: Mask bits can be set to turn off individual channel. Serial data to Discriminator Board: Control test pulse firing and discriminator threshold ( chip by chip) Sept 25, 2008 PHENIX RPC review C. Y. Chi 12

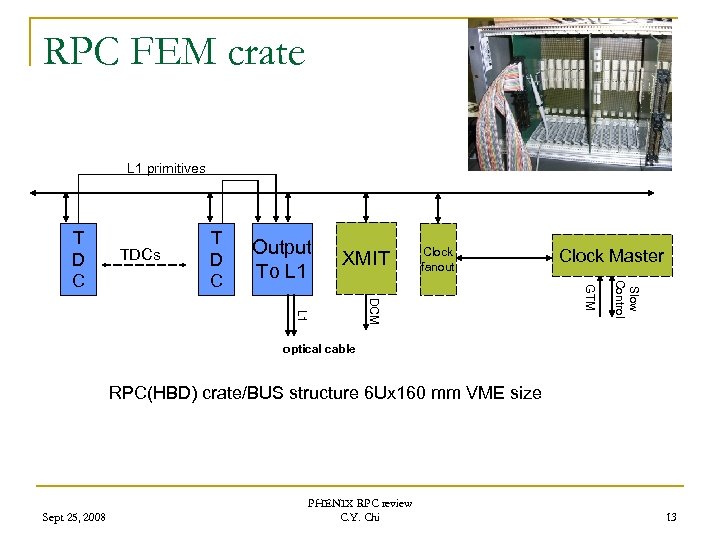

RPC FEM crate L 1 primitives TDCs Output To L 1 XMIT Clock fanout Clock Master DCM L 1 Slow Control T D C GTM T D C optical cable RPC(HBD) crate/BUS structure 6 Ux 160 mm VME size Sept 25, 2008 PHENIX RPC review C. Y. Chi 13

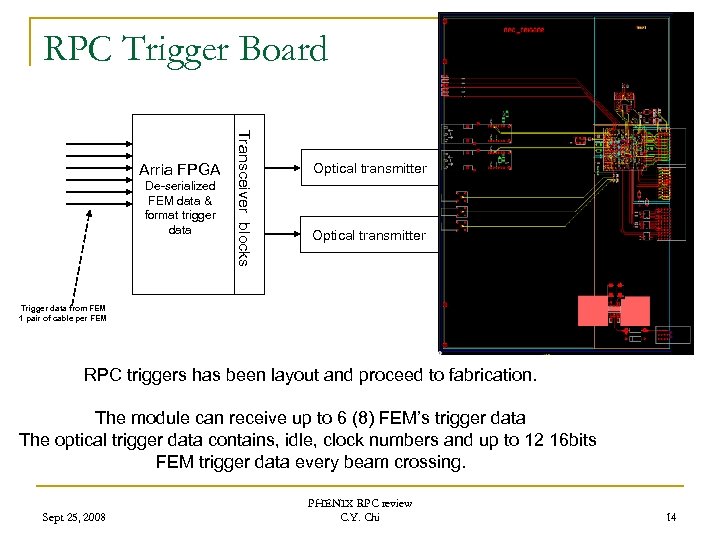

RPC Trigger Board De-serialized FEM data & format trigger data Transceiver blocks Arria FPGA Optical transmitter 2. 8 Gbits/sec Optical transmitter Trigger data from FEM 1 pair of cable per FEM RPC triggers has been layout and proceed to fabrication. The module can receive up to 6 (8) FEM’s trigger data The optical trigger data contains, idle, clock numbers and up to 12 16 bits FEM trigger data every beam crossing. Sept 25, 2008 PHENIX RPC review C. Y. Chi 14

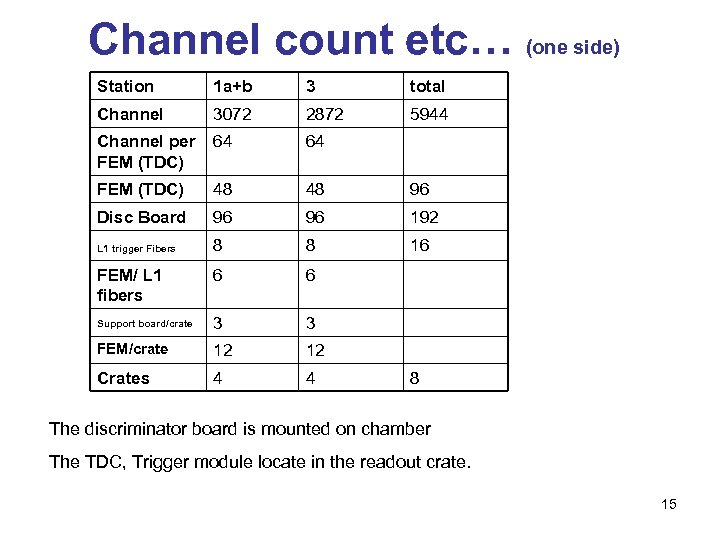

Channel count etc… (one side) Station 1 a+b 3 total Channel 3072 2872 5944 Channel per FEM (TDC) 64 64 FEM (TDC) 48 48 96 Disc Board 96 96 192 L 1 trigger Fibers 8 8 16 FEM/ L 1 fibers 6 6 Support board/crate 3 3 FEM/crate 12 12 Crates 4 4 8 The discriminator board is mounted on chamber The TDC, Trigger module locate in the readout crate. 15

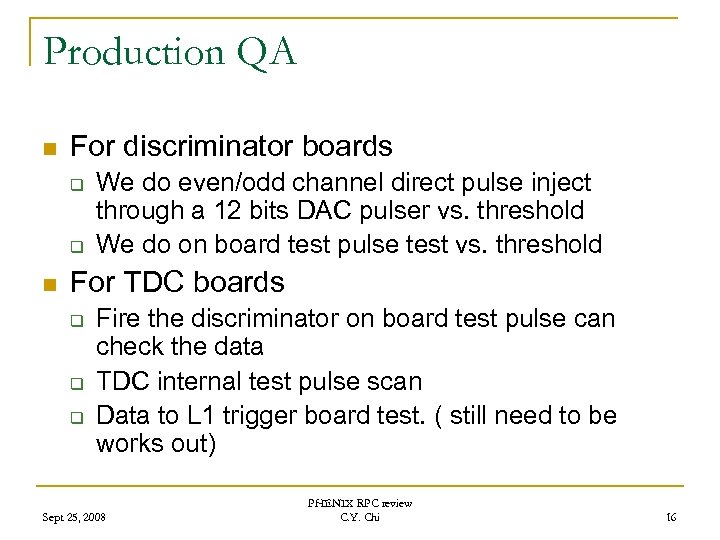

Production QA n For discriminator boards q q n We do even/odd channel direct pulse inject through a 12 bits DAC pulser vs. threshold We do on board test pulse test vs. threshold For TDC boards q q q Fire the discriminator on board test pulse can check the data TDC internal test pulse scan Data to L 1 trigger board test. ( still need to be works out) Sept 25, 2008 PHENIX RPC review C. Y. Chi 16

STATUS n n The discriminator and TDC modules has been successfully prototyped. Waiting for on chamber testing. q n n Grounding issue need to be resolved with chamber testing n CMS 32 channel board has been tested in both Colorado and BNL factory. We are building, 40 discriminator modules, 20 TDC boards, 3 sets of crates+ clock master modules for the coming run and individual factory readout/test stand. Trigger modules is designed and proceed to fabrication. Sept 25, 2008 PHENIX RPC review C. Y. Chi 17

Production Outlook n The production cycle normally last about 6 months. This include, fabricate boards, buy parts, board assembly and testing. q n For the RPC 3 N discriminator board, we have most of parts on hand already. We will start production around Nov this year. Sept 25, 2008 PHENIX RPC review C. Y. Chi 18

3a480774e42978f17e8ed68341d8e21f.ppt